C fr

C fr

C fr

C fr

Cyfrowe

Cyfrowe

Cyfrowe

Cyfrowe

yy

układy

układy

yy

układy

układy

układy

układy

kk

jj

układy

układy

kk

jj

sekwen

sekwencyjne

cyjne

sekwen

sekwencyjne

cyjne

6 marca 2011

Wojciech Kucewicz

2

yj

yj

yj

yj

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne to takie układy logiczne których stan

to takie układy logiczne których stan

Układy sekwencyjne

Układy sekwencyjne to takie układy logiczne, których stan

to takie układy logiczne, których stan

wyjść zależy nie tylko od aktualnego stanu wejść, lecz

wyjść zależy nie tylko od aktualnego stanu wejść, lecz

również od poprzednich stanów wejść i wyjść.

również od poprzednich stanów wejść i wyjść.

Układy sekwencyjne pamiętają historię stanów systemu,

czyli posiadają pamięć.

czyli posiadają pamięć.

6 marca 2011

Wojciech Kucewicz

3

Opis układów

Opis układów

Opis układów

Opis układów

Opis układów

Opis układów

k

j

h

k

j

h

Opis układów

Opis układów

k

j

h

k

j

h

sekwencyjnych

sekwencyjnych

sekwencyjnych

sekwencyjnych

6 marca 2011

Wojciech Kucewicz

4

Opis układów sekwencyjnych

Opis układów sekwencyjnych

Opis układów sekwencyjnych

Opis układów sekwencyjnych

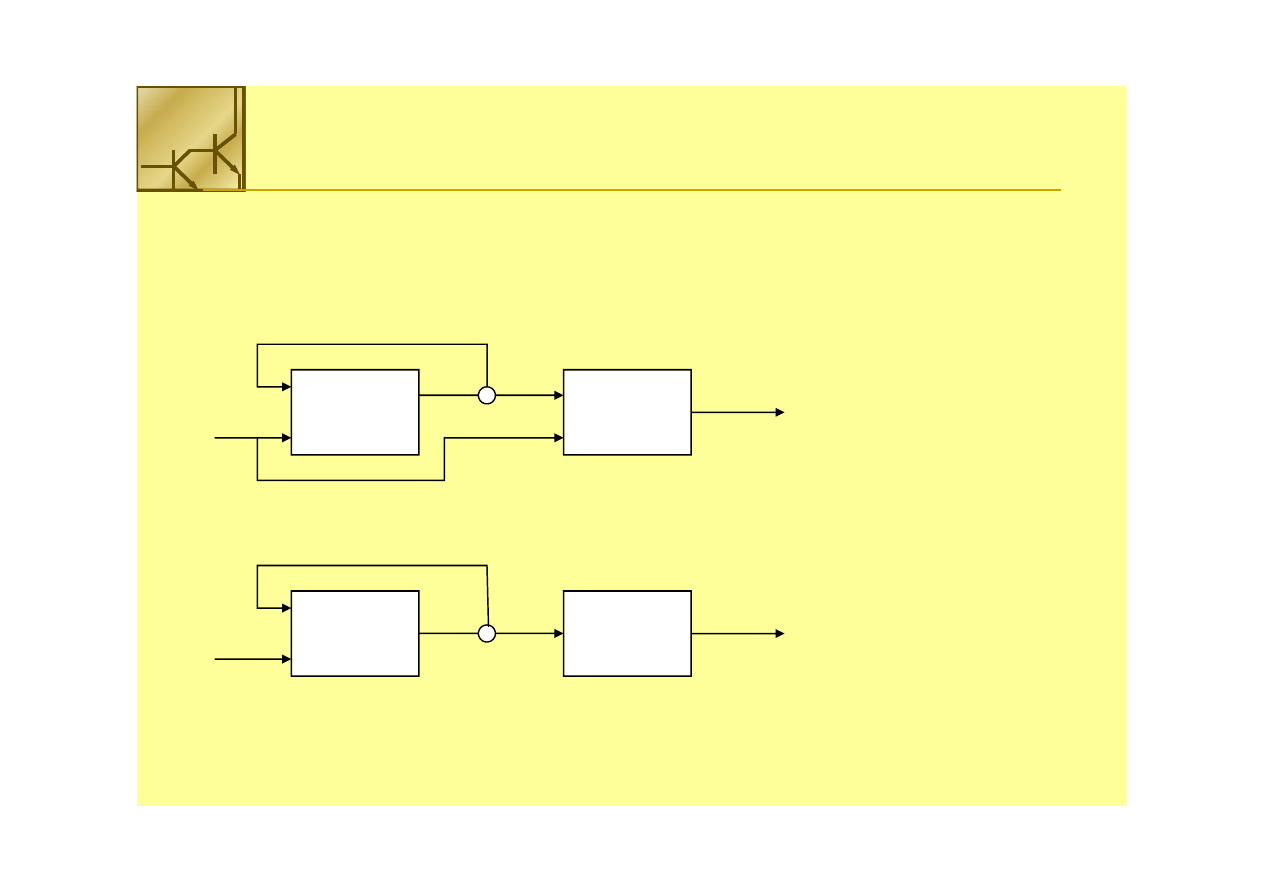

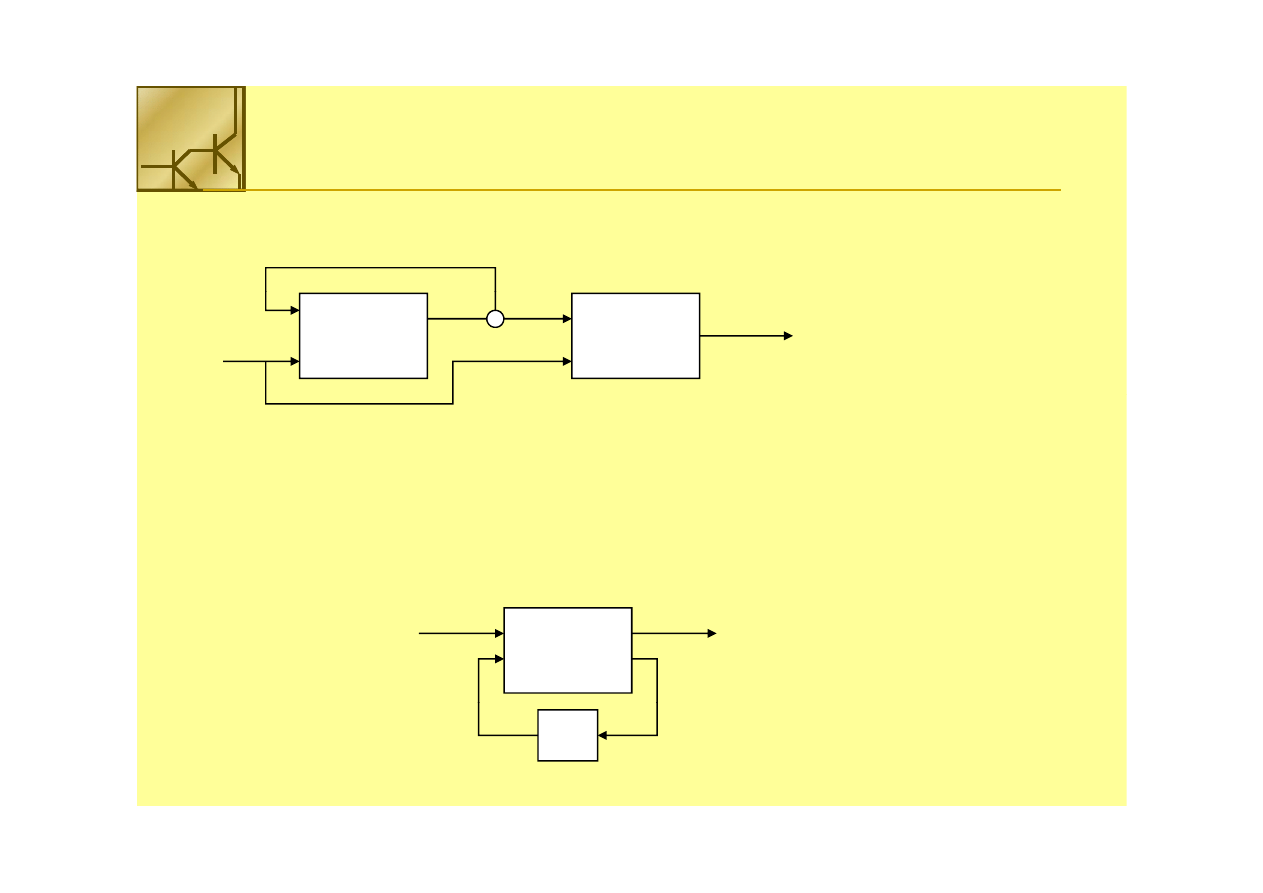

Do opisu funkcji sekwencyjnych stosowane są dwa modele układów:

Do opisu funkcji sekwencyjnych stosowane są dwa modele układów:

FF

S

S

automat Mealy’ego

automat Mealy’ego

FF

tt

f(S

f(S

tt

X

X

tt

))

gg

ff

FF

X

X

FF

tt

= f(S

= f(S

tt

, X

, X

tt

))

automat Moore’a

automat Moore’a

FF

S

S

gg

ff

FF

X

X

S

S

FF

tt

= f(S

= f(S

tt

) ) Î

Î

S

S

tt

= g(X

= g(X

tt

))

6 marca 2011

Wojciech Kucewicz

5

Blok g jest blokiem pamięci, natomiast blok f jest układem

Blok g jest blokiem pamięci, natomiast blok f jest układem kombinacyjnym

kombinacyjnym

Wyrażenie automat oznacza model matematyczny układu sekwencyjnego

Wyrażenie automat oznacza model matematyczny układu sekwencyjnego

Opis układów sekwencyjnych

Opis układów sekwencyjnych

Opis układów sekwencyjnych

Opis układów sekwencyjnych

S

S

automat Mealy’ego

automat Mealy’ego

gg

ff

FF

X

X

S

S

FF

tt

= f(S

= f(S

tt

, X

, X

tt

))

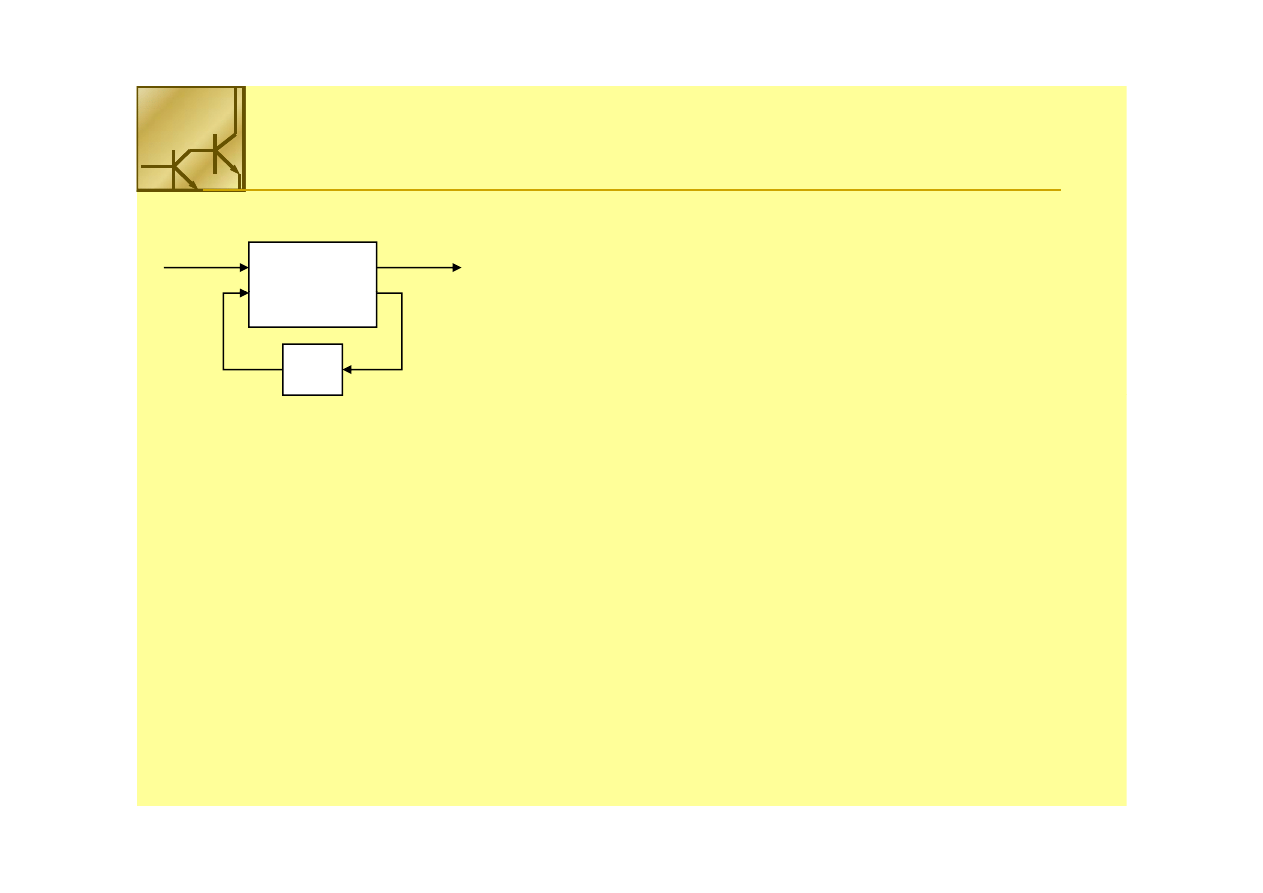

Blok g można rozdzielić na dwa bloki: rejestr u (zawierający elementy

Blok g można rozdzielić na dwa bloki: rejestr u (zawierający elementy

pamięciowe) oraz układ kombinacyjny z

pamięciowe) oraz układ kombinacyjny z

p

ę

)

yj y

p

ę

)

yj y

Schemat blokowy automatu Mealy’ego można przekształcić do postaci:

Schemat blokowy automatu Mealy’ego można przekształcić do postaci:

Blok kombinacyny

Blok kombinacyny

d l

k śl

d l

k śl

ff

zz

y y

y y

X

X

FF

S

S

Model automatu jest określony

Model automatu jest określony

przez zbiory X, S i F oraz funkcje g

przez zbiory X, S i F oraz funkcje g

i f

i f

J ż li bi

X S F k ń

t

J ż li bi

X S F k ń

t

6 marca 2011

Wojciech Kucewicz

6

uu

Rejestr

Rejestr

Jeżeli zbiory X, S, F są skończone to

Jeżeli zbiory X, S, F są skończone to

tworzony automat jest skończony

tworzony automat jest skończony

FSM (ang. Finite State Machine)

FSM (ang. Finite State Machine)

Opis układów sekwencyjnych

Opis układów sekwencyjnych

Opis układów sekwencyjnych

Opis układów sekwencyjnych

ff

Blok kombinacyjny

Blok kombinacyjny

X

X

FF

S

S

Działanie układu sekwencyjnego można opisać w

Działanie układu sekwencyjnego można opisać w

postaci przebiegów czasowych sygnałów na

postaci przebiegów czasowych sygnałów na

zz

uu

S

S

postac przeb egów czasowych sygnałów na

postac przeb egów czasowych sygnałów na

wejściach X i wyjściach F.

wejściach X i wyjściach F.

Rejestr

Rejestr

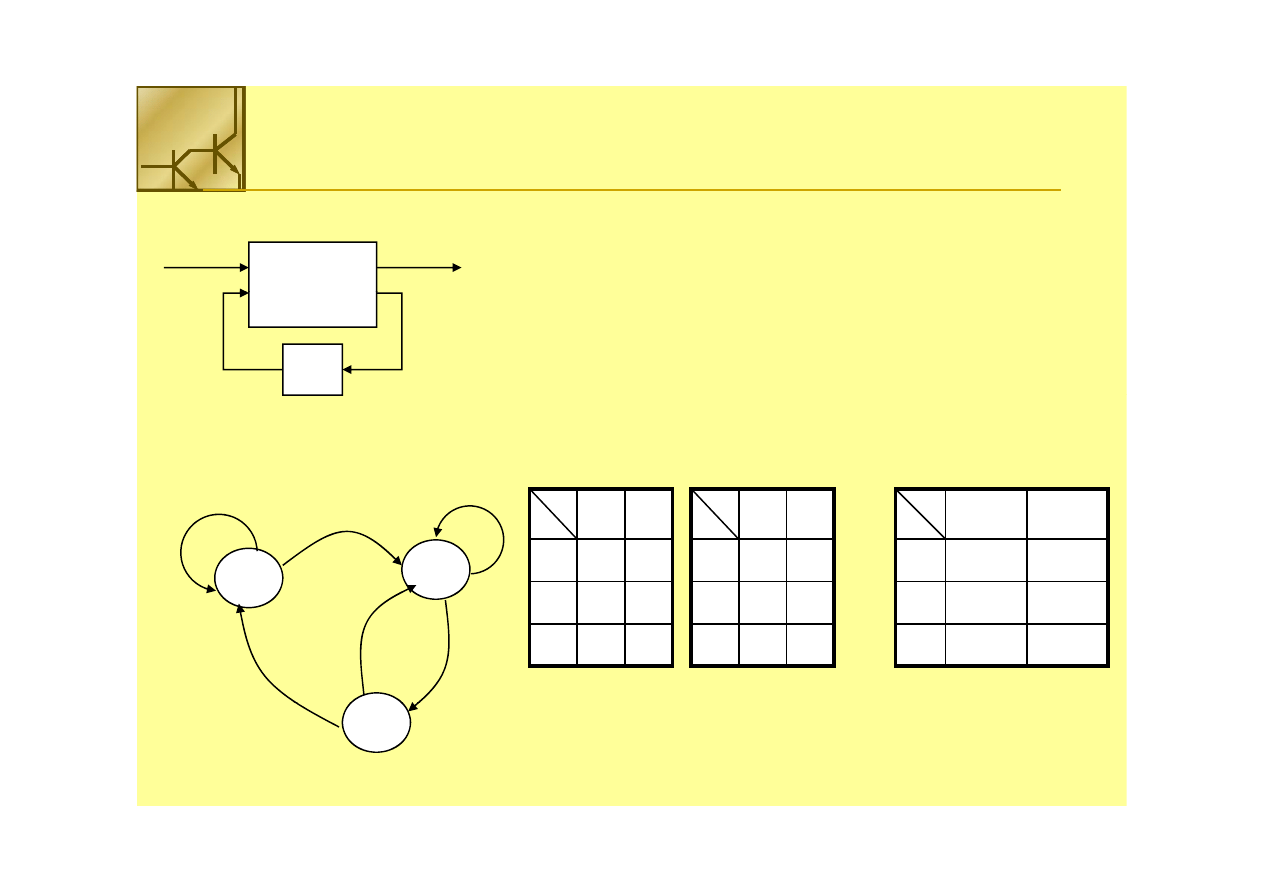

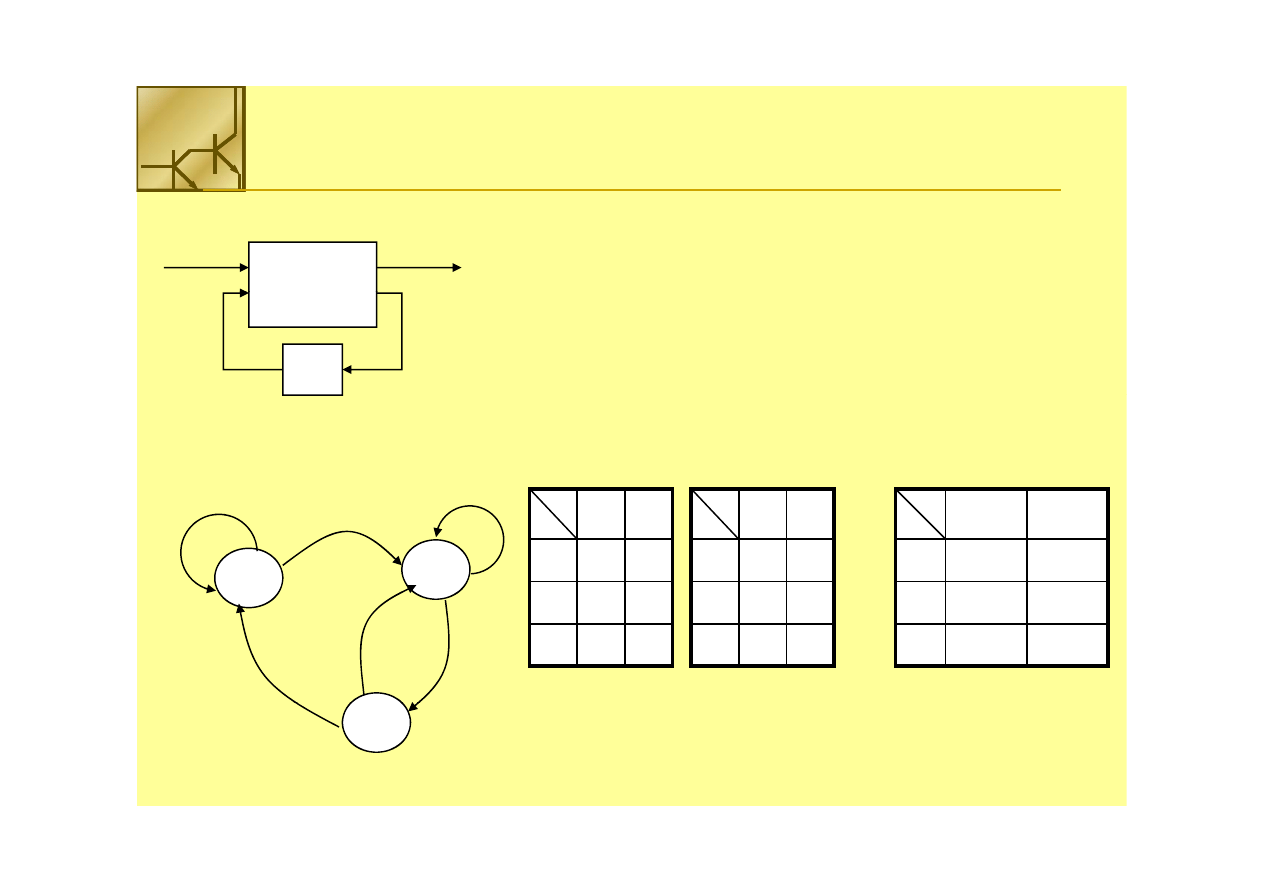

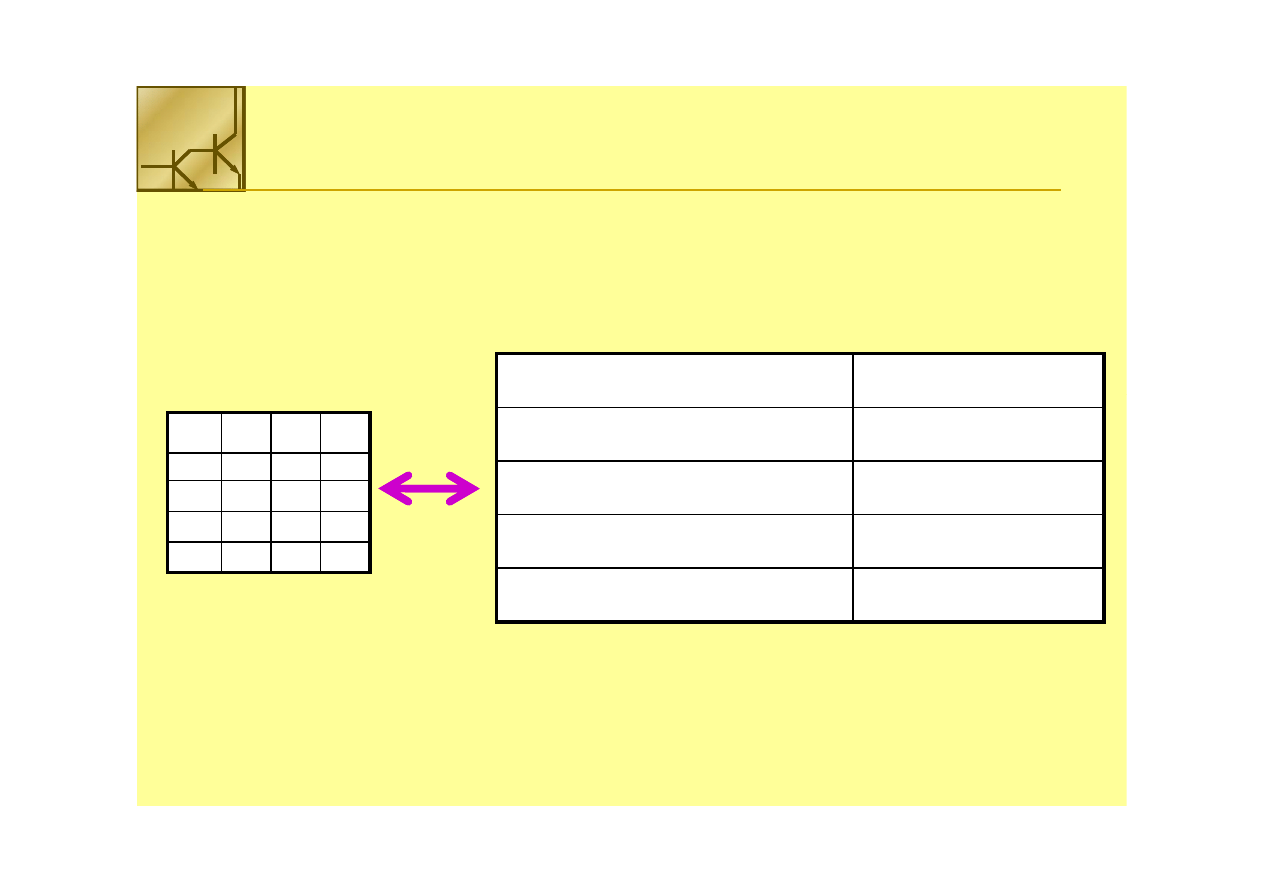

Działanie układu sekwencyjnego można opisać w postaci grafu przejść

Działanie układu sekwencyjnego można opisać w postaci grafu przejść

między definiowanymi stanami wewnętrznymi układu.

między definiowanymi stanami wewnętrznymi układu.

Dla określonych zbiorów X, F, S opisuje on funkcję g, czyli każdej parze

Dla określonych zbiorów X, F, S opisuje on funkcję g, czyli każdej parze

stanów obecnych (X,S) przyporządkowuje stan następny S

stanów obecnych (X,S) przyporządkowuje stan następny S

++

. Ponadto graf

. Ponadto graf

przejść ilustruje funkcję wyjściową f.

przejść ilustruje funkcję wyjściową f.

Od

i d iki f jść j t t bli

jść P i

ż f

i

Od

i d iki f jść j t t bli

jść P i

ż f

i

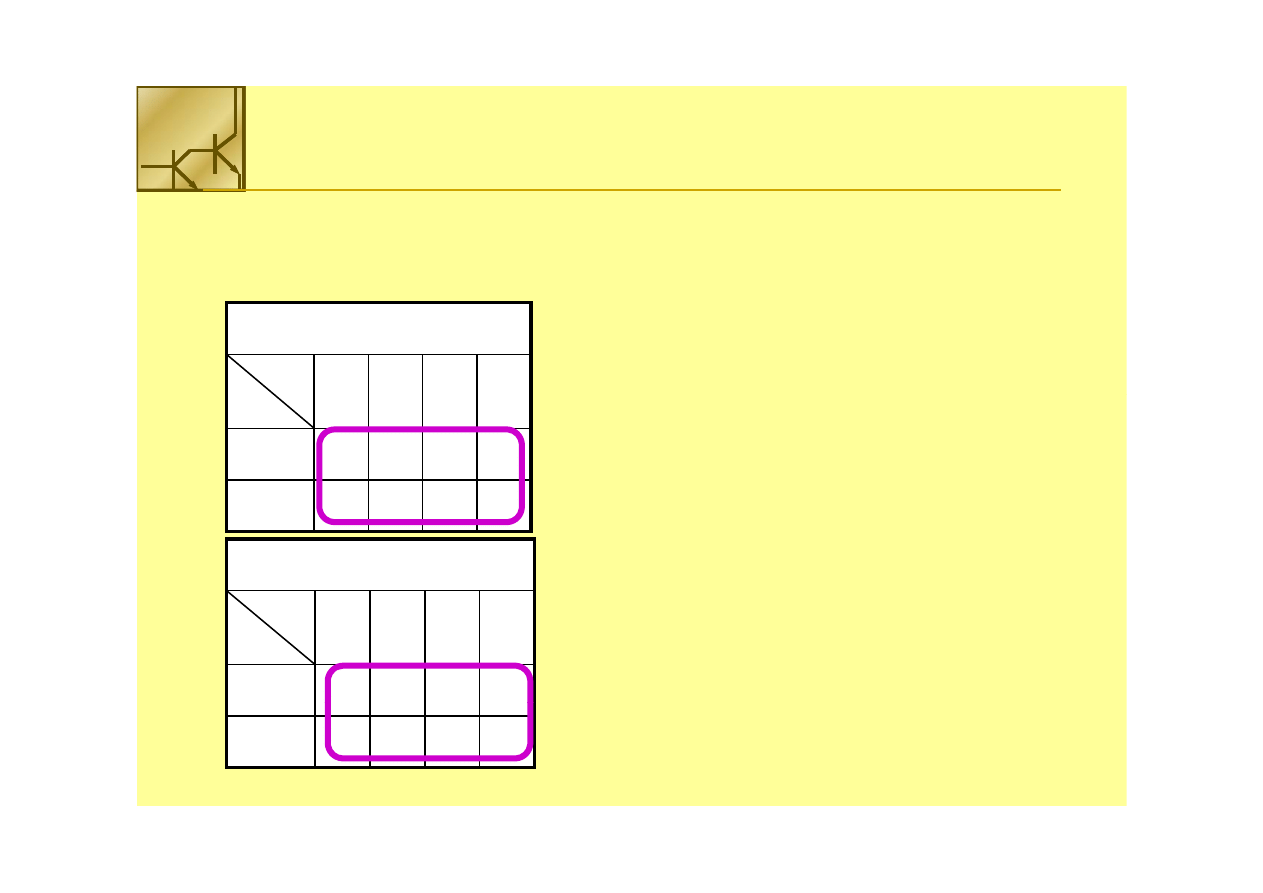

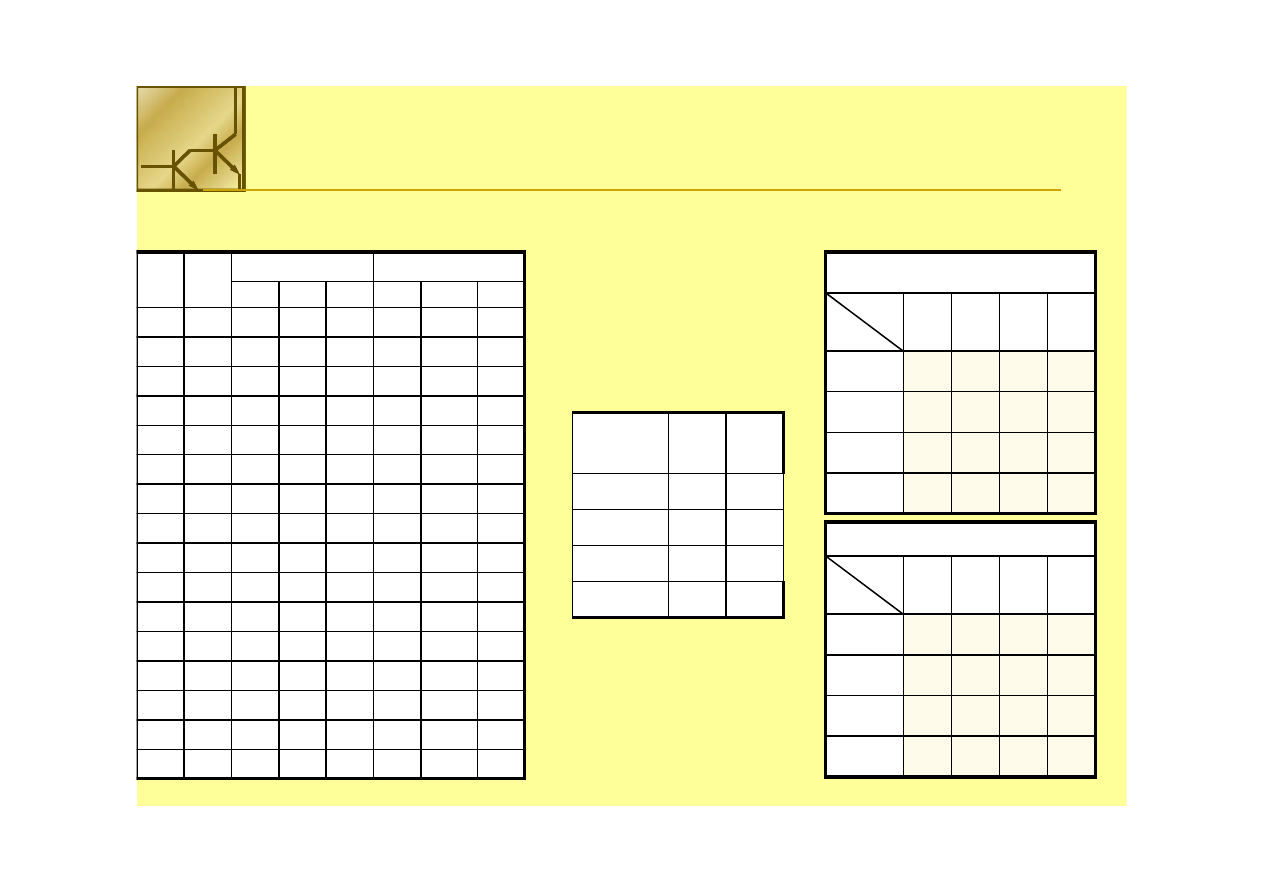

Odpowiednikiem grafu przejść jest tablica przejść. Ponieważ graf i

Odpowiednikiem grafu przejść jest tablica przejść. Ponieważ graf i

tablica zawierają również stany wyjść, stosuje się określenie: graf

tablica zawierają również stany wyjść, stosuje się określenie: graf

(tablica) przejść

(tablica) przejść--wyjść.

wyjść.

6 marca 2011

Wojciech Kucewicz

7

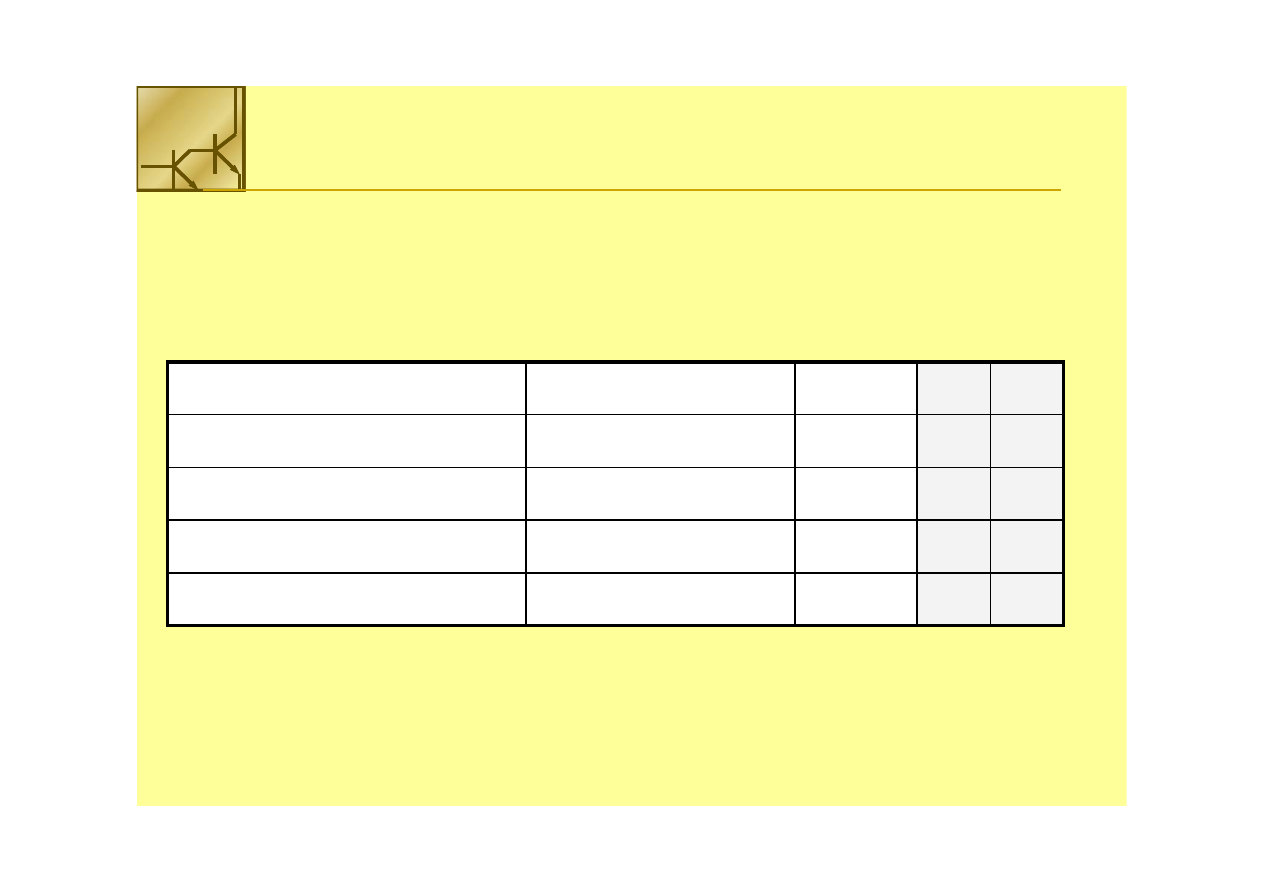

Konstrukcja grafów i tablic

Konstrukcja grafów i tablic

Konstrukcja grafów i tablic

Konstrukcja grafów i tablic

ff

Blok kombinacyjny

Blok kombinacyjny

X

X

FF

S

S

Wierzchołki grafu są oznaczone symbolami stanów

Wierzchołki grafu są oznaczone symbolami stanów

wewnętrznych S. Strzałki grafu są opisane przez

wewnętrznych S. Strzałki grafu są opisane przez

parę stanów (X F) Strzałka oznacza przejście z

parę stanów (X F) Strzałka oznacza przejście z

zz

uu

S

S

parę stanów (X, F). Strzałka oznacza przejście z

parę stanów (X, F). Strzałka oznacza przejście z

jednego stanu wewnętrznego do innego (lub

jednego stanu wewnętrznego do innego (lub

utrzymanie tego samego) oraz utworzenie nowego

utrzymanie tego samego) oraz utworzenie nowego

stanu

stanu wyjść F pod warunkiem wystąpienia podanego

wyjść F pod warunkiem wystąpienia podanego

Rejestr

Rejestr

yj

p

y ąp

p

g

yj

p

y ąp

p

g

w opisie strzałki stanu X.

w opisie strzałki stanu X.

X2 F2

X2 F2

X2 F2

X2 F2

X

X

X

X

X

X

S1

S1

S2

S2

X F

X F

X1 F2

X1 F2

X2 F2

X2 F2

X

X

S

S

X1

X1

X2

X2

S1

S1

S2

S2 S1

S1

S2

S2

S3

S3 S2

S2

X

X

S

S

X1

X1

X2

X2

S1

S1

F2

F2

F2

F2

S2

S2

F3

F3

F2

F2

X

X

S

S

X1

X1

X2

X2

S1

S1

S2,F2

S2,F2

S1,F2

S1,F2

S2

S2

S3 F3

S3 F3

S2 F2

S2 F2

X1 F3

X1 F3

X1 F2

X1 F2

S2

S2

S3

S3 S2

S2

S3

S3

S2

S2 S1

S1

S2

S2

F3

F3

F2

F2

S3

S3

F2

F2

F3

F3

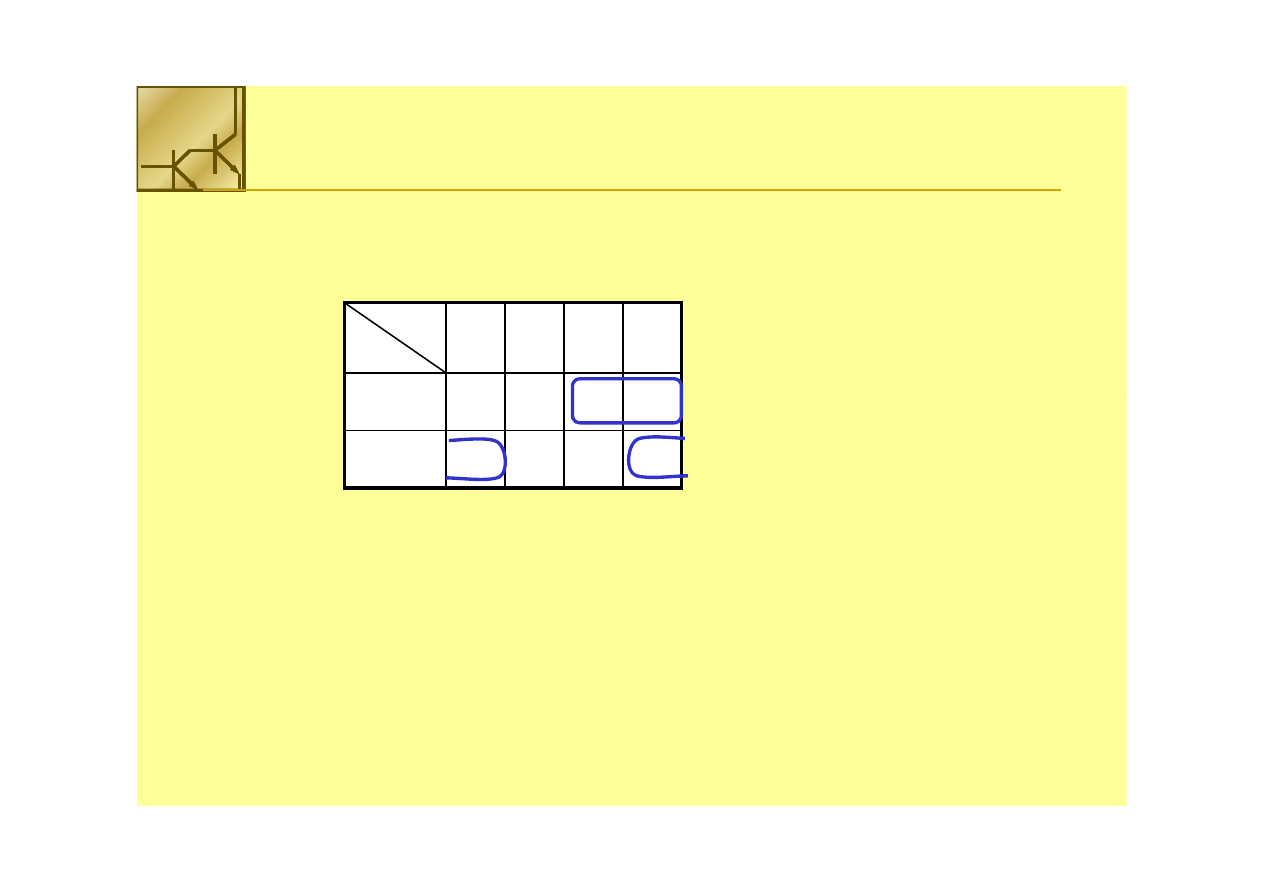

Tablica przejść

Tablica przejść

Tablica wyjść

Tablica wyjść

S2

S2

S3,F3

S3,F3

S2,F2

S2,F2

S3

S3

S2,F2

S2,F2

S1,F3

S1,F3

Tablica kompletna

Tablica kompletna

6 marca 2011

Wojciech Kucewicz

8

S3

S3

X2 F3

X2 F3

Tablica przejść

Tablica przejść

Tablica wyjść

Tablica wyjść

Tablica kompletna

Tablica kompletna

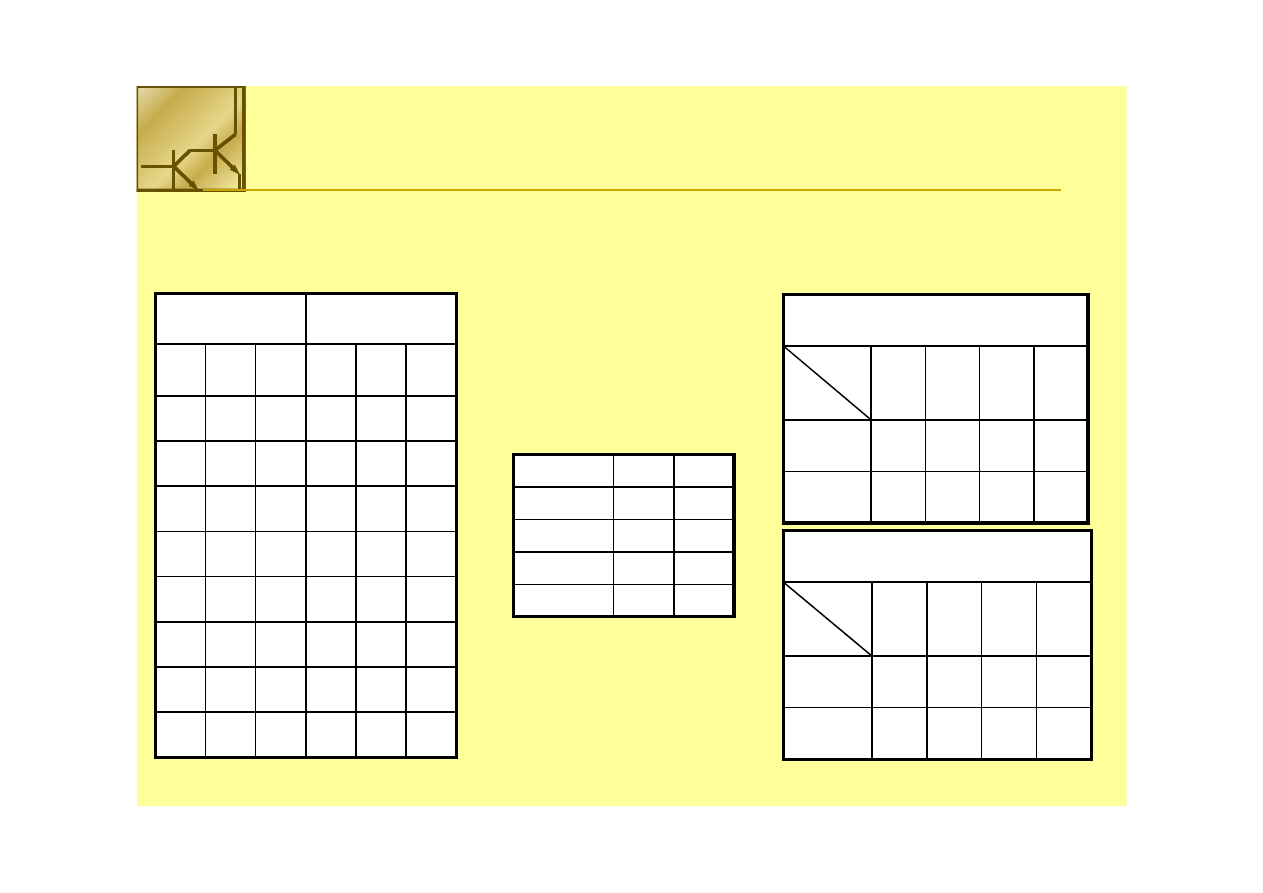

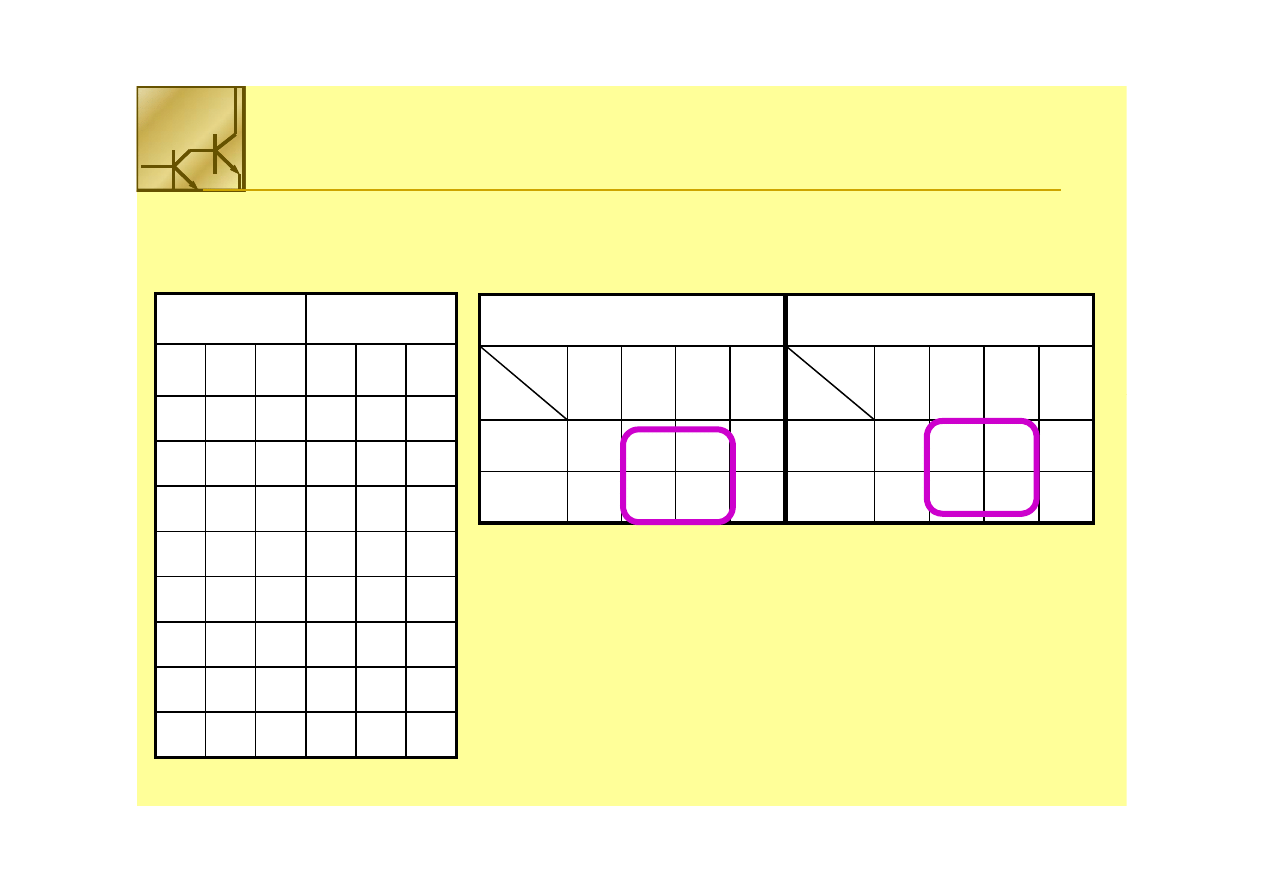

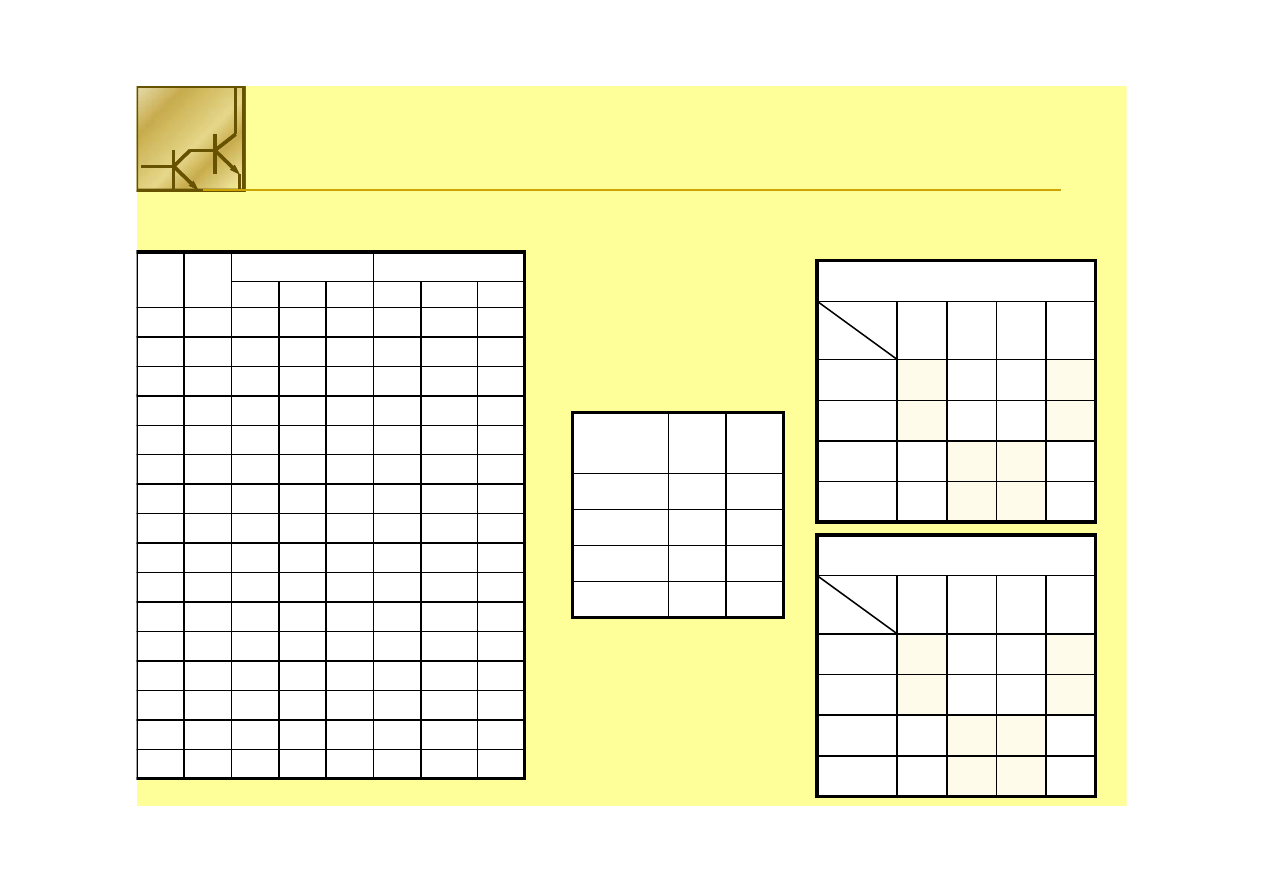

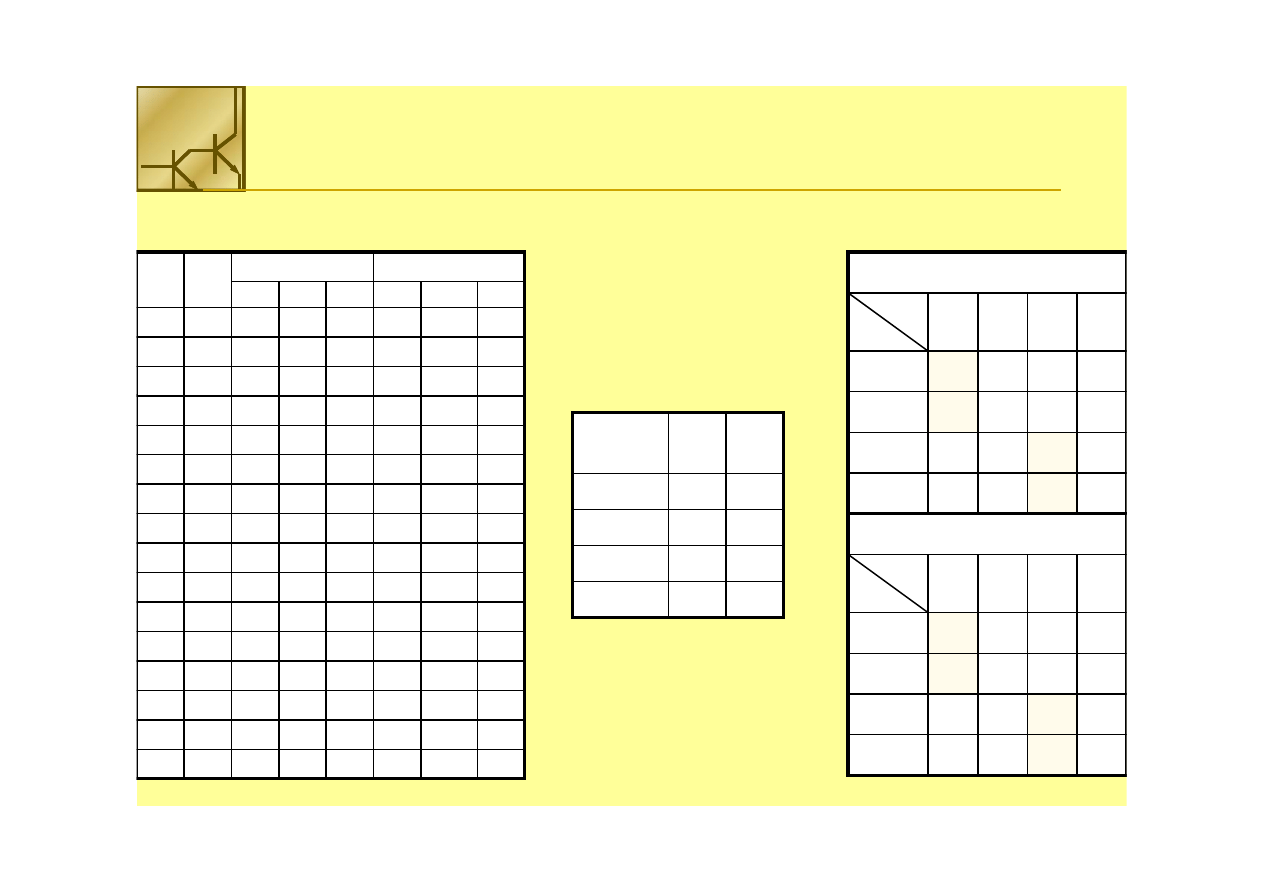

Konstrukcja grafów i tablic

Konstrukcja grafów i tablic

Konstrukcja grafów i tablic

Konstrukcja grafów i tablic

ff

Blok kombinacyjny

Blok kombinacyjny

X

X

FF

S

S

Jeśli symbolicznym

Jeśli symbolicznym elementom

elementom przyporządkuje się

przyporządkuje się

stany O1 to otrzyma się tablice przejść w postaci

stany O1 to otrzyma się tablice przejść w postaci

zakodowanej

zakodowanej

zz

uu

S

S

zakodowanej.

zakodowanej.

np. X={0,1} S {00, 01, 10} F={10, 11, 01}

np. X={0,1} S {00, 01, 10} F={10, 11, 01}

Rejestr

Rejestr

1,10

1,10

1 11

1 11

X

X

X

X

X

X

00

00

01

01

, 0

, 0

0,11

0,11

1,11

1,11

X

X

S

S

X1

X1

X2

X2

S1

S1

01

01

00

00

S2

S2

10

10

01

01

X

X

S

S

X1

X1

X2

X2

S1

S1

11

11

11

11

S2

S2

01

01

10

10

X

X

S

S

X1

X1

X2

X2

S1

S1

01,11

01,11

00,11

00,11

S2

S2

10 01

10 01

01 10

01 10

0,01

0,01

0,11

0,11

S2

S2

10

10

01

01

S3

S3

01

01

00

00

S2

S2

01

01

10

10

S3

S3

11

11

01

01

Tablica przejść

Tablica przejść

Tablica wyjść

Tablica wyjść

S2

S2

10,01

10,01

01,10

01,10

S3

S3

01,11

01,11

00,01

00,01

Tablica kompletna

Tablica kompletna

6 marca 2011

Wojciech Kucewicz

9

10

10

1,01

1,01

Tablica przejść

Tablica przejść

Tablica wyjść

Tablica wyjść

Tablica kompletna

Tablica kompletna

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

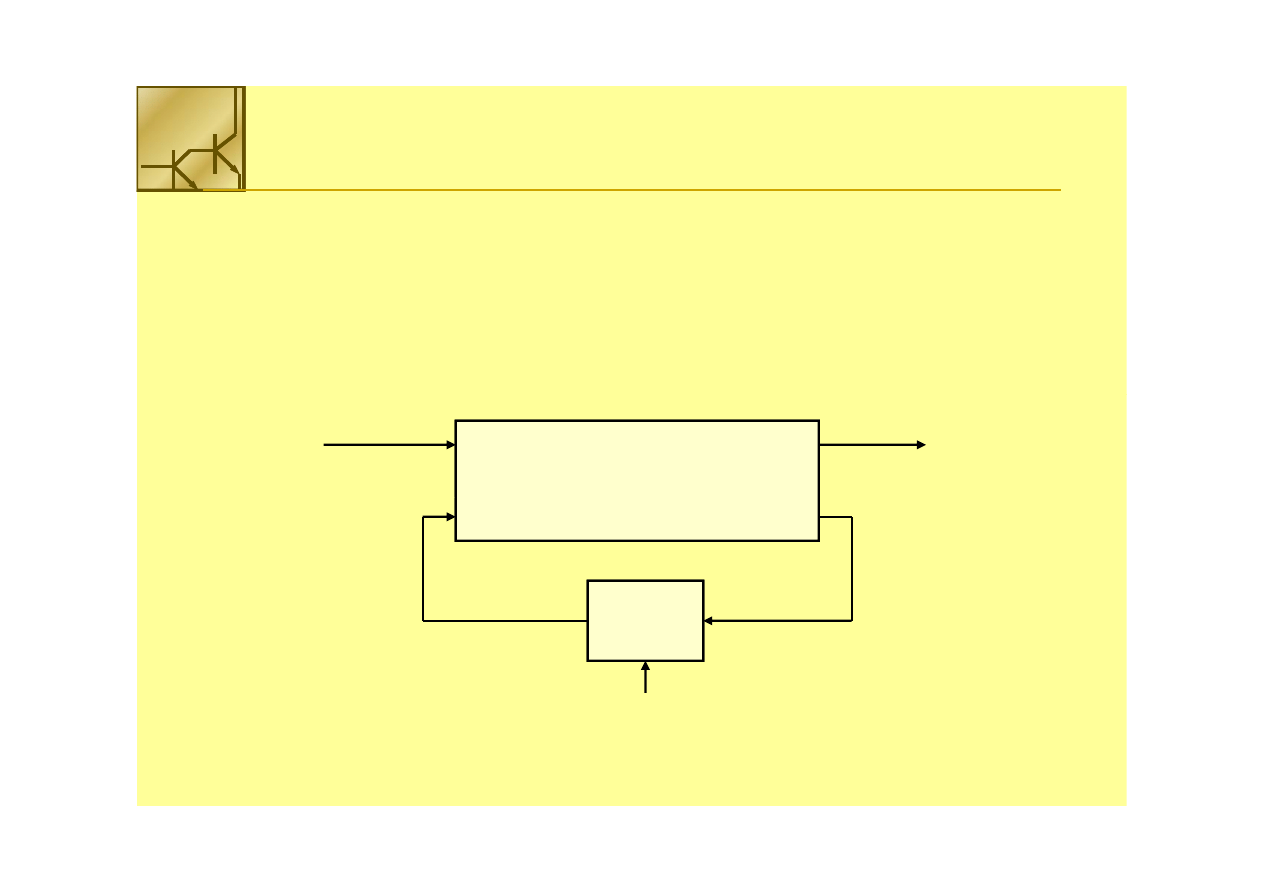

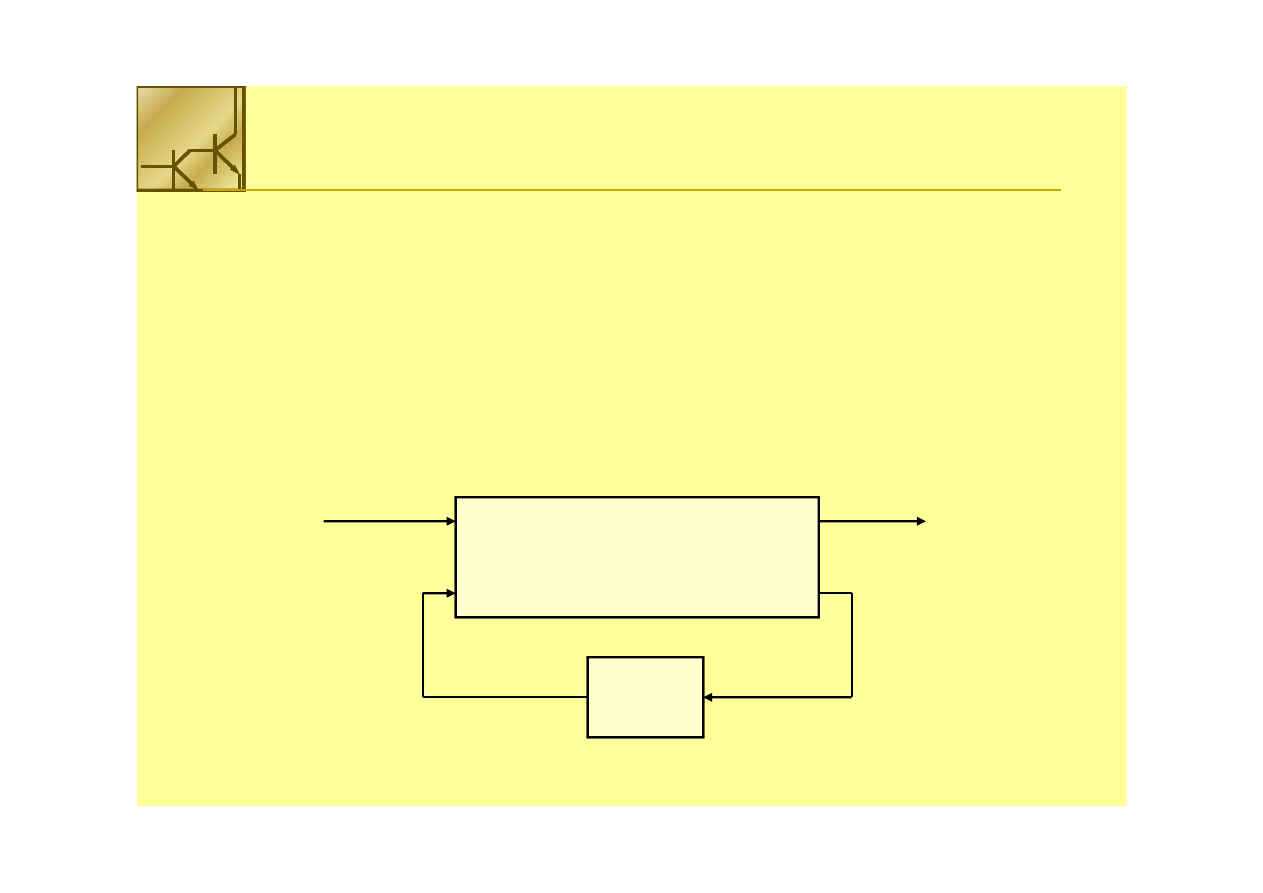

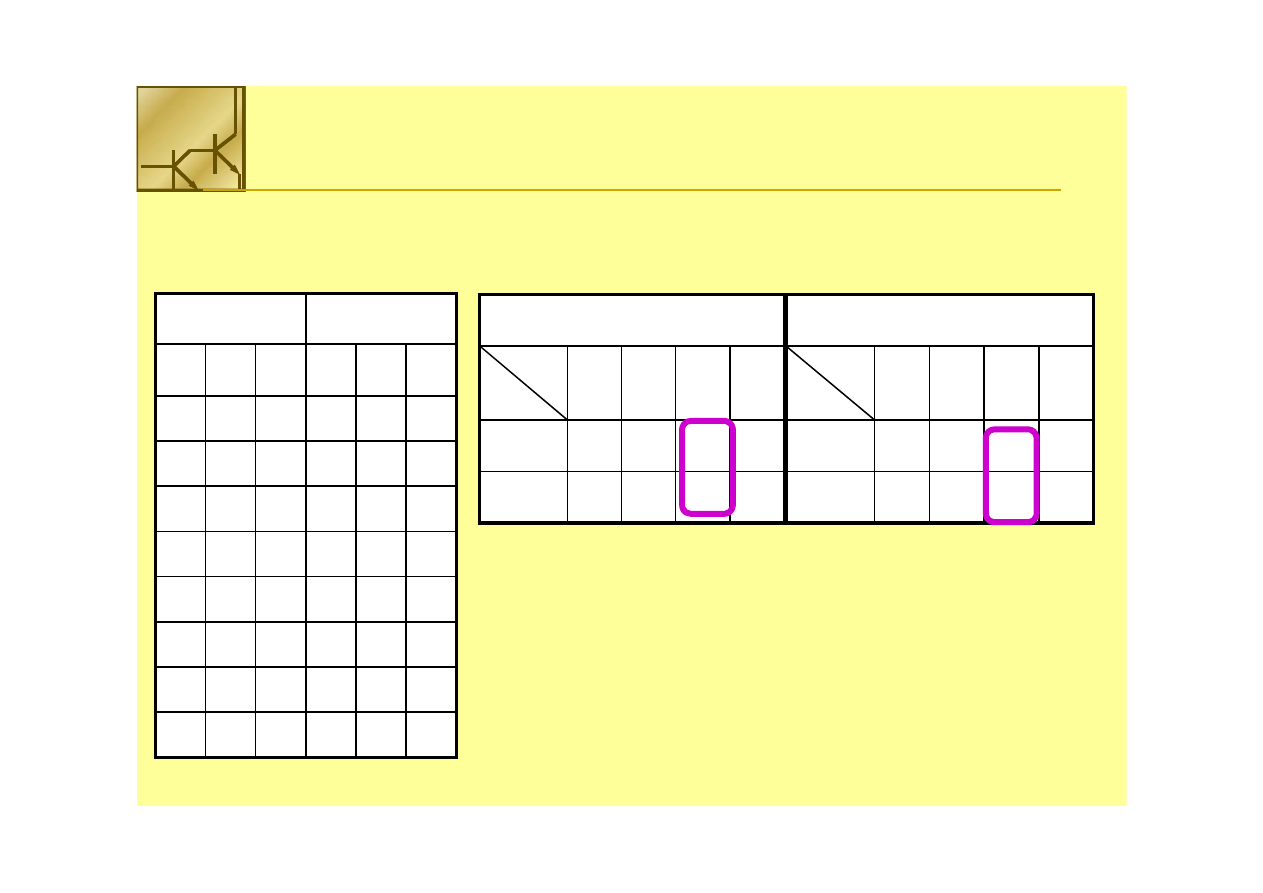

Układ sekwencyjny składa się z logicznego

układu

układu

kombinacyjnego

kombinacyjnego

i

rejestru

rejestru

, który zapamiętuje stan systemu.

Combinational

Combinational

Logic Unit

Logic Unit

Inputs

Inputs

Outputs

Outputs

Logic Unit

Logic Unit

R i

R i

Next State

Next State

Current State

Current State

Register

Register

Q D

Q D

Clock

Clock

6 marca 2011

Wojciech Kucewicz

10

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

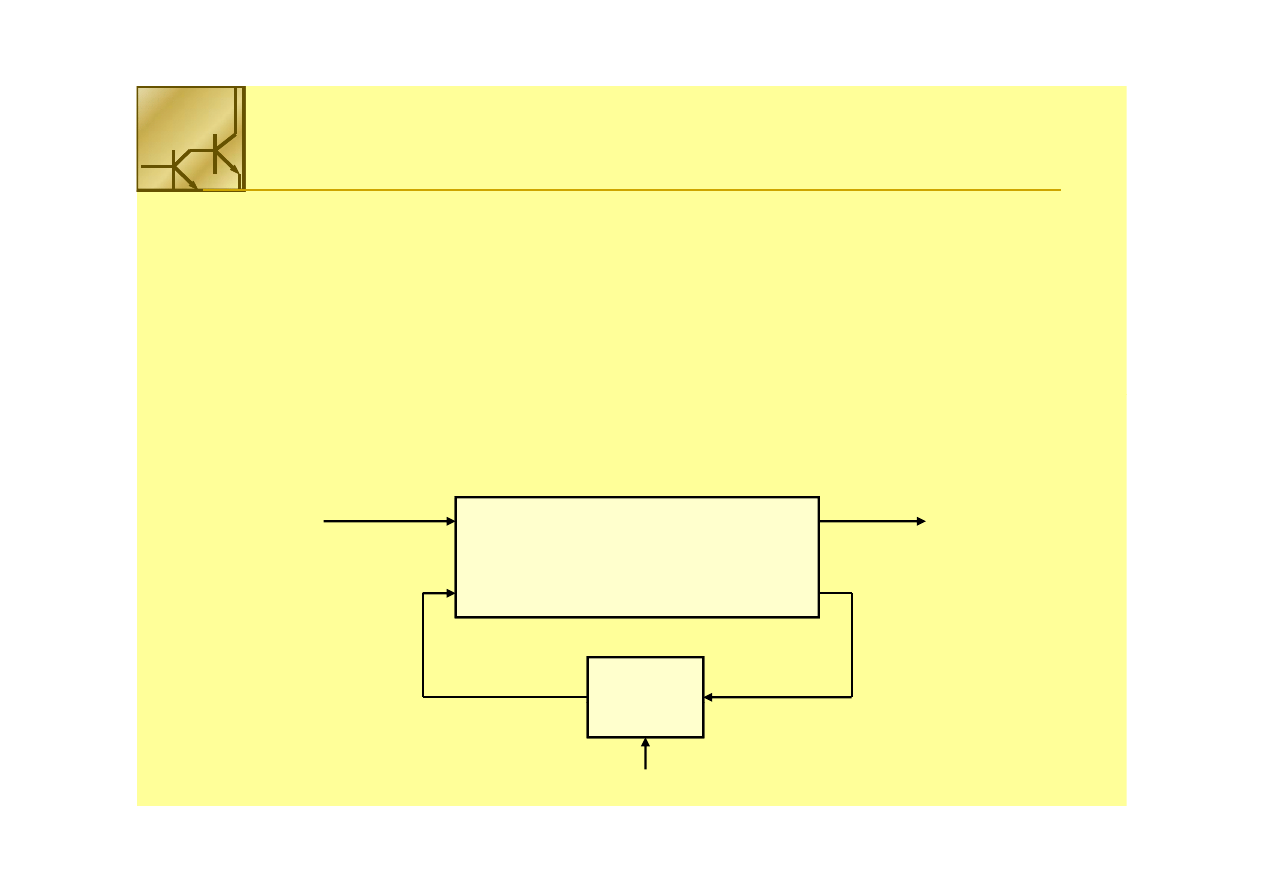

Ze względu na sposób funkcjonowania rozróżniamy:

synchroniczne

synchroniczne

układy sekwencyjne

układy sekwencyjne

, które reagują na zmianę stanu wejściowego

t lk d k t

h h il h

h k śl

h

tylko w dyskretnych chwilach czasowych, określonych przez

okresowy sygnał zewnętrzny zwany sygnałem zegarowym. Sygnał ten

doprowadzony jest do rejestru (bloku pamięciowego).

Każdy kolejny stan wewnętrzny jest wytwarzany synchronicznie z

impulsami zegarowymi.

Combinational

Combinational

Logic Unit

Logic Unit

Inputs

Inputs

Outputs

Outputs

Register

Register

Q D

Q D

Next State

Next State

Current State

Current State

6 marca 2011

Wojciech Kucewicz

11

Q D

Q D

Clock

Clock

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

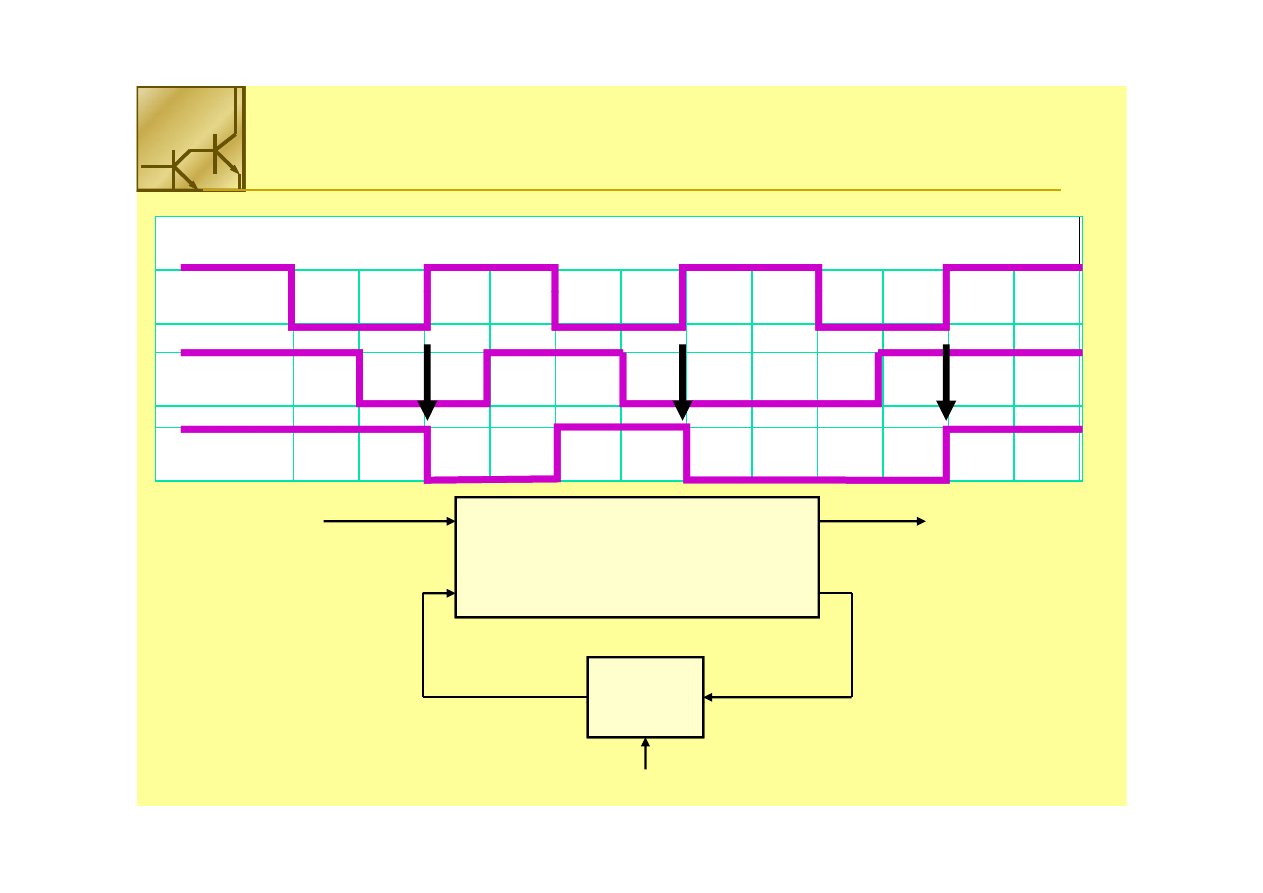

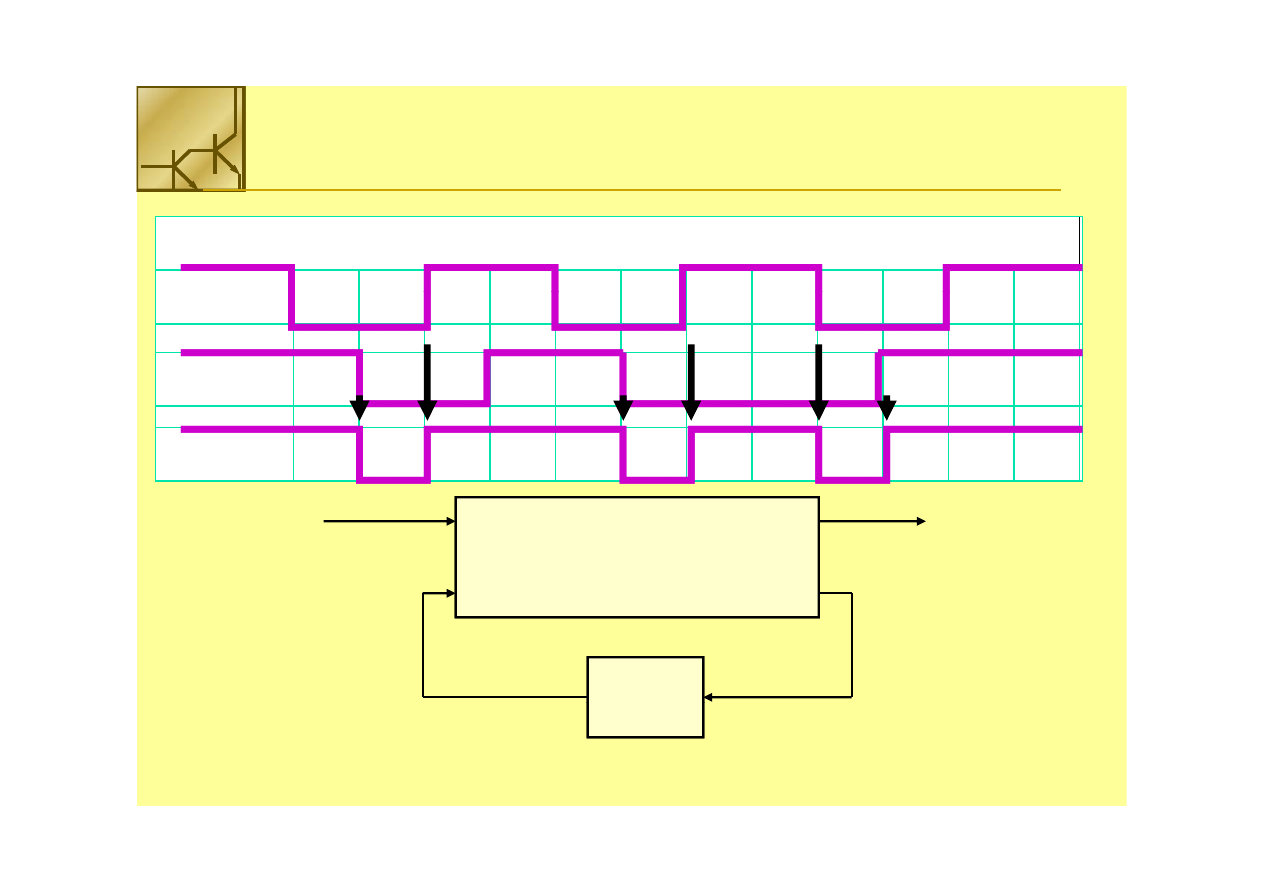

Synchroniczny układ sekwencyjny

Synchroniczny układ sekwencyjny

Cl k

Cl k

Clock

Clock

Input

Input

Output

Output

Combinational

Combinational

Logic Unit

Logic Unit

Inputs

Inputs

Outputs

Outputs

Register

Register

Q D

Q D

Next State

Next State

Current State

Current State

6 marca 2011

Wojciech Kucewicz

12

Q D

Q D

Clock

Clock

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

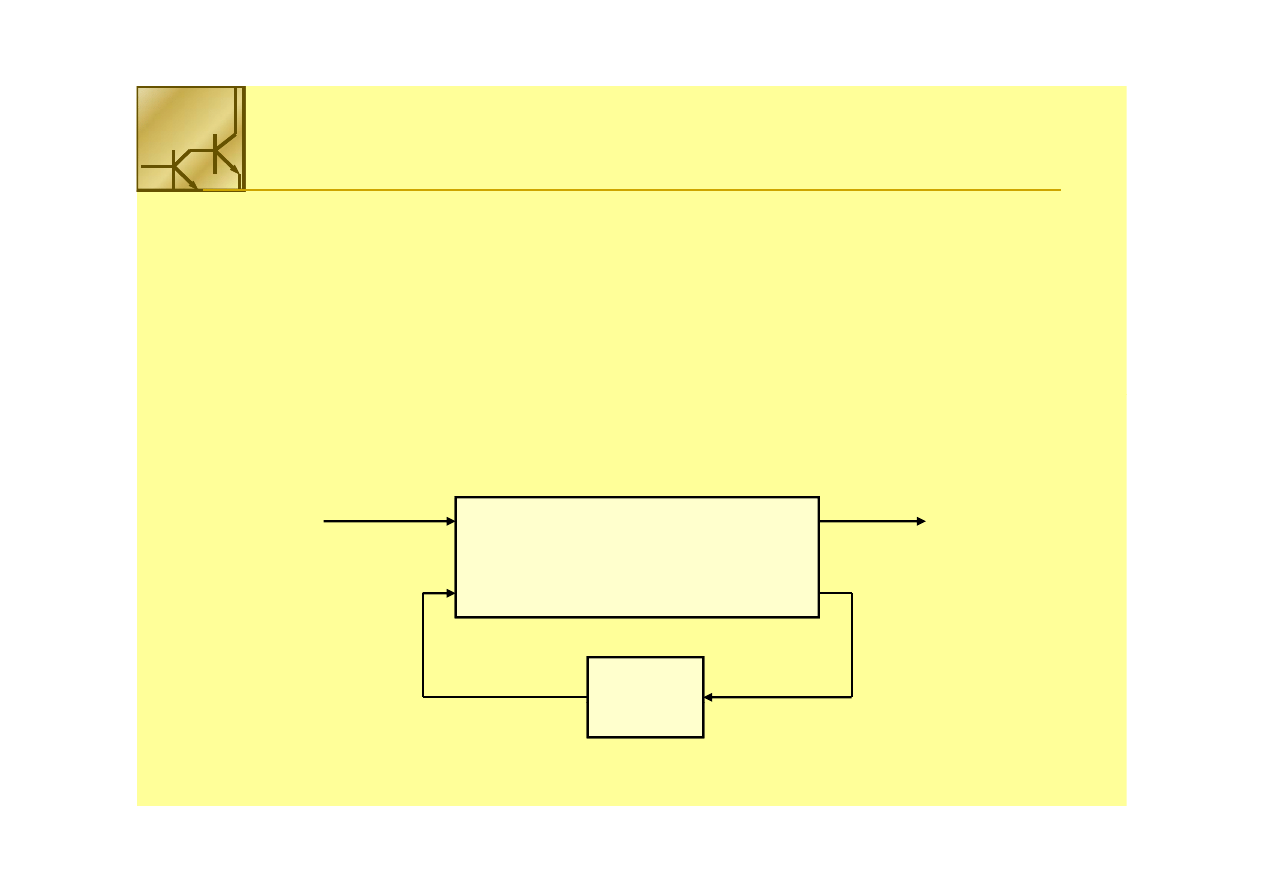

Ze względu na sposób funkcjonowania rozróżniamy:

asynchroniczne

asynchroniczne

układy sekwencyjne

układy sekwencyjne

, które reagują natychmiast na zmianę stanu

jś i

Ukł d h

i

i

j jś i

wejściowego. Układy asynchroniczne nie mają wejścia zegarowego

Combinational

Combinational

Logic Unit

Logic Unit

Inputs

Inputs

Outputs

Outputs

Register

Register

Q D

Q D

Next State

Next State

Current State

Current State

6 marca 2011

Wojciech Kucewicz

13

Q D

Q D

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Asynchroniczny układ sekwencyjny

Asynchroniczny układ sekwencyjny

I

t

I

t

Input

Input

Current

Current

Output

Output

Combinational

Combinational

Logic Unit

Logic Unit

Inputs

Inputs

Outputs

Outputs

Register

Register

Q D

Q D

Next State

Next State

Current State

Current State

6 marca 2011

Wojciech Kucewicz

14

Q D

Q D

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne

Układy sekwencyjne mogą reagować w dwojaki sposób na sygnały

wejściowe:

Jeżeli układ reaguje na poziomy sygnałów wejściowych to taki układ

określa się jako

statyczny (wyzwalany poziomem)

statyczny (wyzwalany poziomem)

.

Jeżeli układ reaguje na zmiany poziomów sygnałów wejsciowych to

taki układ nazywamy

dynamicznym (wyzwalany zboczem)

dynamicznym (wyzwalany zboczem)

.

Combinational

Combinational

Logic Unit

Logic Unit

Inputs

Inputs

Outputs

Outputs

Register

Register

Q D

Q D

Next State

Next State

Current State

Current State

6 marca 2011

Wojciech Kucewicz

15

Q D

Q D

Cyfrowe układy sekwencyjne

Cyfrowe układy sekwencyjne

Cyfrowe układy sekwencyjne

Cyfrowe układy sekwencyjne

Przerzutniki

Przerzutniki

Przerzutniki

Przerzutniki

Przerzutniki

Przerzutniki

Przerzutniki

Przerzutniki

6 marca 2011

Wojciech Kucewicz

16

Przerzutniki

Przerzutniki

Przerzutniki

Przerzutniki

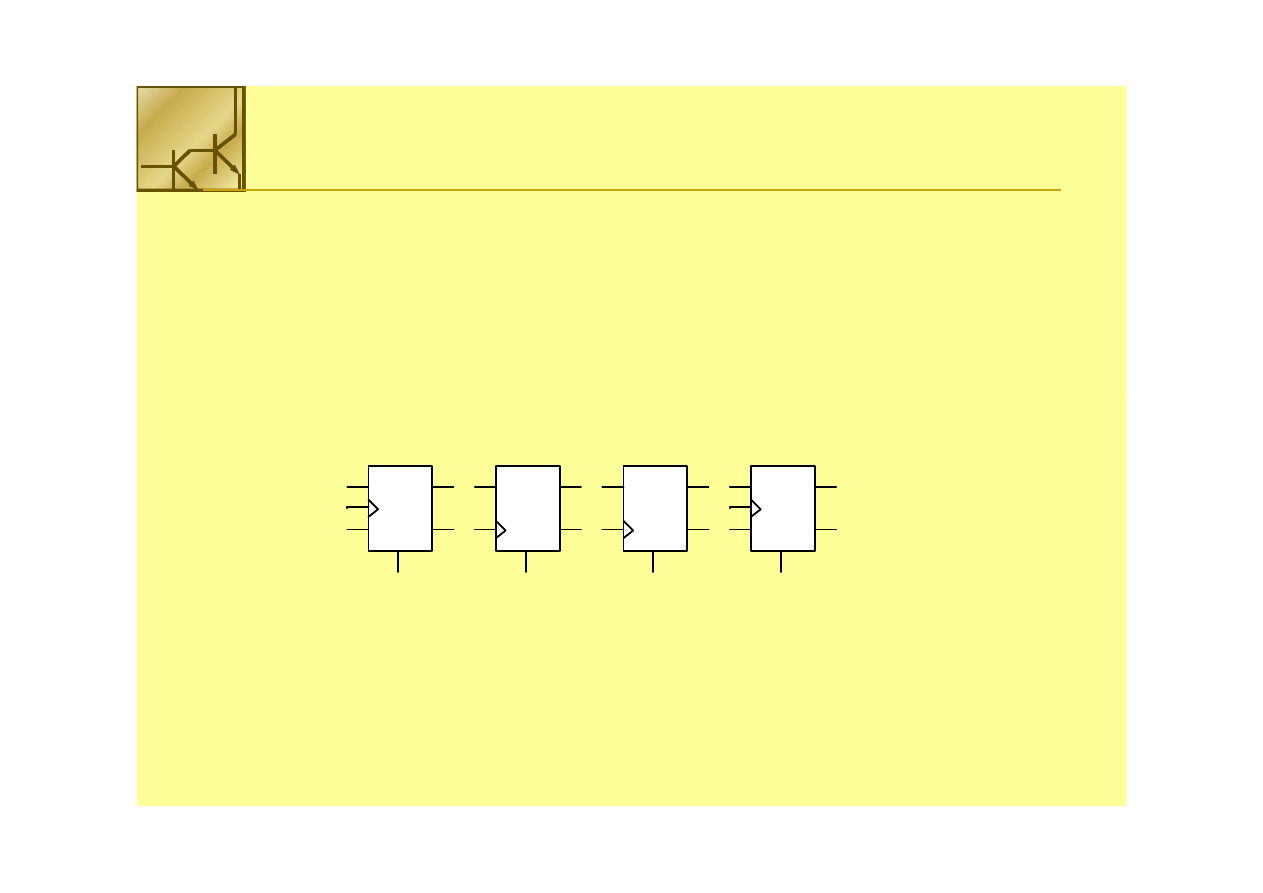

Podstawowymi układami sekwencyjnymi są przerzutniki.

Symbolem graficznym przerzutnika jest prostokąt posiadający

Symbolem graficznym przerzutnika jest prostokąt posiadający

wejścia informacyjne (np. S, R, J, K, D, T) i sterujące (CLK) oraz

wyjścia stanowiące komplementarną parę (Q i Q’).

T Q’

D Q’

R Q’

J Q’

Clk Q

Res

Clk Q

Res

S Q

Res

Clk

K Q

Res

Clk

Istnieją cztery zasadnicze typy przerzutników:

Istnieją cztery zasadnicze typy przerzutników:

SR,

SR, JK, T, D

JK, T, D

6 marca 2011

Wojciech Kucewicz

17

Definicje przerzutników opisuje norma IEC 617

Definicje przerzutników opisuje norma IEC 617 -- 12

12

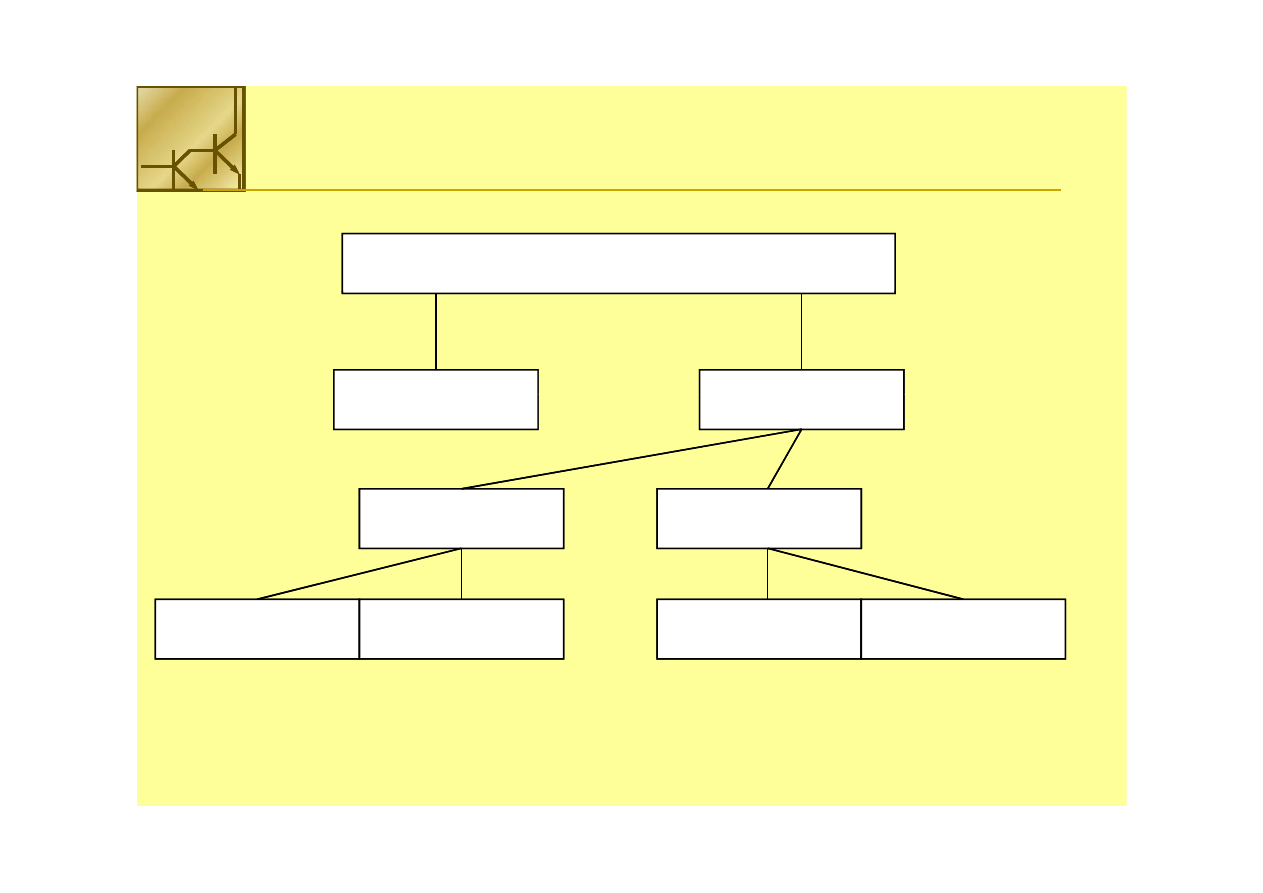

Rodzaje przerzutników

Rodzaje przerzutników

Rodzaje przerzutników

Rodzaje przerzutników

Przerzutniki

Przerzutniki

As

h

i

As

h

i

S

h

i

S

h

i

Asynchroniczne

Asynchroniczne

Synchroniczne

Synchroniczne

W

l

W

l

W

l

W

l

Wyzwalane

Wyzwalane

poziomem sygnału

poziomem sygnału

Wyzwalane

Wyzwalane

zboczem sygnału

zboczem sygnału

Wyzwalane

Wyzwalane

poz. wysokim

poz. wysokim

Wyzwalane

Wyzwalane

poz. niskim

poz. niskim

Wyzwalane

Wyzwalane

zboczem dodatn.

zboczem dodatn.

Wyzwalane

Wyzwalane

zboczem ujemn.

zboczem ujemn.

6 marca 2011

Wojciech Kucewicz

18

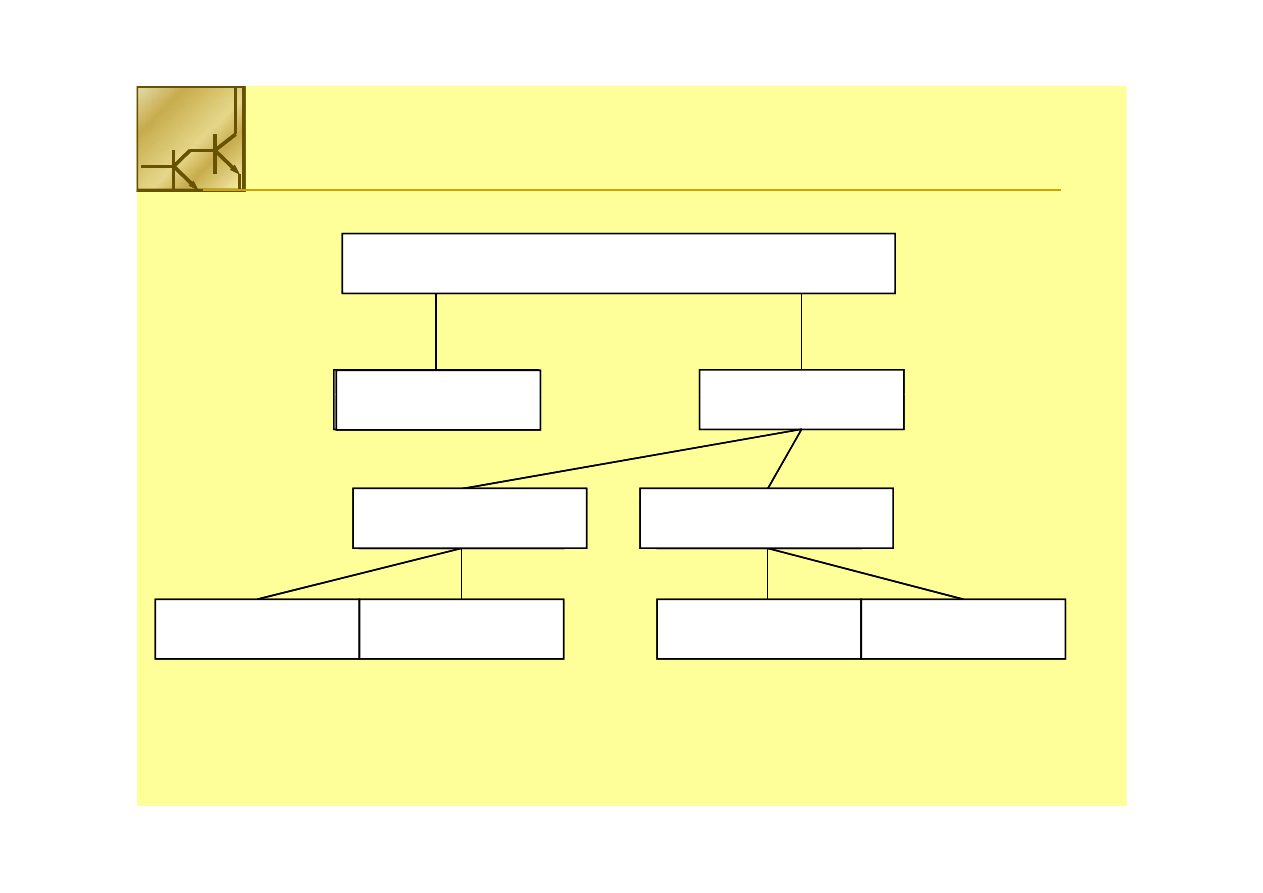

Rodzaje przerzutników

Rodzaje przerzutników

Rodzaje przerzutników

Rodzaje przerzutników

Przerzutniki

Przerzutniki

As

h

i

As

h

i

S

h

i

S

h

i

Z t

ki (SR)

Z t

ki (SR)

Asynchroniczne

Asynchroniczne

Synchroniczne

Synchroniczne

W

l

W

l

W

l

W

l

Zatrzaski (SR)

Zatrzaski (SR)

Z t

ki

Z t

ki

P

t iki

P

t iki

Wyzwalane

Wyzwalane

poziomem sygnału

poziomem sygnału

Wyzwalane

Wyzwalane

zboczem sygnału

zboczem sygnału

Zatrzaski

Zatrzaski

Bramkowane (SR, D)

Bramkowane (SR, D)

Przerzutniki

Przerzutniki

flip

flip--flop

flop(SR, D, JK, T)

(SR, D, JK, T)

Wyzwalane

Wyzwalane

poz. wysokim

poz. wysokim

Wyzwalane

Wyzwalane

poz. niskim

poz. niskim

Wyzwalane

Wyzwalane

zboczem dodatn.

zboczem dodatn.

Wyzwalane

Wyzwalane

zboczem ujemn.

zboczem ujemn.

6 marca 2011

Wojciech Kucewicz

19

Przerzutnik synchroniczny wyzwalany poziomem

Przerzutnik synchroniczny wyzwalany poziomem

wysokim

wysokim

Przerzutnik synchroniczny wyzwalany poziomem

Przerzutnik synchroniczny wyzwalany poziomem

wysokim

wysokim

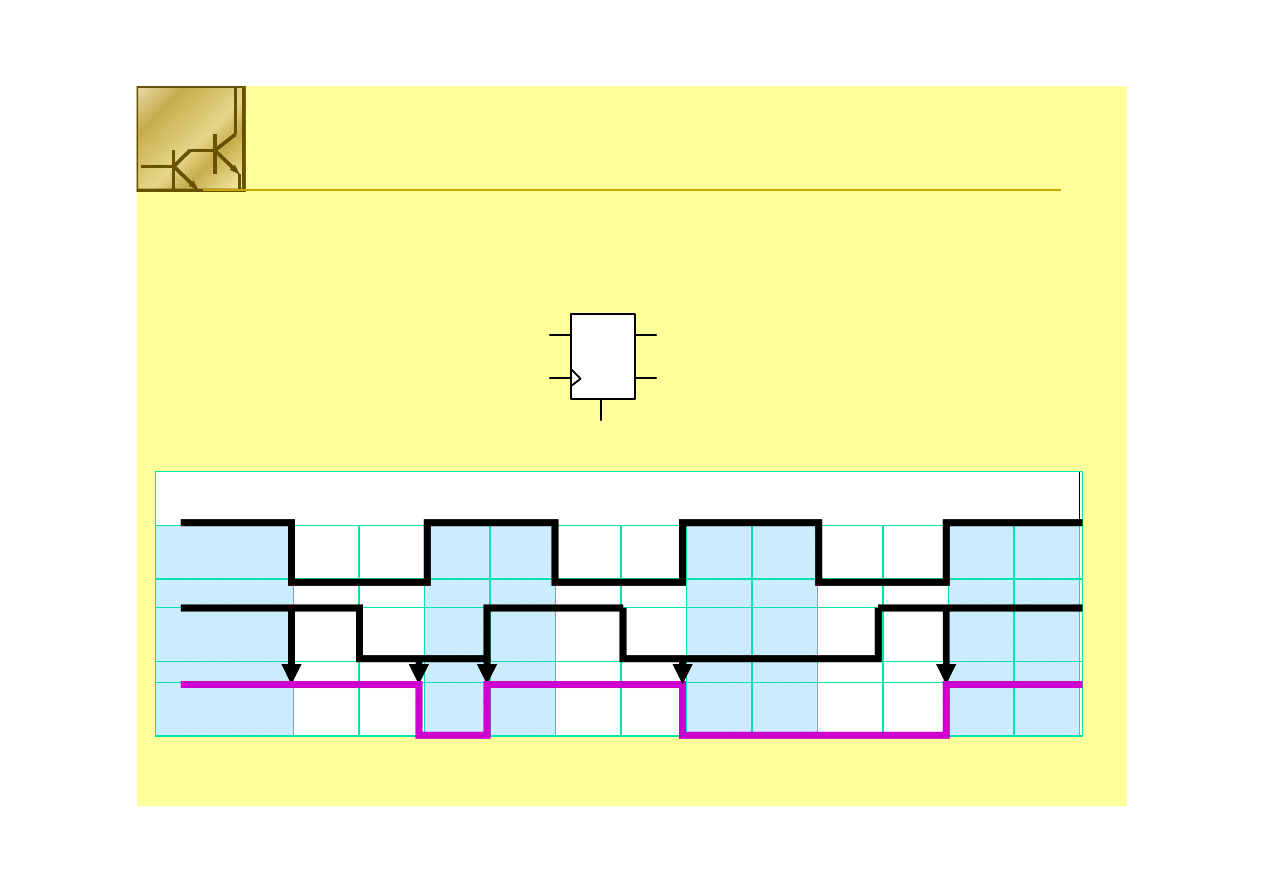

Sygnał wejściowy może zmieniać stan wyjścia tylko przy wysokim poziomie sygnału

Sygnał wejściowy może zmieniać stan wyjścia tylko przy wysokim poziomie sygnału

zegarowego (transparent

zegarowego (transparent mode

mode). Przy niskim poziomie sygnału zegarowego stan

). Przy niskim poziomie sygnału zegarowego stan

wyjścia pozostaje bez zmian (

wyjścia pozostaje bez zmian (hold

hold mode

mode))

yj

p

j

(

yj

p

j

(

))

D Q’

Clk Q

Res

Przerzutnik synchroniczny wyzwalany poziomem wysokim

Przerzutnik synchroniczny wyzwalany poziomem wysokim

Przerzutnik synchroniczny wyzwalany poziomem wysokim

Przerzutnik synchroniczny wyzwalany poziomem wysokim

Clock

Clock

D

D

Q

Q

6 marca 2011

Wojciech Kucewicz

20

Q

Q

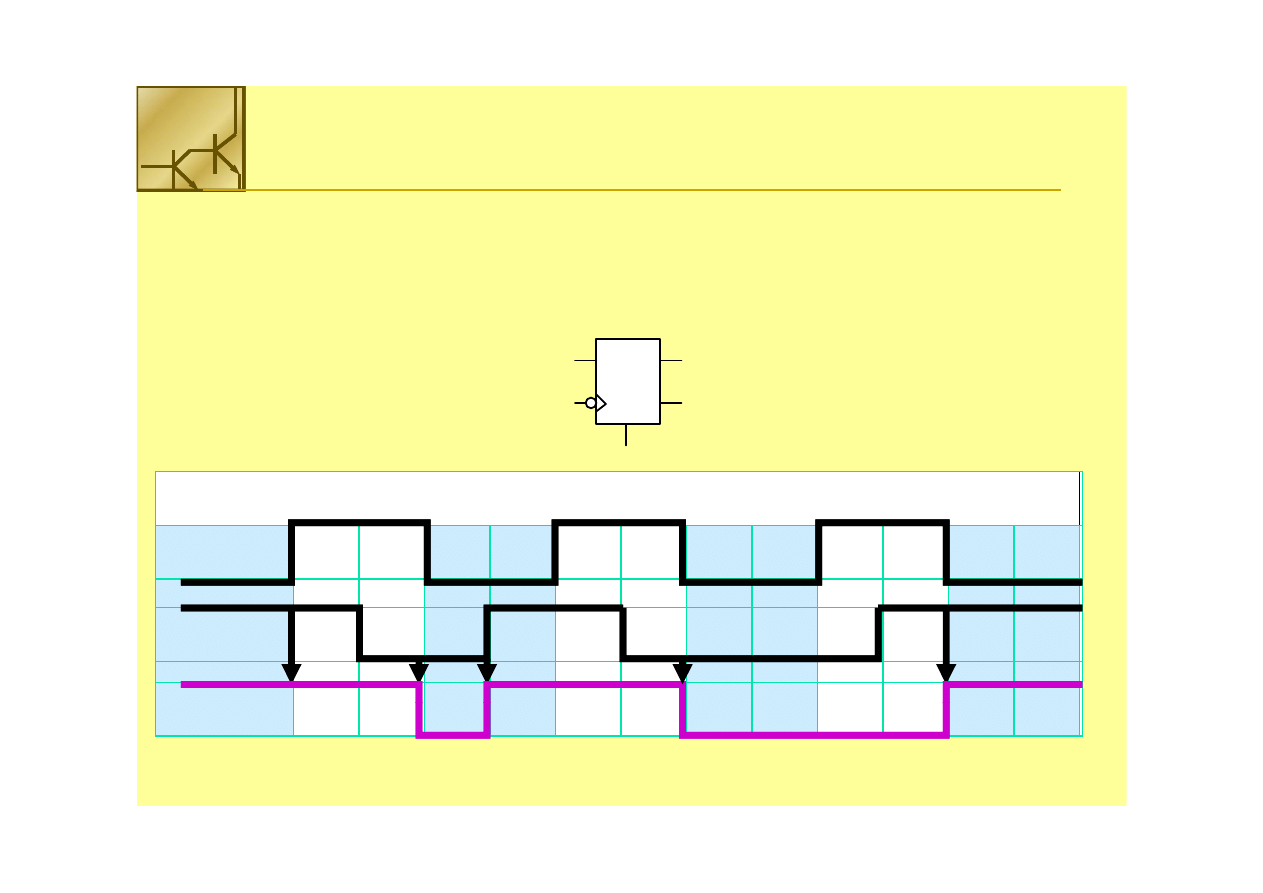

Przerzutnik synchroniczny wyzwalany poziomem

Przerzutnik synchroniczny wyzwalany poziomem

niskim

niskim

Przerzutnik synchroniczny wyzwalany poziomem

Przerzutnik synchroniczny wyzwalany poziomem

niskim

niskim

Sygnał wejściowy może zmieniać stan wyjścia tylko przy niskim poziomie sygnału

Sygnał wejściowy może zmieniać stan wyjścia tylko przy niskim poziomie sygnału

zegarowego (transparent

zegarowego (transparent mode

mode). Przy wysokim poziomie sygnału zegarowego stan

). Przy wysokim poziomie sygnału zegarowego stan

wyjścia pozostaje bez zmian (

wyjścia pozostaje bez zmian (hold

hold mode

mode))

wyjśc a pozostaje bez zm an (

wyjśc a pozostaje bez zm an (hold

hold mode

mode))

D Q’

Clk Q

Przerzutnik synchroniczny wyzwalany poziomem niskim

Przerzutnik synchroniczny wyzwalany poziomem niskim

Clk Q

Res

Przerzutnik synchroniczny wyzwalany poziomem niskim

Przerzutnik synchroniczny wyzwalany poziomem niskim

Clock

Clock

D

D

O t t

O t t

6 marca 2011

Wojciech Kucewicz

21

Output

Output

Przerzutnik synchroniczny wyzwalany

Przerzutnik synchroniczny wyzwalany

zboczem dodatnim sygnału zegarowego

zboczem dodatnim sygnału zegarowego

Przerzutnik synchroniczny wyzwalany

Przerzutnik synchroniczny wyzwalany

zboczem dodatnim sygnału zegarowego

zboczem dodatnim sygnału zegarowego

Sygnał wejściowy może zmieniać stan wyjścia tylko przy przejściu sygnału zegarowego

Sygnał wejściowy może zmieniać stan wyjścia tylko przy przejściu sygnału zegarowego

ze stanu 0 do 1.

ze stanu 0 do 1.

M st

M st

Sl

Sl

Master

Master

Slave

Slave

Przerzutnik synchroniczny wyzwalany zboczem dodatnim

Przerzutnik synchroniczny wyzwalany zboczem dodatnim

Clock

Clock

Clock

Clock

D

D

6 marca 2011

Wojciech Kucewicz

22

Output

Output

Przerzutnik synchroniczny wyzwalany

Przerzutnik synchroniczny wyzwalany

zboczem ujemnym sygnału zegarowego

zboczem ujemnym sygnału zegarowego

Przerzutnik synchroniczny wyzwalany

Przerzutnik synchroniczny wyzwalany

zboczem ujemnym sygnału zegarowego

zboczem ujemnym sygnału zegarowego

Sygnał wejściowy może zmieniać stan wyjścia tylko przy przejściu sygnału zegarowego

Sygnał wejściowy może zmieniać stan wyjścia tylko przy przejściu sygnału zegarowego

ze stanu 1 do 0.

ze stanu 1 do 0.

M st

M st

Sl

Sl

Master

Master

Slave

Slave

Przerzutnik synchroniczny wyzwalany zboczem ujemnym

Przerzutnik synchroniczny wyzwalany zboczem ujemnym

Clock

Clock

Clock

Clock

D

D

6 marca 2011

Wojciech Kucewicz

23

Output

Output

P

P

P

P

Parametry

Parametry

Parametry

Parametry

yy

t ikó

t ikó

yy

t ikó

t ikó

przerzutników

przerzutników

przerzutników

przerzutników

6 marca 2011

Wojciech Kucewicz

24

Parametry przerzutników

Parametry przerzutników

Parametry przerzutników

Parametry przerzutników

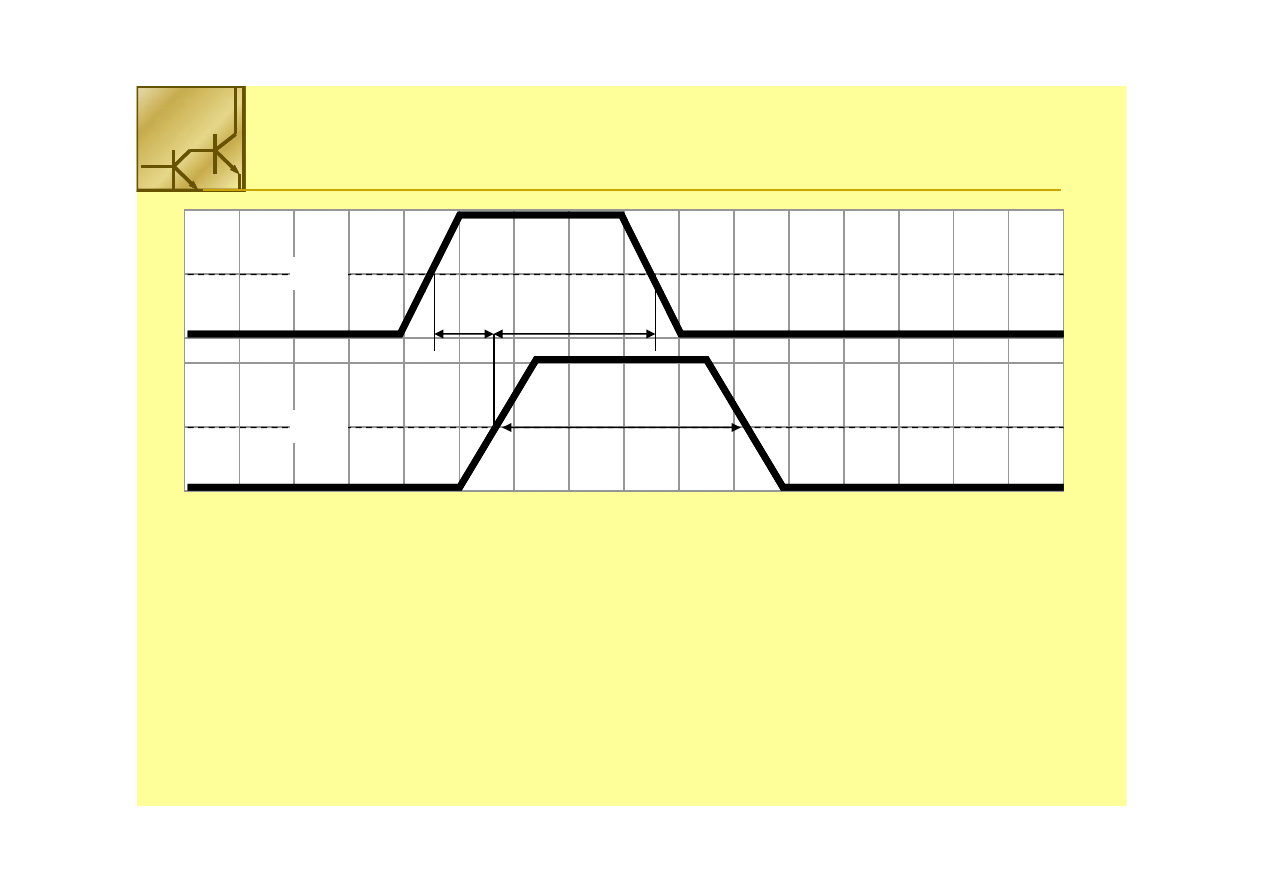

Zmiana stanu przerzutnika następuje zawsze z pewnym opóźnieniem

Zmiana stanu przerzutnika następuje zawsze z pewnym opóźnieniem

względem chwili osiągnięcia wartości progowej napięcia przez zbocze impulsu

względem chwili osiągnięcia wartości progowej napięcia przez zbocze impulsu

inicjującego zmianę stanu

inicjującego zmianę stanu

inicjującego zmianę stanu.

inicjującego zmianę stanu.

Dlatego

Dlatego definiuje się parametry dynamiczne przerzutnika:

definiuje się parametry dynamiczne przerzutnika:

•• czas propagacji sygnałów od wejścia zegarowego do wyjść Q i

czas propagacji sygnałów od wejścia zegarowego do wyjść Q i

nQ

nQ,,

•• czasy propagacji sygnałów od wejść asynchronicznych do wyjść

czasy propagacji sygnałów od wejść asynchronicznych do wyjść

Q i

Q i nQ

nQ,,

•• czas ustalania

czas ustalania tt

ss

(setup time)

(setup time)

•• czas przetrzymywania

czas przetrzymywania tt

hh

((hold

hold time)

time)

i i l i

k śl

h

łó

i i l i

k śl

h

łó

•• minimalny czas trwania określonych sygnałów

minimalny czas trwania określonych sygnałów tt

w

w

•• maksymalna częstotliwość przebiegu synchronizującego

maksymalna częstotliwość przebiegu synchronizującego

6 marca 2011

Wojciech Kucewicz

25

Parametry przerzutników

Parametry przerzutników

Parametry przerzutników

Parametry przerzutników

D

D

50%

50%

Clk

Clk

tt

ss

tt

hh

l

l

l

k ó

ś

ć

l

k ó

ś

ć

50%

50%

tt

w

w

Czas ustalania

Czas ustalania tt

ss

jest to minimalny czas , w którym sygnał wejściowy musi być obecny

jest to minimalny czas , w którym sygnał wejściowy musi być obecny

na wejściach informacyjnych (synchronizowanych) przerzutnika przed nadejściem

na wejściach informacyjnych (synchronizowanych) przerzutnika przed nadejściem

wyzwalającego zbocza impulsu

wyzwalającego zbocza impulsu

Czas przetrzymywania

Czas przetrzymywania tt

hh

jest to minimalny czas, w którym sygnał wejściowy musi

jest to minimalny czas, w którym sygnał wejściowy musi

pozostać na wejściu informacyjnym po wystąpieniu wyzwalającego zbocza sygnału

pozostać na wejściu informacyjnym po wystąpieniu wyzwalającego zbocza sygnału

zegara

zegara

6 marca 2011

Wojciech Kucewicz

26

Minimalny czas trwania sygnału

Minimalny czas trwania sygnału tt

w

w

jest to czas, w którym sygnał nie zmienia swego

jest to czas, w którym sygnał nie zmienia swego

stanu

stanu

Zatrzask

Zatrzask

Zatrzask

Zatrzask

Zatrzask

Zatrzask

Zatrzask

Zatrzask

SR

SR

SR

SR

SR

SR

SR

SR

6 marca 2011

Wojciech Kucewicz

27

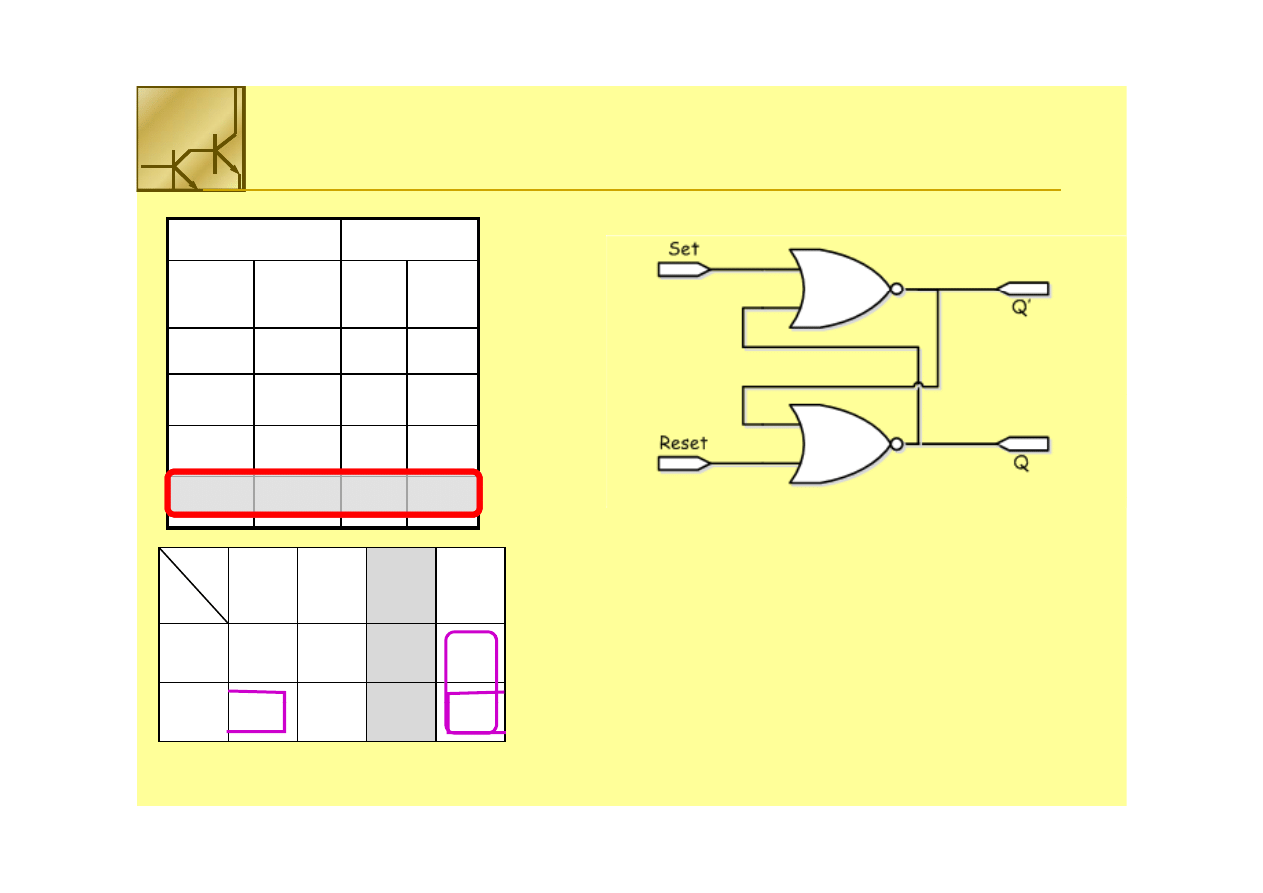

Zatrzask SR

Zatrzask SR

Zatrzask SR

Zatrzask SR

RR

S

S

Q

Q

nnQ

Q

00

00

11

00

00

11

Q

Q

nQ

nQ

11

11

11

00

Not

Not used

used

Not

Not used

used

00

11

00

00

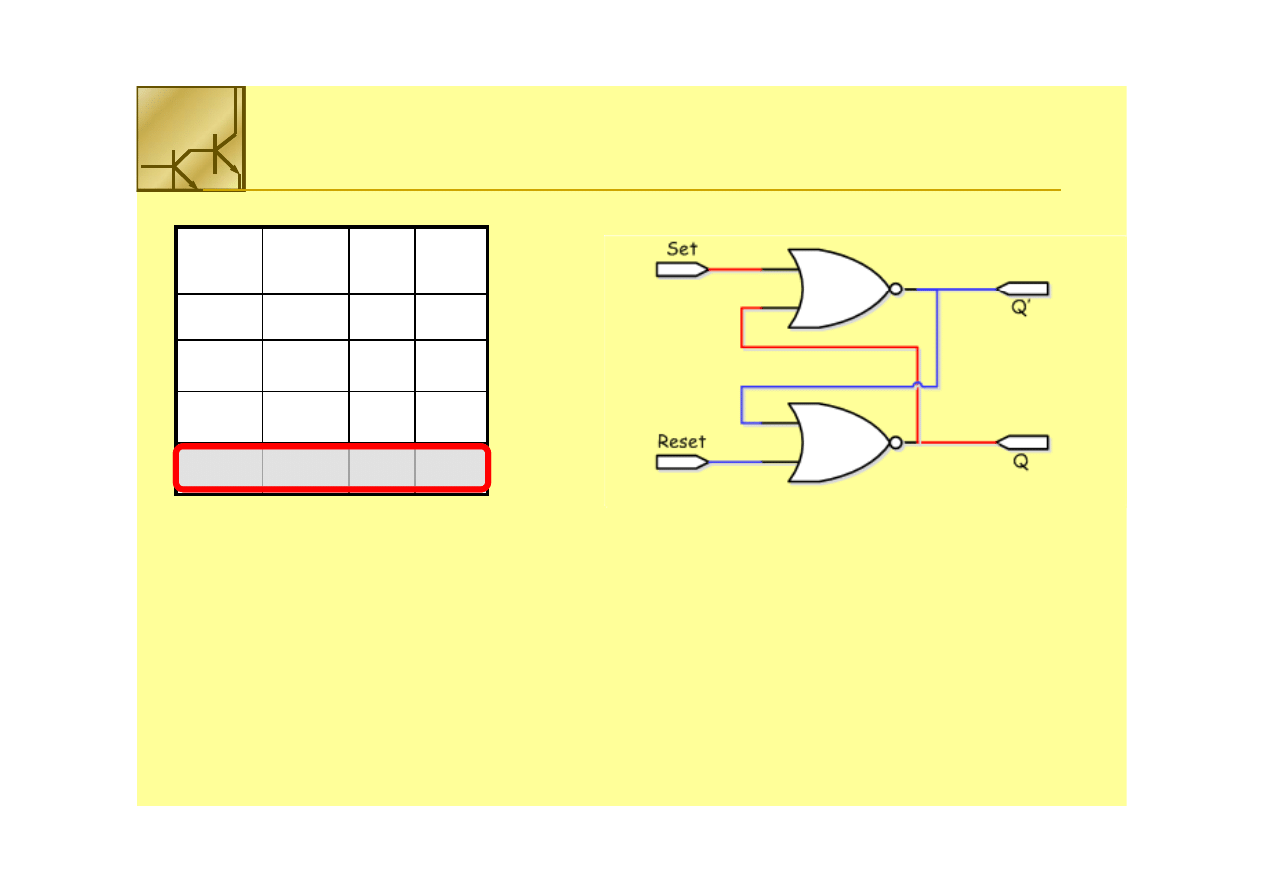

Zatrzask SR

Zatrzask SR ma dwa wejścia: S (set

ma dwa wejścia: S (set--ustawianie), R (reset

ustawianie), R (reset-- zerowanie).

zerowanie).

Gdy wejście S = 0 i R = 1 wówczas na wyjściu Q jest stan 0

Gdy wejście S = 0 i R = 1 wówczas na wyjściu Q jest stan 0

Gdy wejście S = 1 i R = 0 wówczas na wyjściu Q jest stan 1

Gdy wejście S = 1 i R = 0 wówczas na wyjściu Q jest stan 1

Gdy wejście S = 0 i R = 0 wówczas na wyjściu Q utrzymany jest stan poprzedni

Gdy wejście S = 0 i R = 0 wówczas na wyjściu Q utrzymany jest stan poprzedni

6 marca 2011

Wojciech Kucewicz

28

y

j

yj

Q

y

y j

p p

y

j

yj

Q

y

y j

p p

Stany logiczne S = 1 i R = 1 są zabronione ze względu na sprzeczność w opisie wyjść

Stany logiczne S = 1 i R = 1 są zabronione ze względu na sprzeczność w opisie wyjść

Zatrzask SR

Zatrzask SR

Zatrzask SR

Zatrzask SR

RR

S

S

Q

Q

nnQ

Q

00

00

11

00

00

11

Q

Q

nQ

nQ

11

11

11

00

Not

Not used

used

Not

Not used

used

00

11

00

00

Zatrzask SR

Zatrzask SR

RR

S

S

Q

Q

Not used

Not used

6 marca 2011

Wojciech Kucewicz

29

Q

Q

Not used

Not used

Stan wysoki wyjścia Q jest utrzymywany do zresetowania przerzutnika

Zatrzask SR

Zatrzask SR

Zatrzask SR

Zatrzask SR

tt

t+

t+ττ

RR

S

S

Q

Q

++

nnQ

Q

++

RR

S

S

Q

Q

++

nnQ

Q

++

00

00

11

00

00

11

Q

Q

nQ

nQ

11

11

11

00

11

00

Not

Not used

used

Not

Not used

used

00

11

00

00

00

11

11

11

Not

Not used

used

Not

Not used

used

00

00

SR

Q

00

01

11

10

Î

Î

Q

Q

+

+

= SR’ +

= SR’ + R’Q

R’Q =R’(S + Q)

=R’(S + Q)

Q

00

0

0

0

1

11

1

0

0

1

Q

Q

++

= S + QR’

= S + QR’

Przy założeniu, że SR=0 Î Q

+

= R’S + RS + R’Q

6 marca 2011

Wojciech Kucewicz

30

11

1

0

0

1

Q

Q

++

= S + QR

= S + QR

Zastosowanie zatrzasku SR

Zastosowanie zatrzasku SR

Zastosowanie zatrzasku SR

Zastosowanie zatrzasku SR

RR

S

S

Q

Q

nnQ

Q

00

11

11

00

11

00

00

11

n

Clock

Generator sygnałów zegarowych do rejestru przesuwnego

Generator sygnałów zegarowych do rejestru przesuwnego

Clock

Clock

nnΦ

Φ

6 marca 2011

Wojciech Kucewicz

31

nnΦ

Φ

Φ

Φ

Zatrzask SR

Zatrzask SR

Zatrzask SR

Zatrzask SR

RR

S

S

Q

Q

nnQ

Q

00

00

11

00

00

11

Q

Q

nQ

nQ

11

11

11

00

Not

Not used

used

Not

Not used

used

00

11

00

00

Przerzutnik

Przerzutnik SR

SR ma dwa wejścia: S (set

ma dwa wejścia: S (set--ustawianie), R (reset

ustawianie), R (reset-- zerowanie).

zerowanie).

Gdy wejście S = 0 i R = 1 wówczas na wyjściu Q jest stan 0

Gdy wejście S = 0 i R = 1 wówczas na wyjściu Q jest stan 0

Gdy wejście S = 1 i R = 0 wówczas na wyjściu Q jest stan 1

Gdy wejście S = 1 i R = 0 wówczas na wyjściu Q jest stan 1

6 marca 2011

Wojciech Kucewicz

32

Gdy wejście S = 0 i R = 0 wówczas na wyjściu Q utrzymany jest stan poprzedni

Gdy wejście S = 0 i R = 0 wówczas na wyjściu Q utrzymany jest stan poprzedni

Gdy wejście S = 1 i R = 0 wówczas na wyjściu Q jest stan 1

Gdy wejście S = 1 i R = 0 wówczas na wyjściu Q jest stan 1

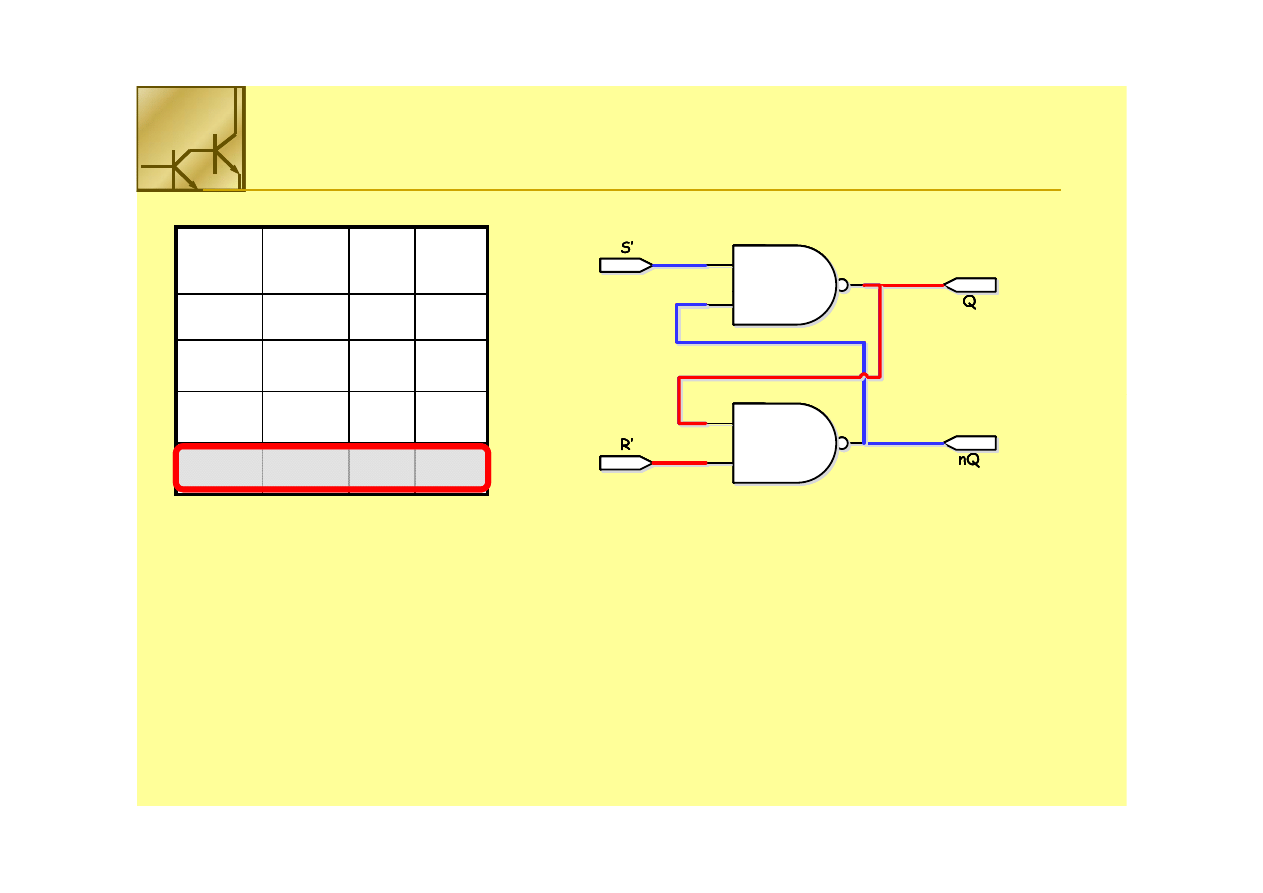

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

S

S’

Q

Clock

nQ

R

R’

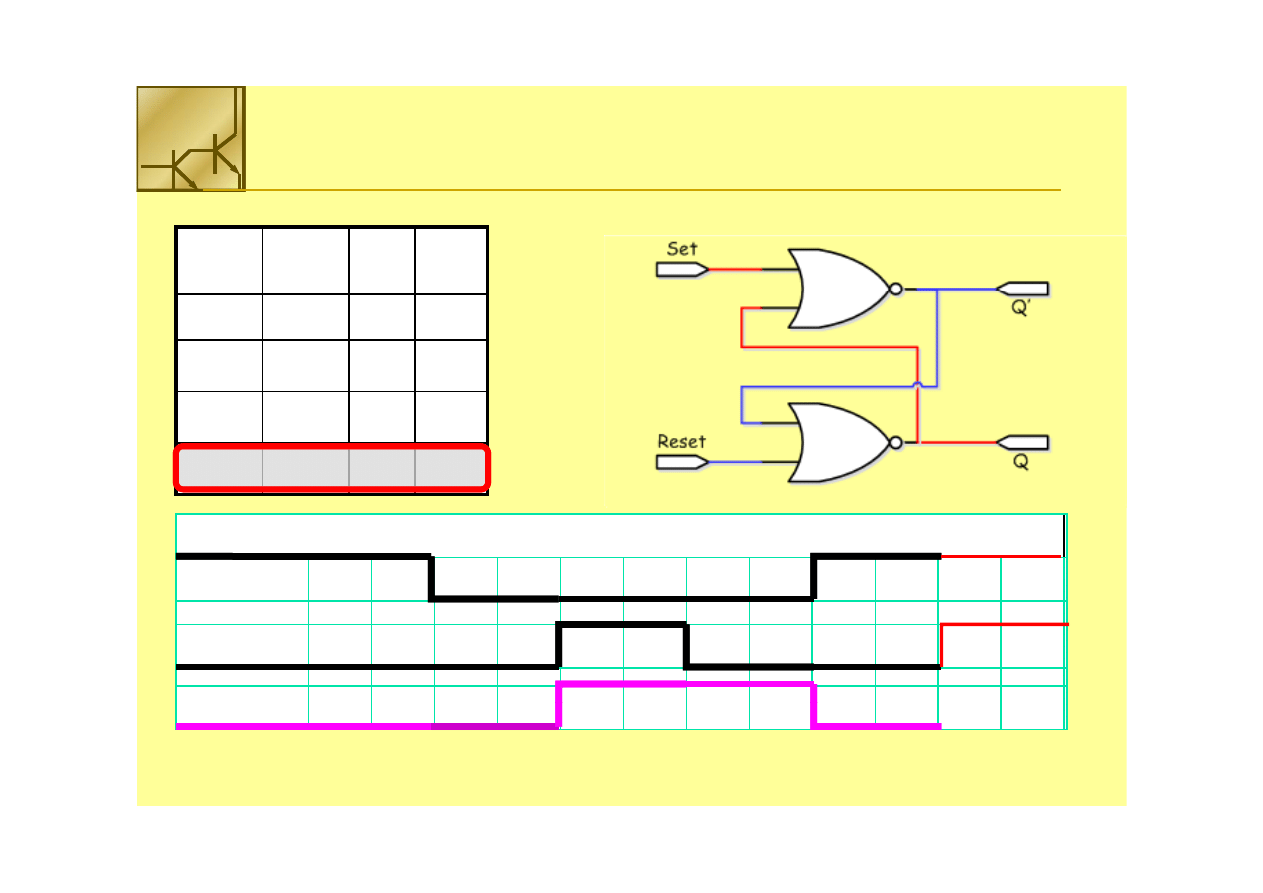

Dla synchronizacji przełączania przerzutnika stosuje się dodatkowe wejście

Dla synchronizacji przełączania przerzutnika stosuje się dodatkowe wejście

synchronizujące (

synchronizujące (Clock

Clock).

).

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

przerzutnika S’ i R’ są w stanie 1, czyli wyjścia Q i

przerzutnika S’ i R’ są w stanie 1, czyli wyjścia Q i nQ

nQ nie zmieniają stanu.

nie zmieniają stanu.

Jeżeli sygnał zegarowy jest w stanie 1 to stany wejść R i S są na wejściach

Jeżeli sygnał zegarowy jest w stanie 1 to stany wejść R i S są na wejściach

6 marca 2011

Wojciech Kucewicz

33

yg

g

y j

y

j

j

yg

g

y j

y

j

j

przerzutnika S’ i R’ zaprzeczone

przerzutnika S’ i R’ zaprzeczone -- przerzutnik może zmieniać stany wyjść Q i

przerzutnik może zmieniać stany wyjść Q i nQ

nQ

Stan R = S = 1 jest zabroniony.

Stan R = S = 1 jest zabroniony.

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

S

Clock

Q

Q

S Q

R Q’

R

nQ

Dla synchronizacji przełączania przerzutnika stosuje się dodatkowe wejście

Dla synchronizacji przełączania przerzutnika stosuje się dodatkowe wejście

synchronizujące (

synchronizujące (Clock

Clock).

).

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

Jeżeli sygnał zegarowy jest w stanie 0 to bez względu na stan wejść R i S oba wejścia

przerzutnika S’ i R’ są w stanie 1, czyli wyjścia Q i

przerzutnika S’ i R’ są w stanie 1, czyli wyjścia Q i nQ

nQ nie zmieniają stanu.

nie zmieniają stanu.

Jeżeli sygnał zegarowy jest w stanie 1 to stany wejść R i S są na wejściach

Jeżeli sygnał zegarowy jest w stanie 1 to stany wejść R i S są na wejściach

6 marca 2011

Wojciech Kucewicz

34

yg

g

y j

y

j

j

yg

g

y j

y

j

j

przerzutnika S’ i R’ zaprzeczone

przerzutnika S’ i R’ zaprzeczone -- przerzutnik może zmieniać stany wyjść Q i

przerzutnik może zmieniać stany wyjść Q i nQ

nQ

Stan R = S = 1 jest zabroniony.

Stan R = S = 1 jest zabroniony.

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

CLK

CLK

RR

S

S

Q

Q

nnQ

Q

00

xx

xx

Q

Q

nQ

nQ

Q

S

Q

S

Q

S

Q

S

Q

S

Q

Q

Q

Q

11

00

00

Q

Q

nQ

nQ

11

00

11

11

00

Clock

Clock

Clock

Clock

Clock

11

11

00

00

11

11

11

11

11

11

nQ

R

nQ

R

nQ

R

nQ

R

nQ

R

Przerzutnik SR

Przerzutnik SR

Clock

Clock

RR

S

S

6 marca 2011

Wojciech Kucewicz

35

S

S

Q

Q

Not used

Not used

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

Zatrzask SR

Zatrzask SR bramkowany

bramkowany

CLK

CLK

RR

S

S

Q

Q

nnQ

Q

00

xx

xx

Q

Q

nQ

nQ

Cl k

S

S Q

S

Q

Q

Q

Q

Q

11

00

00

Q

Q

nQ

nQ

11

00

11

11

00

Clock

R

nQ

Q

S Q

R Q’

Clock

R

Q

S Q

R Q’

Clk

11

11

00

00

11

11

11

11

11

11

R

R

nQ

R Q’

SR

QC

00

01

11

10

00

00

0

0

0

0

Î

Î

Q

Q

+

+

= C(S + QR’) +

= C(S + QR’) +C’Q

C’Q

00

00

0

0

0

0

01

01

0

0

1

1

11

11

1

0

1

1

6 marca 2011

Wojciech Kucewicz

36

11

11

1

0

1

1

10

10

1

1

1

1

SR

SR Clocked Latch

Clocked Latch

SR

SR Clocked Latch

Clocked Latch

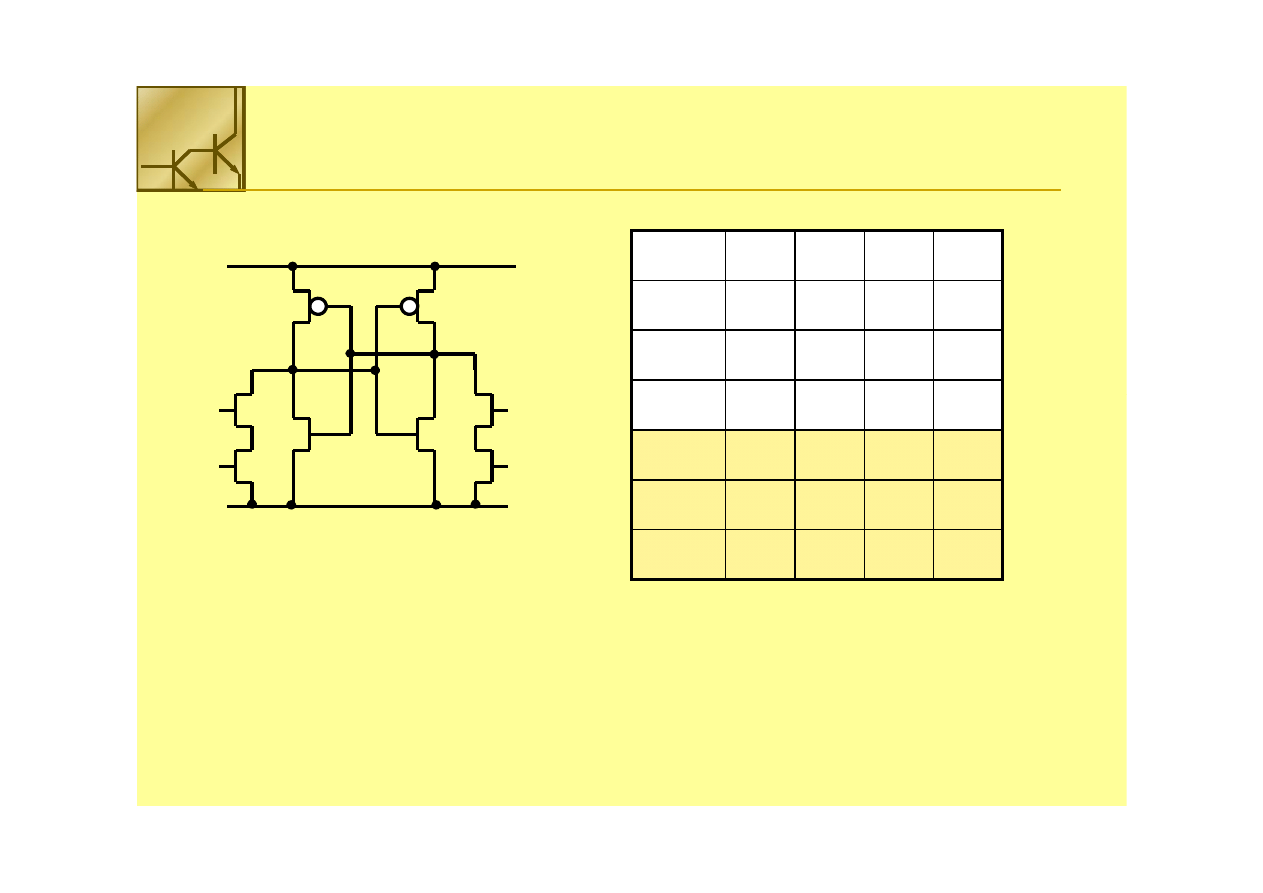

VV

DD

DD

CLK

CLK

RR

S

S

Q

Q

nQ

nQ

11

00

11

11

00

Q

notQ

11

00

11

11

00

11

11

00

00

11

11

00

00

Q

Q

nQ

nQ

M2

M2

M4

M4

S

et

R

eset

CLK

CLK

11

00

00

Q

Q

nQ

nQ

00

00

11

Q

Q

nQ

nQ

00

11

00

Q

Q

nQ

nQ

M1

M1

M3

M3

M5

M5

M6

M6

M8

M8

M7

M7

VV

SS

SS

00

11

00

Q

Q

nQ

nQ

00

00

00

Q

Q

nQ

nQ

Only 8 transistors

Only 8 transistors

The output can only change state while the CLK input is a logic 1.

The output can only change state while the CLK input is a logic 1.

6 marca 2011

Wojciech Kucewicz

37

When CLK is a logic 0, the S and R inputs will have no effect.

When CLK is a logic 0, the S and R inputs will have no effect.

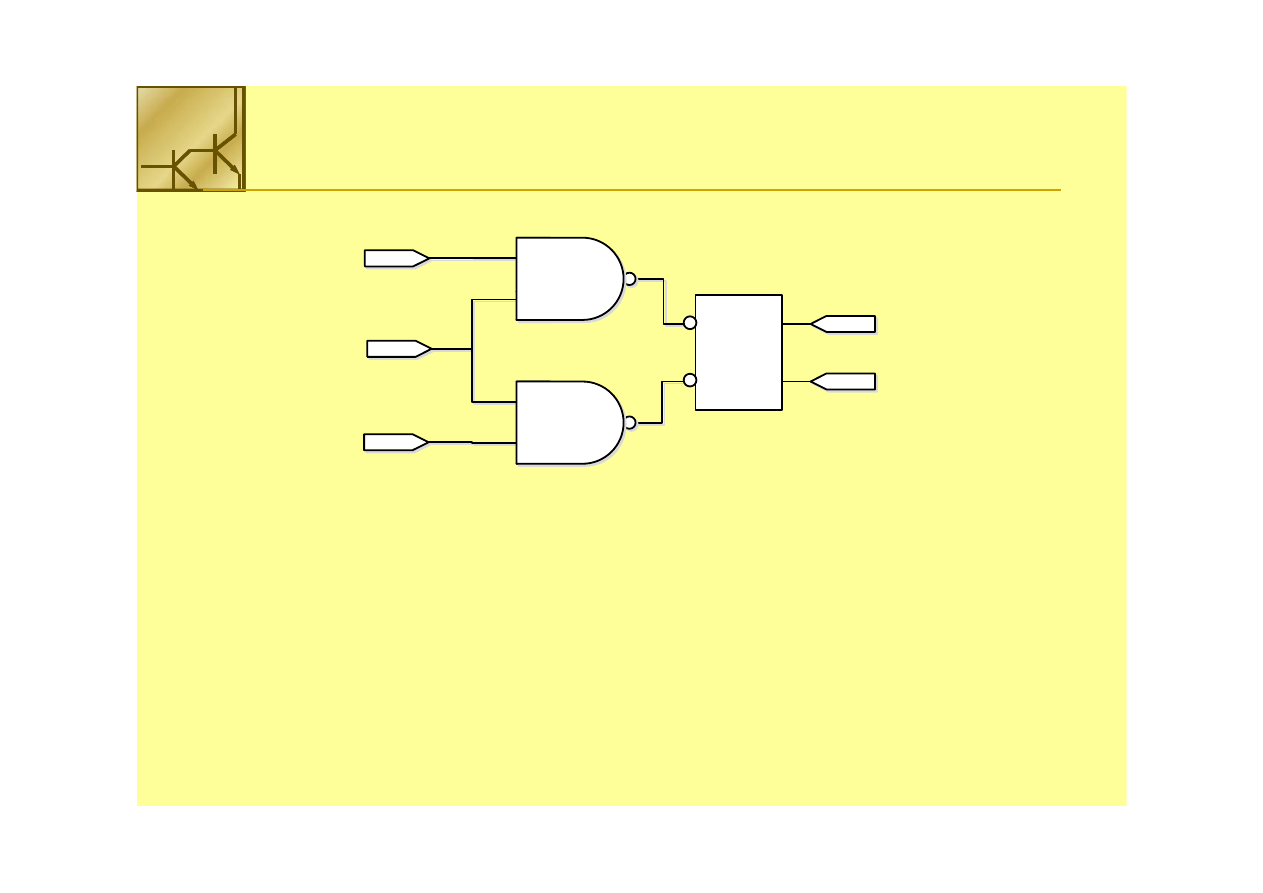

Przerzutnik SR wyzwalany zboczem

Przerzutnik SR wyzwalany zboczem

opadającym

opadającym

Przerzutnik SR wyzwalany zboczem

Przerzutnik SR wyzwalany zboczem

opadającym

opadającym

Slave

Slave

Master

Master

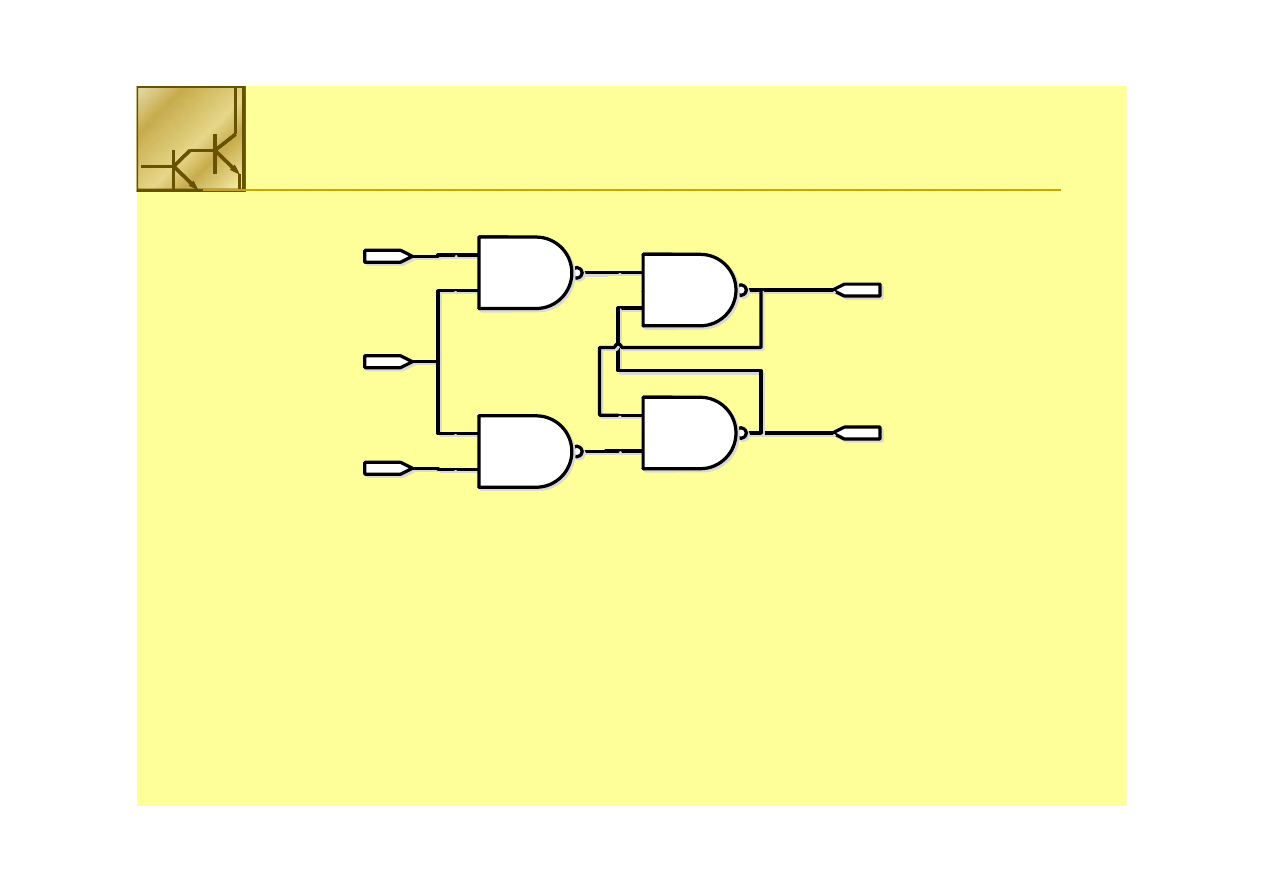

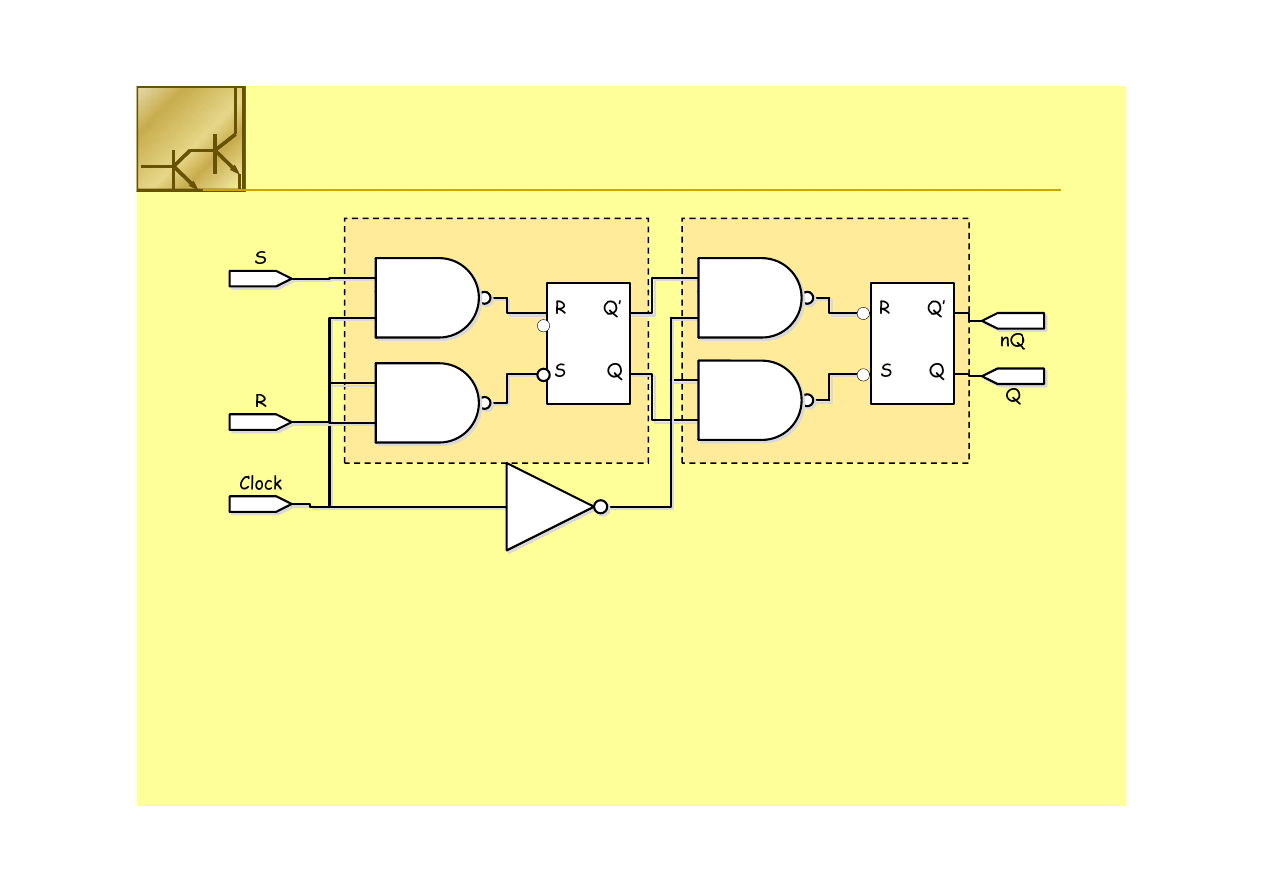

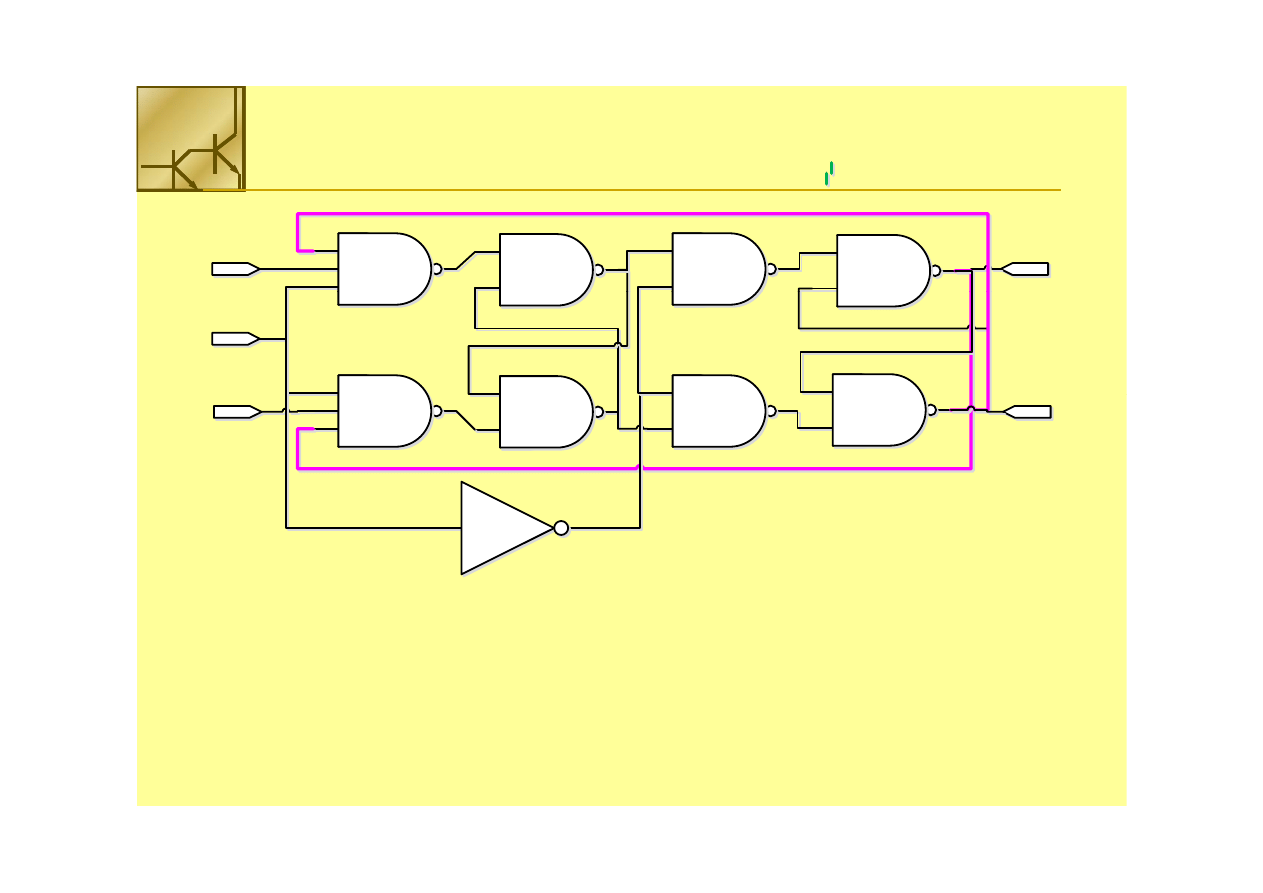

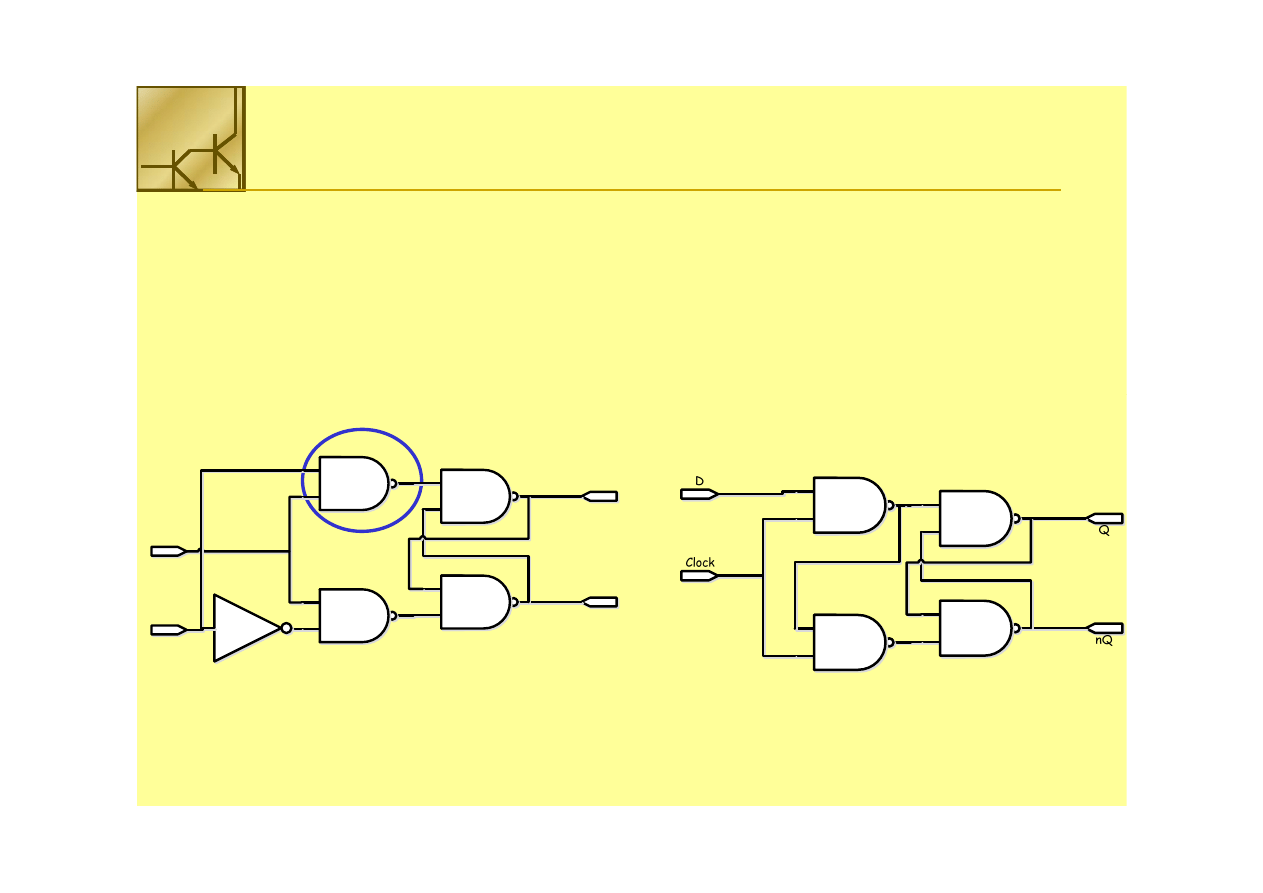

Przerzutnik SR flip-flop zbudowany jest z dwóch bramkowanych zatrzasków SR,

które są sterowane przez komplementarne stany sygnału zegarowego Clock

Clock

które są sterowane przez komplementarne stany sygnału zegarowego Clock

Clock.

Pierwszy zatrzask od strony wejścia nosi nazwę Master

Master, a drugi Slave

Slave.

Jeżeli zatrzask Master jest w stanie aktywnym (transparent mode) to zatrzask Slave

jest nieaktywny (hold mode) i odwrotnie.

T li j i

d

i i

l i

6 marca 2011

Wojciech Kucewicz

38

Ten stan realizuje się poprzez odwracanie na inwerterze stanu logicznego zegara

jednego z zatrzasków.

Przerzutnik SR wyzwalany zboczem

Przerzutnik SR wyzwalany zboczem

opadającym

opadającym

Przerzutnik SR wyzwalany zboczem

Przerzutnik SR wyzwalany zboczem

opadającym

opadającym

Slave

Slave

Master

Master

Przerzutnik SR

Przerzutnik SR

Clock

Clock

Clock

Clock

RR

6 marca 2011

Wojciech Kucewicz

39

S

S

Q

Q

Not usedNot usedNot usedNot used

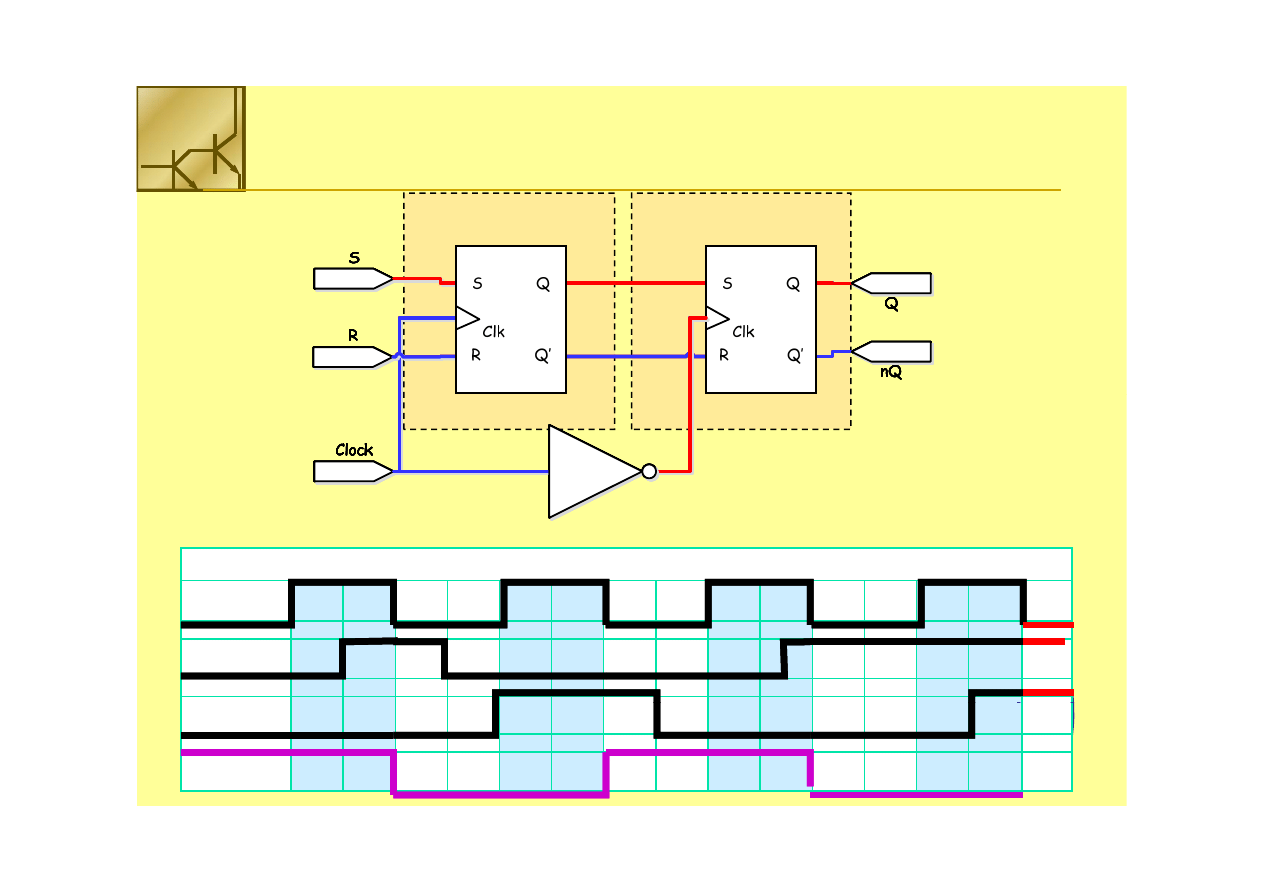

Przerzutnik SR wyzwalany zboczem

Przerzutnik SR wyzwalany zboczem

narastającym

narastającym

Przerzutnik SR wyzwalany zboczem

Przerzutnik SR wyzwalany zboczem

narastającym

narastającym

Slave

Slave

Master

Master

S

R

S Q

R Q’

Clk

nQ

Q

S Q

R Q’

Clk

Q

Clock

J

l

ł

b

ś d d

k R

Jeżeli sygnał zegarowy jest bezpośrednio podawany na zatrzask SR

Master, a zanegowany na zatrzask Slave to przerzutnik wyzwalany jest

przerzutnik wyzwalany jest

zboczem opadającym

zboczem opadającym.

Jeżeli sygnał zegarowy podawany na zatrzask SR Master jest zanegowany

6 marca 2011

Wojciech Kucewicz

40

Jeżeli sygnał zegarowy podawany na zatrzask SR Master jest zanegowany,

a na zatrzask Slave niezanegowany to przerzutnik wyzwalany jest

przerzutnik wyzwalany jest

zboczem narastającym

zboczem narastającym.

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

JK

JK

JK

JK

JK

JK

JK

JK

6 marca 2011

Wojciech Kucewicz

41

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

Przerzutnik typu JK

Przerzutnik typu JK ma wejścia informacyjne (J i K), zegarowe (C), wyjście proste

ma wejścia informacyjne (J i K), zegarowe (C), wyjście proste

(Q) i j

j ( i Q)

ż t ż i ć jś i k

j

(

t t ) (R) i t i j

(Q) i j

j ( i Q)

ż t ż i ć jś i k

j

(

t t ) (R) i t i j

(Q) i jego negację (nie Q), może też mieć wejście kasujące (restartu) (R) i ustawiające

(Q) i jego negację (nie Q), może też mieć wejście kasujące (restartu) (R) i ustawiające

(S).

(S).

Przerzutnik jest przerzutnikiem synchronicznym, co oznacza, że zmienia stan przy

Przerzutnik jest przerzutnikiem synchronicznym, co oznacza, że zmienia stan przy

zmianie stanu wejścia zegarowego z niskiego na wysoki (0 na 1)

zmianie stanu wejścia zegarowego z niskiego na wysoki (0 na 1)--wyzwalanie zboczem

wyzwalanie zboczem

zm an stanu w jśc a z garow go z n s

go na wyso ( na )

zm an stanu w jśc a z garow go z n s

go na wyso ( na ) wyzwa an z ocz m

wyzwa an z ocz m

narastającym lub przy zmianie stanu wejścia zegarowego z wysokiego na niski (1 na 0)

narastającym lub przy zmianie stanu wejścia zegarowego z wysokiego na niski (1 na 0)--

wyzwalanie zboczem opadającym .

wyzwalanie zboczem opadającym .

Nazwa przerzutnika JK pochodzi od imienia i nazwiska Jacka

Nazwa przerzutnika JK pochodzi od imienia i nazwiska Jacka Kilby

Kilby, inżyniera

, inżyniera

amerykańskiego wynalazcy układów scalonych

amerykańskiego wynalazcy układów scalonych

amerykańskiego, wynalazcy układów scalonych.

amerykańskiego, wynalazcy układów scalonych.

J Q’

Set

K Q

Res

Clk

6 marca 2011

Wojciech Kucewicz

42

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

J

Q

Clock

K

Q

K

nQ

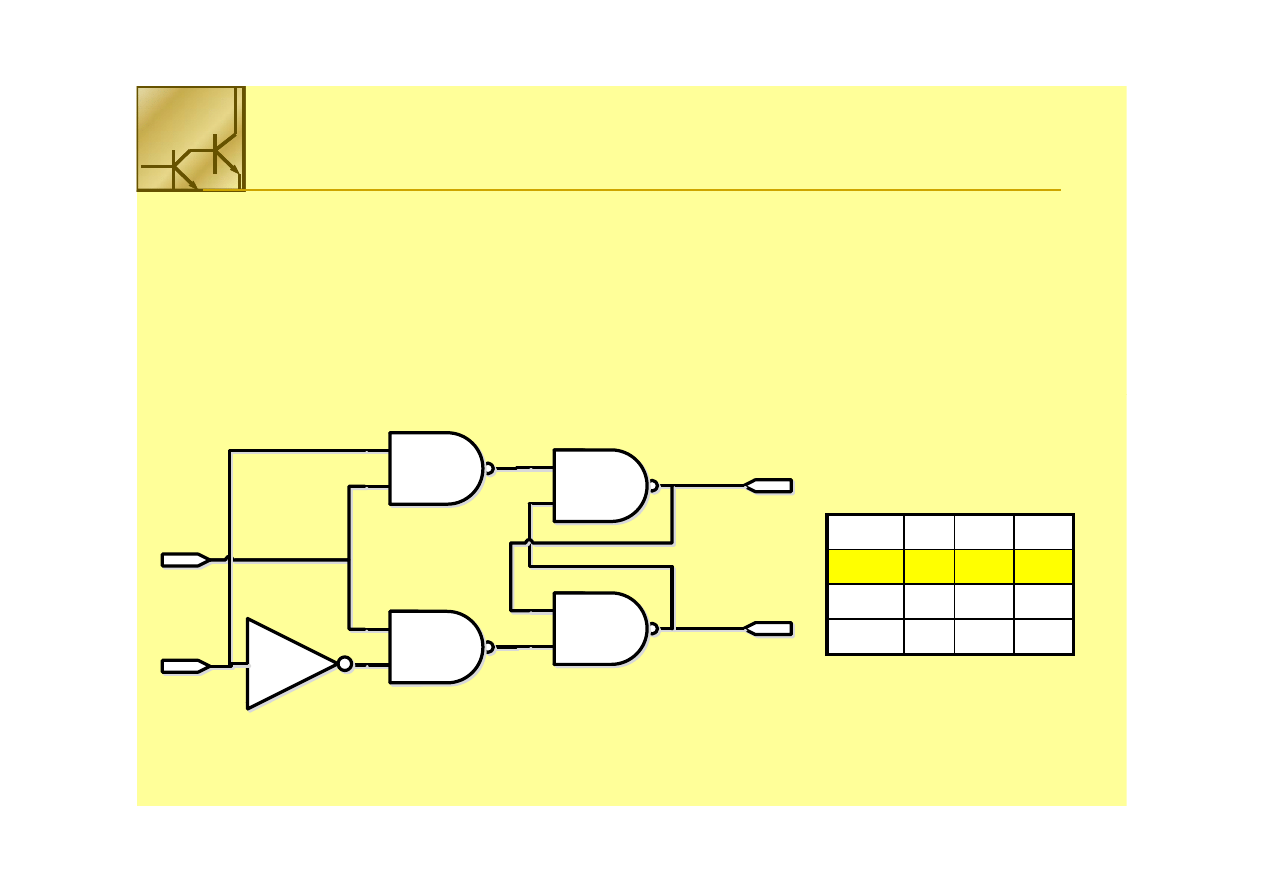

Przerzutnik JK jest zaprojektowany w taki sposób, że nie ma stanów zabronionych

nie ma stanów zabronionych.

Wejściowe bramki NAND są 3 wejściowe. Na dodatkowe wejścia doprowadzony jest

sygnał z wyjść Q i nQ. Ponieważ wyjścia Q i nQ mają zawsze różne stany, więc

niemożliwe jest wystąpienie na obu bramkach wejściowych samych 1 (stan

6 marca 2011

Wojciech Kucewicz

43

niemożliwe jest wystąpienie na obu bramkach wejściowych samych 1 (stan

zabroniony).

Wejścia informacyjne

J i K

J i K

, odpowiadają wejściom

S i R

S i R

przerzutnika SR.

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

J

S Q

J

S Q

J

S Q

J

S Q

J

S Q

J

S Q

J

S Q

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Q

Q

Q

Q

Q

Q

Q

Przerzutnik JK

Przerzutnik JK

Clock

Clock

Clock

Clock

JJ

6 marca 2011

Wojciech Kucewicz

44

KK

Q

Q

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

JJJJJ

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

Clock

K

S Q

R Q’

nQ

Q

S Q

R Q’

nQ

nQ

nQ

nQ

nQ

JJ

KK

Q

Q

nnQ

Q

0

0

Q

Q

nQ

nQ

0

1

00

11

W przypadku jednoczesnego podania sygnałów 1

na wejścia J i K, jego stan będzie się zmieniał po

każdym impulsie zegara.

6 marca 2011

Wojciech Kucewicz

45

11

00

11

00

11

11

nQ

nQ

Q

Q

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

Przerzutnik JK

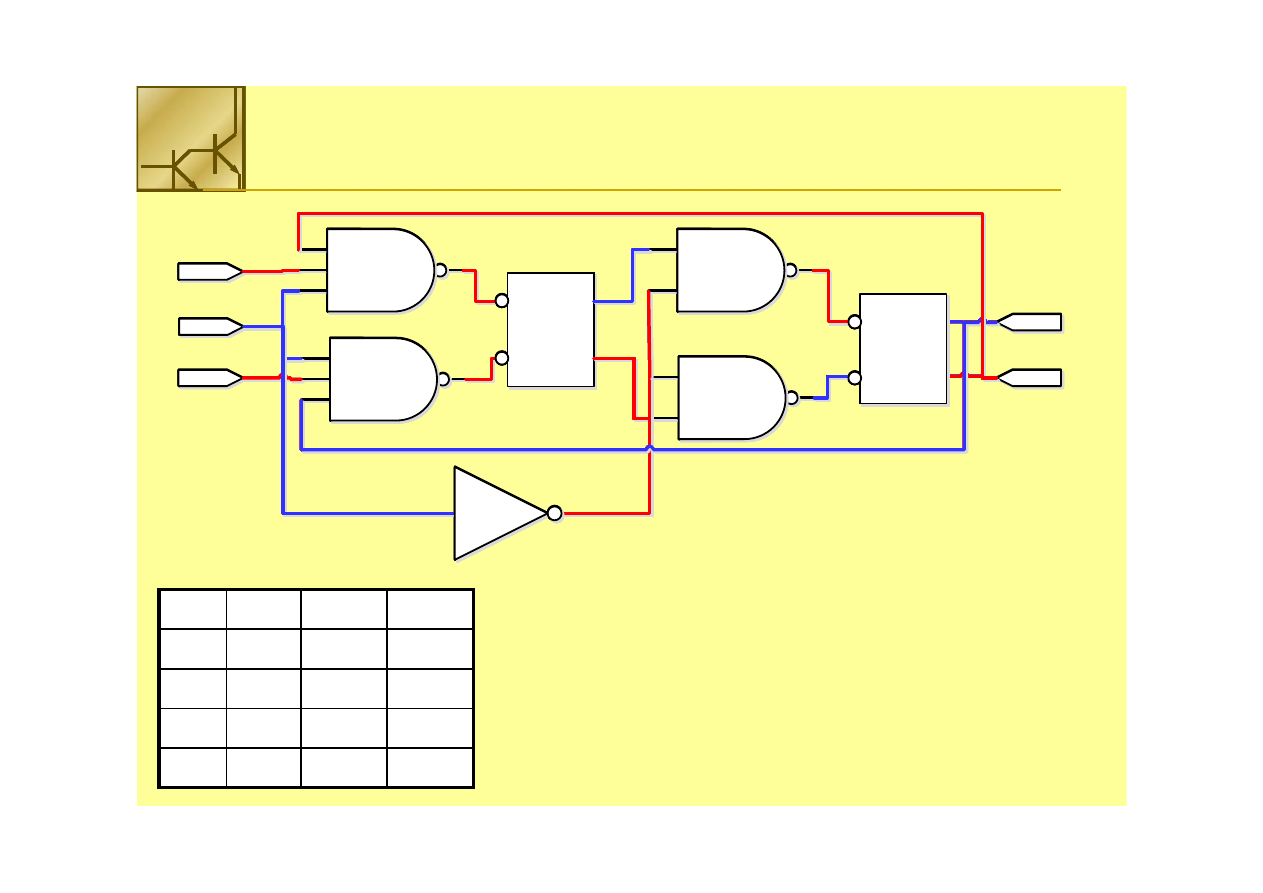

Funkcję realizowaną przez przerzutnik JK można wyznaczyć z tablicy

Funkcję realizowaną przez przerzutnik JK można wyznaczyć z tablicy Karnaugh

Karnaugh

JJ

nn

KK

nn

Qn

Qn

00

00

01

01

11

11

10

10

00

00

00

11

11

00

00

00

11

11

11

11

00

00

11

Q

Q

n+1

n+1

== Q’

Q’

nn

JJ

nn

+

+ Q

Q

nn

K’

K’

nn

6 marca 2011

Wojciech Kucewicz

46

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

D

D

D

D

D

D

D

D

6 marca 2011

Wojciech Kucewicz

47

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Aby wyeliminować stan zabroniony (R=1, S=1) synchronicznego

Aby wyeliminować stan zabroniony (R=1, S=1) synchronicznego

przerzutnika

przerzutnika SR

SR można na wejście wprowadzić dodatkowy inwerter zapewniający

można na wejście wprowadzić dodatkowy inwerter zapewniający

un k R S’

un k R S’

warunek R = S .

warunek R = S .

Taki przerzutnik ma jedno wejście i nazywany jest synchronicznym

Taki przerzutnik ma jedno wejście i nazywany jest synchronicznym

przerzutnikiem typu D lub zatrzaskiem D bramkowanym.

przerzutnikiem typu D lub zatrzaskiem D bramkowanym.

Q

CLK

CLK

D

D

Q

Q

nnQ

Q

0

x

Q

Q

nQ

nQ

11

11

11

00

Q

Clock

11

11

11

00

11

00

00

11

nQ

D

6 marca 2011

Wojciech Kucewicz

48

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

CLK

CLK

RR

S

S

Q

Q

nnQ

Q

0

0

1

Q

Q

nQ

nQ

0

1

0

Q

Q

nQ

nQ

Q

Q

Q

Q

Q

11

00

11

11

00

11

11

00

00

11

Clock

nQ

D

Przerzutnik D

Przerzutnik D

Stan wejścia D jest przenoszony na wyjście tylko przy wysokim (1) stanie zegara

Clock

Clock

D

D

6 marca 2011

Wojciech Kucewicz

49

D

D

Q

Q

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Przerzutnik D

realizuje funkcję przepisywania informacji z wejścia D na wyjście

Q

z opóźnieniem jednego impulsu taktującego. Nazwa pochodzi od angielskiego słowa

Delay = opóźnienie

Delay opóźnienie

Funkcję realizowaną przez przerzutnik D można wyznaczyć tablicy

Funkcję realizowaną przez przerzutnik D można wyznaczyć tablicy Karnaugh

Karnaugh::

D

D

nn

Qn

Qn

00

11

00

00

11

11

00

11

Q

Q

n+1

n+1

=

= D

D

nn

6 marca 2011

Wojciech Kucewicz

50

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Zatrzask bramkowany D

Górna

Górna bramka NAND daje na wyjściu zanegowany sygnał

bramka NAND daje na wyjściu zanegowany sygnał D.

D.

Wobec

Wobec tego schemat układu przerzutnika D można uprościć zastępując inwerter

tego schemat układu przerzutnika D można uprościć zastępując inwerter

g

m

p

m

p

ęp ją

g

m

p

m

p

ęp ją

połączeniem wyjścia tej bramki z jednym z wejść bramki

połączeniem wyjścia tej bramki z jednym z wejść bramki dolnej

dolnej..

D’

D’

≡≡

Q

Clock

nQ

D

6 marca 2011

Wojciech Kucewicz

51

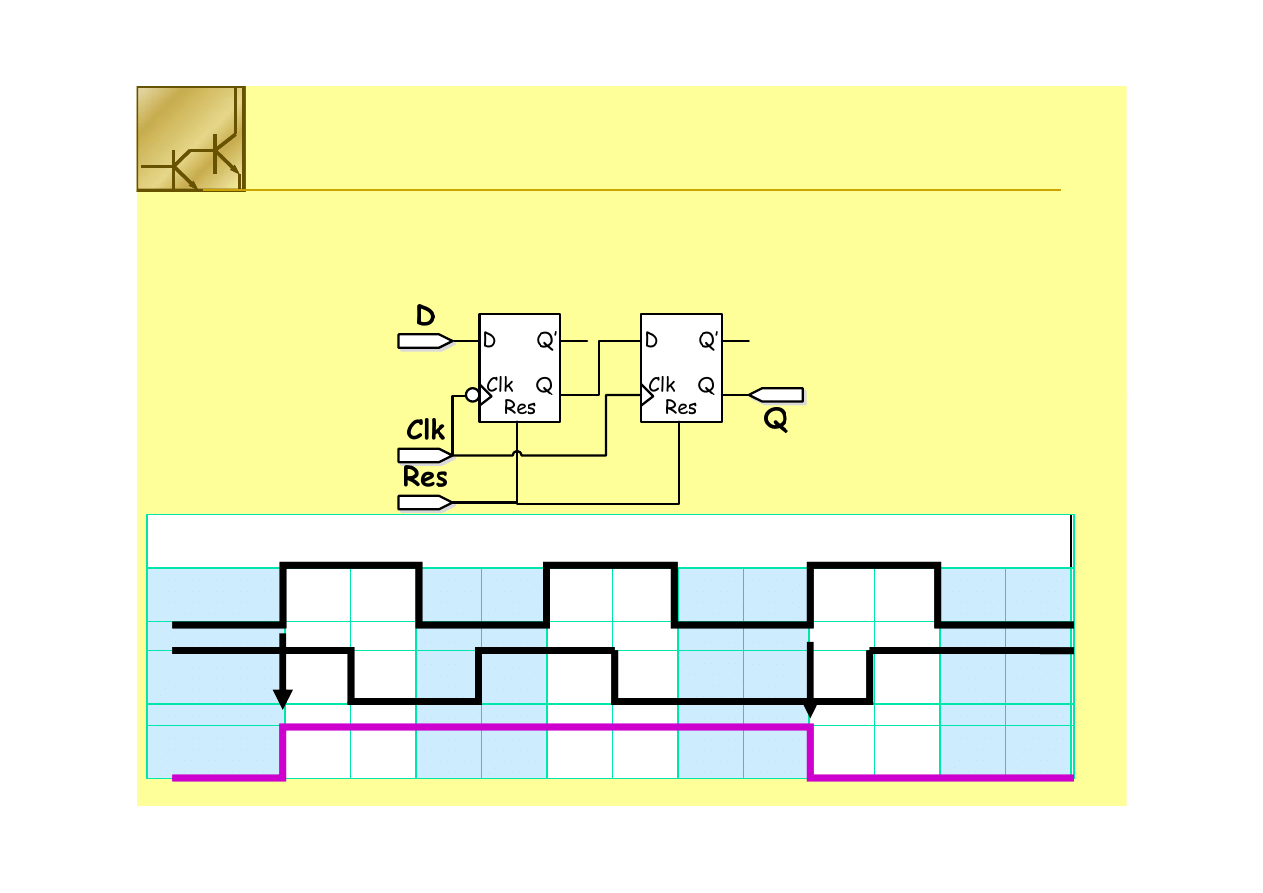

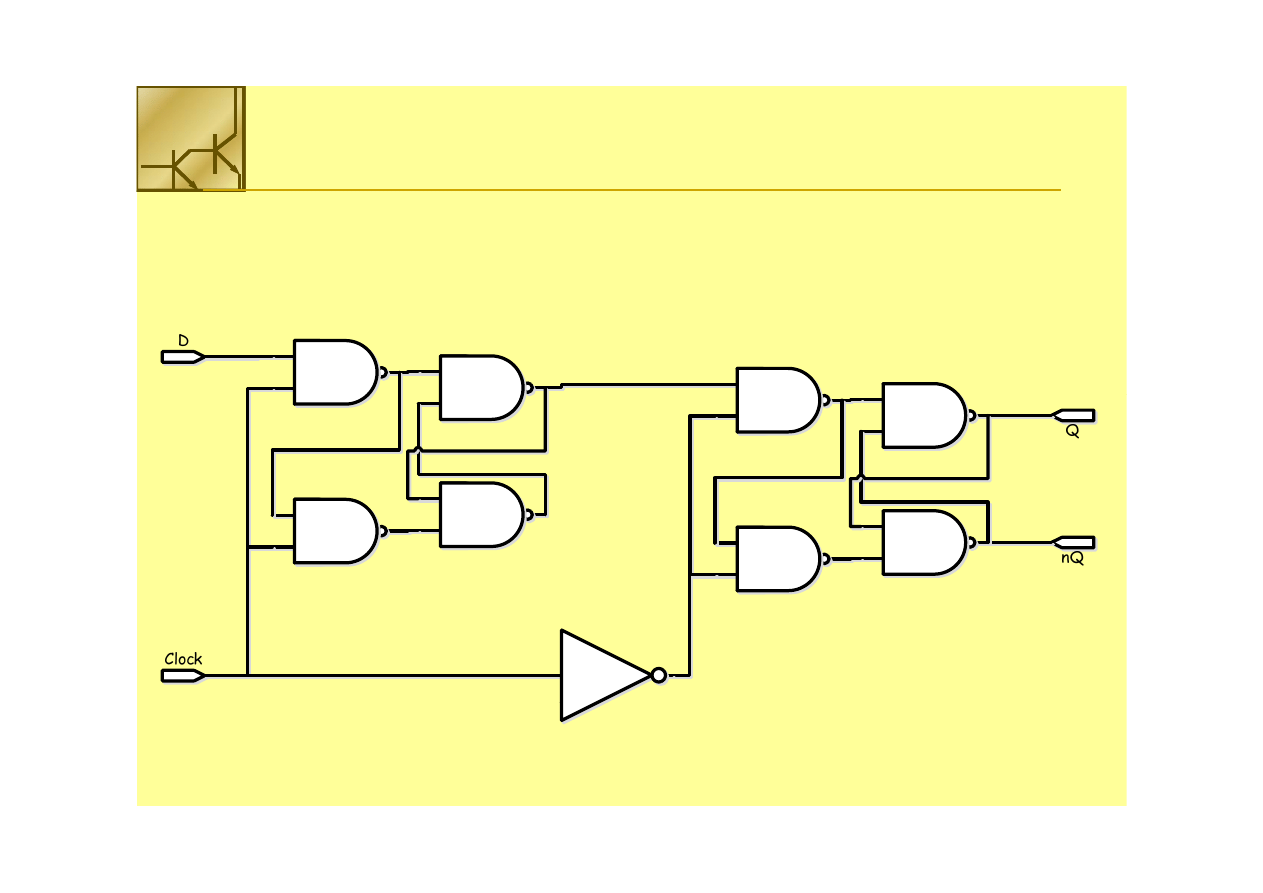

Przerzutnik D wyzwalany zboczem impulsu

Przerzutnik D wyzwalany zboczem impulsu

Przerzutnik D wyzwalany zboczem impulsu

Przerzutnik D wyzwalany zboczem impulsu

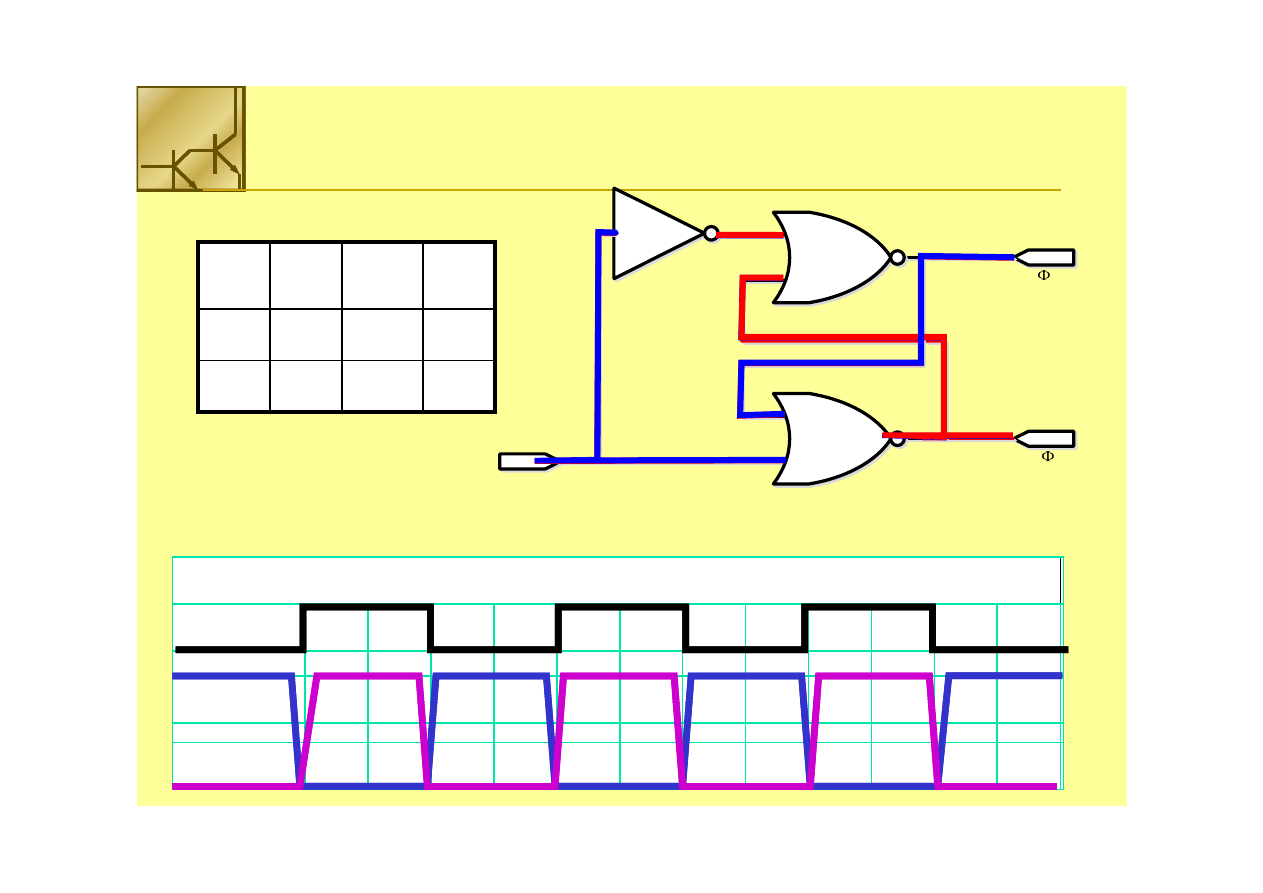

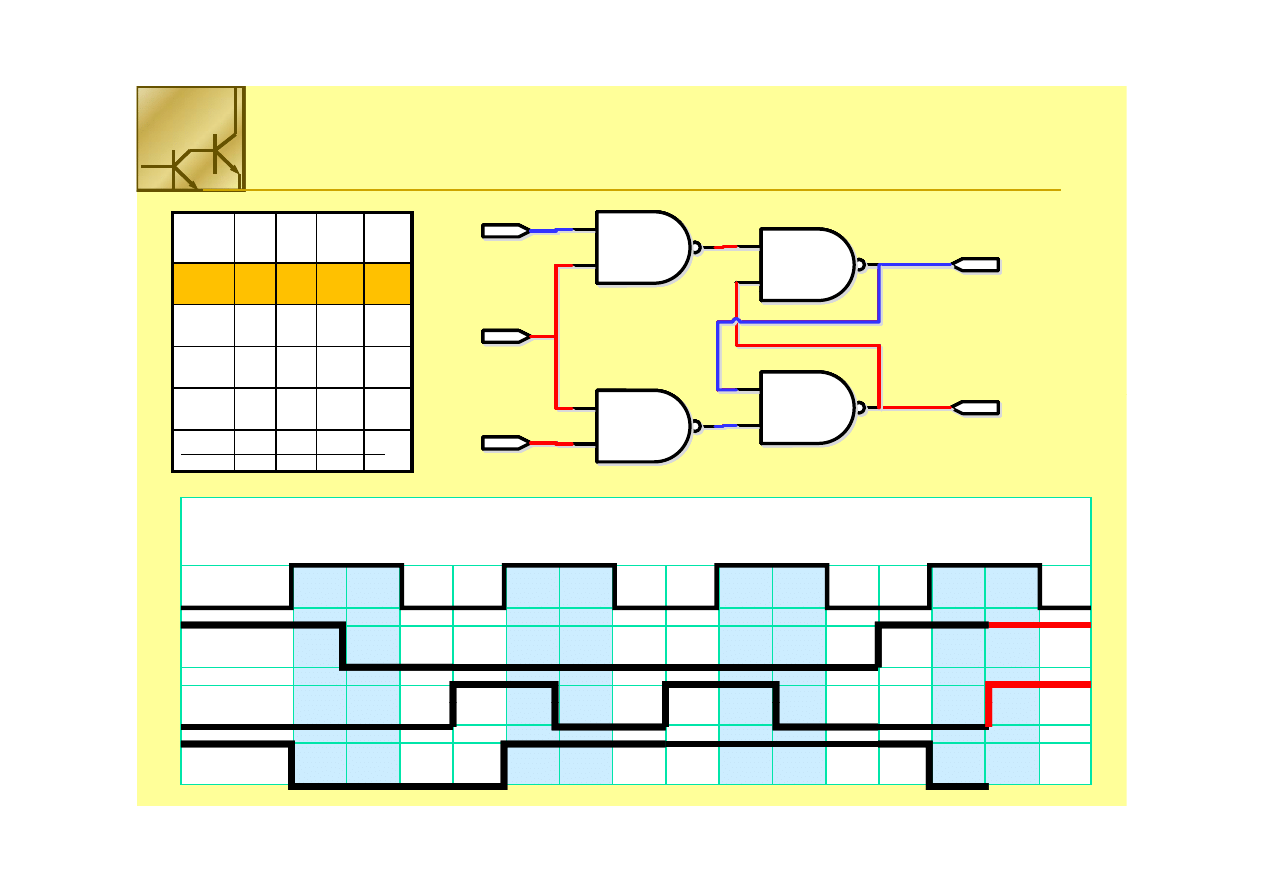

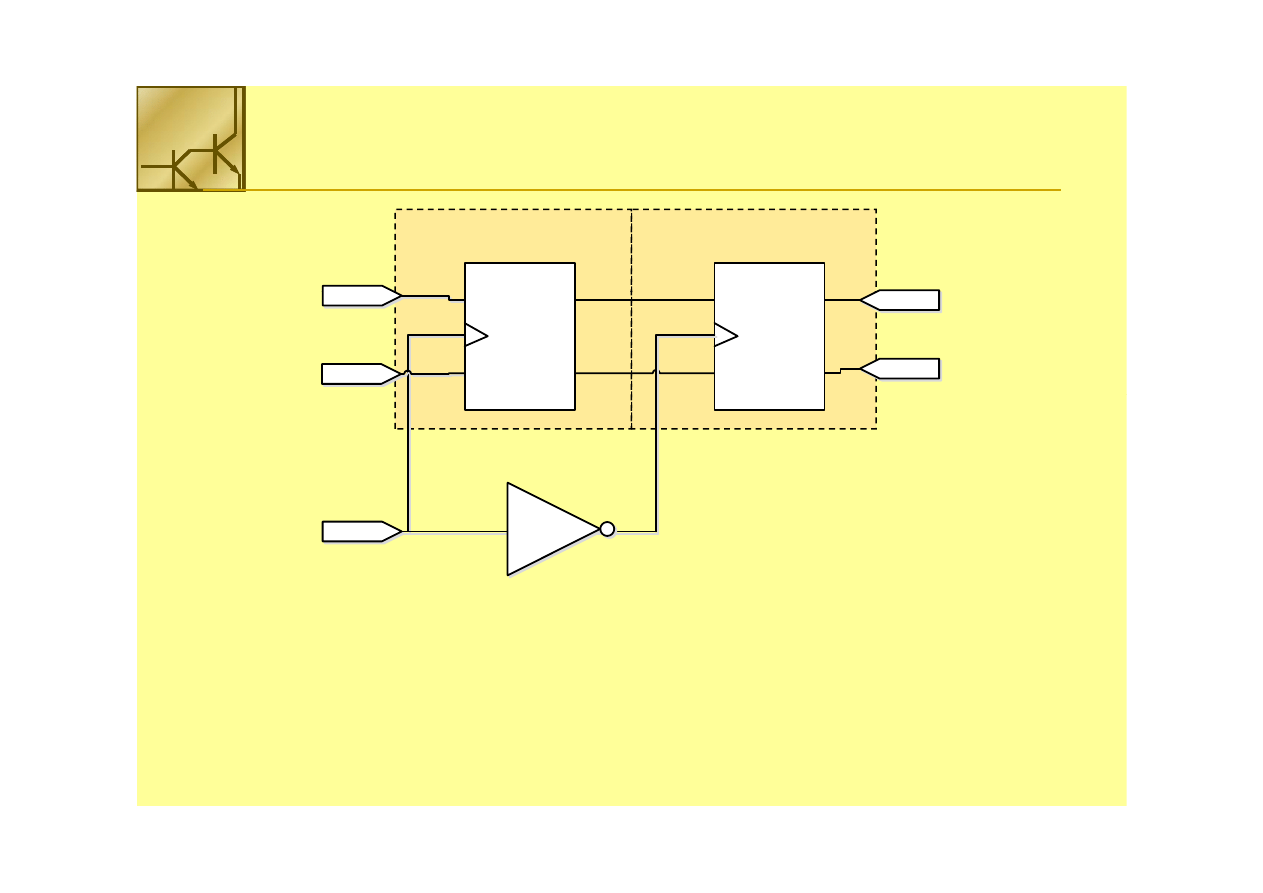

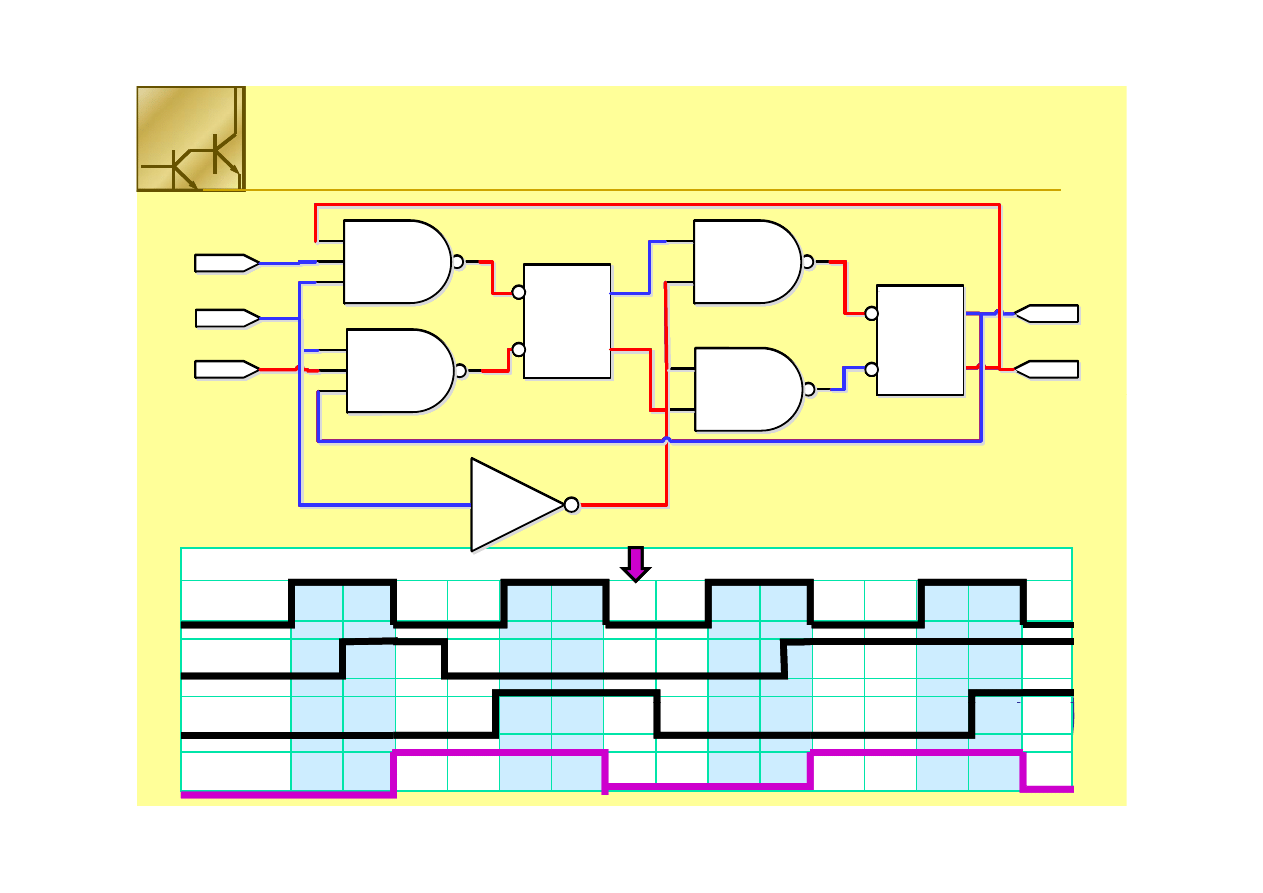

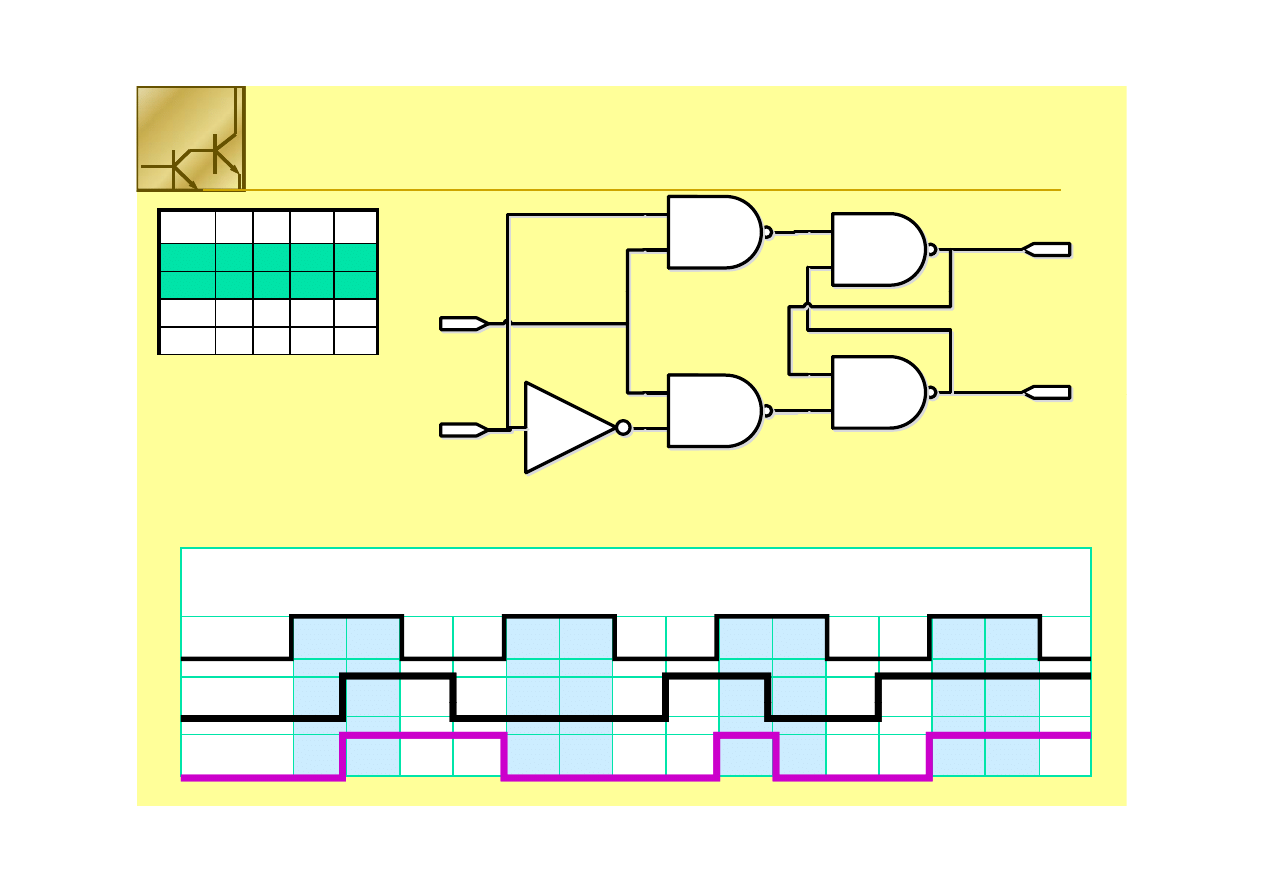

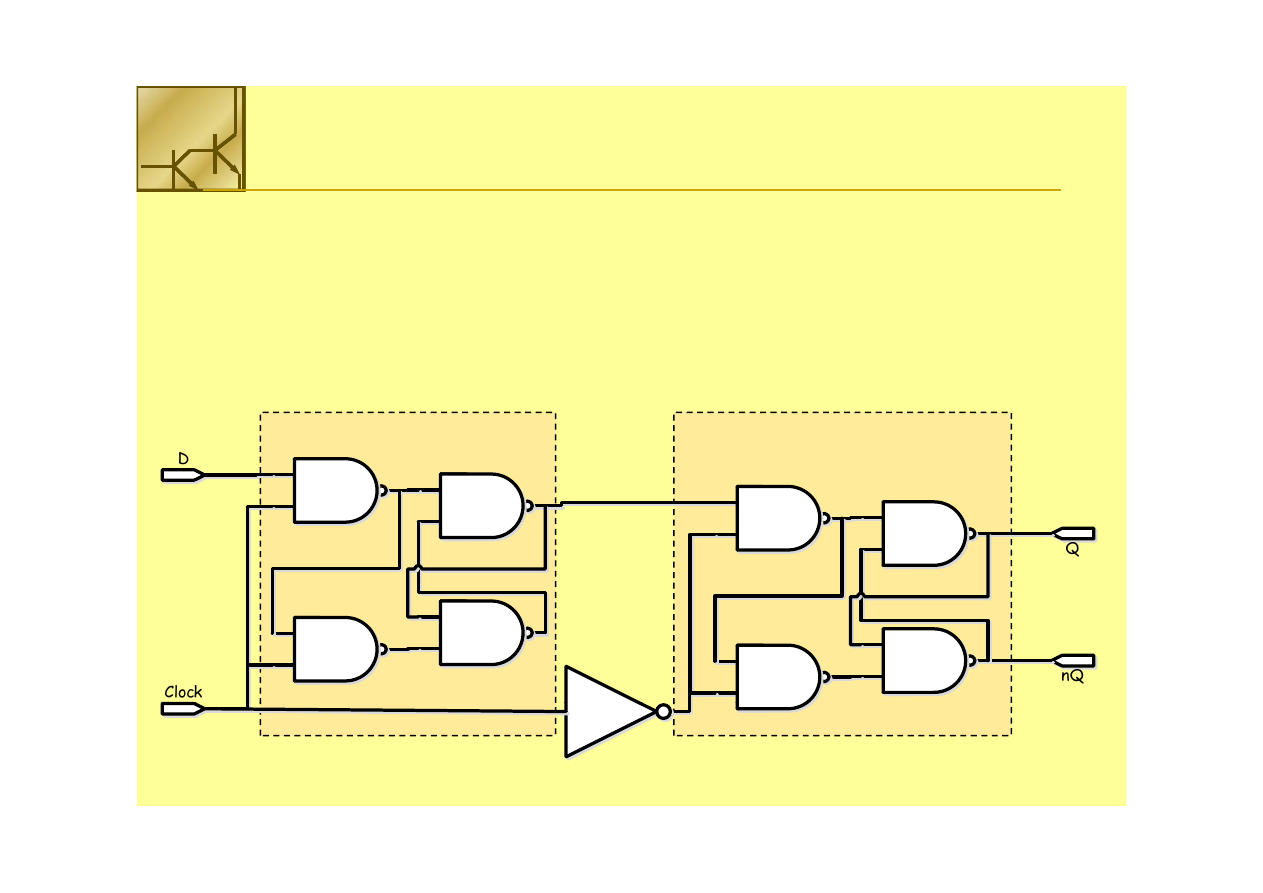

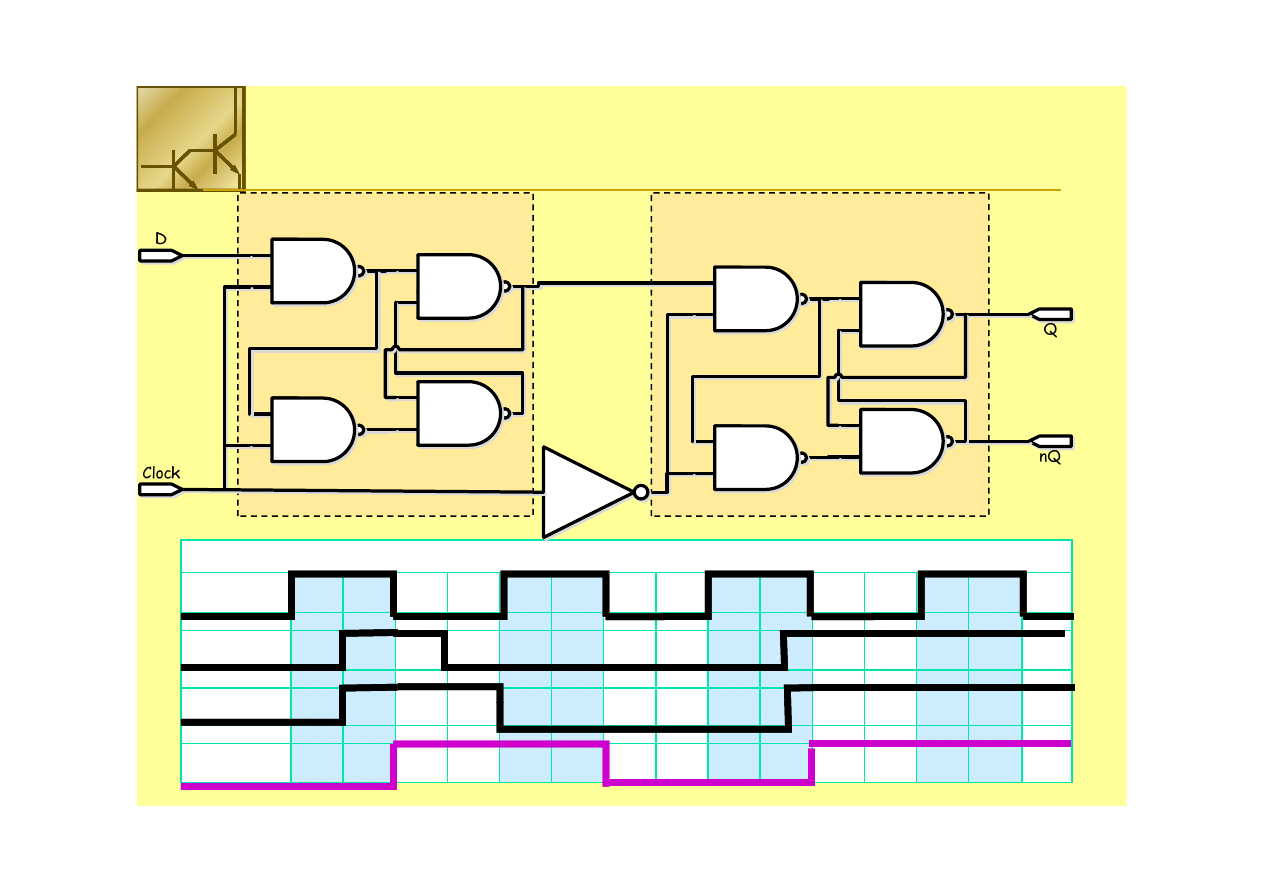

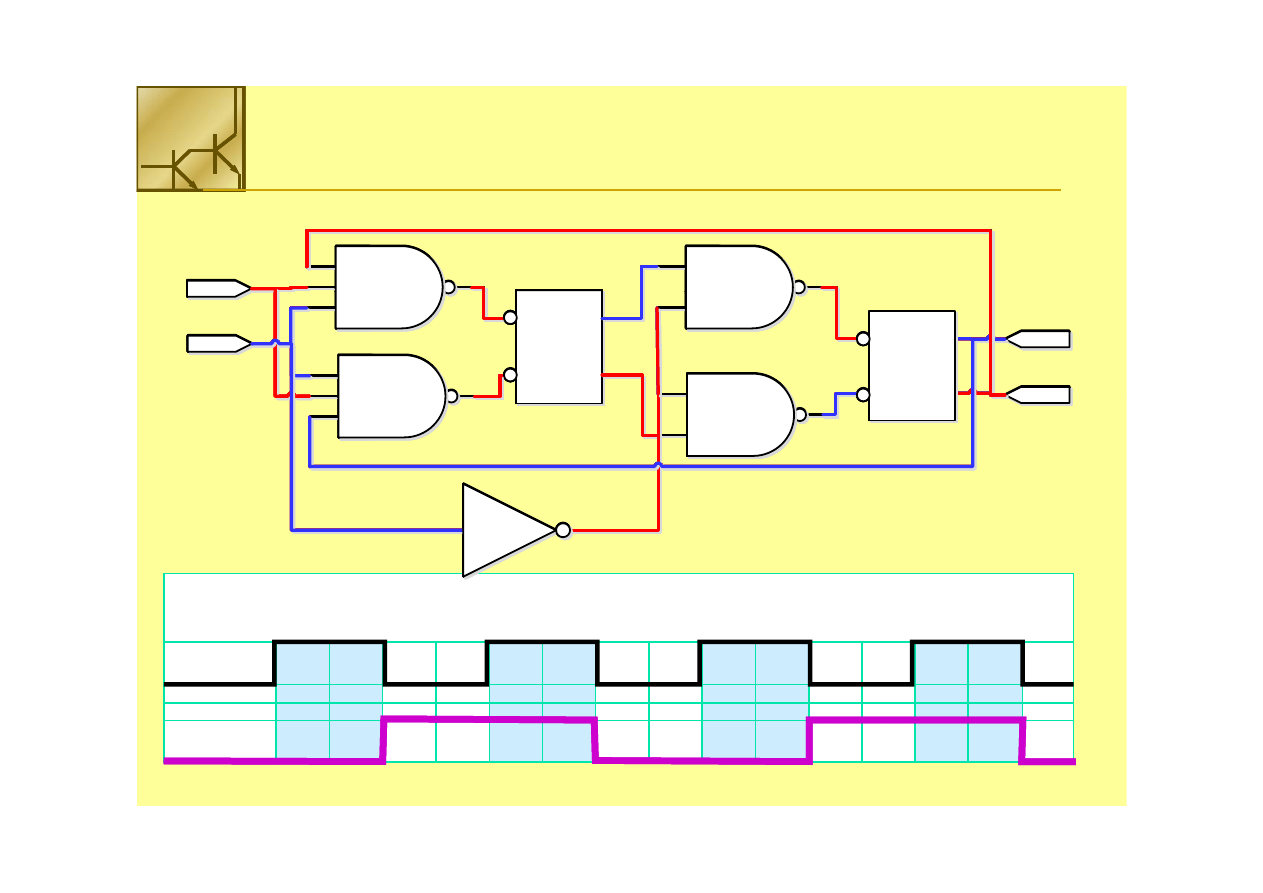

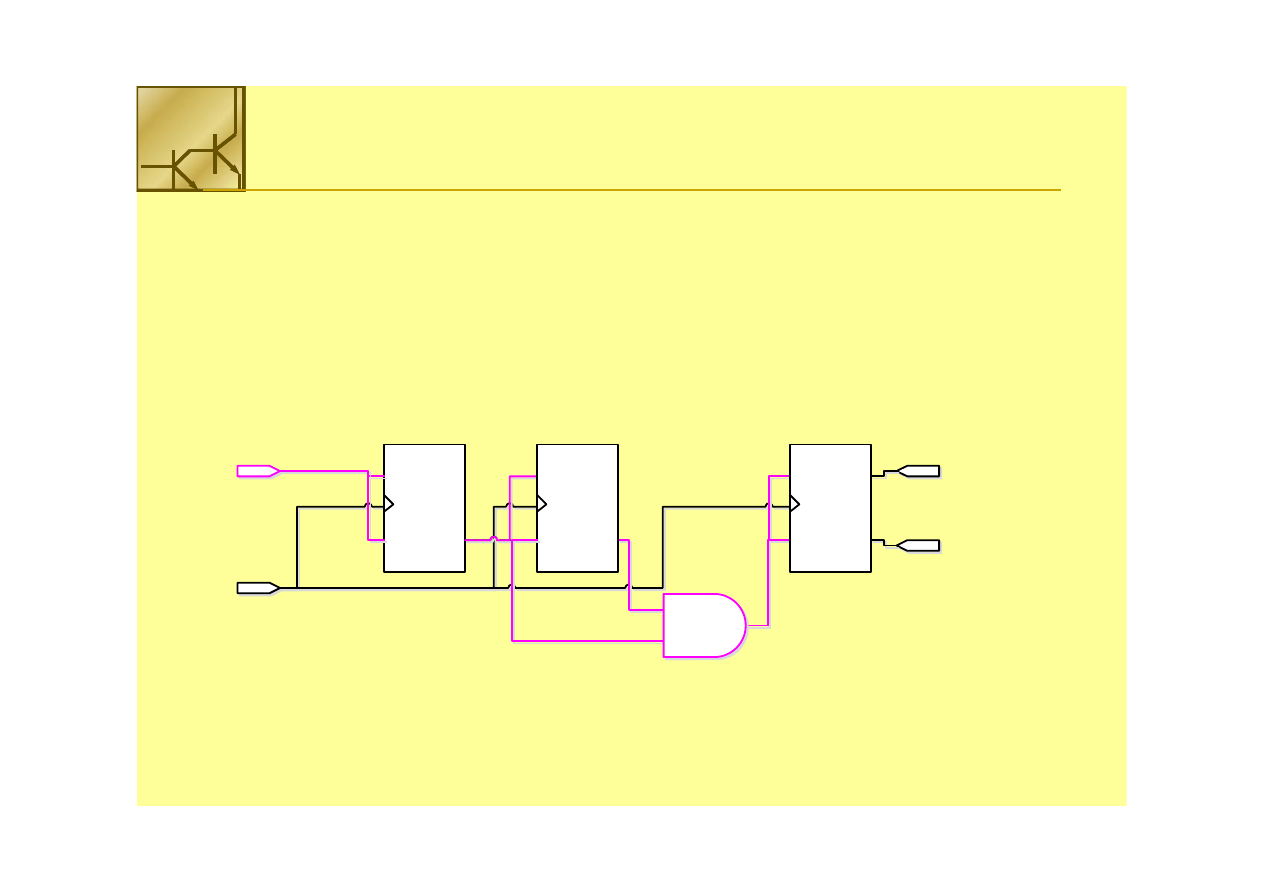

Przerzutnik D wyzwalany zboczem można zrealizować łącząc szeregowo dwa

Przerzutnik D wyzwalany zboczem można zrealizować łącząc szeregowo dwa

przerzutniki D typu zatrzask sterowane dopełniającymi się sygnałami zegarowymi.

przerzutniki D typu zatrzask sterowane dopełniającymi się sygnałami zegarowymi.

Gdy sygnał zegarowy jest w stanie 1 stan wejścia D jest przenoszony na wyjście

Gdy sygnał zegarowy jest w stanie 1 stan wejścia D jest przenoszony na wyjście

Gdy sygnał zegarowy jest w stanie 1 stan wejścia D jest przenoszony na wyjście

Gdy sygnał zegarowy jest w stanie 1 stan wejścia D jest przenoszony na wyjście

przerzutnika Master, a przy przejściu zegara ze stanu 1 na 0 sygnał jest przeniesiony

przerzutnika Master, a przy przejściu zegara ze stanu 1 na 0 sygnał jest przeniesiony

na wyjście Q. Przerzutnik jest wyzwalany zboczem opadającym.

na wyjście Q. Przerzutnik jest wyzwalany zboczem opadającym.

Master

Master

Slave

Slave

6 marca 2011

Wojciech Kucewicz

52

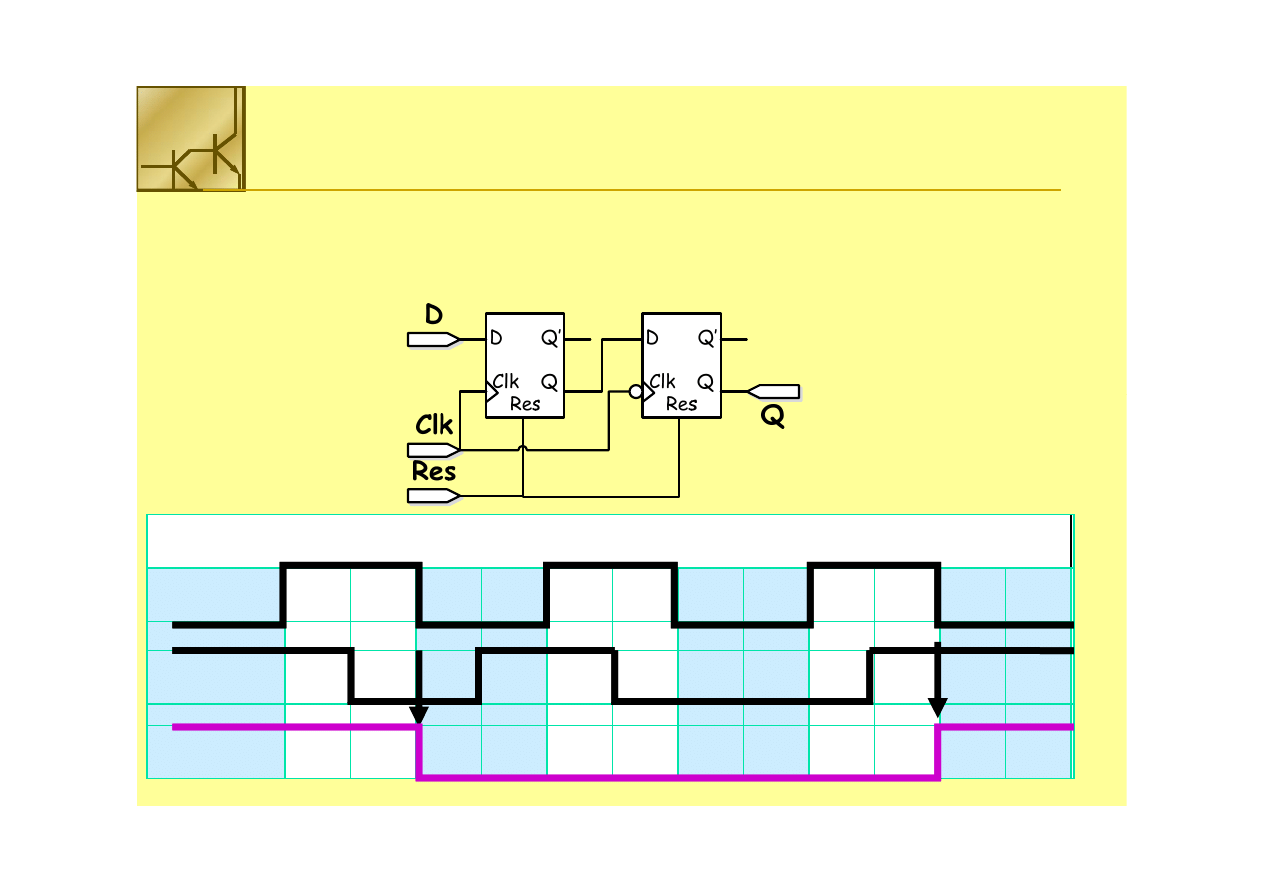

Przerzutnik D wyzwalany zboczem

Przerzutnik D wyzwalany zboczem

impulsu

impulsu

Przerzutnik D wyzwalany zboczem

Przerzutnik D wyzwalany zboczem

impulsu

impulsu

Master

Master

Slave

Slave

Przerzutnik D

Przerzutnik D

Clock

Clock

Clock

Clock

D

D

Q

Q

6 marca 2011

Wojciech Kucewicz

53

Q

Q

M

M

Q

Q

Przerzutnik D wyzwalany zboczem

Przerzutnik D wyzwalany zboczem

impulsu

impulsu

Przerzutnik D wyzwalany zboczem

Przerzutnik D wyzwalany zboczem

impulsu

impulsu

Aby przerzutnik był wyzwalany zboczem narastającym należy odwrócić fazę zegara.

Aby przerzutnik był wyzwalany zboczem narastającym należy odwrócić fazę zegara.

6 marca 2011

Wojciech Kucewicz

54

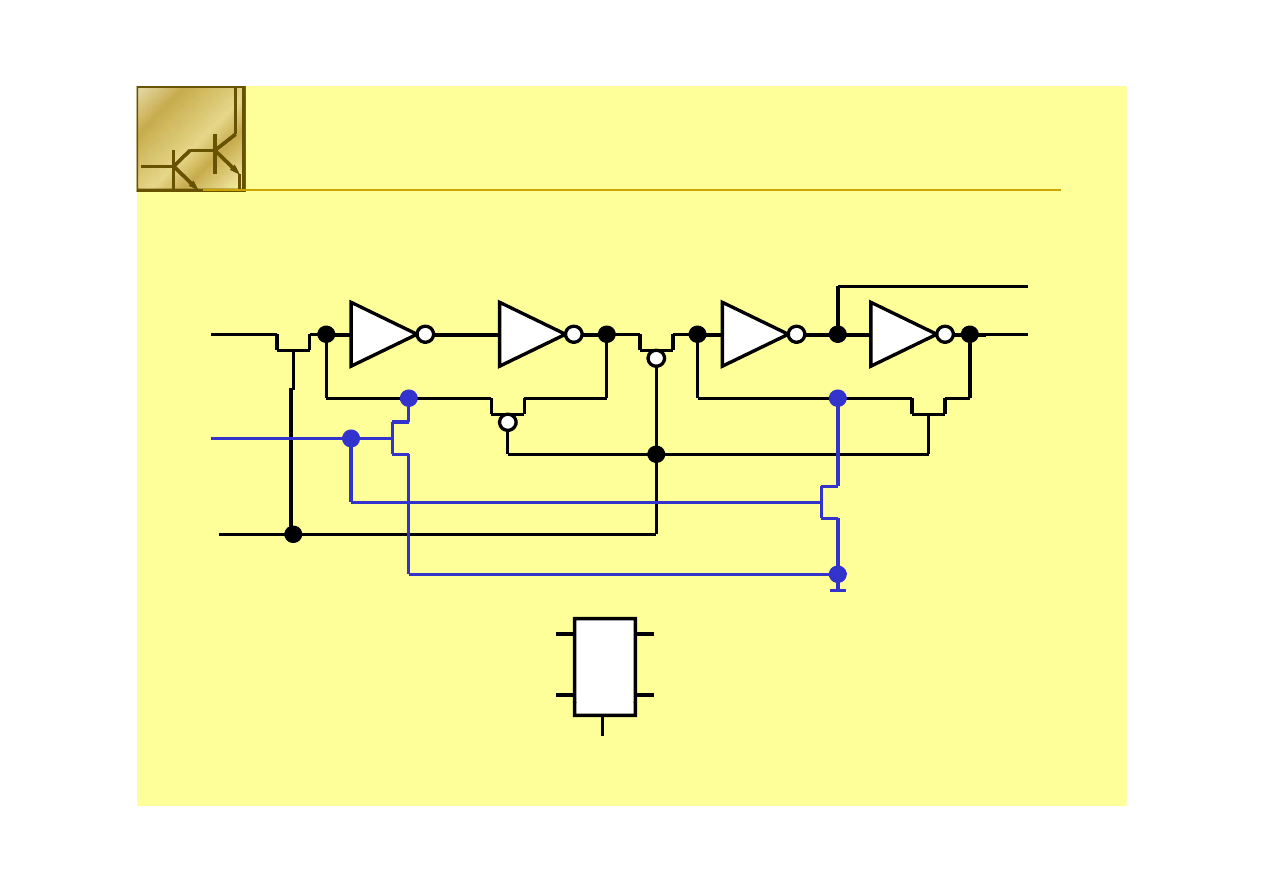

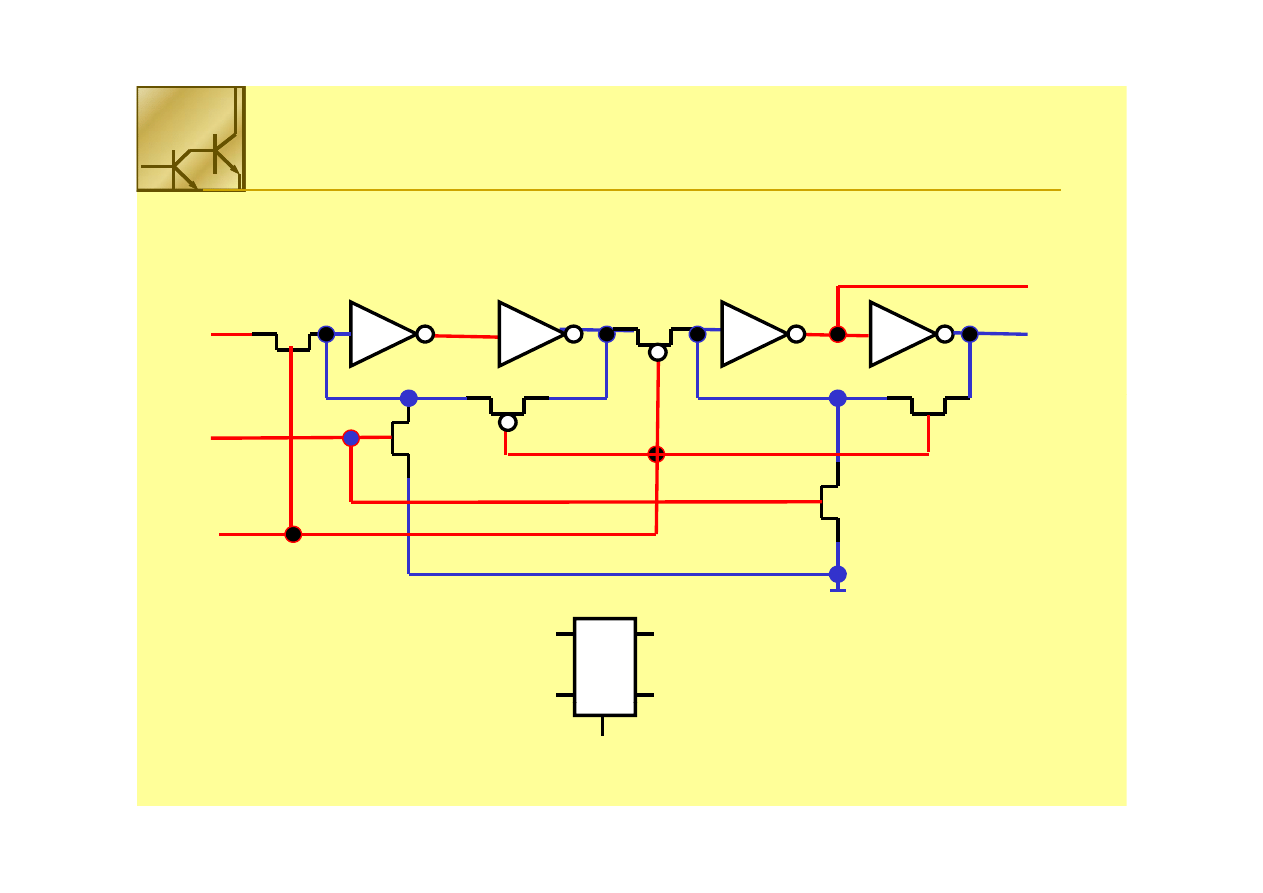

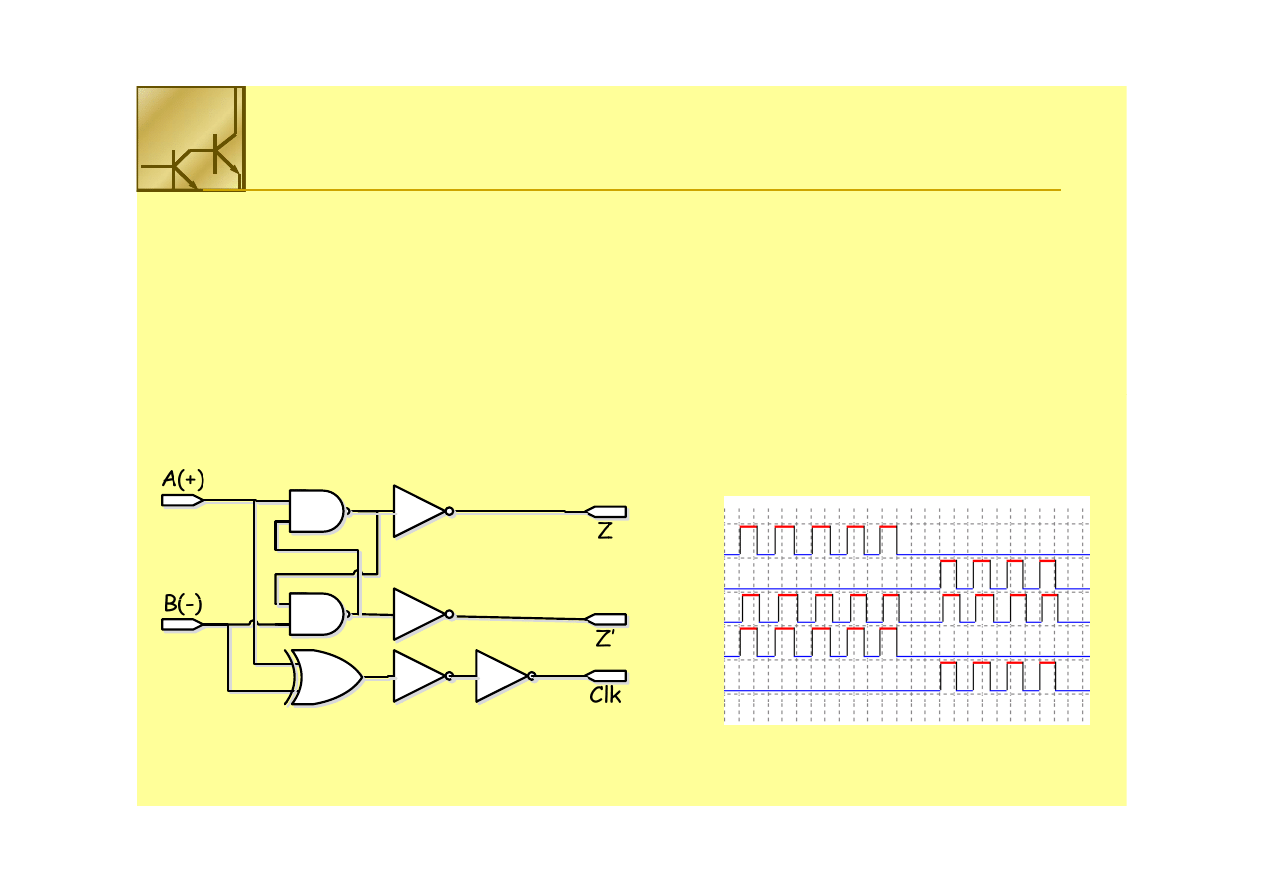

The D Flip

The D Flip--flop (Edge Trigged Latch)

flop (Edge Trigged Latch)

The D Flip

The D Flip--flop (Edge Trigged Latch)

flop (Edge Trigged Latch)

notQ

D

ata

Q

R

eset

C

lock

D flipD flip-

-flo

p

flo

p

Reset

Reset

Data

Data

notQ

notQ

Q

Q

6 marca 2011

Wojciech Kucewicz

55

pp

Clock

Clock

Reset

Reset

Q

Q

The D Flip

The D Flip--flop (Edge Trigged Latch)

flop (Edge Trigged Latch)

The D Flip

The D Flip--flop (Edge Trigged Latch)

flop (Edge Trigged Latch)

notQ

D

ata

Q

R

eset

C

lock

D flipD flip-

-flo

p

flo

p

Reset

Reset

Data

Data

notQ

notQ

Q

Q

6 marca 2011

Wojciech Kucewicz

56

pp

Clock

Clock

Reset

Reset

Q

Q

Przerzutnik T

Przerzutnik T

Przerzutnik T

Przerzutnik T

6 marca 2011

Wojciech Kucewicz

57

T

T Flip

Flip--flop

flop

T

T Flip

Flip--flop

flop

11111

T (Clk)

S Q

R Q’

Q

S Q

R Q’

T (Clk)

S Q

R Q’

Q

S Q

R Q’

T (Clk)

S Q

R Q’

Q

S Q

R Q’

T (Clk)

S Q

R Q’

Q

S Q

R Q’

T (Clk)

S Q

R Q’

Q

S Q

R Q’

nQ

R Q

nQ

R Q

nQ

R Q

nQ

R Q

nQ

R Q

P

t ik T

P

t ik T

Przerzutnik T

Przerzutnik T

Clock

Clock

6 marca 2011

Wojciech Kucewicz

58

Q

Q

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

6 marca 2011

Wojciech Kucewicz

59

Licznik

Licznik

Licznik

Licznik

Liczniki są sekwencyjnymi układami cyfrowymi, które zliczają impulsy podane

Liczniki są sekwencyjnymi układami cyfrowymi, które zliczają impulsy podane

na ich wejście.

na ich wejście.

Budowane są z n przerzutników synchronicznych odpowiedni ze sobą

Budowane są z n przerzutników synchronicznych odpowiedni ze sobą

ł

h

ł

h

połączonych.

połączonych.

W licznikach dwójkowych

W licznikach dwójkowych n oznacza liczbę bitów licznika

n oznacza liczbę bitów licznika, czyli liczbę

, czyli liczbę

znaków w liczbie binarnej reprezentującej stan licznika

znaków w liczbie binarnej reprezentującej stan licznika

znaków w liczbie binarnej, reprezentującej stan licznika.

znaków w liczbie binarnej, reprezentującej stan licznika.

Liczbę stanów przyjmowanych przez licznik w jednym pełnym cyklu nazywa

Liczbę stanów przyjmowanych przez licznik w jednym pełnym cyklu nazywa

się

się długością cyklu

długością cyklu (pojemnością licznika)

(pojemnością licznika)

się

się długością cyklu

długością cyklu (pojemnością licznika).

(pojemnością licznika).

Jeśli licznik ma p różnych stanów, przez które przechodzi cyklicznie, to

Jeśli licznik ma p różnych stanów, przez które przechodzi cyklicznie, to

określa się go jako

określa się go jako licznik modulo p

licznik modulo p..

6 marca 2011

Wojciech Kucewicz

60

określa się go jako

określa się go jako licznik modulo p

licznik modulo p..

Licznik

Licznik

Licznik

Licznik

Ze względu na długość cyklu liczniki możemy podzielić na:

Ze względu na długość cyklu liczniki możemy podzielić na:

liczniki o stałej długości cyklu

liczniki o stałej długości cyklu

liczniki o programowalnej długości cyklu

liczniki o programowalnej długości cyklu

Jeżeli kolejne liczby reprezentujące stan licznika wzrastają w trakcie

Jeżeli kolejne liczby reprezentujące stan licznika wzrastają w trakcie

liczenia impulsów to takie liczniki nazywamy

liczenia impulsów to takie liczniki nazywamy licznikami zliczającymi w przód

licznikami zliczającymi w przód

W przeciwnym razie gdy stany licznika maleją nazywamy je

W przeciwnym razie gdy stany licznika maleją nazywamy je licznikami

licznikami

W przeciwnym razie, gdy stany licznika maleją, nazywamy je

W przeciwnym razie, gdy stany licznika maleją, nazywamy je licznikami

licznikami

zliczającymi wstecz

zliczającymi wstecz.

.

Liczniki mogące zliczać w przód i wstecz nazywa się

Liczniki mogące zliczać w przód i wstecz nazywa się licznikami

licznikami

dwukierunkowymi

dwukierunkowymi lub

lub rewersyjnymi

rewersyjnymi

dwukierunkowymi

dwukierunkowymi lub

lub rewersyjnymi

rewersyjnymi..

6 marca 2011

Wojciech Kucewicz

61

Licznik

Licznik

Licznik

Licznik

Jednym z

Jednym z kryterów

kryterów podziału liczników może być sposób oddziaływania

podziału liczników może być sposób oddziaływania

impulsów zliczanych na stan przerzutników licznika. Liczniki wg tej

impulsów zliczanych na stan przerzutników licznika. Liczniki wg tej

klasyfikacji dzielimy na:

klasyfikacji dzielimy na:

synchroniczne,

synchroniczne,

h

i

h

i

asynchroniczne,

asynchroniczne,

asynchroniczno

asynchroniczno--synchroniczne.

synchroniczne.

W liczniku synchronicznym impulsy zliczane

W liczniku synchronicznym impulsy zliczane sa

sa podawane na wejścia

podawane na wejścia

W liczniku synchronicznym impulsy zliczane

W liczniku synchronicznym impulsy zliczane sa

sa podawane na wejścia

podawane na wejścia

zegarowe wszystkich przerzutników.

zegarowe wszystkich przerzutników.

W liczniku asynchronicznym oraz asynchroniczno

W liczniku asynchronicznym oraz asynchroniczno--synchronicznym impulsy

synchronicznym impulsy

zliczane podaje się tylko na jedno lub niektóre z wejść zegarowych

zliczane podaje się tylko na jedno lub niektóre z wejść zegarowych

zliczane podaje się tylko na jedno lub niektóre z wejść zegarowych

zliczane podaje się tylko na jedno lub niektóre z wejść zegarowych

przerzutników licznika.

przerzutników licznika.

6 marca 2011

Wojciech Kucewicz

62

Licznik

Licznik

Licznik

Licznik

Liczniki charakteryzuje się w oparciu o następujące parametry:

Liczniki charakteryzuje się w oparciu o następujące parametry:

szybkość działania,

szybkość działania,

czas ustalania zawartości licznika

czas ustalania zawartości licznika

czas ustalania zawartości licznika

czas ustalania zawartości licznika

Szybkość działania określa się przez podanie maksymalnej dopuszczalnej

Szybkość działania określa się przez podanie maksymalnej dopuszczalnej

częstotliwości

częstotliwości ff

impulsów zliczanych

impulsów zliczanych

częstotliwości

częstotliwości ff

max

max

impulsów zliczanych.

impulsów zliczanych.

Czas ustalania zawartości licznika jest to czas w którym nastąpią zmiany

Czas ustalania zawartości licznika jest to czas w którym nastąpią zmiany

stanów wszystkich przerzutników ( maksymalnie jest to suma czasów

stanów wszystkich przerzutników ( maksymalnie jest to suma czasów

propagacji wszystkich przerzutników).

propagacji wszystkich przerzutników).

propagacj wszyst ch prz rzutn ów).

propagacj wszyst ch prz rzutn ów).

W licznikach synchronicznych wejścia zegarowe wszystkich przerzutników są

W licznikach synchronicznych wejścia zegarowe wszystkich przerzutników są

połączone, co zapewnia jednoczesność zmian stanów przerzutników.

połączone, co zapewnia jednoczesność zmian stanów przerzutników.

p

p

j

p

p

p

j

p

Sposób działania tych liczników zależy od realizacji funkcji przełączających

Sposób działania tych liczników zależy od realizacji funkcji przełączających

dla wejść informacyjnych.

dla wejść informacyjnych.

Rozróżnia się:

Rozróżnia się:

l

k

h

ó

l

(

l

k

h

ó

l

(

ll l

ll l

))

6 marca 2011

Wojciech Kucewicz

63

liczniki synchroniczne z przeniesienia równoległymi (

liczniki synchroniczne z przeniesienia równoległymi (parallel

parallel carry

carry))

liczniki synchroniczne z przeniesieniami szeregowymi (

liczniki synchroniczne z przeniesieniami szeregowymi (ripple

ripple carry

carry))

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

asynchroniczne

asynchroniczne

asynchroniczne

asynchroniczne

asynchroniczne

asynchroniczne

asynchroniczne

asynchroniczne

6 marca 2011

Wojciech Kucewicz

64

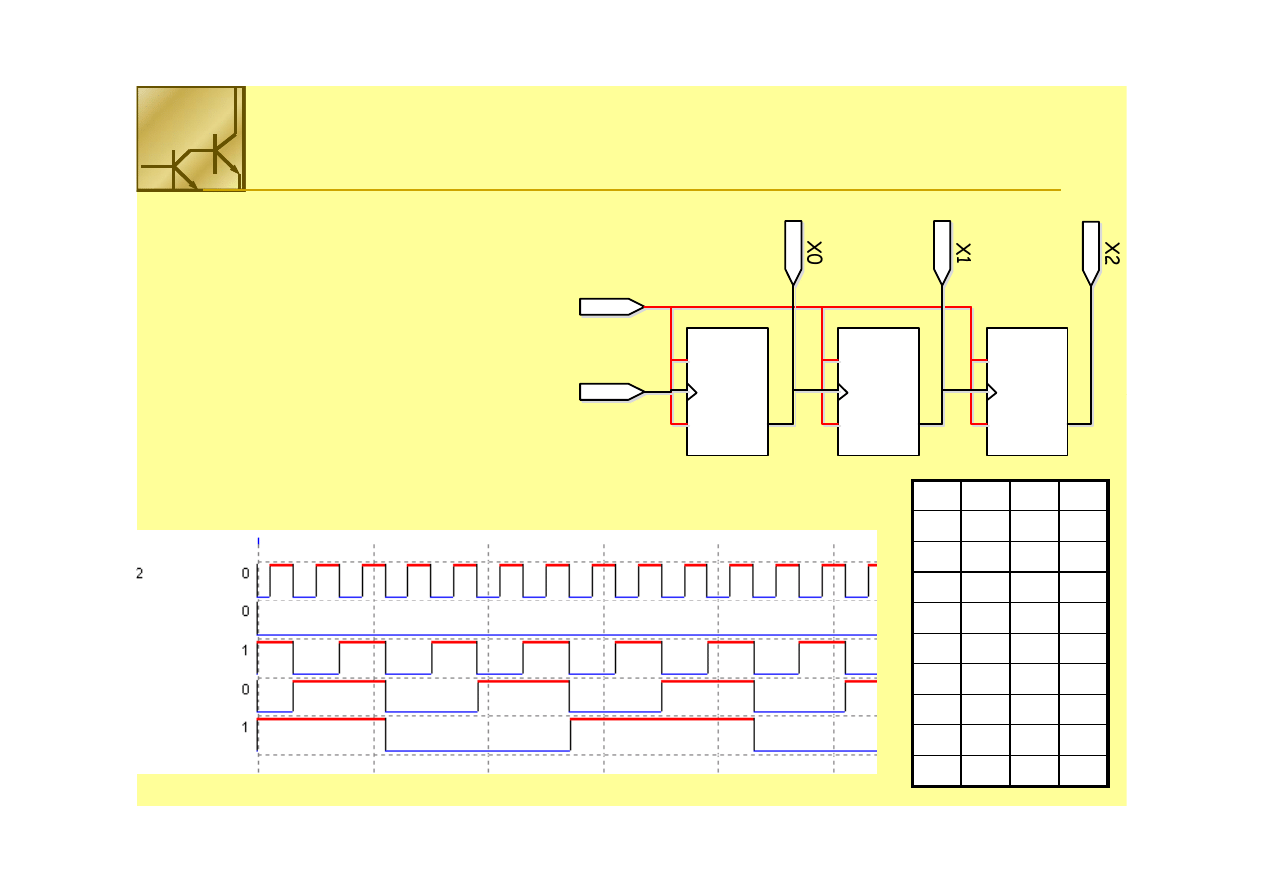

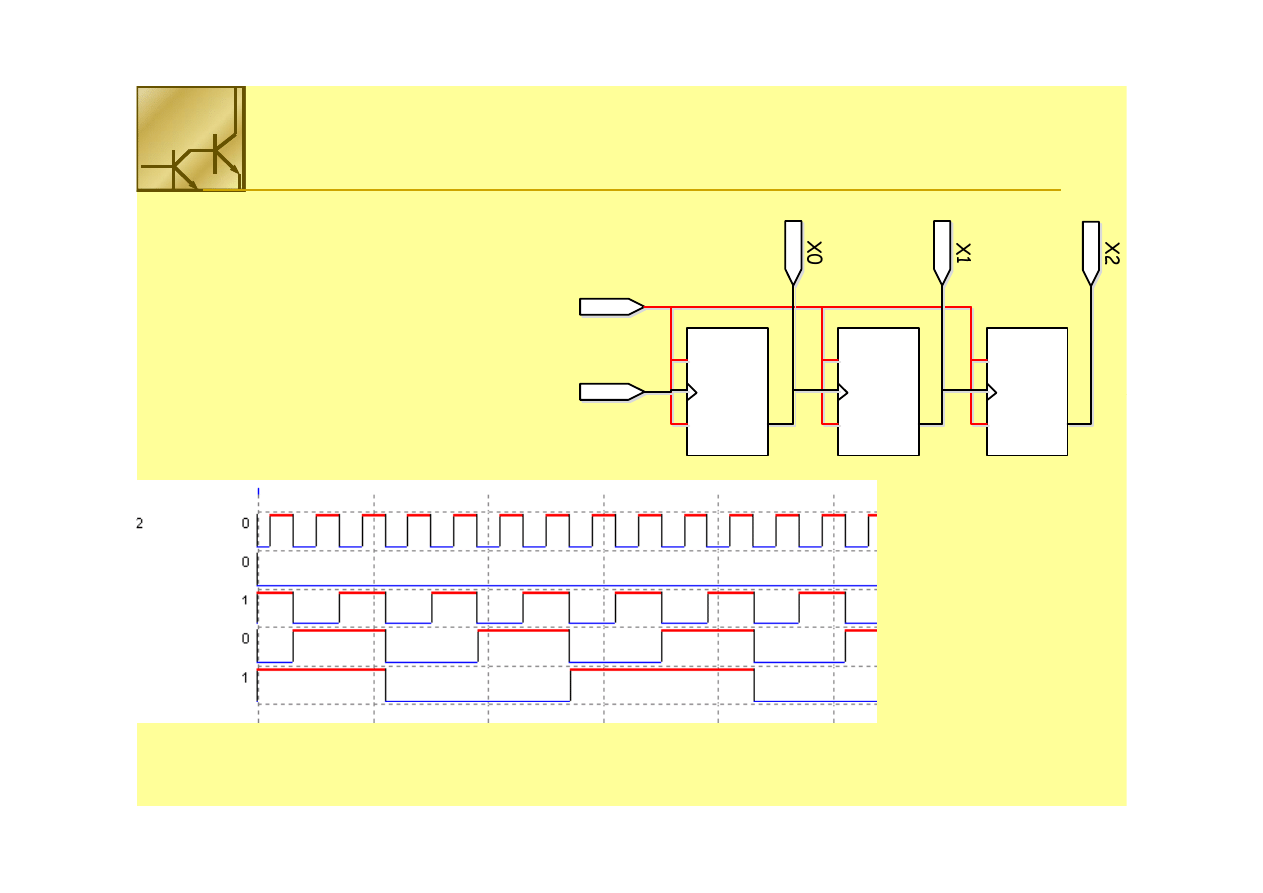

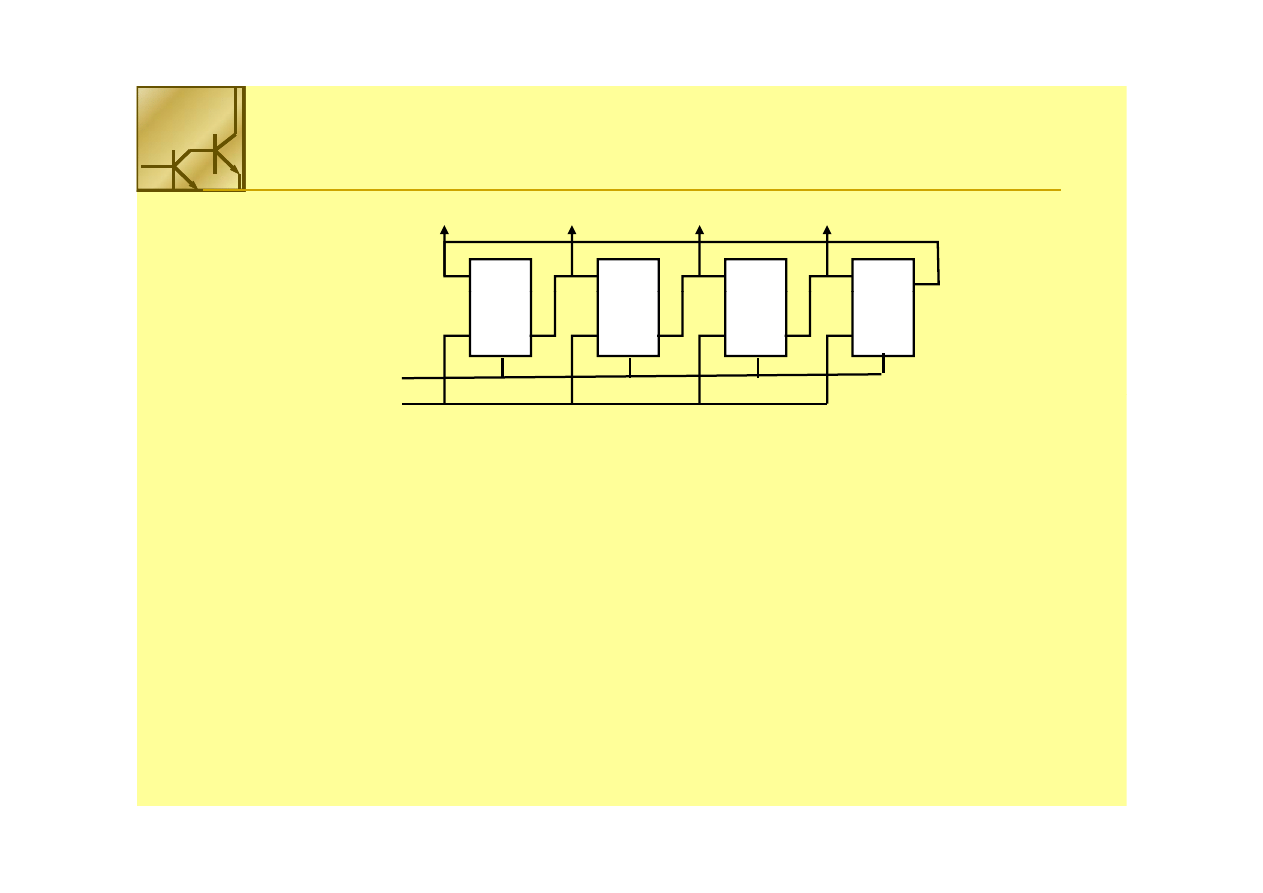

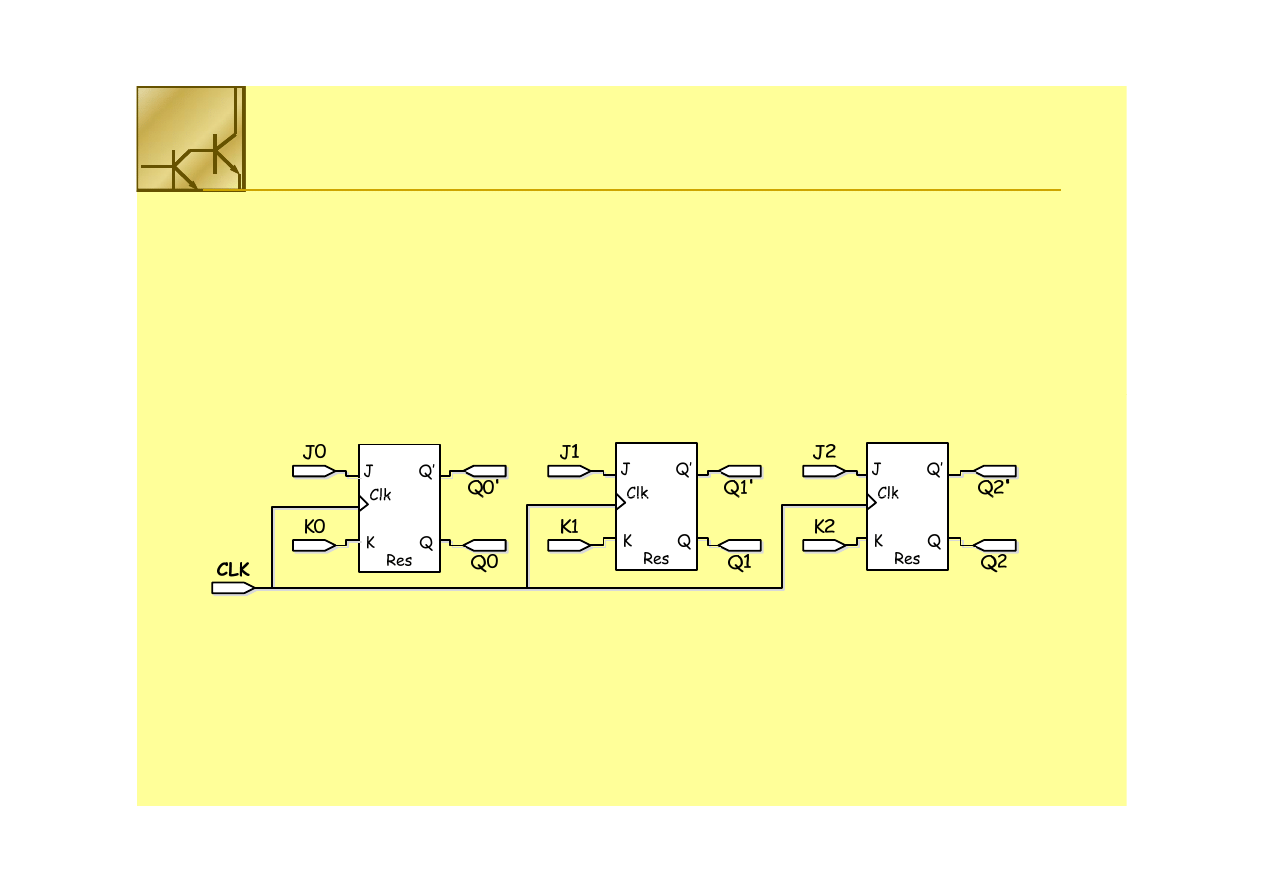

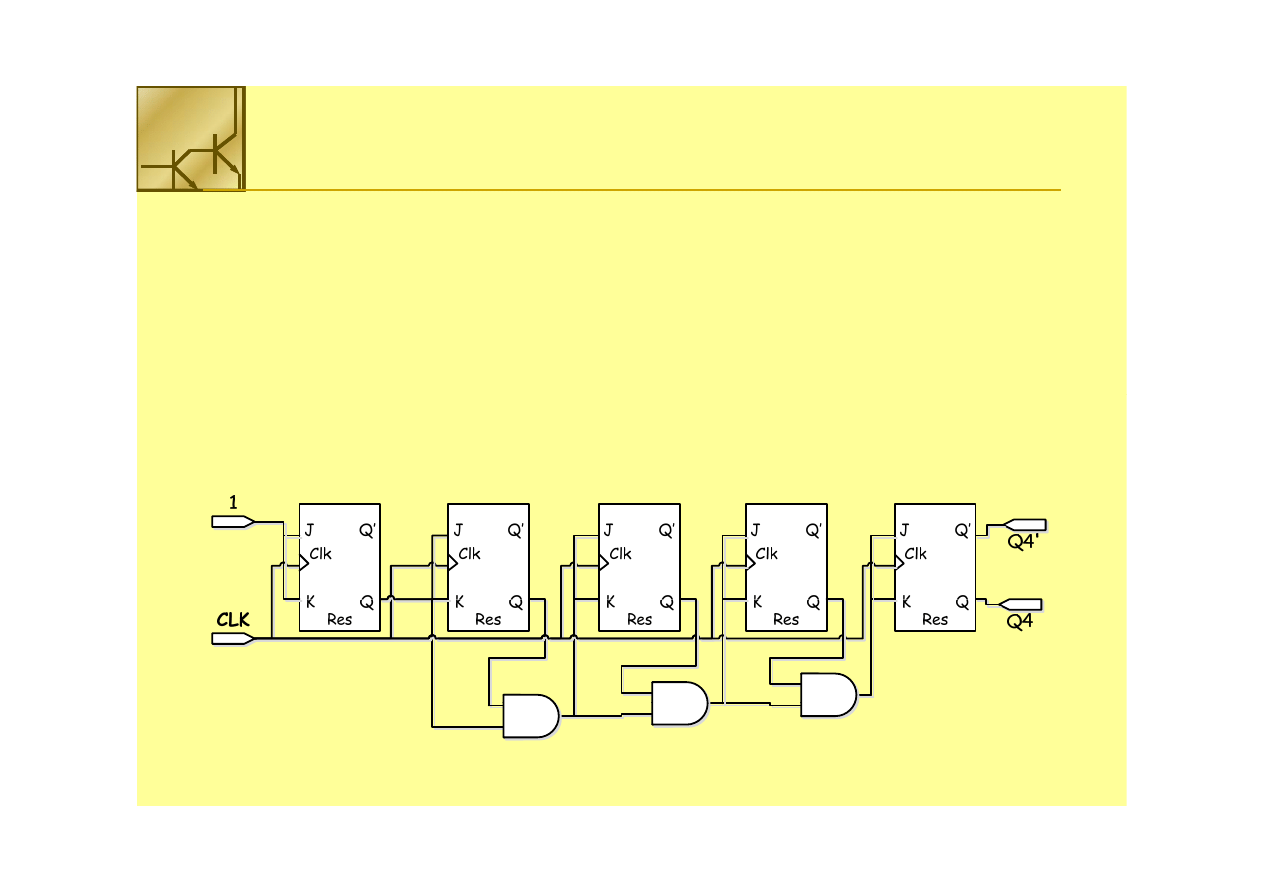

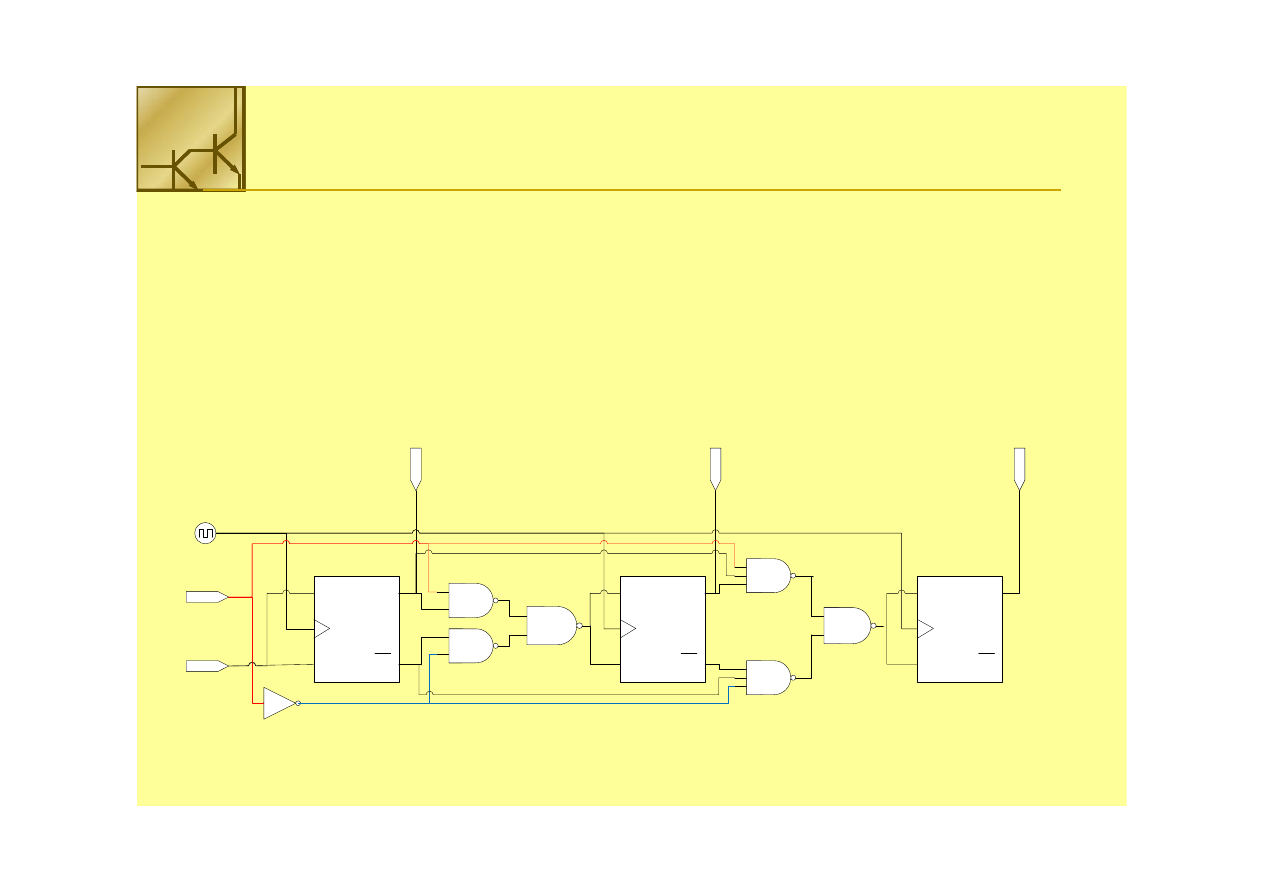

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

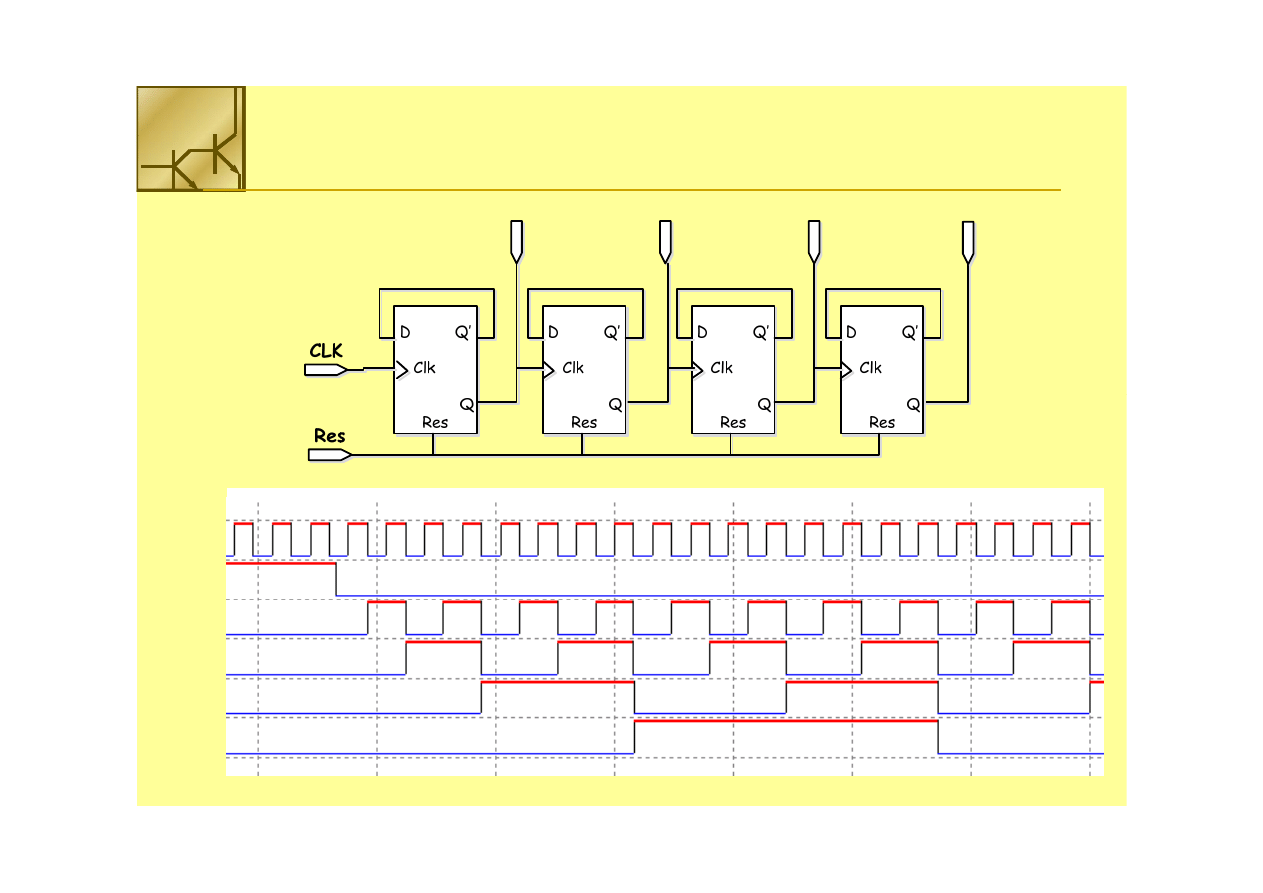

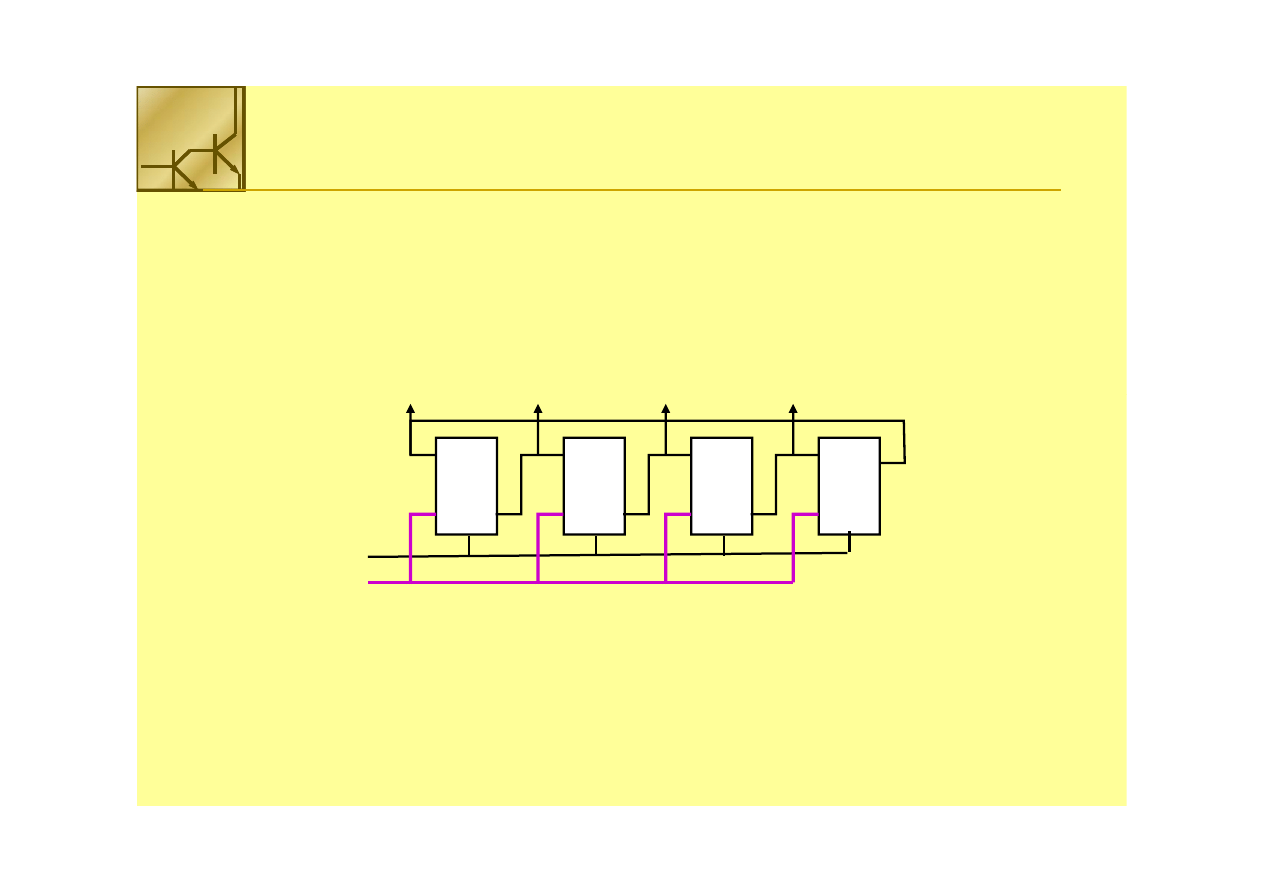

Asynchroniczny licznik binarny można

Asynchroniczny licznik binarny można

zrealizować przy pomocy

zrealizować przy pomocy

przerzutników JK tworząc łańcuch

przerzutników JK tworząc łańcuch

1

przerzutników JK, tworząc łańcuch

przerzutników JK, tworząc łańcuch

szeregowy w którym wejście zegarowe

szeregowy w którym wejście zegarowe

każdego

każdego przerzutnika jest połączone z

przerzutnika jest połączone z

wyjściem Q poprzedniego.

wyjściem Q poprzedniego.

J Q’

Clk

J Q’

Clk

J Q’

Clk

CLK

Clock

Clock X0

X0

X1

X1

X2

X2

Wejścia J=K=1, czyli licznik jest w

Wejścia J=K=1, czyli licznik jest w

stanie

stanie nQ

nQ

K Q

Res

K Q

Res

K Q

Res

Clock

Clock X0

X0

X1

X1

X2

X2

00

00

00

00

11

11

00

00

22

00

11

00

Clk

Clk

33

11

11

00

44

00

00

11

55

11

00

11

66

00

11

11

X0

X0

X1

X1

0

0 1

1 0

0 1

1 0

0 1

1 0

0 1

1 0

0

0

0 00

1 1 11

0 0 00

1

1 11

00

6 marca 2011

Wojciech Kucewicz

65

66

00

11

11

77

11

11

11

88

00

00

00

X2

X2

0

0 00

00

00

1 1

11

11

11

00

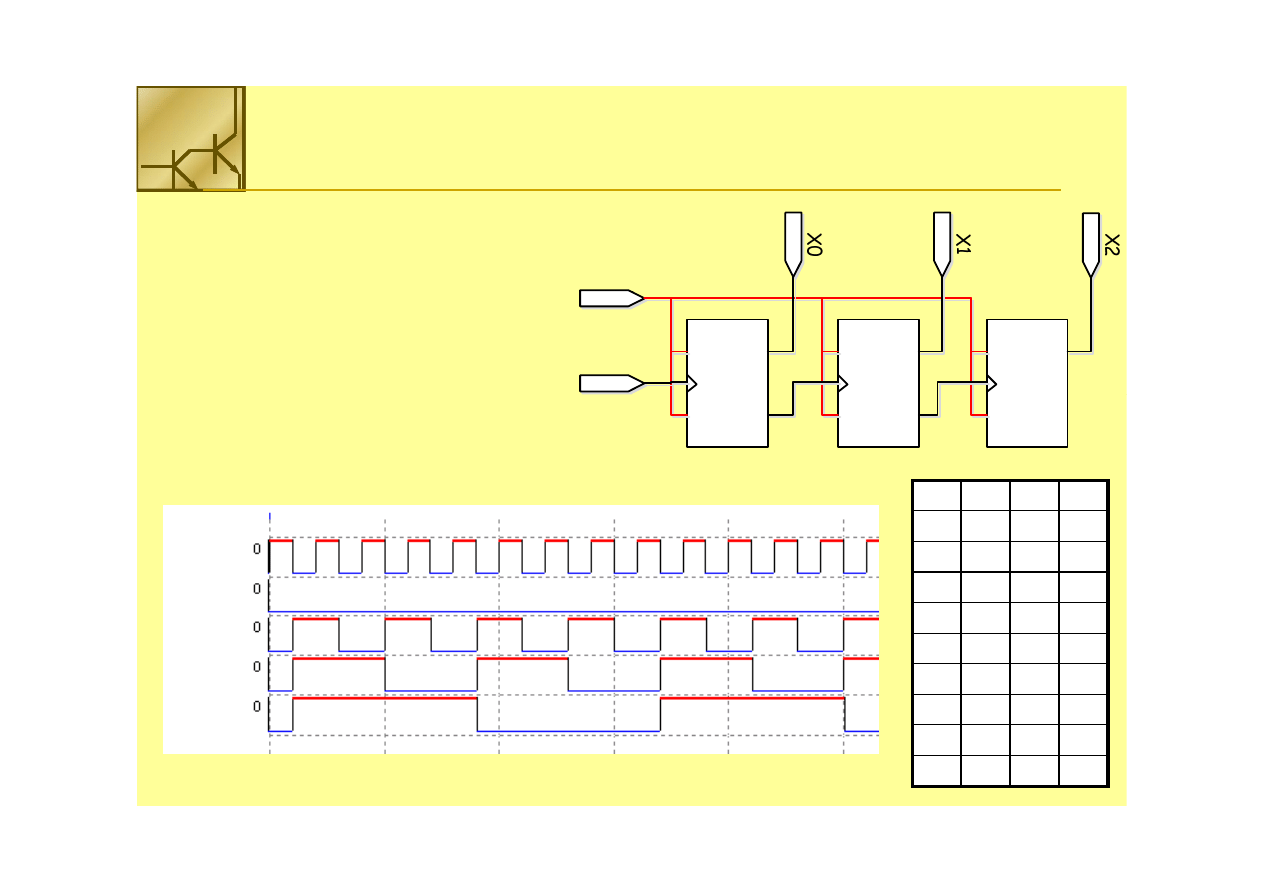

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

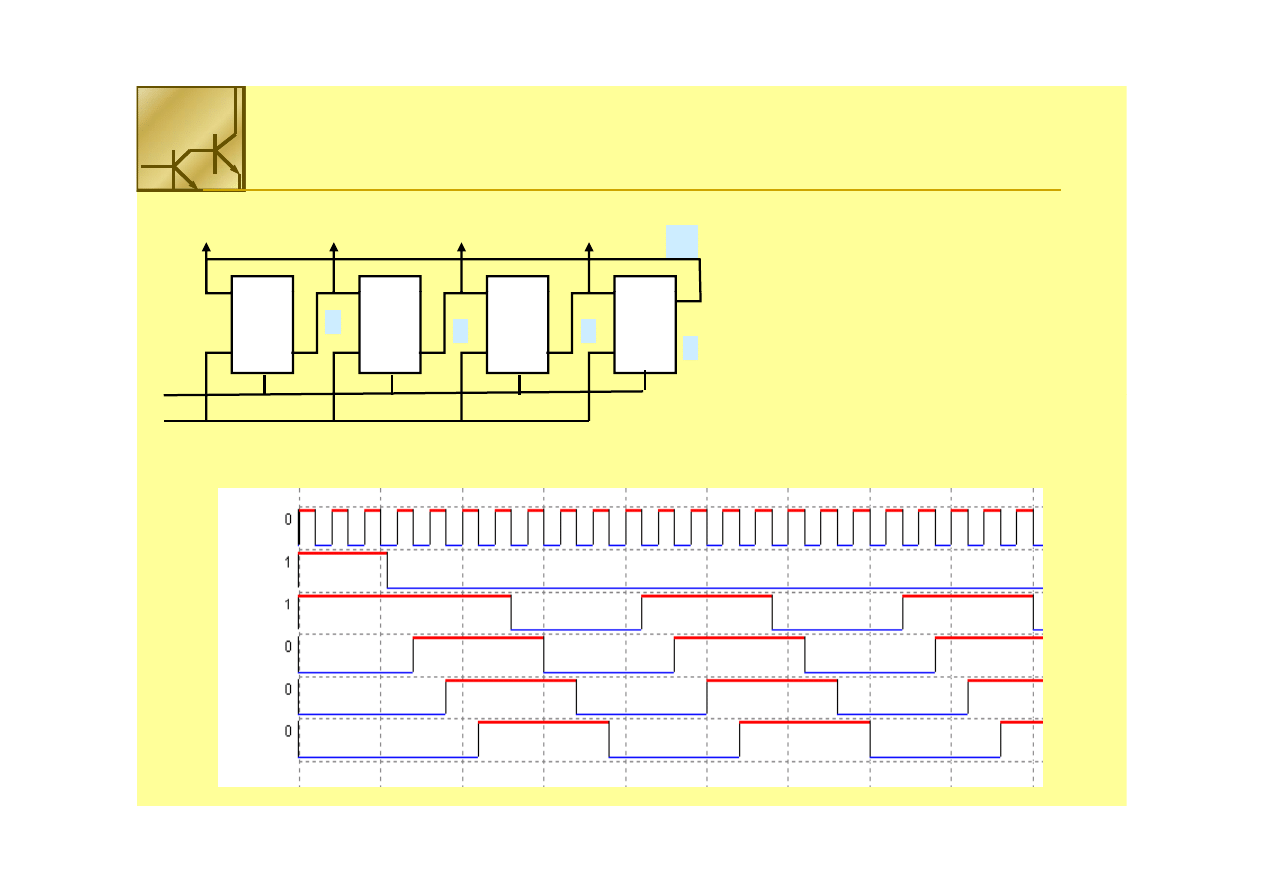

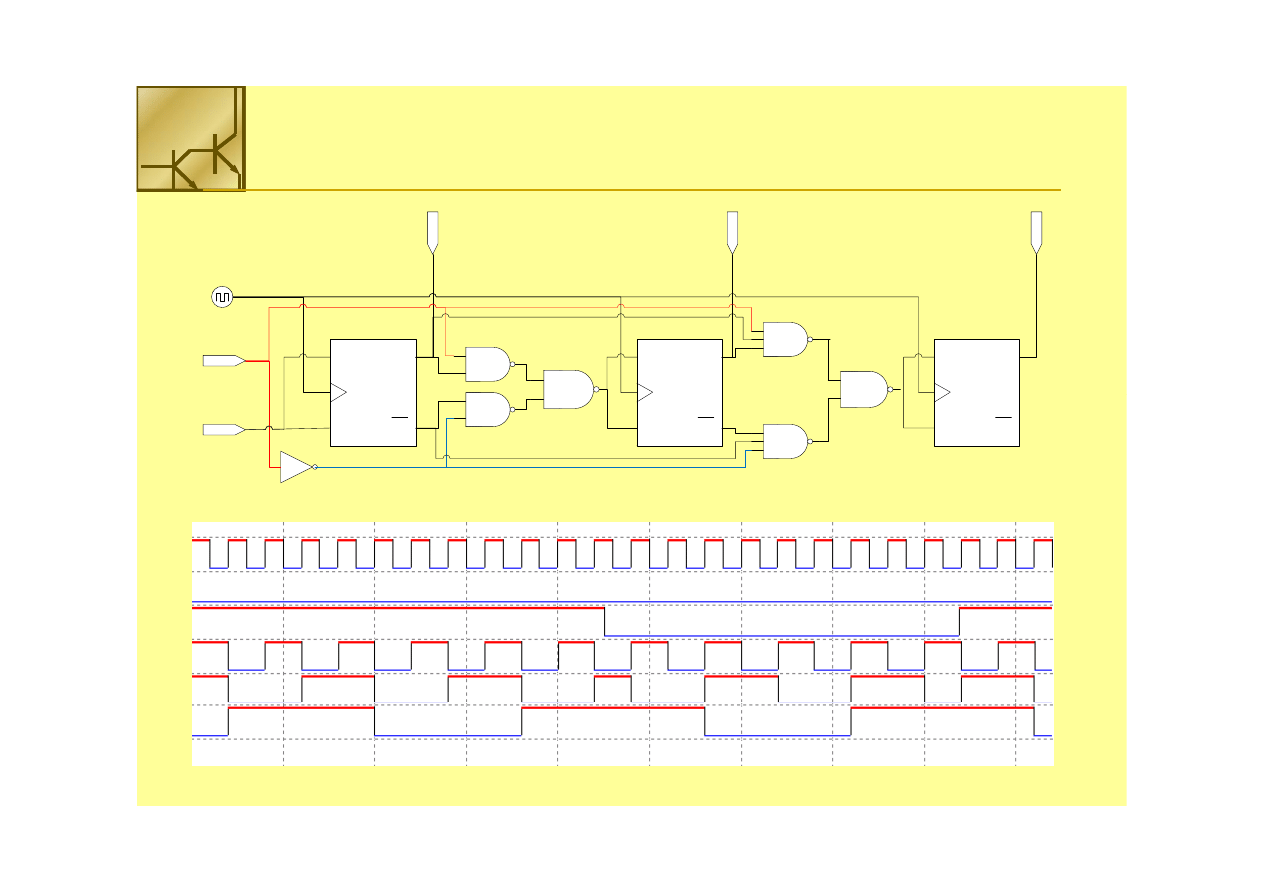

Licznik jest równocześnie dzielnikiem

Licznik jest równocześnie dzielnikiem

częstotliwości.

częstotliwości.

Częstotliwość na wyjściu kolejnego

Częstotliwość na wyjściu kolejnego

1

Częstotliwość na wyjściu kolejnego

Częstotliwość na wyjściu kolejnego

przerzutnika jest dwukrotnie niższa

przerzutnika jest dwukrotnie niższa

niż na wyjściu poprzedzającego

niż na wyjściu poprzedzającego

przerzutnika

przerzutnika

J Q’

Clk

J Q’

Clk

J Q’

Clk

CLK

K Q

Res

K Q

Res

K Q

Res

Clk

Clk

X0

X0

Í

Í

= f

= f

Í

Í

= f/2

= f/2

0 1 0 1 0 1 0 1 0

X1

X1

X2

X2

Í

Í

= f/2

= f/2

Í

Í

= f/4

= f/4

Í

Í

= f/8

= f/8

0 1 0 1 0 1 0 1 0

0 0

1 1

0 0

1 1

0

0 0

0 0

1 1

1

1

0

6 marca 2011

Wojciech Kucewicz

66

Í

Í

= f/8

= f/8

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

Licznik asynchroniczny z przerzutników JK

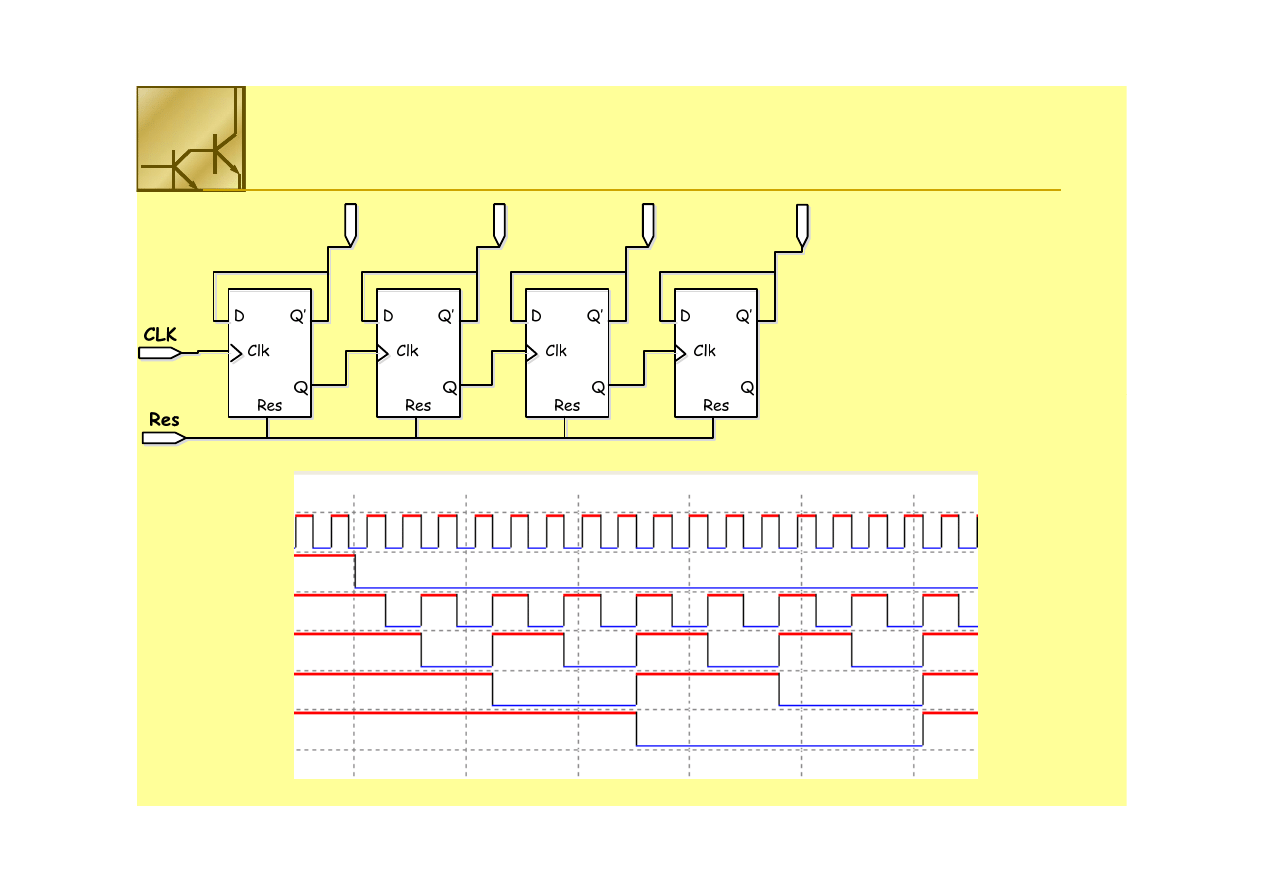

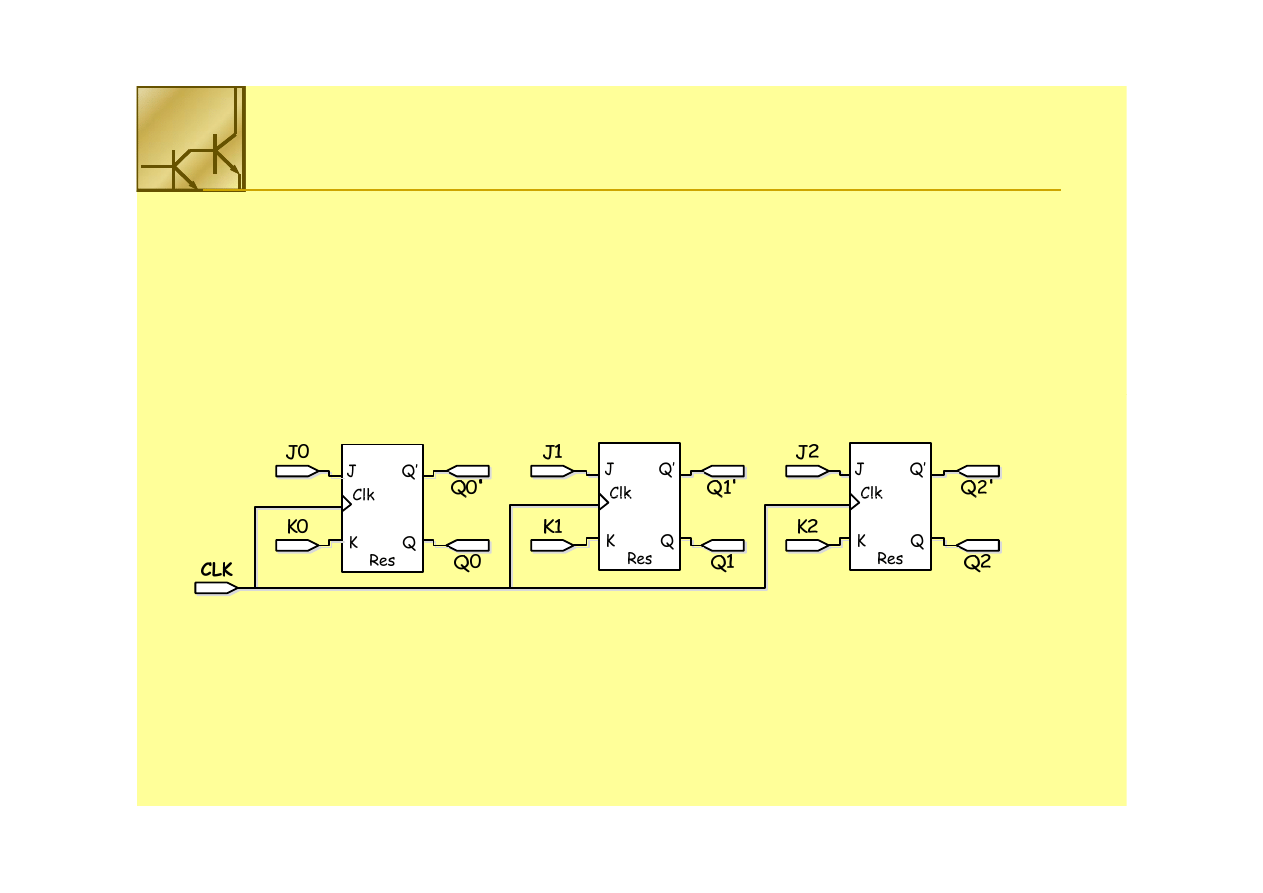

Obserwując stany wyjść

Obserwując stany wyjść nQ

nQ możemy

możemy

zrealizować licznik zliczający wstecz

zrealizować licznik zliczający wstecz

1

zrealizować licznik zliczający wstecz

zrealizować licznik zliczający wstecz

J Q’

Clk

J Q’

Clk

J Q’

Clk

CLK

Clock

Clock X0

X0

X1

X1

X2

X2

K Q

Res

K Q

Res

K Q

Res

Clock

Clock X0

X0

X1

X1

X2

X2

00

11

11

11

11

11

11

00

22

11

00

11

Clk

Clk

33

11

00

00

44

00

11

11

55

00

11

00

66

00

00

11

X0

X0

X1

X1

1 0 1 0 1 0 1 0 1

1 0 1 0 1 0 1 0 1

1 1 0 0 1 1 0 0 1

1 1 0 0 1 1 0 0 1

6 marca 2011

Wojciech Kucewicz

67

66

00

00

11

77

00

00

00

88

11

11

11

X2

X2

1 1 1 1 0 0 0 0 1

1 1 1 1 0 0 0 0 1

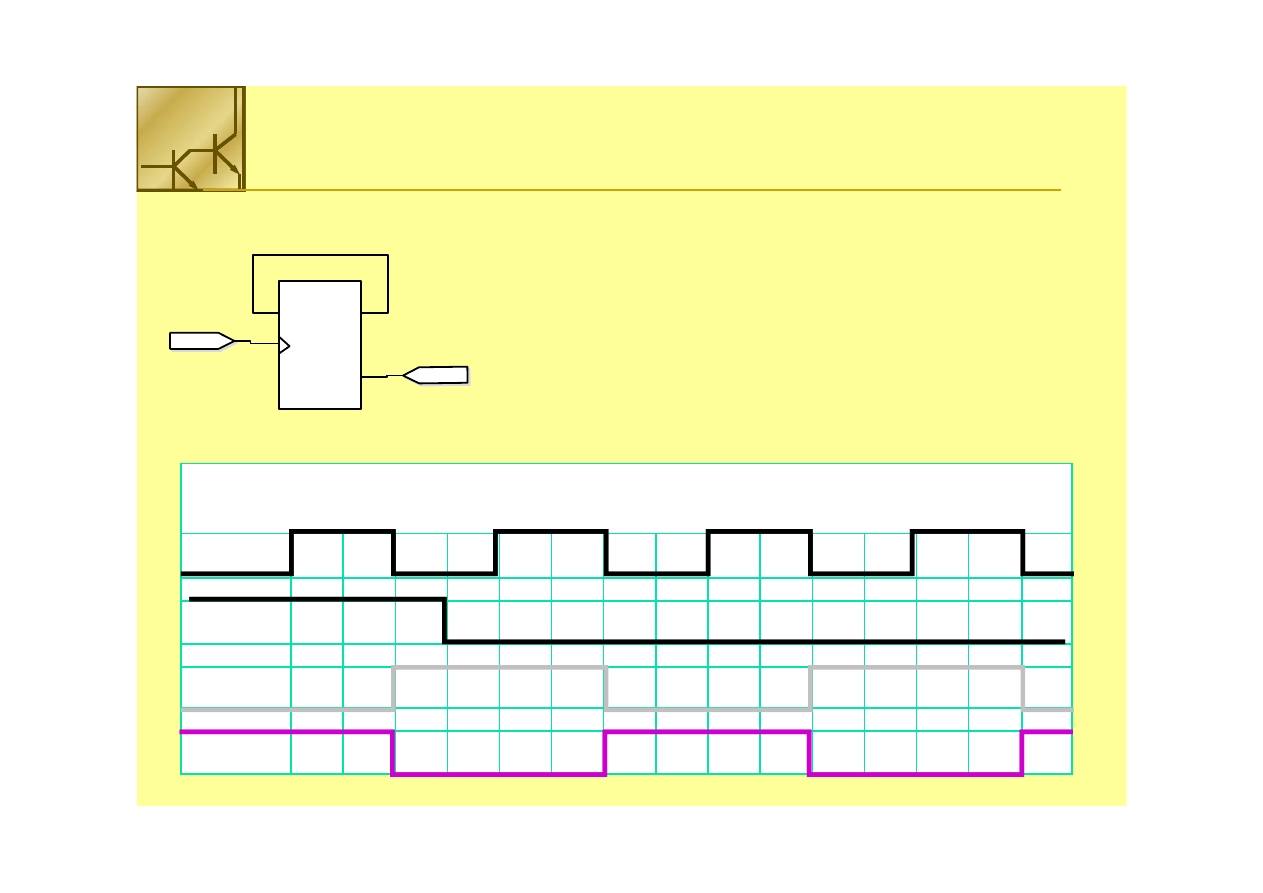

Licznik asynchroniczny z przerzutników D

Licznik asynchroniczny z przerzutników D

Licznik asynchroniczny z przerzutników D

Licznik asynchroniczny z przerzutników D

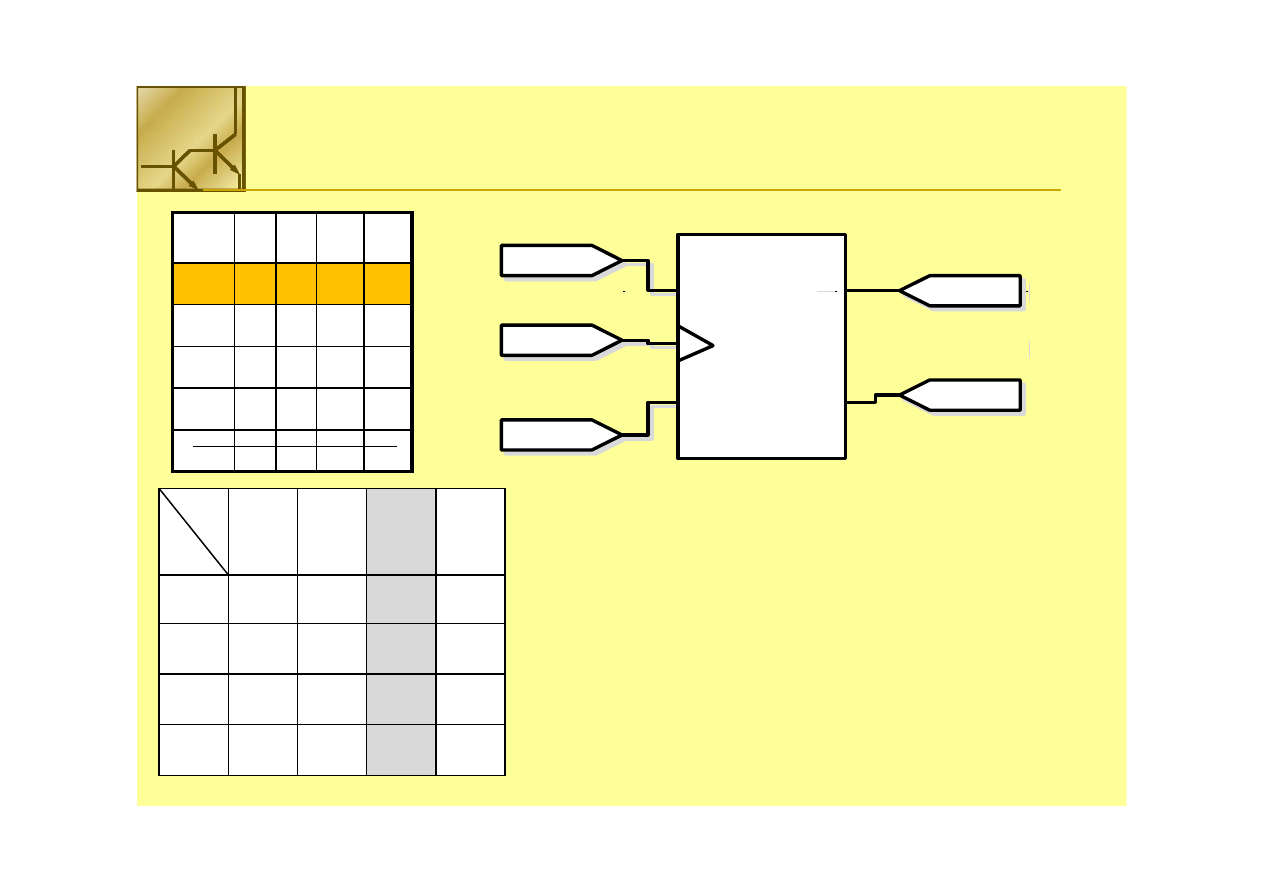

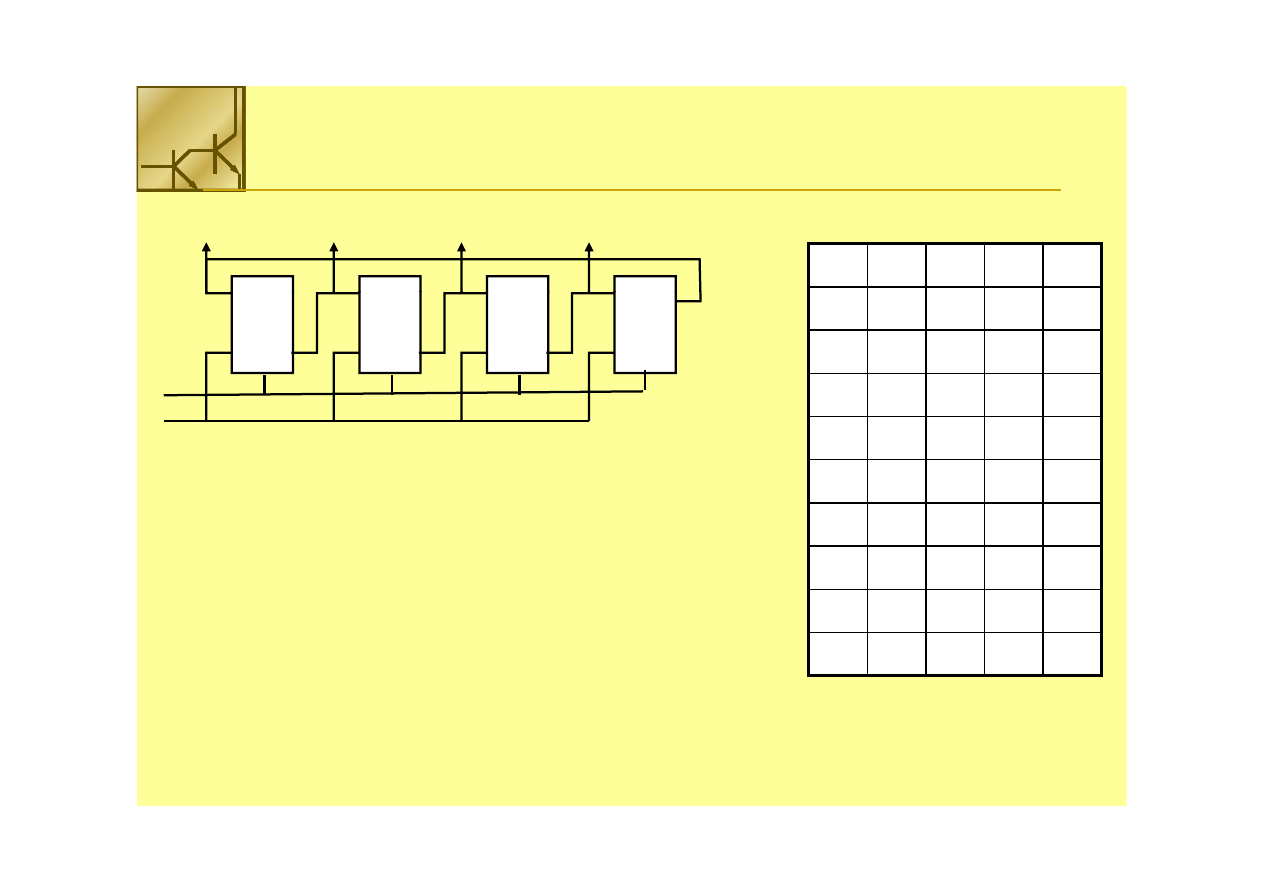

Asynchroniczny licznik dwójkowy można zrealizować tworząc

Asynchroniczny licznik dwójkowy można zrealizować tworząc

szeregowy łańcuch przerzutników D przy czym każdy ma

szeregowy łańcuch przerzutników D przy czym każdy ma

D Q’

Clk

Q

R s

CLK

Q

szeregowy łańcuch przerzutników D, przy czym każdy ma

szeregowy łańcuch przerzutników D, przy czym każdy ma

wyjście

wyjście nQ

nQ połączone z wejściem D oraz wyjście Q jednego

połączone z wejściem D oraz wyjście Q jednego

jest połączone z wejściem CLK następnego.

jest połączone z wejściem CLK następnego.

11

00

Res

Q

Licznik asynchroniczny

Licznik asynchroniczny

Licznik asynchroniczny

Licznik asynchroniczny

Clock

Clock

RR

D

D

6 marca 2011

Wojciech Kucewicz

68

Q

Q

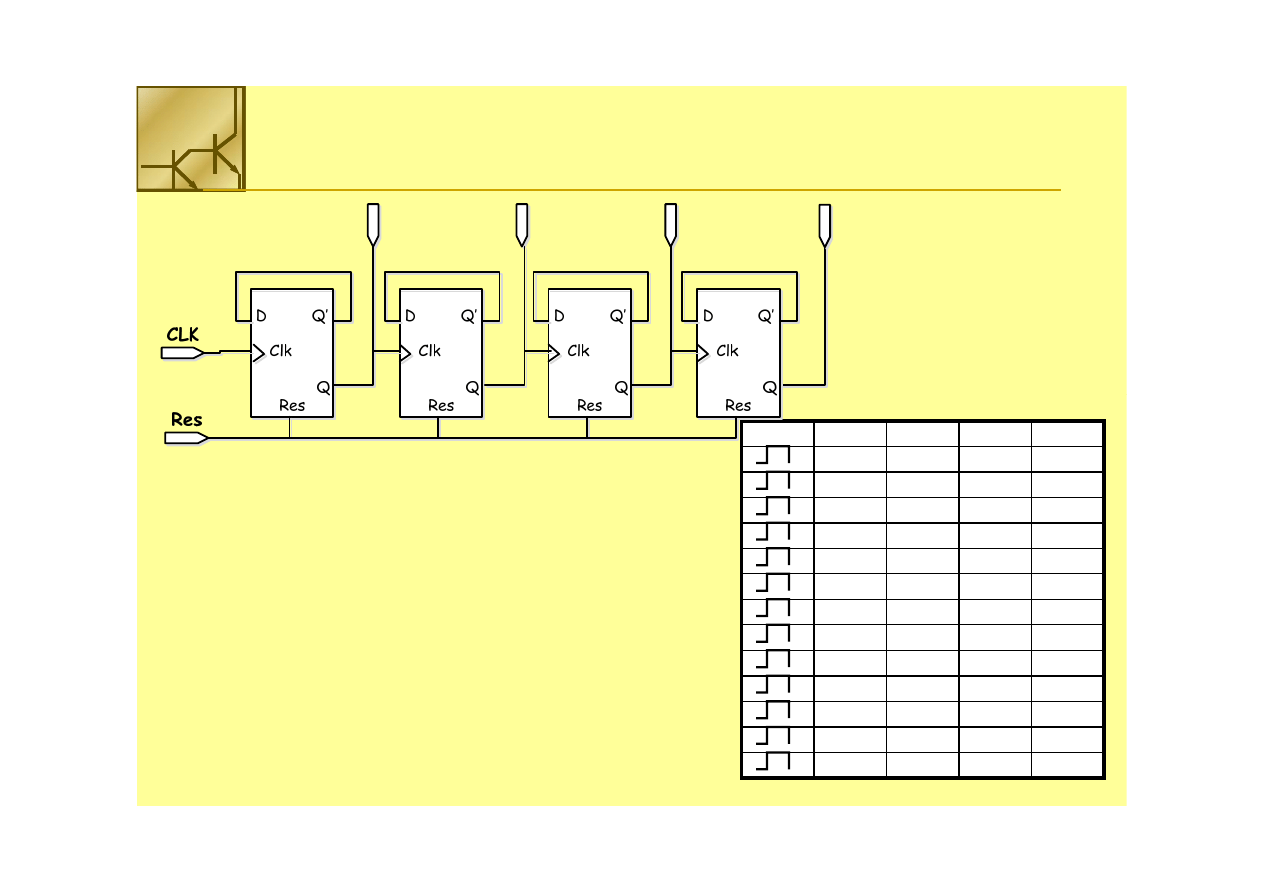

Licznik asynchroniczny

Licznik asynchroniczny

Licznik asynchroniczny

Licznik asynchroniczny

X0

X1

X2

X3

Clock

Clock

X0

X0

X1

X1

X2

X2

X3

X3

11

00

11

11

11

00

00

11

11

00

11

00

11

11

Przerzutnik D przełącza się przy

Przerzutnik D przełącza się przy

opadającym zboczu sygnału na wejściu

opadającym zboczu sygnału na wejściu

11

11

11

00

00

00

11

11

00

00

11

00

11

00

11

opadającym zboczu sygnału na wejściu

opadającym zboczu sygnału na wejściu

zegarowym

zegarowym

6 marca 2011

Wojciech Kucewicz

69

11

11

00

11

00

00

11

11

11

00

11

11

Licznik asynchroniczny liczący w przód

Licznik asynchroniczny liczący w przód

Licznik asynchroniczny liczący w przód

Licznik asynchroniczny liczący w przód

X0

X1

X2

X3

Clk

Clk

Res

Res

00

X0

X0

X1

X1

X2

X2

0

0 1

1 0

0 1

1 0

0 1

1 0

0 1

1 0

0 1 0 1

1 0 1 0 1 0 1 0

0 1 0 1 0

0

0 00 1 1 11 0

0 00 1 1 11 0 0 00 1 1 11

0 0 00

1 1 11

00

0

0 00 00 00 1

1 11 11 11 0

0 00 00 00

1

1 11

11 11

00

6 marca 2011

Wojciech Kucewicz

70

X

X

X3

X3

0

0 00 00 00 1

1 11 11 11 0

0 00 00 00

1

1 11

11 11

00

0

0 00 00 00 00

00 00 00 1

1 11

11 11

11 11

11 11

0

0

Licznik asynchroniczny liczący wstecz

Licznik asynchroniczny liczący wstecz

Licznik asynchroniczny liczący wstecz

Licznik asynchroniczny liczący wstecz

X0

X1

X2

X3

Aby licznik złożony z

Aby licznik złożony z

y

y

y

y

przerzutników D zliczał

przerzutników D zliczał

wstecz wystarczy

wstecz wystarczy

podłączyć wyjścia do

podłączyć wyjścia do

zanegowanych wyjść

zanegowanych wyjść

zanegowanych wyjść

zanegowanych wyjść

przerzutników

przerzutników

Clk

Clk

Res

Res

X0

X0

X0

X0

X1

X1

X2

X2

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1

1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1

6 marca 2011

Wojciech Kucewicz

71

X3

X3

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1

Licznik asynchroniczny modulo n

Licznik asynchroniczny modulo n

Licznik asynchroniczny modulo n

Licznik asynchroniczny modulo n

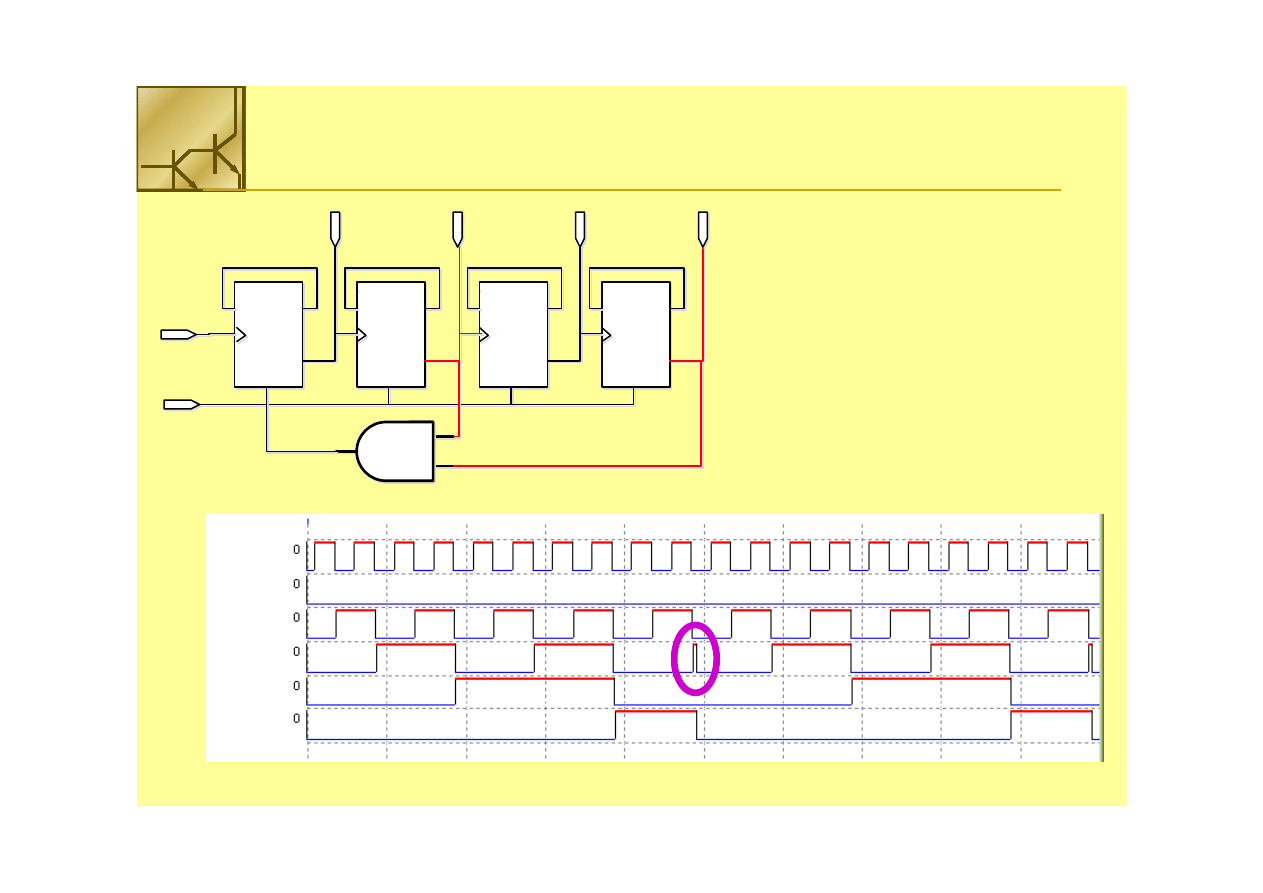

Licznik złożony z n przerzutników

Licznik złożony z n przerzutników

liczy od 0 do 2

liczy od 0 do 2

nn

–– 1. Aby uzyskać

1. Aby uzyskać

inny zakres licznika należy

inny zakres licznika należy

X0

X1

X2

X3

inny zakres licznika należy

inny zakres licznika należy

zastosować sprzężenie zwrotne,

zastosować sprzężenie zwrotne,

resetujące licznik po wymaganej

resetujące licznik po wymaganej

ilości stanów. Np. Można

ilości stanów. Np. Można

b d

ć li

ik d i i t

b d

ć li

ik d i i t

D Q’

Clk

Q

Res

CLK

D Q’

Clk

Q

Res

D Q’

Clk

Q

Res

D Q’

Clk

Q

Res

Res

zbudować licznik dziesiętny.

zbudować licznik dziesiętny.

Zanim licznik zostanie

Zanim licznik zostanie

wyzerowany pojawia się kawałek

wyzerowany pojawia się kawałek

następnego

następnego -- 10 impulsu.

10 impulsu.

Res

następnego

następnego 10 impulsu.

10 impulsu.

Clk

Clk

X0

X0

0 1 2 3 4 5 6 7 8 9 10

0 1 2 3 4 5 6 7 8 9 10

X0

X0

X1

X1

X2

X2

0 1 2 3 4 5 6 7 8 9 10

0 1 2 3 4 5 6 7 8 9 10

6 marca 2011

Wojciech Kucewicz

72

X3

X3

Licznik asynchroniczny modulo n

Licznik asynchroniczny modulo n

Licznik asynchroniczny modulo n

Licznik asynchroniczny modulo n

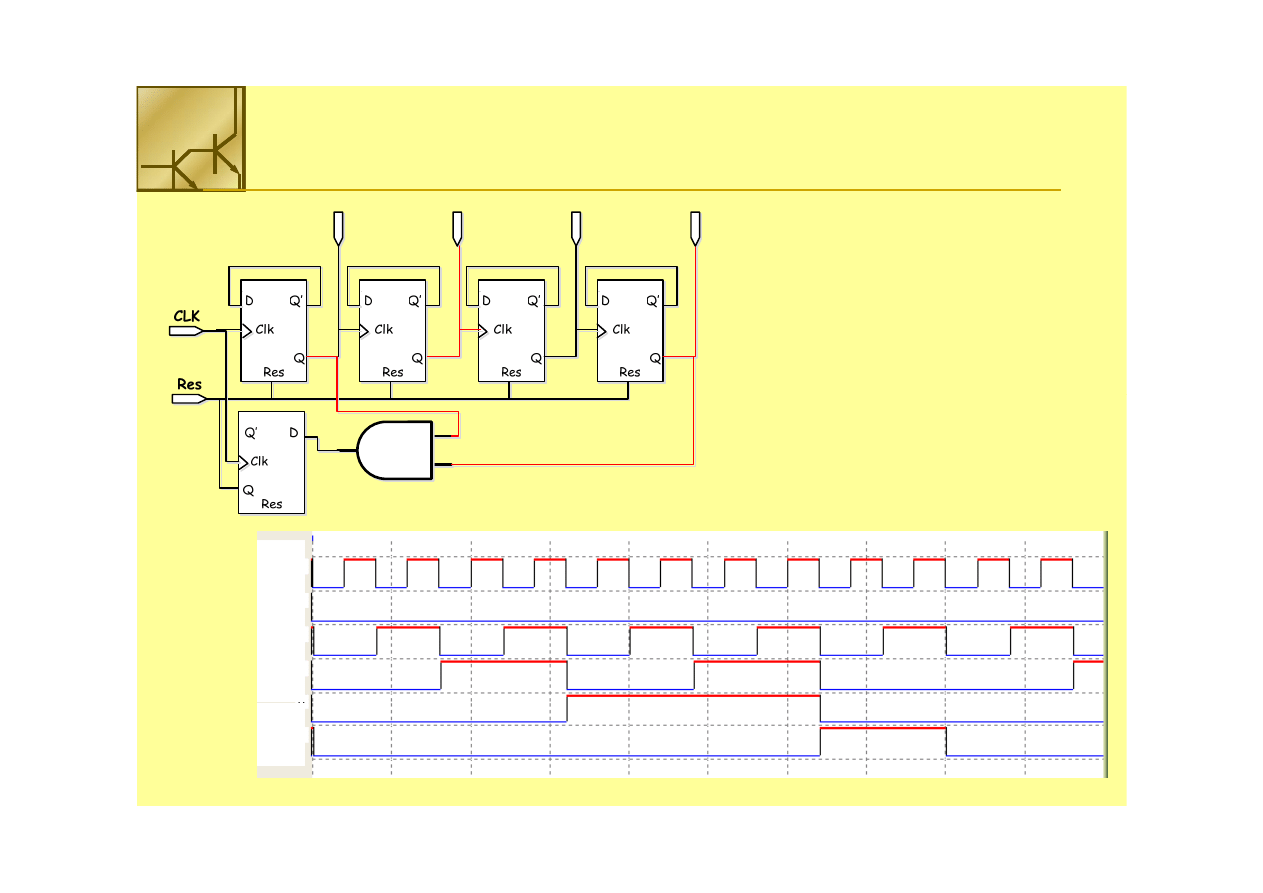

Problem można rozwiązać

Problem można rozwiązać

stosując na wyjściu resetującym

stosując na wyjściu resetującym

X0

X1

X2

X3

ją

yj

ją ym

ją

yj

ją ym

przerzutnik, który zresetuje

przerzutnik, który zresetuje

liczniki dopiero przy opadającym

liczniki dopiero przy opadającym

zboczu zegara

zboczu zegara

Clk

Clk

1 4 6

1 4 6

X0

X0

X1

X1

X2

X2

0 1 2 3 4 5 6 7 8 9 0

0 1 2 3 4 5 6 7 8 9 0

6 marca 2011

Wojciech Kucewicz

73

X2

X2

X3

X3

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

Liczniki

synchroniczne

synchroniczne

Liczniki

Liczniki

synchroniczne

synchroniczne

synchroniczne

synchroniczne

synchroniczne

synchroniczne

6 marca 2011

Wojciech Kucewicz

74

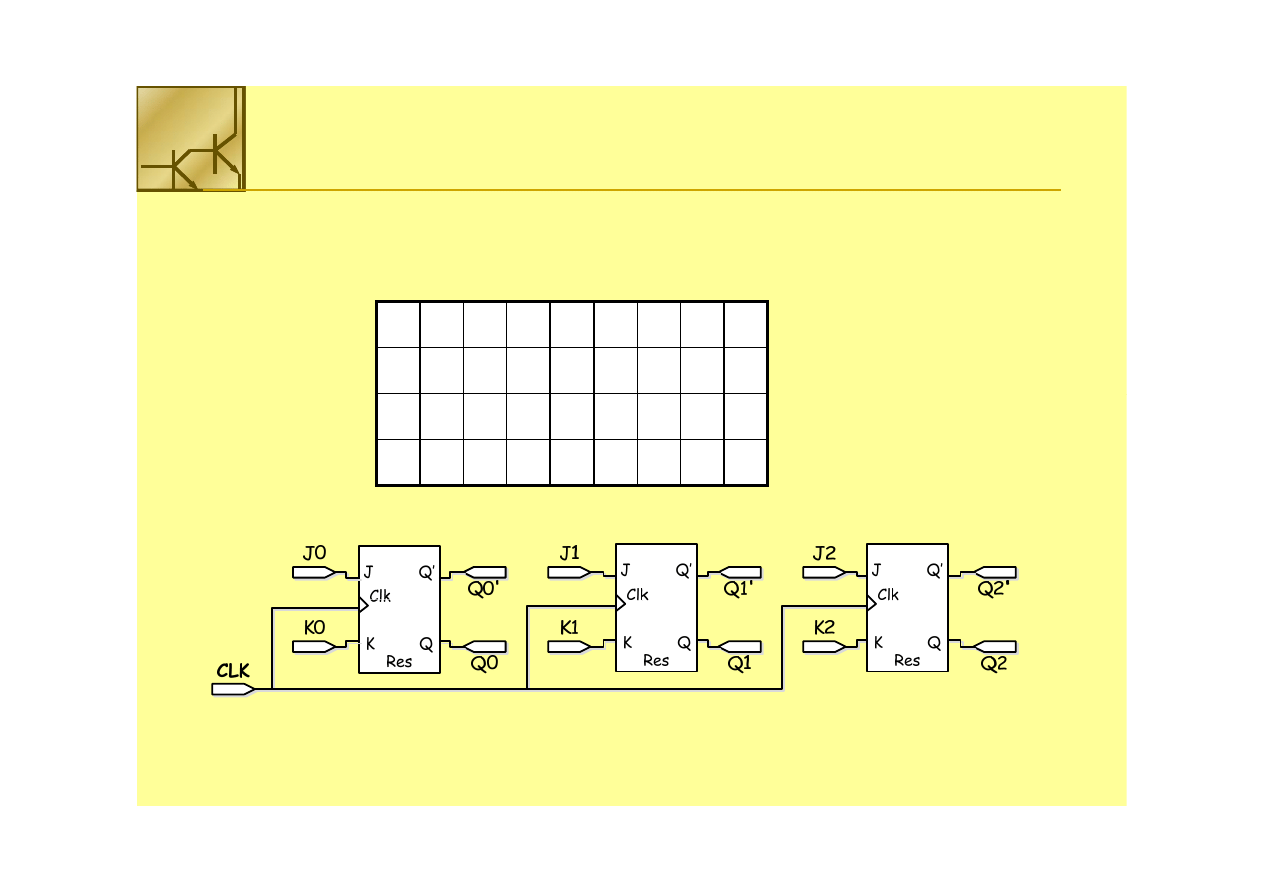

Liczniki synchroniczne

Liczniki synchroniczne

Liczniki synchroniczne

Liczniki synchroniczne

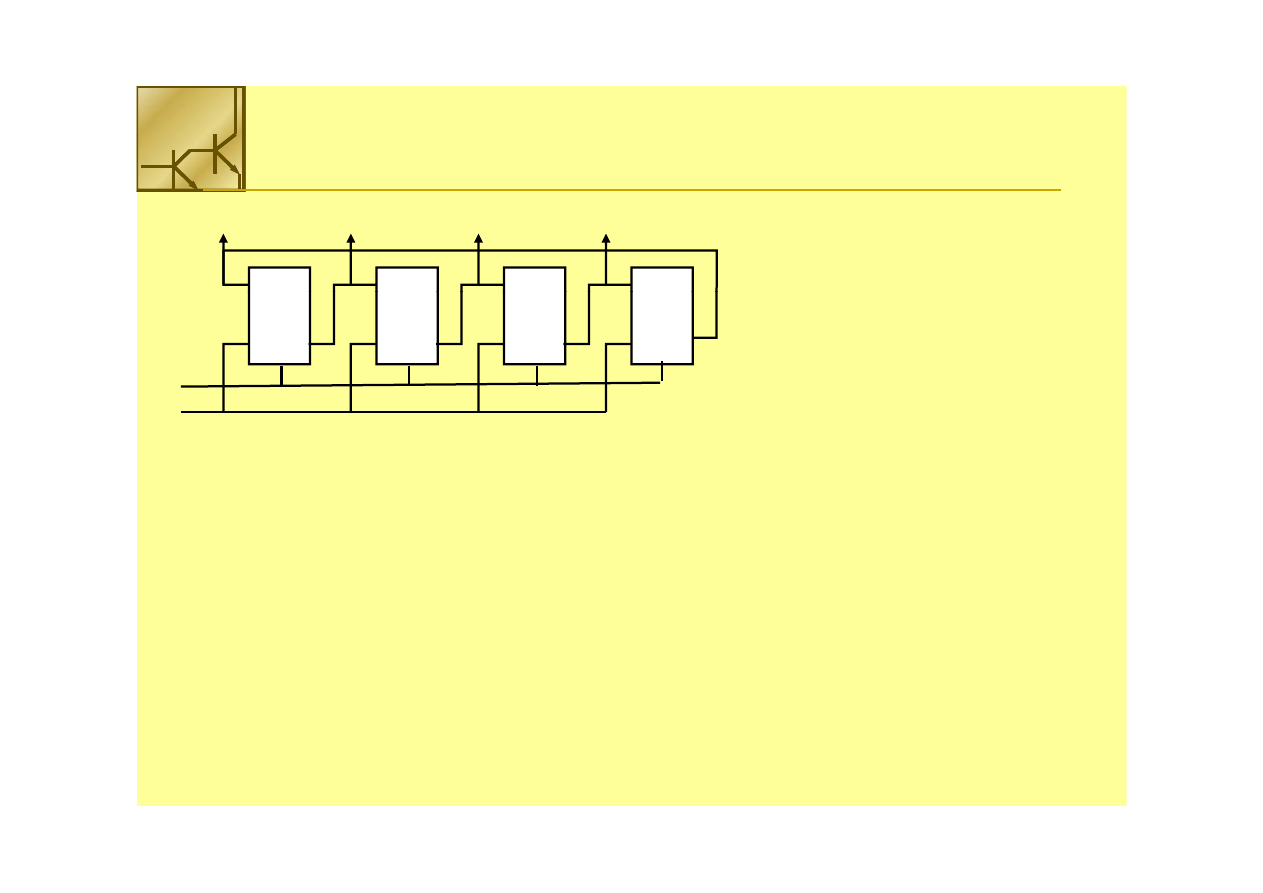

Liczniki synchroniczne charakteryzują się tym, że zliczane impulsy są

Liczniki synchroniczne charakteryzują się tym, że zliczane impulsy są

p d

n ró n cz śni n sz stki jści z

r

p d

n ró n cz śni n sz stki jści z

r

Clk

Clk prz rzutnikó

prz rzutnikó

X0

X0

X1

X1

X2

X2

X3

X3

podawane równocześnie na wszystkie wejścia zegarowe

podawane równocześnie na wszystkie wejścia zegarowe Clk

Clk przerzutników.

przerzutników.

D

D nQ

nQ

Clk Q

Clk Q

D

D nQ

nQ

Clk Q

Clk Q

D

D nQ

nQ

Clk Q

Clk Q

X0

X0

X1

X1

X2

X2

D

D nQ

nQ

Clk Q

Clk Q

X3

X3

Clk

Clk

Clk Q

Clk Q

RR

Reset

Reset

Clk Q

Clk Q

RR

Clk Q

Clk Q

RR

Clk Q

Clk Q

RR

6 marca 2011

Wojciech Kucewicz

75

Licznik pierścieniowy

Licznik pierścieniowy

Licznik pierścieniowy

Licznik pierścieniowy

D

D nQ

nQ

D

D nQ

nQ

D

D nQ

nQ

X0

X0

X1

X1

X2

X2

D

D nQ

nQ

X3

X3

Clk

Clk

Clk Q

Clk Q

RR

Reset

Reset

Clk Q

Clk Q

RR

Clk Q

Clk Q

RR

Clk Q

Clk Q

RR

Clk

Clk

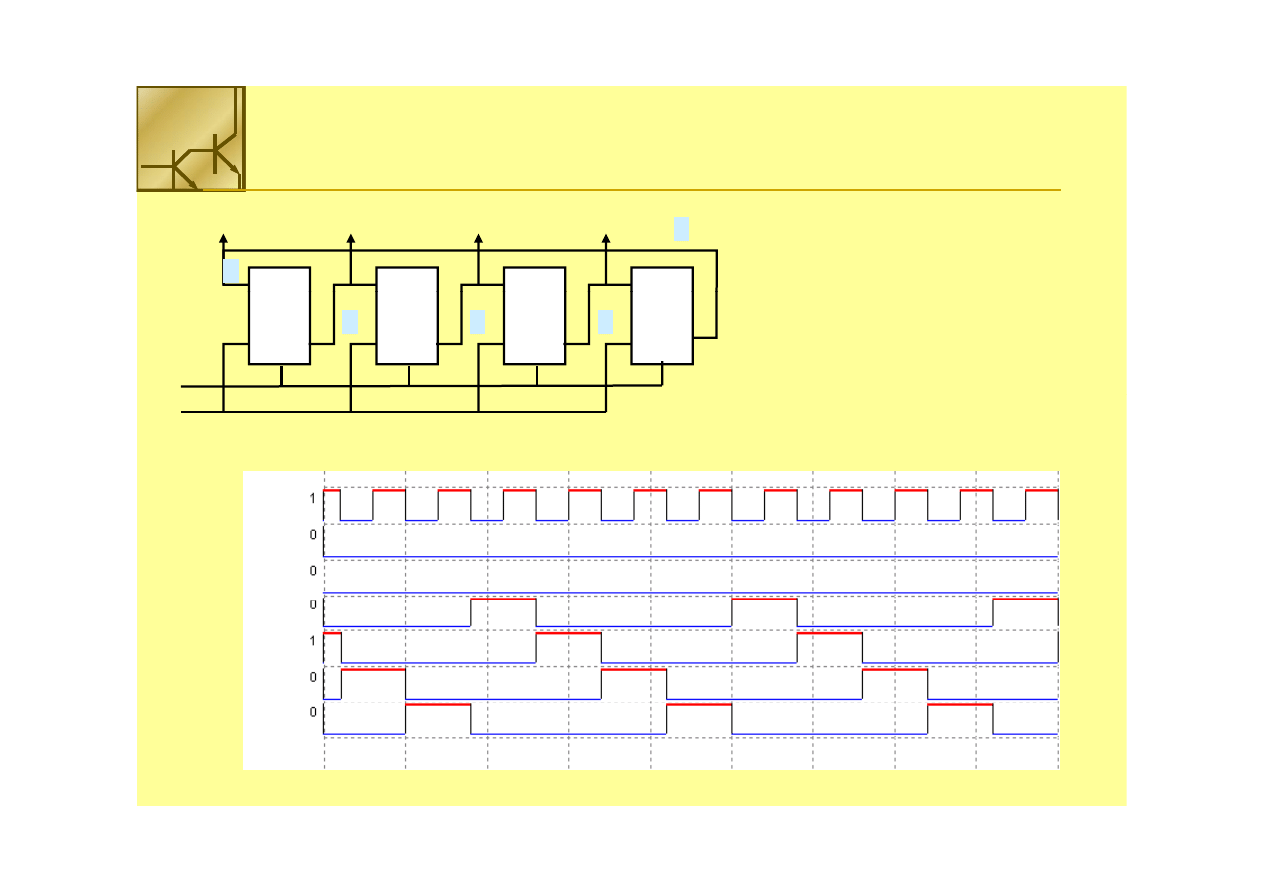

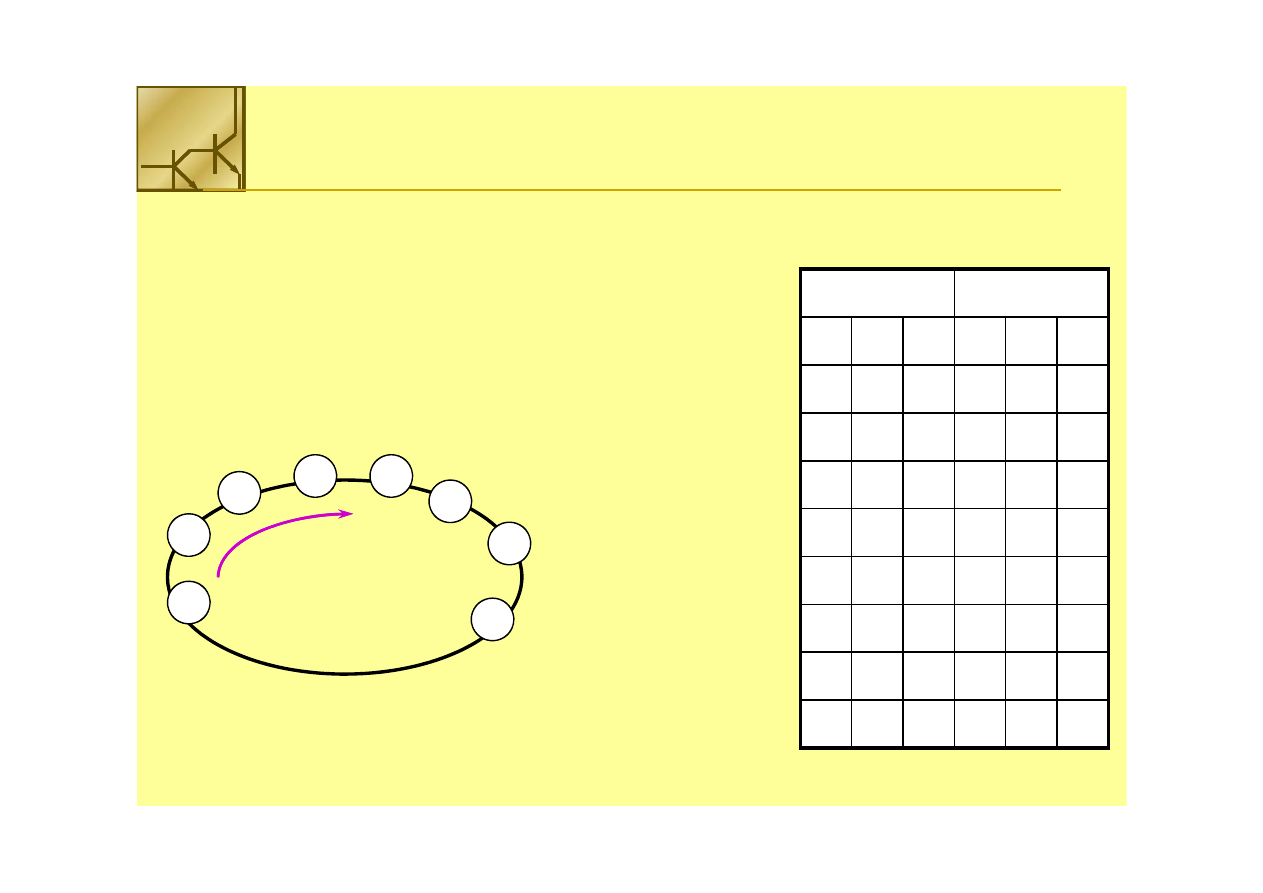

Licznik pierścieniowy (ring

Licznik pierścieniowy (ring counter

counter) jest licznikiem synchronicznym

) jest licznikiem synchronicznym

Licznik pierścieniowy (ring

Licznik pierścieniowy (ring counter

counter) jest licznikiem synchronicznym.

) jest licznikiem synchronicznym.

Powstaje w wyniku utworzenia rejestru przesuwnego, w którym wyjście Q

Powstaje w wyniku utworzenia rejestru przesuwnego, w którym wyjście Q

ostatniego przerzutnika jest połączone z wejście D pierwszego

ostatniego przerzutnika jest połączone z wejście D pierwszego

przerzutnika.

przerzutnika.

przerzutn ka.

przerzutn ka.

Jeżeli w rejestrze zostanie wpisany stan początkowy np. 1000 to będzie on

Jeżeli w rejestrze zostanie wpisany stan początkowy np. 1000 to będzie on

w kolejnych cyklach zegarowych przesuwany wzdłuż rejestru.

w kolejnych cyklach zegarowych przesuwany wzdłuż rejestru.

6 marca 2011

Wojciech Kucewicz

76

j y

y

g

y

p

y

j

j y

y

g

y

p

y

j

Licznik pierścieniowy

Licznik pierścieniowy

Licznik pierścieniowy

Licznik pierścieniowy

D

D nQ

nQ

D

D nQ

nQ

D

D nQ

nQ

X0

X0

X1

X1

X2

X2

D

D nQ

nQ

X3

X3

Na każdym wyjściu licznika

Na każdym wyjściu licznika

pierścieniowego jest generowany

pierścieniowego jest generowany

w różnym czasie tylko jeden

w różnym czasie tylko jeden

00

1100

11

11

Clk

Clk

Clk Q

Clk Q

RR

Reset

Reset

Clk Q

Clk Q

RR

Clk Q

Clk Q

RR

Clk Q

Clk Q

RR

y

y

j

y

y

j

impuls (1) o czasie trwania

impuls (1) o czasie trwania

równym okresowi sygnału

równym okresowi sygnału

zegarowego.

zegarowego.

Te impulsy mogą być

Te impulsy mogą być

11

11

00

11

00

00

Clk

Clk

Clk

Clk

Te impulsy mogą być

Te impulsy mogą być

wykorzystane do sterowania np.

wykorzystane do sterowania np.

wewnętrznych bloków komputera.

wewnętrznych bloków komputera.

Res

Res

X0

X0

X1

X1

X2

X2

6 marca 2011

Wojciech Kucewicz

77

X3