Politechnika Lubelska w Lublinie |

Laboratorium elektronicznych układów analogowych i cyfrowych |

|||

|

Ćwiczenie Nr 8 |

|||

Imię i nazwisko: Tadeusz Klukowski

|

Semestr VII |

Grupa ED 7.1 |

Rok akad. 1999/2000 |

|

Temat ćwiczenia: Rejestr rewersyjny o długości 4 bity szeregowo- rewersyjny.

|

Data wykonania 14.12.99 |

Ocena

|

||

Założenia i cel ćwiczenia:

Celem ćwiczenia było zaprojektowanie rejestru rewersyjnego o długości 4 bity szeregowo-równoległego.

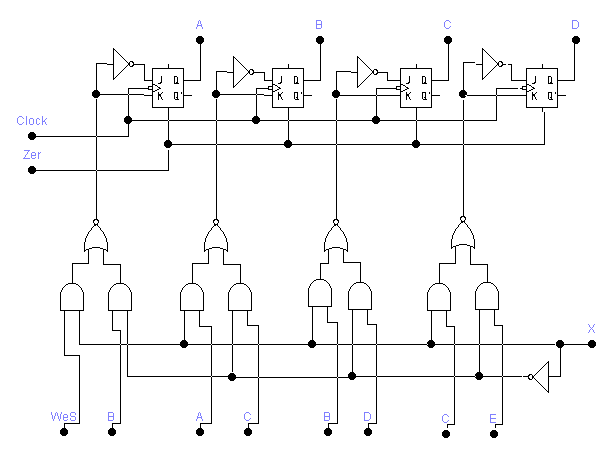

Schemat pomiarowy:

Na wykresie zastosowano następujące oznaczenia:

WeS- wejście szeregowe

Clock- zegar taktujący

Zer- zerowanie układu

A,B,C,D,E- wyjścia równoległe rejestru

X- w zależności od podanego stanu realizuje przesuwanie w lewo (0) lub w prawo (1)

Po sprawdzeniu działania układu potwierdzonego przez prowadzącego zajęcia można stwierdzić, że układ realizuje założenia ćwiczenia.

Wnioski:

W ćwiczeniu mieliśmy za zadanie zbadanie układu rejestrującego rewersyjnego o długości 4 bity szeregowo-równoległego. Schemat realizujący założenia ćwiczenia został przedstawiony powyżej. W ćwiczeniu układ został zrealizowany na układach przerzutników JK oraz na bramkach NOR, AND i NOT. Przerzutniki JK zrealizowane zostały poprzez układy 74107, które zawierają w swojej strukturze po dwa przerzutniki JK. Za realizację bramek AND i NOR posłużyły nam układy 7451, które w swojej strukturze zawierają po dwie bramki AND i jedną bramkę NOR. Bramki NOT zostały zrealizowane na układach 7404. Układ ten zawiera sześć bramek NOT. Po przeprowadzeniu ćwiczenia możemy stwierdzić, że przedstawiony układ realizuje bezbłędnie zadane funkcje logiczne.

Wyszukiwarka

Podobne podstrony:

Tadek 5, Studia, sprawozdania, sprawozdania z układów elektronicznych

Tadek3 PID, Studia, sprawozdania, sprawozdania z układów elektronicznych

regulatorPID-3, Studia, sprawozdania, sprawozdania z układów elektronicznych

el4, Studia, sprawozdania, sprawozdania z układów elektronicznych

elektronika6, Studia, sprawozdania, sprawozdania z układów elektronicznych

elektronika4d, Studia, sprawozdania, sprawozdania z układów elektronicznych

elektronika9d, Studia, sprawozdania, sprawozdania z układów elektronicznych

elektronika3, Studia, sprawozdania, sprawozdania z układów elektronicznych

el1, Studia, sprawozdania, sprawozdania z układów elektronicznych

PID, Studia, sprawozdania, sprawozdania z układów elektronicznych

M2, Studia, sprawozdania, sprawozdania z układów elektronicznych

Politechnika Lubelska bezpieczniki, Studia, sprawozdania, sprawozdania z układów elektronicznych

protokół - multiplekser, Studia, sprawozdania, sprawozdania z układów elektronicznych

Tadek1, Studia, sprawozdania, sprawozdania z układów elektronicznych

elektronika1, Studia, sprawozdania, sprawozdania z układów elektronicznych

m9, Studia, sprawozdania, sprawozdania z układów elektronicznych

el9, Studia, sprawozdania, sprawozdania z układów elektronicznych

Tadek9 multip, Studia, sprawozdania, sprawozdania z układów elektronicznych

więcej podobnych podstron