II.

Zagadnienia obowiązujące do części „Mikrokontrolery”:

1.

Definicja mikrokontrolera (w skrócie: mk), dwie najważniejsze cechy techniczne jego

jednostki centralnej.

Mikrokontroler definicja:

–

układ cyfrowy z wyspecjalizowanym mikroprocesorem i niezbędnymi do jego samodzielnej pracy

urządzeniami zawartymi w jednym układzie scalonym

–

zdolny do autonomicznej pracy (nie wymaga układów pomocniczych)

–

zaprojektowany do pracy w systemach kontrolno-pomiarowych i komunikacyjnych, stąd posiada

rozbudowany system komunikacji z otoczeniem

–

pracuje w czasie rzeczywistym

Cechy jednostki centralnej:

–

szerokość szyny danych (8, 16, 32 bity)

–

częstotliwość sygnału taktującego. Jej wartość powinna być jak najmniejsza, ponieważ pobór mocy

jest proporcjonalny do częstotliwości sygnału taktującego, ale jednocześnie na tyle duża, aby

zapewnić minimalną wymaganą prędkość przetwarzania danych

2.

·

Uszczegółowiona budowa mk oraz funkcje realizowane przez jego bloki.

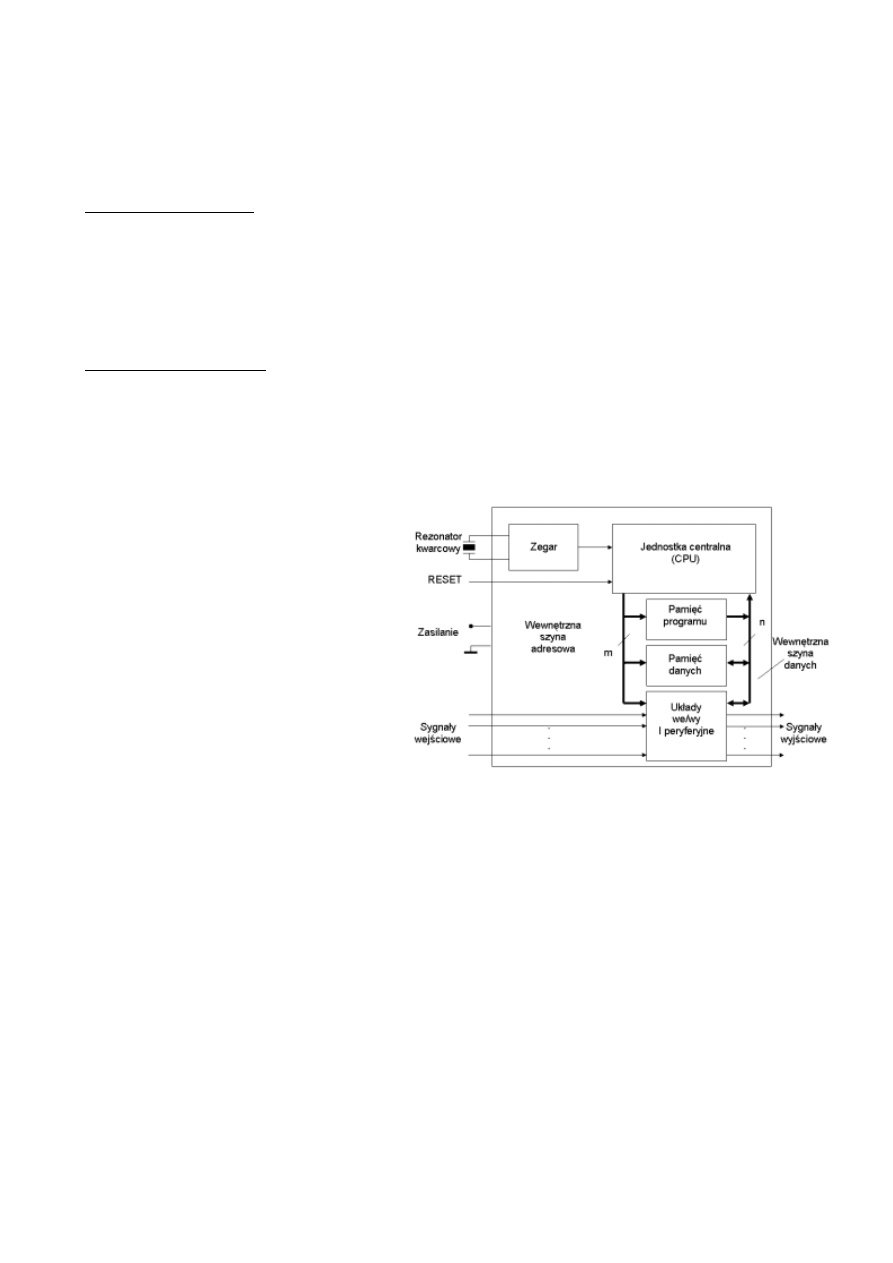

–

j.c. realizuje program zawarty w

pamięci programu (ROM, FLASH)

–

zmienne programu przechowywane są

w pamięci danych RAM

–

j.c. jest taktowana zegarem, którego

częstotliwość jest stabilizowana

oscylatorem kwarcowym

–

mk jest wprowadzany w stan

początkowy sygnałem RESET

–

układy peryferyjne umożliwiają oczyt

sygnałów wejściowych cyfrowym i

analogowych oraz generację sygnałów

wyjściowych stosowanych do

sterowania układami mse

3.

·

Cechy mk wyróżniające go spośród innych układów cyfrowych z wbudowanym

mikroprocesorem.

–

zamknięcie magistrali danych i adresowej wewnątrz układu scalonego

–

stała struktura pamięci RAM/ROM

–

stałość programu sterującego

–

dostęp do rejestrów procesora i układów we/wy poprzez mechanizm adresowania pamięci RAM

–

rejestrowa struktura j.c.

–

Procesory boolowskie wykonujące operacje na pojedynczych bitach w pamięci, rejestrach i układach

we/wy

–

bogaty zestaw urządzeń we/wy

–

rozbudowane i szybkie układy przerwań we/wy

–

różnorodne tryby i środki redukcji mocy pobieranej

–

rozbudowane mechanizmy kontroli i detekcji nieprawidłowych stanów mk

–

zawarcie w jednej strukturze układów cyfrowych i analogowych

4.

·

Pełnione funkcje i typy pamięci zaimplementowanych w mk.

Podział ze względu na pełnione funkcje:

–

pamięć programu, zawierająca kod programu, tablice stałych, wektor resetu i przerwań

–

pamięć danych, przechowująca zmienne

–

stos sprzętowy (obsługa przerwań i wywołań funkcji – przechowuje bieżącą wartość licznika)

–

pamięć EEPROM – przechowuje zmienne i tablice stałych, które nie mogą ulec skasowaniu

Podział pamięci programu:

–

ROM – pamięć stała umożliwiająca tylko odczytywanie swojej zawartości, nieprogramowalna

–

EPROM – pamięć z możliwością kasowania dotychczasowej zawartości i wprowadzenia nowej

zawartości

–

OTP – pamięci typu EPROM, możliwe jest tylko jednokrotne zaprogramowanie bez możliwości

skasowania zawartości

–

FLASH – pamięć z mozliwością kasowania zawartości i programowania bezpośrednio w systemie

mikroprocesorowym

5.

·

Struktury mk ze względu na sposób korzystania z zewnętrznych pamięci.

1) mk udostępniające szyny systemowe poprzez wyprowadzenia portów:

- szyny systemowe są dostępne dla użytkownika jako alternatywne funkcje wyprowadzeń portów.

Daje to możliwość podłączenia układów pamięci zewnetrznej, którą podłącza się do odpowiednich

portów mk

- wadą jest rezygnacja z części portów

2) mk udostępniające bezpośrednio szyny systemowe

- szyny systemowe mk są dostępne dla użytkownika bezpośrednio jako wyprowadzenia układu

scalonego bez funkcji alternatywnych przypisanych tym wyprowadzeniom

- możliwość przyłączenia pamięci zewnętrznych bez rezygnacji z niektórych portów

- takie mk nie posiadają wewnętrznych pamięci programu i danych

- możliwe jest korzystanie ze znacznie większych pamięci

3) mk zamknięte

- szyny systemowe nie są dostępne dla użytkownika

- mk korzysta wyłącznie z pamięci wewnętrznej

- można podłączać do niego urządzenia peryferyjne przez porty

- stosowane w przypadku prostych mk 8-bitowych

6.

·

Zalety zamknięcia magistrali wewnątrz mk.

–

zwiększenie niezawodności mikrosterownika

–

zmniejszenie poboru mocy

–

zwiększenie szybkości pracy

–

zmniejszenie ilości zacisków zewnętrznych i zwiększenie ich elastyczności

7.

·

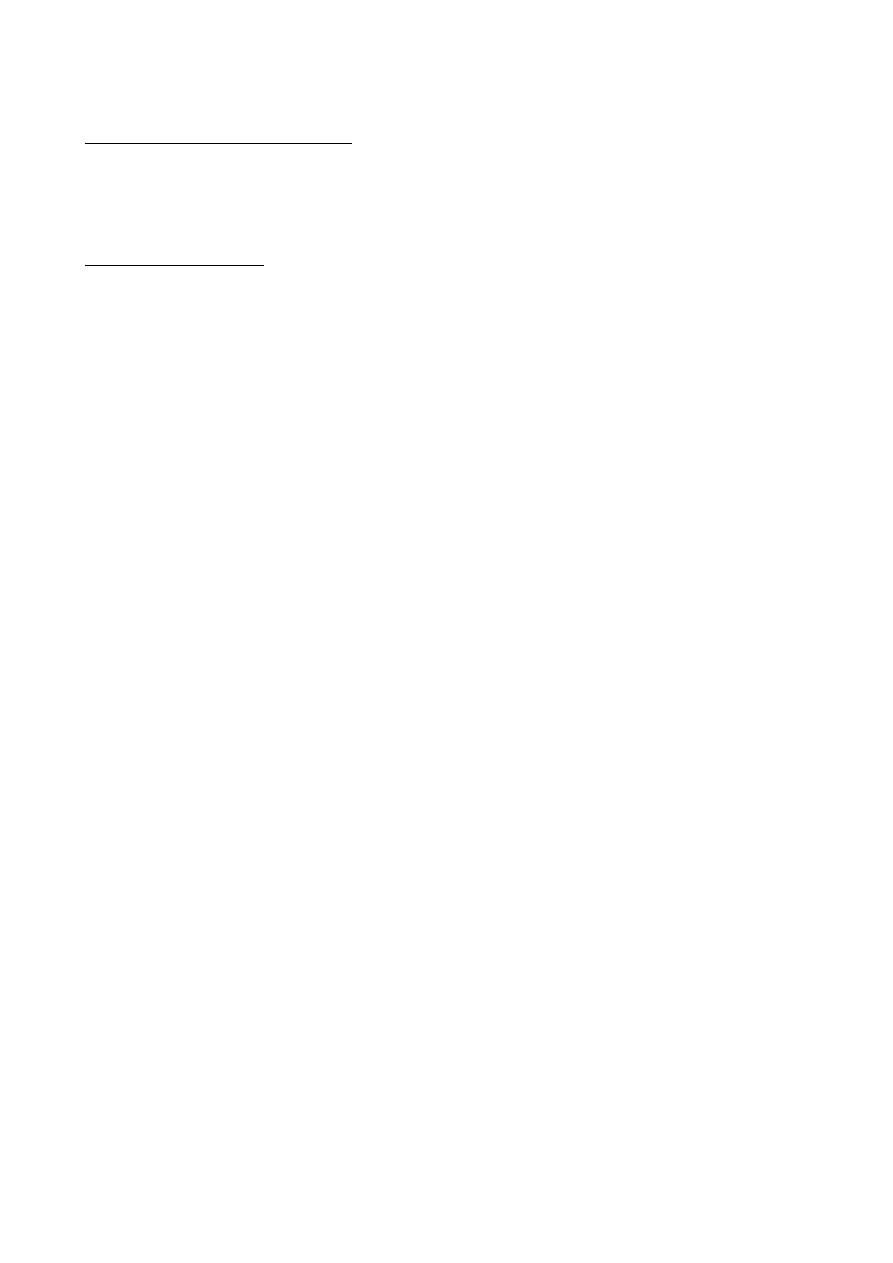

Warstwowy model mk zamkniętego.

8.

·

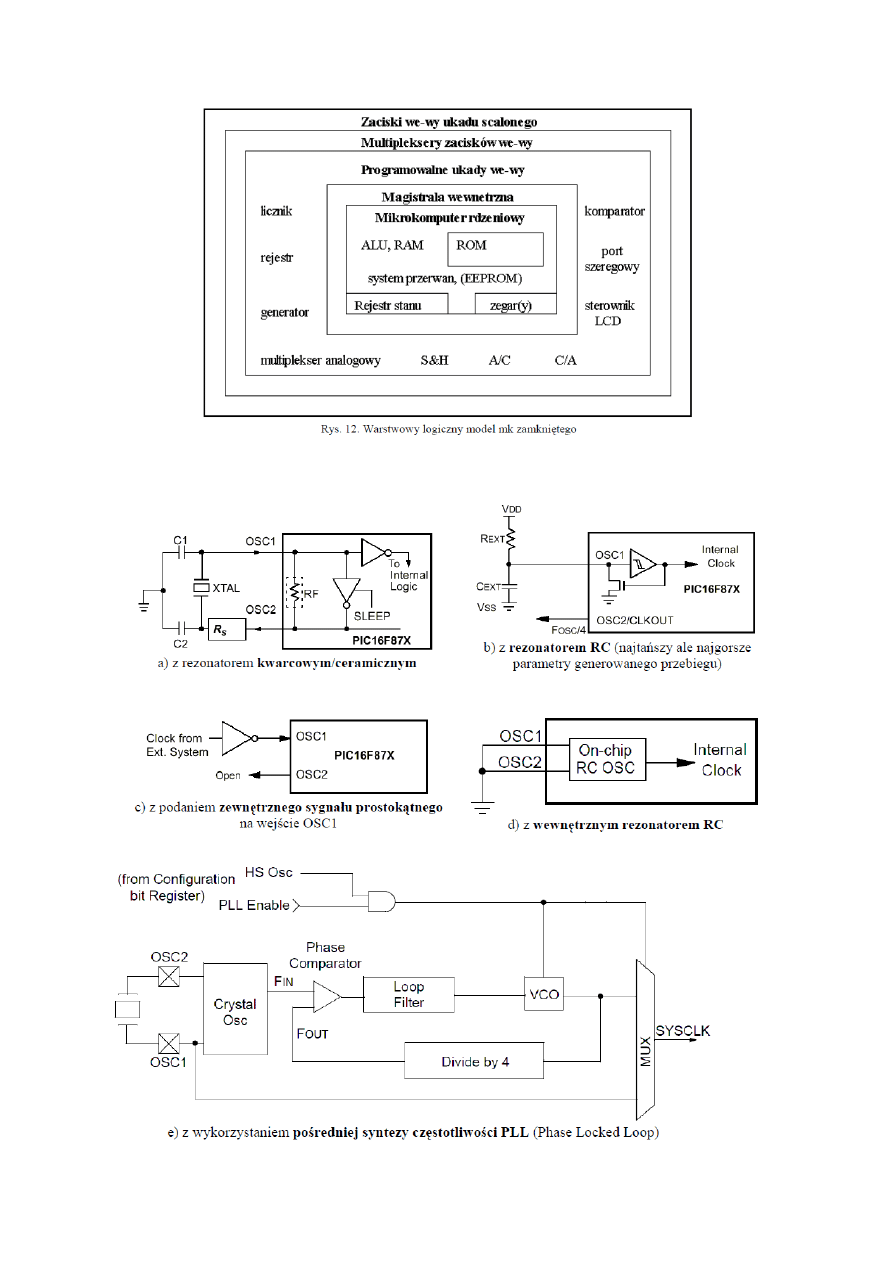

Sposoby generacji sygnału zegarowego w mk.

9.

·

Techniki redukcji pobieranej mocy w mk i tryby specjalne pracy mk.

Techniki redukcji:

–

Elastyczne sterowanie szybkością pracy w zależności od aktualnych potrzeb, gdyż zależność poboru

mocy układów CMOS zależy od częstotliwości pracy. Służy do tego sieć dystrybucji sygnałów

zegarowych w mk

–

Zastosowanie 2 oscylatorów. Jeden pracuje z maksymalną częstotliwością, drugi z niską. Przejście z

wysokiej do niskiej częstotliwości powoduje spadek pobieranej mocy o 3 rzędy

Specjalne tryby pracy mk:

–

tryb pełnej aktywności (RUN)

–

tryb uśpienia (pracują wszystkie urządzenia peryferyjne, procesor nie) (WAIT lub SLEEP)

–

tryb, w którym nie pracuje procesor, a pracują niektóre urządzenia peryferyjne

–

tryb pełnego wstrzymania pracy mk (zamrożenia) (STOP lub HALT)

10.

·

Sposoby wejścia i wyjścia z poszczególnych trybów specjalnych pracy mk.

Sposoby wejścia:

–

wykonując odpowiednią instrukcję

–

ustawiając odpowiednie bity

Sposoby wyjścia:

–

pojawienie się przerwania zewnętrznego lub przerwania od urządzeń peryferyjnych

–

reset zewnętrzny mk

–

reset wywołany przez niezablokowany, aktualnie pracujący układ watchdog

11.

·

Przeznaczenia sygnału RESET z źródła sygnału RESET w mk.

Sygnał RESET służy do:

–

inicjalizacji pracy mk (wprowadzenie w stan początkowy). Inicjalizacja polega na ustawieniu

licznika rozkazów na początek kodu programu.

–

Urządzenia we/wy i rejestry sterujące ustawiane są w tryb standardowy (spoczynku)

–

uniwersalne końcówki we/wy są ustawione jako wejścia o wysokiej impedancji, aby minimalnie

wpływać na otoczenie mk

–

służy do wprowadzania mk w tryb programowania lub testowania

Źródła RESETU:

–

po włączeniu zasilania

–

wywołany zewnętrznym sygnałem RESET

–

reset programowy (wykonanie instrukcji RESET lub ustawienie odpowiedniego bita)

–

reset wywołany przez układ watchdog

–

reset wywołany przez układy nadzorujące poprawność pracy mk

12.

·

Przeznaczenie i zasada pracy licznika watchdog w mk.

Przeznaczenie:

–

autonomiczne liczniki watchdog

–

monitory sygnału zegarowego

–

układy detekcji zaniku i powrotu napięć zasilających

–

układy detekcji przyczyn awarii systemowych

13.

·

Cechy systemu przerwań z programowym przeglądaniem urządzeń w mk.

–

jc nie zna źródła przerwania. Musi programowo przejrzeć flagi przerwań wszystkich urządzeń

–

flagi poszczególnych przerwań nie są kasowane sprzętowo przy wejściu w obsługę przerwania.

Trzeba je kasować programowo w trakcie obsługi

–

najczęściej obsługa wszystkich przerwań jest pod jednym wspólnym adresem, zwanym wektorem

przerwań

–

kolejność priorytetu przerwań zależy od przyjętej kolejności odpytywania flag przerwań

poszczególnych urządzeń

–

zaleta: prostota struktury sprżetowej potrzebnej do realizacji systemu przerwań z programowym

przeglądaniem urządzeń

–

wada: długi czas potrzebny na identyfikację źródła przerwania

14.

·

Cechy systemu przerwań wektoryzowanych w mk.

–

na sygnał potwierdzenia przyjęcia przerwania przez jc urządzenie, które zgłosiło przerwanie, podaje

na szynę danych kod identyfikacyjny, który jest traktowany jak numer elementu w wektorze

przerwań. Wektor przerwań reprezentuje listę adresów obsługi przerwań

–

każde źródło przerwania ma przypisany adres obsługi przerwania w pamięci programu, zwany

wektorem przerwania

–

każdemu przerwaniu przypisany jest priorytet (najpierw obsługiwany jest wyższy priorytet,

przerwanie o wyższym priorytecie może przerwać obsługę przerwania o niższym, istnieje możliwość

zmiany kolejności priorytetów)

–

wejście w obsługę danego przerwania zeruje sprzetowo jego flagę przerwania

15.

·

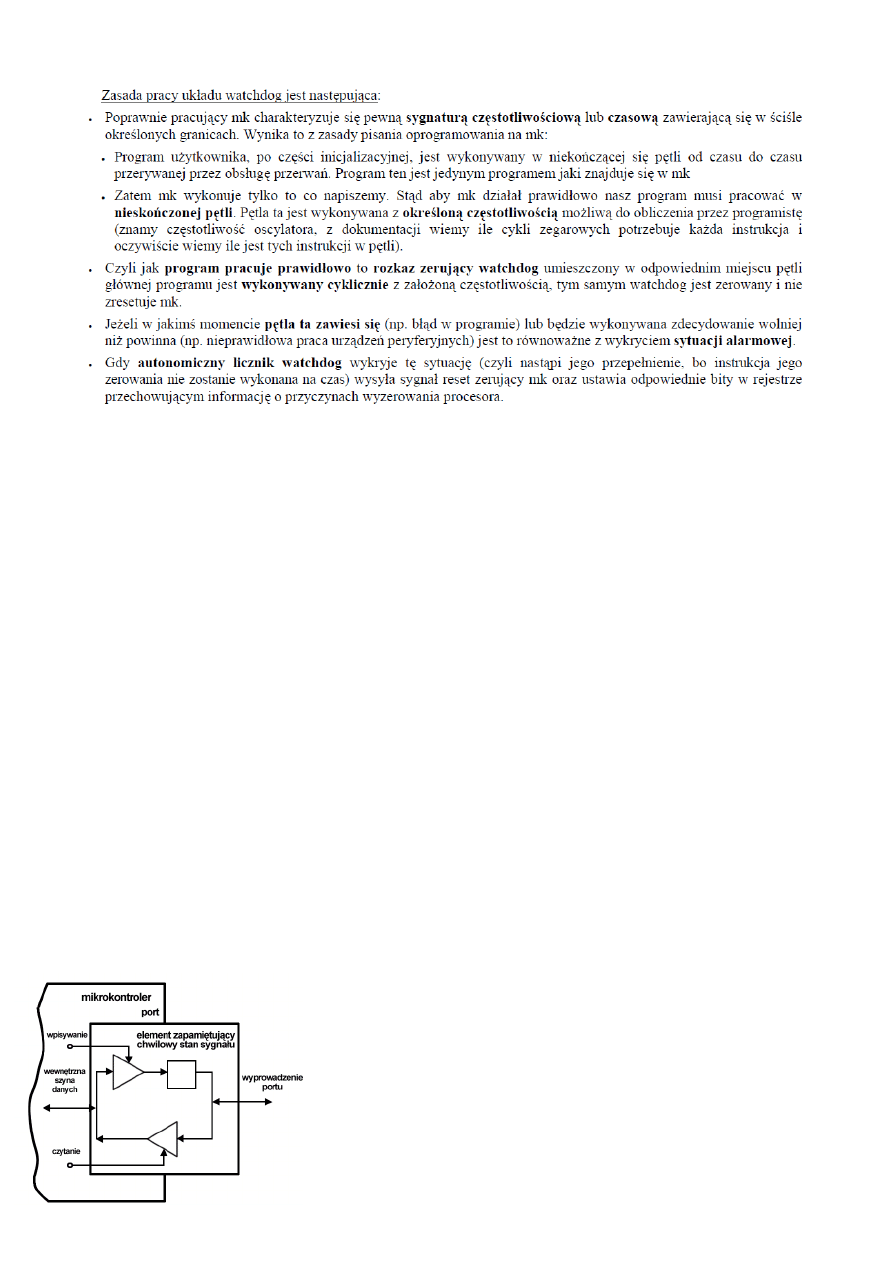

Budowa i zasada działania linii portów równoległych.

- czytanie danych (pobieranie) podawanych z zewnątrz na wyprowadzenia

portu przez port polega na doprowadzeniu chwilowych stanów napięć na

tych wyprowadzeniach do wewnętrznej szyny danych układu. Jest to

realizowane przez uaktywnienie trójstanowego bufora sygnałem „czytanie”

wpisywanie (wprowadzanie) danej do portu powoduje, że chwilowy stan

wewnętrznej szyny danych zostaje zapamiętany w elementach

zapamietujących poszczególnych linii i wystawiany na wyprowadzenia

portu. Stan wyprowadzeń portu pozostaje niezmienny, dopóki nie nastąpi

kolejna operacja wpisania do portu.

16.

·

Właściwości układów peryferyjnych mk.

–

są programowalne – zadania przekazywane są im do wykonania odpowiednimi rozkazami, przez

ustawienie odpowiednich bitów w rejestrach sterujących, przez wpisanie danych do rejestrów

danych

–

duży stopień autonomii w stosunku do procesora rdzeniowego. Zadania wykonywane są

samodzielnie, bez zaangażowania czasu procesora

–

układy we/wy programowane są za pośrednictwem magistrali wewnętrznej. Układom tym

przypisane są rejestry robocze, sterujące i statusu

–

o zakończeniu wykonywania zadań procesor informowany jest ustawieniem odpowiedniego bitu w

rejestrze stanu urządzenia lub wysłaniem sygnału żądania przerwania o ile jest ono odblokowane

17.

·

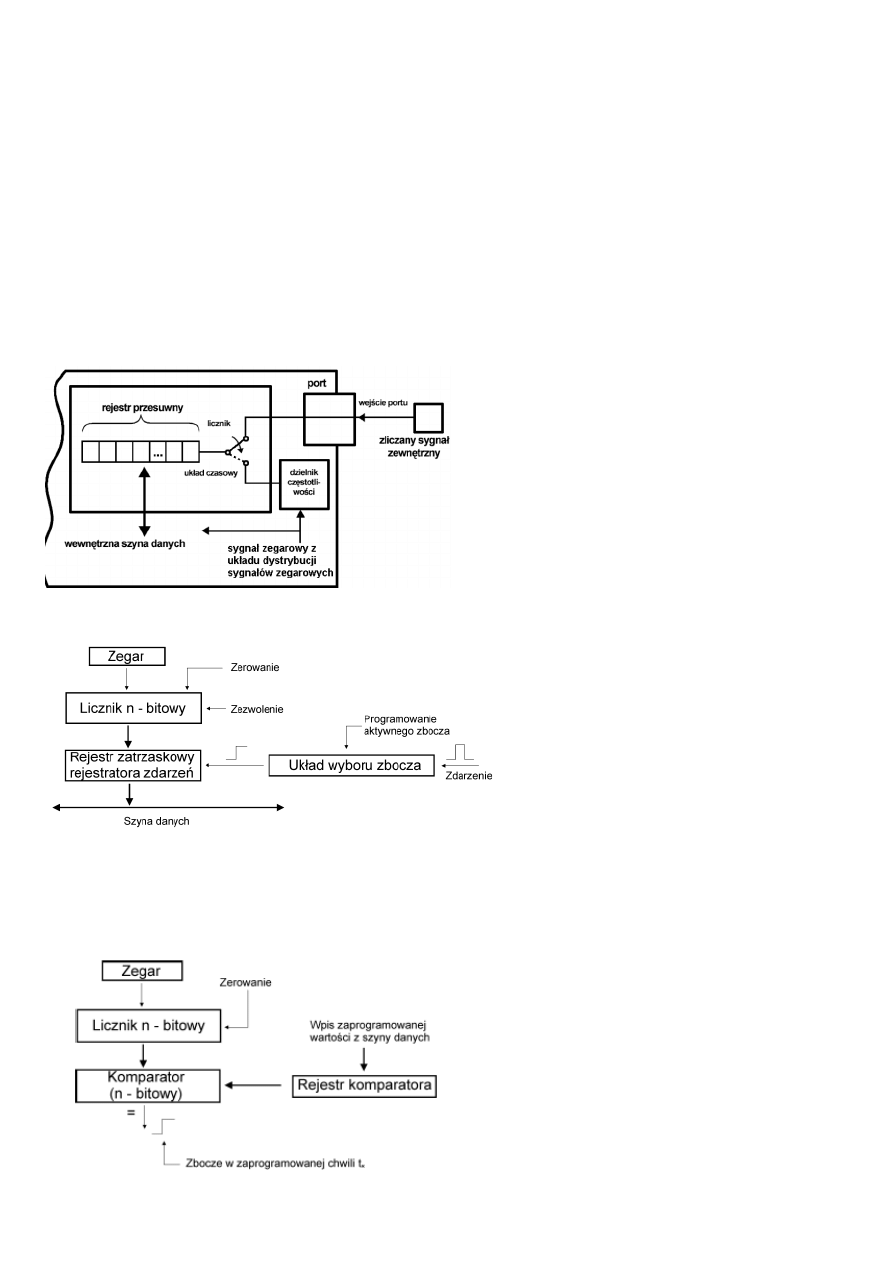

Schematyczna budowa układu czasowego w mk oraz jego zasada pracy w dwóch

podstawowych konfiguracjach.

–

jako właściwe układy czasowe – taktowane

wewnętrznym sygnałem zegarowym

przeznaczonym do taktowania jc. Timery

wykorzystywane są w programie

użytkownika jako wzorce czasu.

–

Jako liczniki – taktowane zewnętrznymi

sygnałami doprowadzającymi poprzez linie

wejściowe portów i wykorzystywane w

programie użytkownika np. jako liczniki

zmian poziomów sygnałów zewnętrznych

18.

·

Schemat blokowy i zasada działania licznika w mk w konfiguracji rejestratora zdarzeń.

Przed uruchomieniem zliczania program zeruje

licznik i określa zbocze sygnału zewnętrznego,

które ma spowodować rejestrację zdarzenia. Po

wystąpieniu tego zbocza zawartość licznika

jest przepisywana do rejestru zatrzaskowego

rejestratora zdarzeń. Układ może równocześnie

wygenerować przerwanie informujące jc o

zarejestrowaniu zdarzenia, jeśli wcześniej

ustawiono zezwolenie przerwania. W tym

układzie odczyt rejestru zatrzaskowego musi nastąpić przed wystąpieniem kolejnego zdarzenia, ponieważ

pracujący przez cały czas licznik przy następnym sygnale zewnętrznym zmieni zawartość rejestru

zatrzaskowego.

19.

·

Schemat blokowy i zasada działania licznika w mk w konfiguracji programowalnego

generatora impulsów.

Jc wpisuje do rejestru komparatora liczbę określającą

chwilę wygenerowania impulsu, po czym uruchamia

licznik. Po upływie zaprogramowanej liczby cykli

zegara, komparator wykrywa zrównanie ię zawartości

licznika i rejestru. Gdy to wykryje generuje sygnał

wyjściowy o zaprogramowanej wartości. Jednocześnie

licznik może wysyłać do jc przerwanie, o ile zostało

odblokowane.

20.

·

Schemat blokowy i zasada działania licznika w mk w konfiguracji generatora PWM.

Program zeruje licznik, po czym go uruchamia. Jeśli

zawartość licznika osiągnie zaprogramowaną liczbę

NT określającą okres impulsów, komparator ustawia

przerzutnik wyjściowy. Sygnał przepełnienia licznika

określa zatem początek okresu generowanego

przebiegu. W czasie zliczania kolejnych impulsów

zegara zawartość licznika jest porównywana z

zawartością rejestru szerokości impulsów, a po

zrównaniu się z nią generowany jest sygnał „=”,

który zeruje przerzutnik wyjściowy. Tym samym

impuls wytwarzany przez PWM kończy się.

21.

·

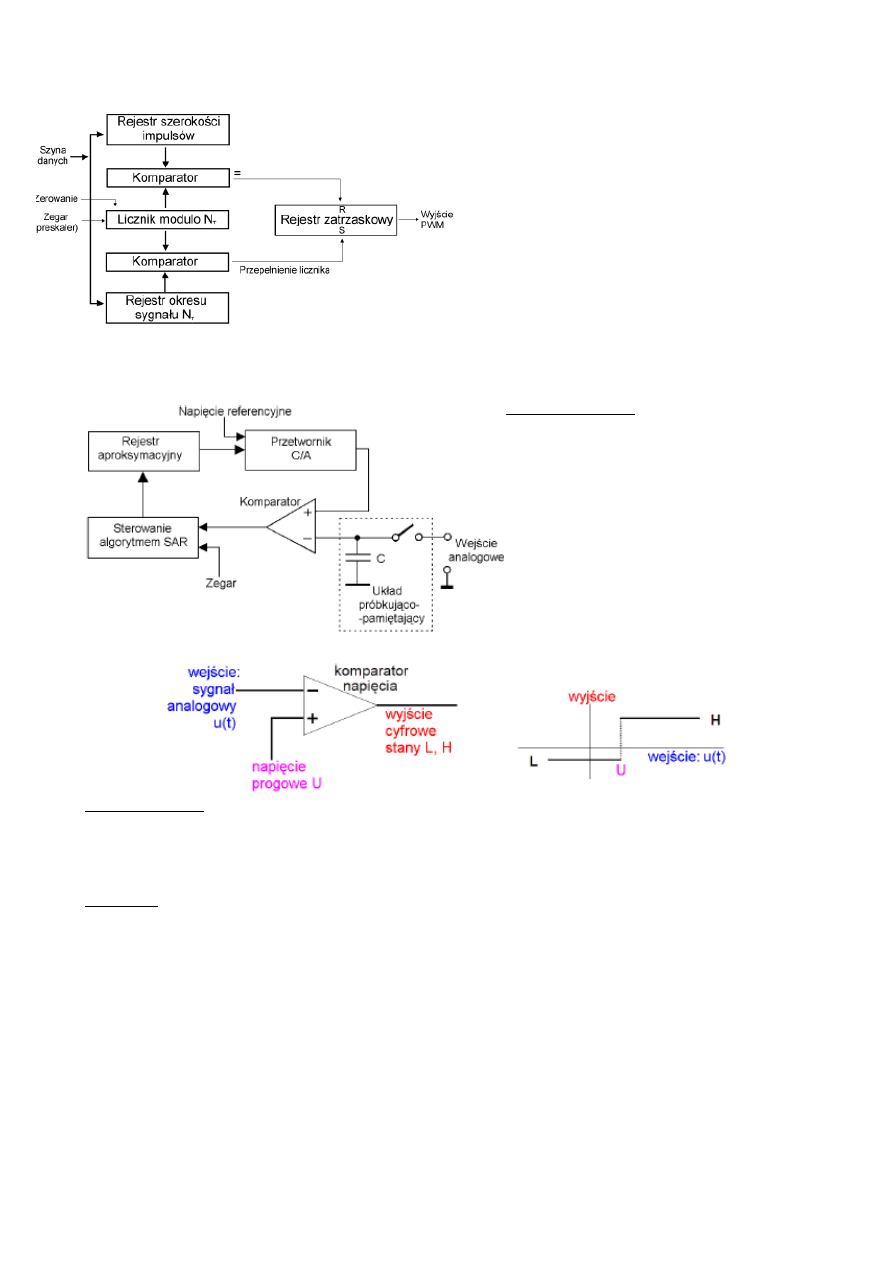

Budowa, zasada działania i typowe parametry wewnętrznego przetwornika A/C w

mk.

Typowe parametry:

–

długość słowa (najczęściej 10 bitów)

–

czas konwersji (od kilku do

kilkunastu us)

–

rozdzielczość (zwykle 1LSB ~5mV

przy zakresie 5V dla długości słowa

10 bitów)

–

błąd całkowity (około 2LSB)

22.

·

Schemat blokowy, parametry i zasada działania komparatora analogowego w mk.

Zasada działania:

W przypadku idealnym wyjście komparatora przyjmuje tylko dwie wartości napięcia: wysoką dla u(t)<U i

niską dla u(t)>U. Przejście od jednego stanu do drugiego zachodzi dla u(t)=U, to jest dla punktu, w którym

charakterystyka wyjściowa wykazuje nieciągłość.

Parametry:

–

próg komparacji – zewnętrzne napięcie podawane na jedno z wejść komparatora traktowane jako

napięcie odniesienia

–

warunek komparacji – co się stanie, gdy napięcie wejściowe wzrośnie powyżej progu komparacji lub

zmaleje poniżej jego. Spełnienie warunku komparacji powoduje ustawienie odpowiedniej flagi i

generację przerwania, o ile nie zostało zablokowane

23.

·

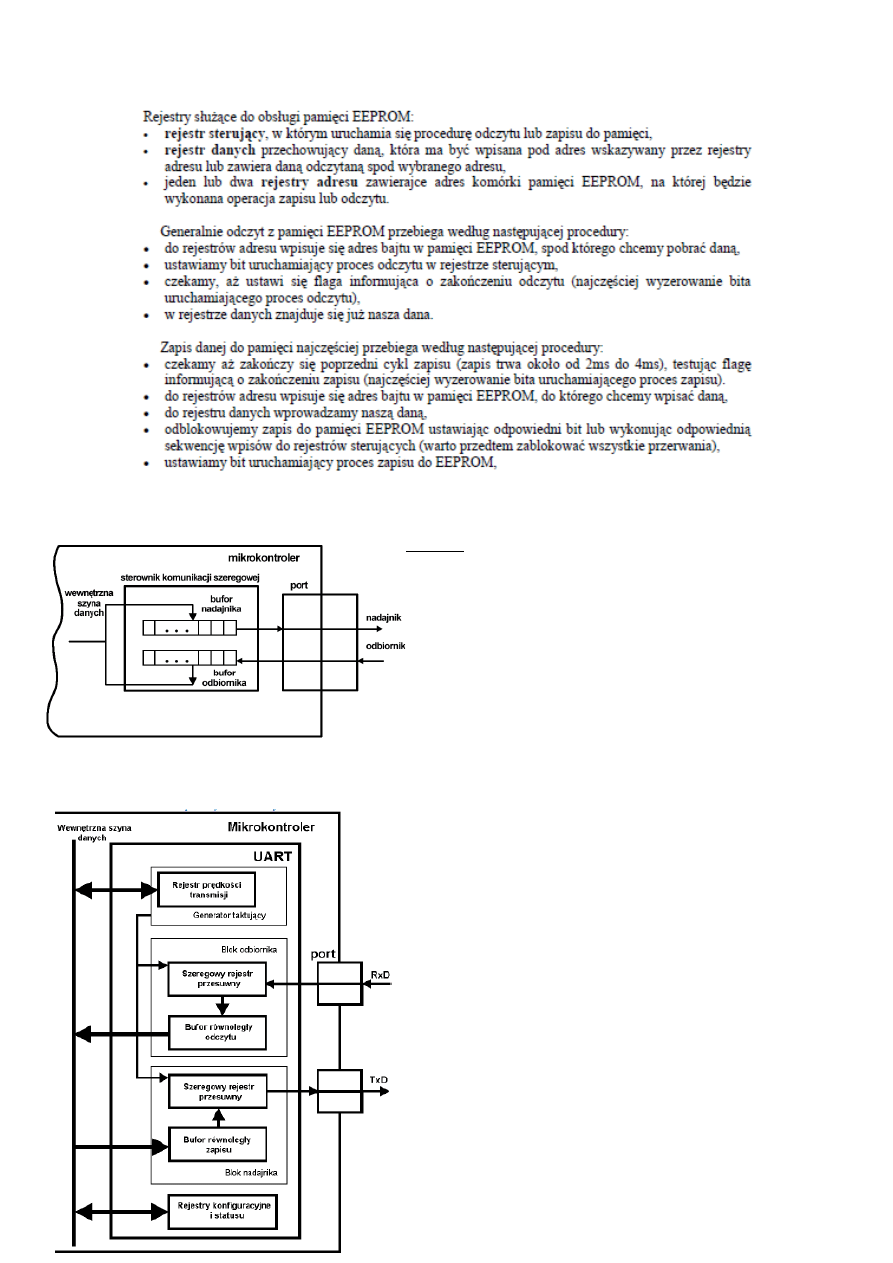

Sterowanie oraz sposób odczytu i zapisu danych do wewnętrznej pamięci EEPROM.

24.

·

Schematyczna budowa sterownika komunikacji szeregowej w mk oraz realizowane

przez niego funkcje.

Funkcje:

- Funkcja nadajnika - wysyłanie zawartości określonego

rejestru, tzw. bufora nadajnika, w postaci szeregowej

poprzez określone wyprowadzenia portu. Oznacza to, że na

wyjściu linii portu pojawia się ciąg binarny odpowiadający

zawartości wysyłanego rejestru

- W funkcji odbiornika sterownik komunikacji szeregowej

potrafi przetworzyć ciąg binarny doprowadzony do wejścia

określonej linii portu na zawartość rejestru, zwanego

buforem odbiornika. Bufory nadajnika i odbiornika są

dostępne z poziomu programu użytkownika.

25.

·

Format danych dla standardu UART, budowa kontrolera interfejsu UART oraz

ogólna jego obsługa.

- Należy najpierw ustalić prędkość transmisji wpisując

odpowiednia wartość do rej. Generatora prędkości transmisji.

- Wybrać 8 lub 9 bitowy format danych w rej.

konfiguracyjnym.

- Odblokować przerwania od nadajnika i od odbiornika.

- Włączyć nadajnik i odbiornik.

- Jeśli chcemy wysłać daną, to w celu uruchomienia transmisji

wprowadzamy ją do rejestru danych interfejsu UART. Gdy

dana ma być 9 bitowa, to przed tą operacją należy ustawić 9

bit danej znajdujący się w rej. Konfiguracyjnym. Przed

wysłaniem należy sprawdzić, czy poprzednia operacja

wysyłania danej przez UART została zakończona.

- Gdy interfejs odebrał daną, ustawiona jest flaga zakończony

odbior danej i generowane jest przerwanie. Odebrana dana

znajduje się w rejestrze danych.

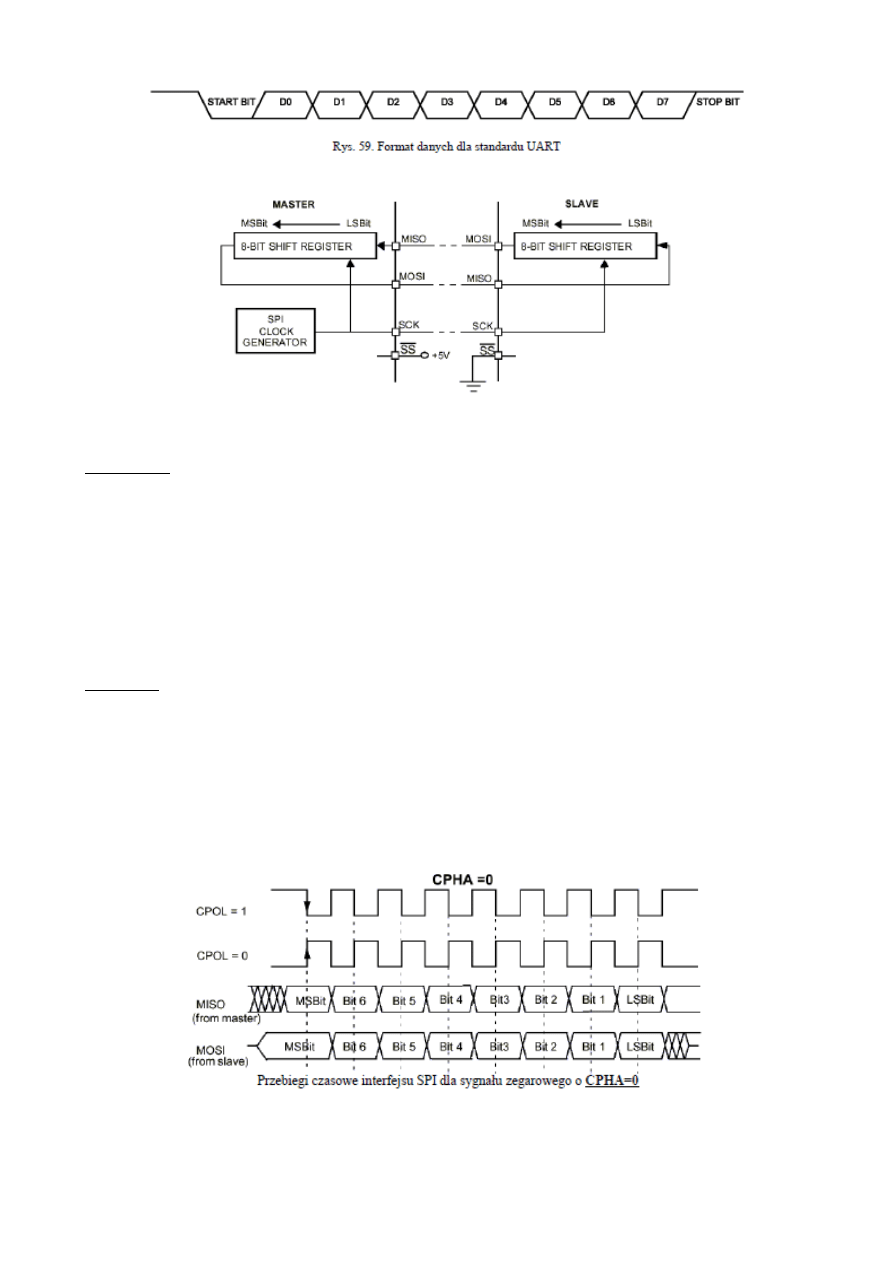

26.

·

Sposób łączenia za pomocą interfejsu SPI układów typu master i slave.

27.

·

Procedury wymiany danych za pomocą interfejsu SPI dla trybu master i trybu slave.

Tryb master:

–

najpierw należy odpowiednio skonfigurować interfejs SPI mk: tryb master, poprawnie

skonfigurowane piny interfejsu (pin SCK ma być wyjściem), ustawić częstotliwość sygnału

zegarowego

–

urządzenie peryferyjne musi być uaktywnione – najczęściej sluży do tego dodatkowa linia mk

podłączona do wejścia CS urządzenia peryferyjnego

–

aby rozpocząć transmisję wpisuje się daną do rejestru przesuwnego

–

po czym czeka się na zakończenie transmisji, testując flagę informującą o zakończeniu transmisji lub

czeka się na przerwanie od układu SPI, o ile jest odblokowane

–

na zakończenie z rejestru przesuwnego można odczytać daną odebraną

Tryb slave:

–

najpierw należy odpowiednio skonfigurować interfejs SPI mk: tryb slave poprawnie skonfigurowane

piny interfejsu (pin SCK ma być wejściem)

–

następnie wpisuje się daną, którą chcemy wysłać do rejestru przesuwnego

–

jeśli jest to wymagane, ustawia się odpowiedni bit w rejestrze sterującym SPI włączający interfejs

–

urządzenie peryferyjne musi być aktywne i pracować w trybie master

–

po czym czeka się na zakończenie transmisji, tktóre wywołuje przerwanie, o ile jest odblokowane

–

na zakończenie z rejestru przesuwnego można odczytać daną odebraną

28.

·

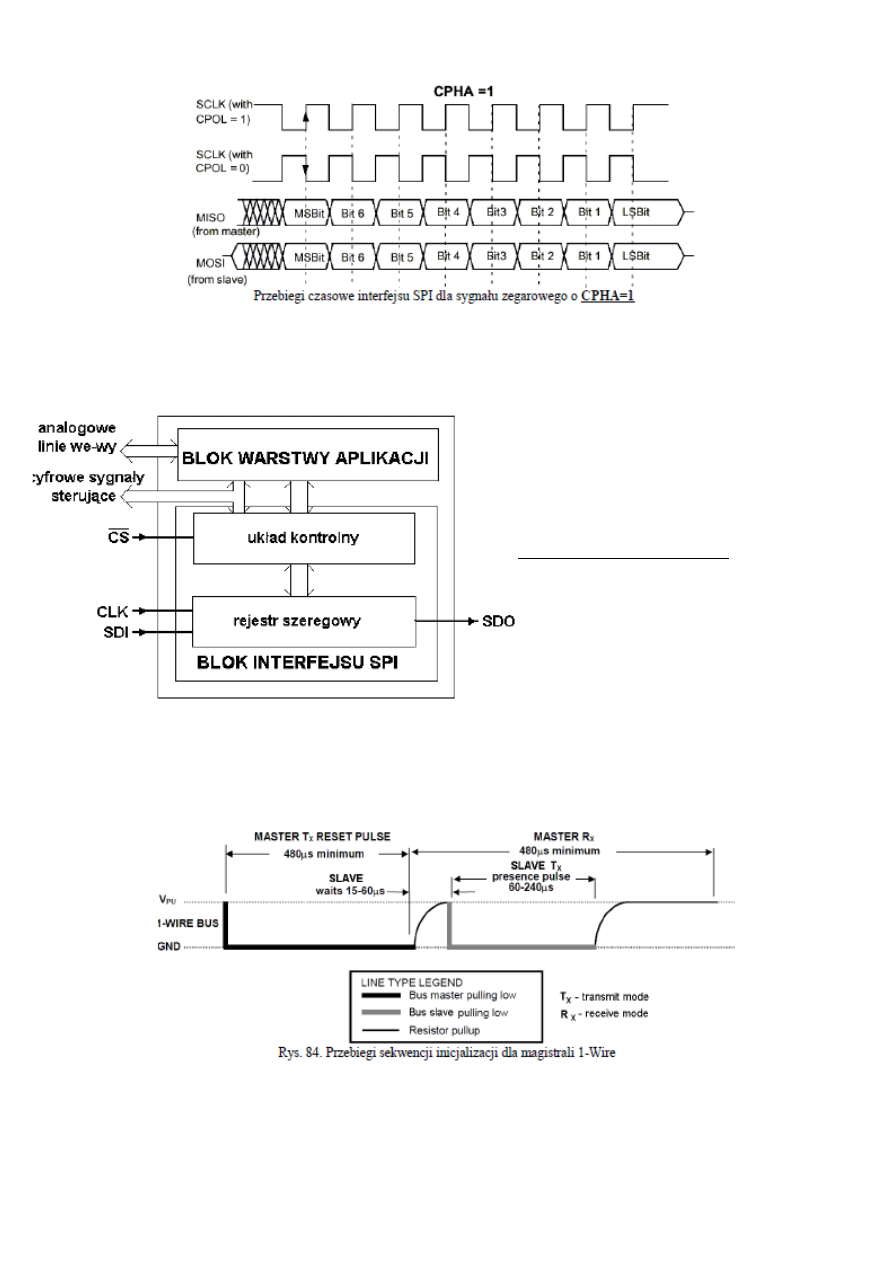

Przebiegi czasowe interfejsu SPI.

29.

·

Budowa kontrolera interfejsu SPI w mk i znaczenie linii interfejsu SPI w mk.

30.

·

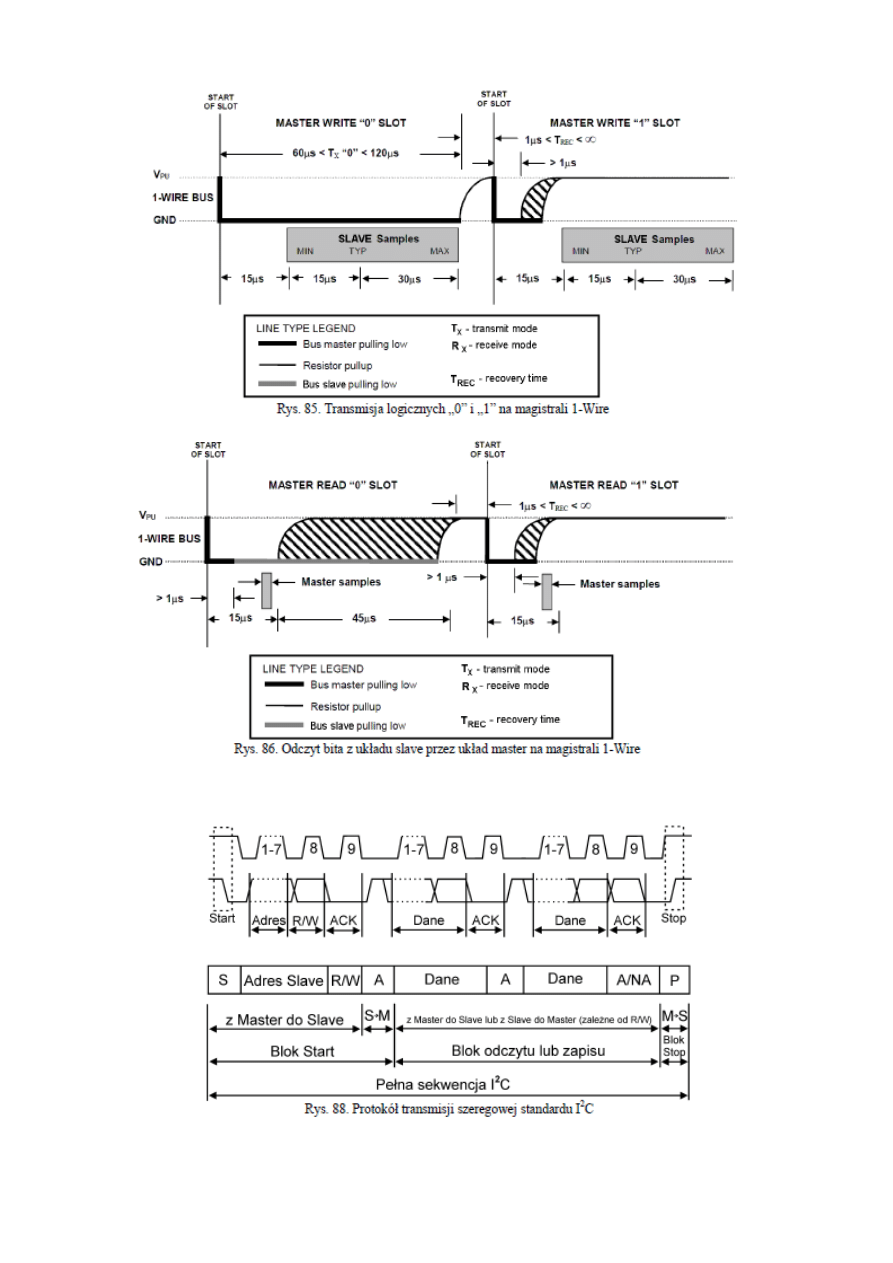

Schemat ogólny, zasada działania (funkcje poszczególnych bloków) układu

peryferyjnego z interfejsem SPI.

Blok interfejsu SPI – służy do

komunikacji z układem (wysyłanie i odbiór

danych, wysyłanie rozkazów i odbiór

danych statusowych).

Blok warstwy aplikacji – realizuje zadania

zgodne z przeznaczeniem układu.

Blok interfejsu SPI składa się z:

- rejestru szeregowego – w takt sygnału

zegarowego wprowadzane są do niego

szeregowo dane na linii wejścia danych

SDI. Dane z układu szeregowo są

wystawiane na linii wyjście danych SDO

- układ kontrolny – steruje interfejsem SPI

za pośrednictwem linii CS oraz

podłączonych do niego cyfrowych

sygnałów sterujących, których występowanie zależy od zastosowania układu. Zarządza również

komunikacją między rejestrem szeregowym a blokiem aplikacji.

31.

·

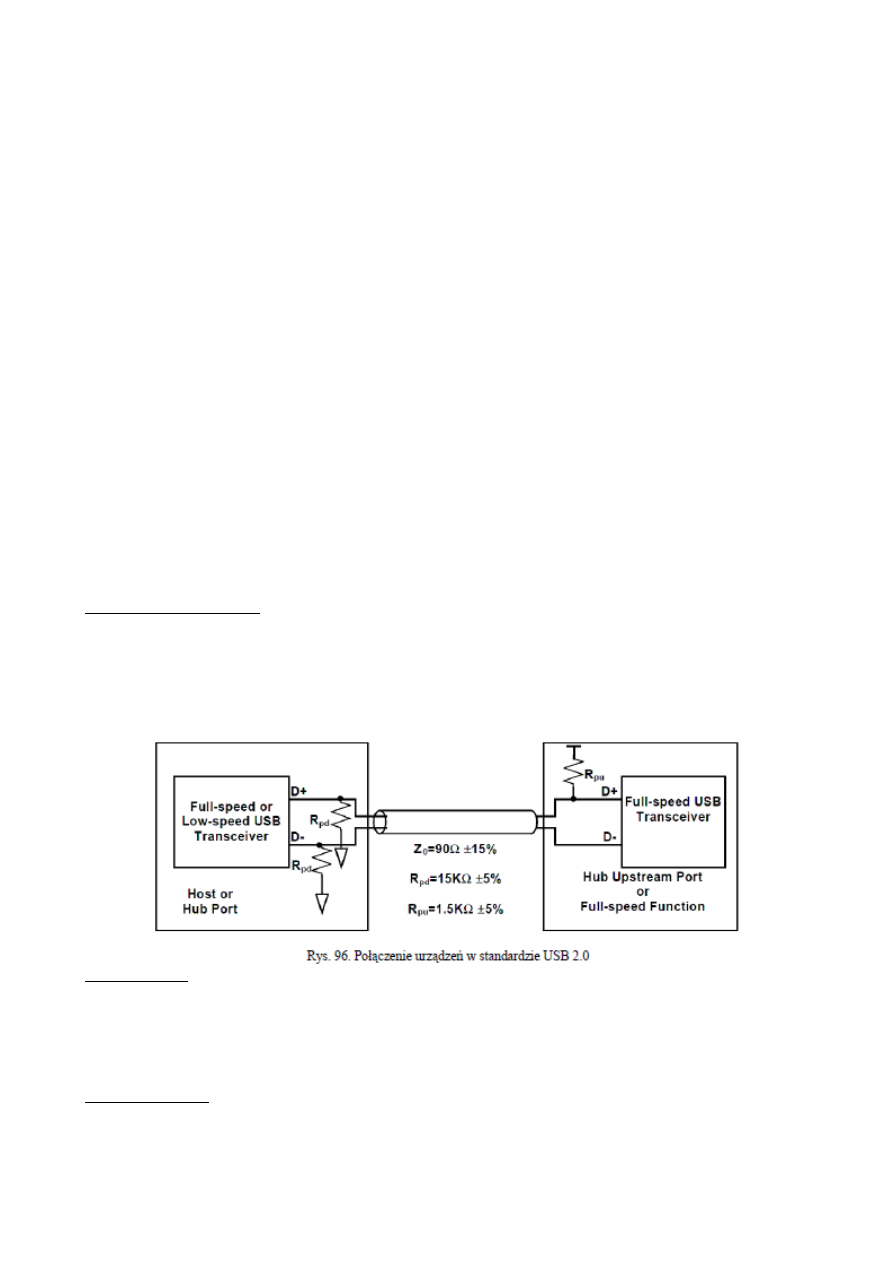

Przebiegi czasowe sekwencji inicjalizacji, wysyłania i odbierania bitów dla standardu

interfejsu 1- Wire.

32.

·

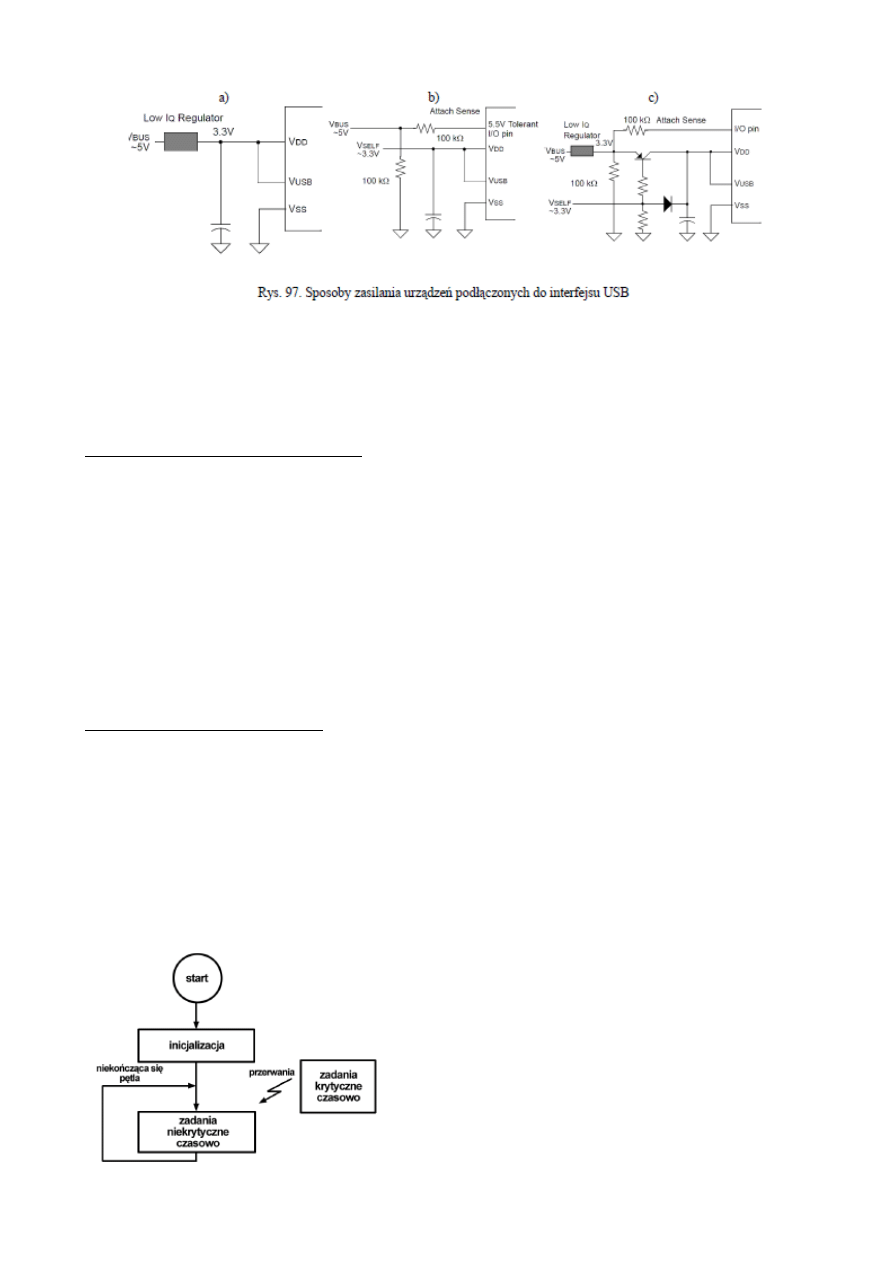

Zasada pracy interfejsu I

2

C i jego pełna sekwencja protokołu transmisji szeregowej.

Standard I2C jest stosowany w urządzeniach powszechnego użytku, zwłaszcza audio-video, telekomunikacji

i systemach elektroniki przemyslowej. Transmisja danych odbywa się:

- szeregowo w dwóch kierunkach;

- przy użyciu dwóch linii: SCL – impulsy zegarowe synchronizujące transmisję, SDA – dwukierunkowa linia

danych

Układy współpracujące z magistralą I2C muszą być wyposażone w wyjścia z otwartym drenem dla linii SCL

i SDA. Do jednego układu master można przyłączyć dowolną liczbę układów slave, jednak pod warunkiem,

że pojemność połączeń nie przekroczy maksymalnej wartości równej 400pF. W transmisji interfejsem I2C

uczestniczy układ nadrzędny (master) oraz jeden lub więcej układów podrzędnych (slave).

33.

·

Właściwości interfejsu CAN oraz grupy układów obsługujących interfejs CAN.

Właściwości:

–

interfejs asynchroniczny, half-duplex

–

struktura otwarta, tzn. może być rozszerzany o nowe węzły. Minimalna konfiguracja składa się z

dwóch węzłów. Liczba węzłów w trakcie pracy szyny może się zmieniać bez wpływu na działanie

szyny.

–

Składa się z jednej linii transmisyjnej

–

konfiguracja liniowa, czyli nie zawiera pętli

–

przy braku sterowania szyna znajduje się w stanie recesywnym R, któremu odpowiada stan „1”. Jeśli

choć jeden węzeł wymusi stan dominujący D, stan może być zmieniony na „0”

–

dane transmitowane są metodą NRZ (non return to zero). Ponieważ interfejs składa się z jednej linii

konieczny jest arbitraż szyny. Wykonuje się go metodą CSMA/CD z opcją NDA

–

adresy odbiorników (identyfikatory) są przesyłane jako integralna część przekazu.Standard CAN

przewiduje 11 bitowe identyfikatory, czyli umożliwia współpracę 2048 węzłów.

Układy obsługujące CAN:

–

układy nadawczo-odbiorcze

–

kontrolery współpracujące z mikroprocesorami, mikrokontrolerami, procesorami DSP

–

mk z zaimplementowanym kontrolerem CAN

34.

·

Połączenie między urządzeniami z interfejsem USB, znaczenie linii interfejsu USB i

sposoby zasilania urządzeń z interfejsem USB.

Znaczenie linii:

–

Vbus – przewód zasilania +5V

–

D+ - przewód symetrycznej skrętki sygnałowej

–

D- - przewód symetrycznej skrętki sygnałowej

–

GND – przewód masy zasilania

Sposoby zasilania:

–

zasilanie pobierane wyłącznie z interfejsu USB (rys a)

–

urządzenia z własnym zasilaniem (rys b)

–

urządzenia z podwójnym zasilaniem (rys c)

35.

·

Pojęcie rodziny mk. Modyfikacje członków rodziny mk.

Rodzina mk – zbiór mk oparty na tym samym procesorze rdzeniowym, czyli układów o różnych

parametrach, ale zachowujących między sobą kompatybilność programową, tzn. posiadają tą samą jc, czyli

tą samą liste instrukcji

Modyfikacje członków danej rodziny mk:

–

na poziomie jc dotyczy ona zmian: rozmiaru pamięci programu, rozmiaru pamięci danych RAM,

maksymalnej szybkosci pracy

–

na poziomie urządzeń peryferyjnych. Modyfikacje w tej warstwie stanowią podstawowy wyróżnik

danego typu mk. Użytkownik otrzymuje do dyspozycji całą, niekiedy dość liczną rodzinę mk

różniących się kombinacjami wbudowanych w układ scalony układami we/wy

–

na poziomie warstwy zacisków zewnętrznych i typów obudowy. Dotyczy głównie parametrów

elektrycznych zacisków mk oraz stosowanego typu obudowy mk.

36.

·

Definicja programowania zagnieżdżonego i cechy programów zagnieżdżonych.

Programowanie zagnieżdżone - tworzenie oprogramowania dla mse opartych na mk (i nie tylko) i

ukierunkowanych na zadania pomiarowo-sterujące oraz komunikacyjne.

Cechy programów zagnieżdżonych:

–

program jednoznacznie ustala funkcję mse, tzn. użytkownik ma możliwość zmiany funkcji systemu

zazwyczaj tylko w niewielkim zakresie przewidzianym przez program użytkowy, Ta cecha określana

jest jako „zagnieżdżenie” programu.

–

Działanie programu musi spełniać określone wymagania czasowe dotyczące przekraczania

maksymalnego czasu reakcji na określone zdarzenia zewnętrzne oraz realizacji określonych zadań

programowych w nieprzekraczalnym czasie. Ta cecha określana jest jako praca programu w „czasie

rzeczywistym”

–

są to programy działające na specyficznych zasobach sprzętowych warunkowanych

ukierunkowaniem budowy sprzętowej mse na konkretne zadanie

37.

·

Struktura programu użytkownika na mk.

Po włączeniu zasilania w programie użytkownika musi się

odbyć jednorazowa inicjalizacja, np. ustalenie trybu pracy

urządzeń peryferyjnych.

Właściwy program użytkownika jest realizowany:

–

częściowo w niekonczącej się pętli głównej

–

a częściowo w obsługach przerwań

38.

·

Zalety programowania w języku asemblera dla elektronicznych systemów wbudowanych.

–

Możliwość pełnego panowania nad zasobami systemu. Programista ma nieograniczony dostęp do

wszystkich bloków na poziomie rejestrów i pojedynczych bitow

–

żadna z funkcji systemu nie jest ukryta, w szczególności możliwe jest dowolne, nawet nietypowe

oddzialywanie na obszar stosu i mechanizm przerwań

–

swobodne dysponowanie obszarem pamięci

–

efektywny program wynikowy, szybszy i zajmujący na ogół mniej pamięci niż równoważny

program zapisany w języku wysokiego poziomu

–

możliwość swobodnego wyboru formatu danych i precyzji obliczeń. Programista może samodzielnie

definiować wielobajtowe struktury danych do obliczeń o praktycznie dowolnej dokładności

–

mozliwość dopasowania algorytmu do indywidualnych cech architektury mk oraz optymalizacji

programu wynikowego.

39.

·

Cykl projektowania i uruchamiania programu napisanego na mk.

–

napisanie kodu źródłowego

–

przetłumaczenie kodu źródłowego na kod maszynowy danego mk

–

uruchomienie programu w systemie docelowym (mse)

Faza pierwsza i druga wykonywana jest najczęściej przy zastosowaniu standardowego komputera

osobistego, który określany jest mianem systemu rozwojowego.

Faza trzecia realizowana jest na rzeczywistym mse zawierającym mk. System ten jest określany mianem

systemu docelowego.

40.

·

Rozszerzenia języka C oraz zalecenia dotyczące pisania programów w języku C na mk.

Rozszerzenia:

–

wprowadzone są nowe typy zmiennych, np. zmienne bitowe

–

przy deklaracji zmiennych wprowadzane są mechanizmy umożliwiające alokację (umiejscowienie)

zmiennej w określonym miejscu przestrzeni adresowej

–

wprowadzane są nowe słowa kluczowe języka C

Zalecenia:

–

fragmenty kodu źródłowego związane z obsługą specyficznych ukladów peryferyjnych umieszczać

w wydzielonych modułach

–

typy zmiennych deklarować nie bezpośrednio przy deklaracji zmiennych, ale poprzez slowo

kluczowe typdef

–

alokacji zmiennych nie dokonuje się bezpośrednio przy deklaracji zmiennych, lecz za pomocą

dyrektyw preprocesora, głównie przez użycie tzw. modelu pamięci

–

alokacja funkcji służących do obsługi przerwań odbywa się w wydzielonym zbiorze, często

napisanym w języku asemblera

41.

·

Metody uruchamiania programów napisanych na mk.

–

metoda prób i błędów – polega na wielokrotnym programowaniu mk i za każdym razem obserwacji

działania programu w mse i jego korekcji na podstawie tych obserwacji, aż do uzyskania

prawidłowego działania mk

–

zastosowanie monitorów programowych i programów śledzących. Monitory są instalowane w

pamięci programu mk i kontrolują wykonywanie właściwego programu użytkowego oraz

komunikują się z systemem rozwojowym przez złącze szeregowe. Natomiast debuggery pracują w

przyłączonych do systemu komputerach PC

–

zastosowanie emulatora sprzętowego mk – polega to na umieszczeniu, na czas uruchamiania

programu, w podstawce na mk sondy połączonej ze specjalnym układem sprzętowym, który emuluje

działanie mk. Emulator wiernie odtwarza wszystkie właściwości mk łącznie z jego wszystkimi

układami peryferyjnymi oraz pamięcią

–

wykorzystanie specjalnych zasobów wewnętrznych mk– niektóre mk zwłaszcza 32 bitowe posiadają

specjalne zasoby sprzętowe przeznaczone do wspierania procesu uruchamiania programu. Zasoby te

oferują w przybliżeniu wszystkie te możliwości co emulator sprzętowy, między innymi ustawienie

pułapek oraz pracę krokową. Zasoby te komunikują się przez dedykowane wyprowadzenia mk. Są

one dostępne wyłącznie na etapie uruchamiania programu, zatem nie są wykorzystywane przez

normalnmy program użytkowy.

42.

·

Procedura szeregowego programowania pamięci programu mk w systemie docelowym.

–

wprowadzenie mk w tryb programowania. Odbywa się to poprzez podanie na odpowiednie

koncówki określonej sekwencji sygnałów lub odpowiednich poziomów napięć

–

następnie przez dedykowany do programu interfejs szeregowy wprowadza się szeregowo

odpowiednie rozkzy sterujące procesem programowania pamięci. Część rozkazów dotyczy zapisu i

odczytu danych do/ze specjalnych rejestrów konfiguracyjnych zawartych w pamięci FLASH

odpowiedzialnych za konfigurację mk. Rejestry te są dostępne wyłącznie w trybie programowania

mk. Pozostałe rozkazy są związane z zapisem i odczytem danych z pamięci FLASH oraz z jej

kasowaniem.

–

Na zakończenie programowania następuje odpowiednia sekwencja sygnałów lub zdjęcie

odpowiednich napięć powodujące wyjście z trybu programowania

43.

·

Sposoby programowania szeregowego pamięci programu mk w systemie docelowym ze

względu na używany interfejs szeregowy.

–

z wykorzystaniem interfejsu SPI

–

oparte na interfejsie JTAG

–

bazując na dedykowanym interfejsie szeregowym

–

opierając się na interfejsie UART i wbudowanym programie ładującym zawartym w dedykowanej

pamięci ROM mk

–

bazując na interfejsie USB i wbudowanym w programie ladującym zawartym w pamięci mk

Wyszukiwarka

Podobne podstrony:

Nasze opracowanie pytań 1 40

Opracowanie pytań z anatomii

opracowanie pytań z optyki

Maszyny Elektryczne Opracowanie Pytań Na Egzamin

opracowanie pytan id 338374 Nieznany

opracowanie pytan karafiata

Opracowanie pytań 2 kolokwium

cw 3 broma opracowanie pytan 810

Nhip opracowanie pytan id 31802 Nieznany

filozofia opracowanie pytań

opracowanie pytan Automatyka

pytania egz ekonimak II, OPRACOWANIE PYTAŃ NA EGZAMIN

Zestaw 88 Kasia Goszczyńska, materiały farmacja, Materiały 3 rok, Od Ani, biochemia, biochemia, opra

opracowane zestawy, OPRACOWANIE PYTAŃ NA EGZAMIN

Opracowanie pytań MAMET METALE

egzamin z sorbentów opracowanie pytań 1 2 JM

Opracowanie pytań na zaliczenie Opto

więcej podobnych podstron