1

Podstawy techniki

mikroprocesorowej

ETEW006

Typy procesorów

Przetwarzanie danych

Andrzej Stępień

Katedra Metrologii Elektronicznej i Fotonicznej

C

omplex

I

nstruction

S

et

C

omputer

[1#3]

http://en.wikipedia.org/wiki/Complex_instruction_set_computing

wspomaganie j

ę

zyków wysokiego poziomu

:

– p

ę

tle programowe

– wywołania podprogramów, funkcji

– przenoszenie parametrów do/z podprogramów, funkcji

– optymalizacja kodu wynikowego programu

– ograniczenie ilo

ś

ci odwoła

ń

do pami

ę

ci

– obni

ż

enie kosztów systemu procesorowego (mniejsze wymagania

dotycz

ą

ce pami

ę

ci)

Complex Instruction Set Computer

[2#3]

Pravin R. Lakhe: A Technology In

Most Recent Processor Instruction Set Computers (CRISC): A Survey.

International Journal of Innovative Research & Studies, June 2013, Page 710 – 716

http://en.wikipedia.org/wiki/Complex_instruction_set_computing

cechy

procesorów typu

CISC

:

–

du

ż

a liczba instrukcji, prostych i zło

ż

onych

–

niewielka optymalizacja wykonywanych rozkazów, du

ż

a liczba cykli

maszynowych konieczna do wykonania rozkazów (zwykle dłu

ż

ej ni

ż

1

cykl maszynowy)

–

zmienny rozmiar instrukcji, rozkazy o zmiennym formacie (długo

ś

ci)

–

ró

ż

norodne i zło

ż

one tryby adresowania (przy dost

ę

pie do pami

ę

ci)

–

wspomaganie wykonywanych rozkazów mikrokodami (microcode)

–

segmentowy model pami

ę

ci (adresowanie segmentowe)

–

mały zestaw rejestrów strukturalnych (dla u

ż

ytkownika)

Complex Instruction Set Computer

[3#3]

cechy

procesorów typu

CISC

:

–

bezpo

ś

redni dost

ę

p do danych w pami

ę

ci, bez konieczno

ś

ci

kopiowania zawarto

ś

ci pami

ę

ci do rejestrów roboczych

–

zło

ż

ono

ść

i mała efektywno

ść

(szybko

ść

) działania dekodera

rozkazów

–

trudno

ś

ci z racjonalnym wykorzystaniem zasobów procesora; przy

prostych, elementarnych operacjach wykorzystanie niewielkiej cz

ęś

ci

zasobów procesora

–

brak przetwarzania potokowego

–

słaba wydajno

ść

operacji zmiennoprzecinkowych

Pravin R. Lakhe: A Technology In

Most Recent Processor Instruction Set Computers (CRISC): A Survey.

International Journal of Innovative Research & Studies, June 2013, Page 710 – 716

http://en.wikipedia.org/wiki/Complex_instruction_set_computing

Procesory CISC

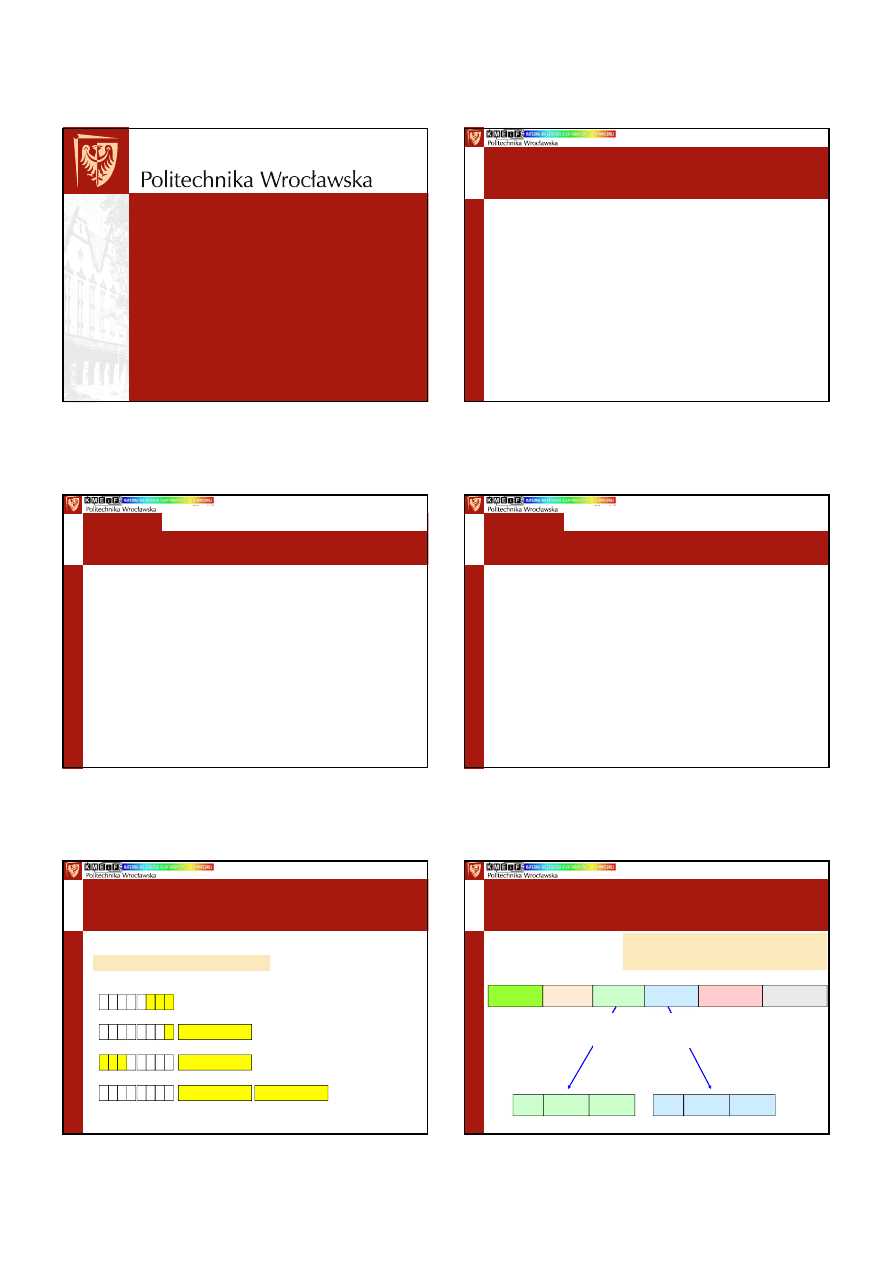

C51 — Formaty instrukcji

MOV

@Ri, #dana

ró

ż

ny, zmienny format rozkazów

:

1

r r r

0

1

0

0

ADD

A, Rn

0 1 1

i

1

1

1

0

dana

ACALL adr_11

0 0 0 1

0

A

A

A

adres A

CJNE

A, adr, rel

0 1 0 1

1

1

0

1

adres

rel

C500 Architecture and Instruction Set. User’s Manual.

Infineon, July 2000

Procesory CISC

8086 — Formaty instrukcji

procesor:

– o zło

ż

onej li

ś

cie rozkazów maj

ą

cych

ró

ż

ny, zmienny format

Intel Architecture Software Developer’s Manual.

Volume 2: Instruction Set Reference. Intel, 1997, p.2-1

Instruction

Prefixes

Opcode

ModR/M

SIB

Dispacement

Immediate

do czterech

1-bajtowych

prefixów

(opcjonalnie)

1 lub 2

bajty Op-

Code

przesuni

ę

cie

adresu

(address

displacement)

0, 1, 2 lub 4

bajty

Mod

Reg/

Opcode

R/M

0

3

6

7

2

5

Scale

Index

Base

0

3

6

7

2

5

1 bajt

(je

ś

li

wymagany)

1 bajt

(je

ś

li

wymagany)

SIB (Scale-Index-Base)

przesuni

ę

cie

adresu

(address

displacement)

0, 1, 2 lub 4

bajty

2

Procesory CISC

C51 — dostęp do pamięci

CISC

(

Complex Instruction Set Computer

) - procesor:

– predefiniowane przeznaczenie rejestrów, np. A (akumulator),

rejestry indeksowe do adresowania pami

ę

ci (wiele rozkazów

wykonuj

ą

cych operacje na komórkach pami

ę

ci)

– o rozbudowanych trybach adresowania

wewn

ę

trzna pami

ęć

RAM (dane)

:

MOV

A, @Ri

; A

←

(Ri)

IDATA

, i=0, 1

lub

MOV

@Ri, addr

; (Ri)

IDATA

←

(addr)

DATA

zewn

ę

trzna pami

ęć

RAM (dane)

:

MOVX

A, @DPTR

; A

←

(DPTR)

XDATA

lub

MOVX

A, @Ri)

; A

←

(256

∗

P2 + Ri)

XDATA

pami

ęć

kodu (stałe)

:

MOVC

A, @A+PC

; A

←

(A + PC)

CODE

C500 Architecture and Instruction Set. User’s Manual.

Infineon, July 2000

Cechy procesora typu CISC

statystyka działania systemów operacyjnych i programów

u

ż

ytkowych wskazuje na cz

ę

ste wykonywanie operacji prostych

i rzadkie zło

ż

onych

sterowanie przepływem rozkazów realizowane programowo

(

mikro-kody

); łatwa realizacja sterowania wykonywania zło

ż

onych

rozkazów wymagaj

ą

cych ró

ż

nych okresów czasu

Czym jest "microcode" ?

[1#2]

Zło

ż

ono

ść

mikroprocesora (miliony tranzystorów) i oprogramowania

(miliony linii kodu

ź

ródłowego) sprzyja powstawaniu bł

ę

dów projektantów

sprz

ę

tu i oprogramowania

Dla systemów operacyjnych

(np. Microsoft Windows) s

ą

dost

ę

pne pakiety

programów (Service Pack), których zadaniem jest eliminacja bł

ę

dów

znalezionych w dost

ę

pnym oprogramowaniu (strony internetowe)

Procesory

, np. firmy Intel, mog

ą

zawiera

ć

sprz

ę

towe

bł

ę

dy działania

,

których eliminacja jest mo

ż

liwa przez aktualizacj

ę

mikrokodu procesora

Aktualizacje mikrokodu s

ą

przechowywane nie w procesorze, s

ą

tracone po

wył

ą

czeniu zasilania procesora (aktualizacja przez BIOS przy ka

ż

dym

starcie systemu operacyjnego)

Intel

®

IXP1200 Network. Processor Family. Microcode Programmer’s Reference Manual.

INTEL Corporation, March 2002, Part Number: 278304-011

80C196KB User's Guide. INTEL Corporation, November 1990, Order Number: 270651-003

www.intel.com: XP SP2 vs. Intel Prescott

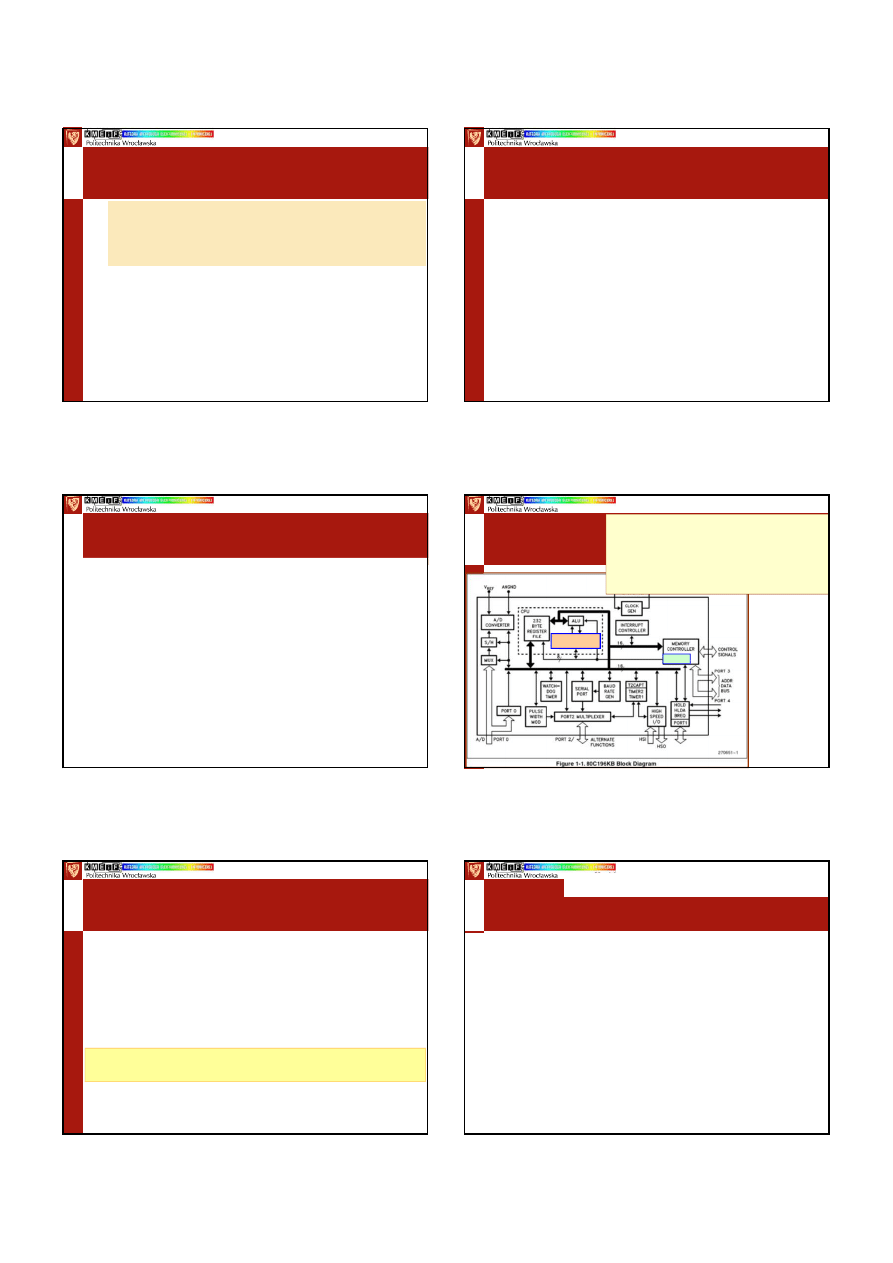

Czym jest

"microcode" ?

[2#2]

MICROCODE

ENGINE

instrukcje dla procesora s

ą

pobierane z kolejki

(queue) i tymczasowo przechowywane w

rejestrze rozkazów

maszyna stanów ’microcode’ dekoduje

instrukcje i generuje prawidłow

ą

(koryguje) ich

sekwencj

ę

80C196KB User's Guide.

INTEL Corporation, November 1990, Order Number: 270651-003

QUEUE

Cechy procesora typu RISC

[1#2]

uproszczon

ą

struktur

ę

mikroprocesora, o

zredukowanej li

ś

cie

rozkazów

zaproponował John Cocke (IBM Research w Yorktown, New

York, 1974) wychodz

ą

c z zało

ż

enia,

ż

e 20% dost

ę

pnych instrukcji

zajmuje a

ż

80% czasu pracy procesora

skrót

RISC

(

Reduced Instruction Set Computer

) zaproponował David

Patterson (University of California, Berkeley, 1985)

obecnie skrót

RISC

tłumaczony jako

Rational Instruction Set

Computer

idea RISC została wykorzystana w konstrukcji procesorów rodziny ARM

Reduced Instruction Set Computer

[2#2]

cechy

procesorów typu

RISC

:

– proste instrukcje i tryby adresowania

– jednolity format oraz stała długo

ść

instrukcji, ortogonalno

ść

instrukcji

– jednolite zasady dost

ę

pu do pami

ę

ci (load/store)

– przetwarzanie potokowe (pipelining)

– instrukcje wykonywane zwykle w 1 cyklu maszynowym

– sterowanie przepływem rozkazów realizowane sprz

ę

towo (brak mikro-kodów,

eliminacja mikroprogramowania)

– wi

ę

ksze mo

ż

liwo

ś

ci wyboru uniwersalnych rejestrów mikroprocesora

– dobra wydajno

ść

operacji zmiennoprzecinkowych

– implementacja pami

ę

ci podr

ę

cznych (cache)

– wykonanie operacji równowa

ż

nej wymaga wi

ę

kszej liczby rozkazów w

procesorze RISC ni

ż

w procesorze CISC

Pravin R. Lakhe: A Technology In

Most Recent Processor Instruction Set Computers (CRISC): A Survey.

International Journal of Innovative Research & Studies, June 2013, Page 710 – 716

http://en.wikipedia.org/wiki/Reduced_instruction_set_computing

3

Procesor RISC

Cortex-M0/M0+

[1#3]

ARM Cortex™-M Programming Guide to

Memory Barrier Instructions. Application Note 321. ARM DAI 0321A, p.3

The

ARM Cortex-M

processors are high performance, low cost, low power,

32-bit RISC processors

, designed for microcontroller applications.

The range includes the Cortex-M3, Cortex-M4,

Cortex-M0, Cortex-M0+

,

and Cortex-M1 processors.

The

Cortex-M1

processor is targeted at implementation in

FPGA

devices.

Cortex-M

processors

differ

from

other ARM

processors, including the

Cortex-A/R

processors, because they

only execute Thumb instructions

.

They are based on the ARMv7-M and

ARMv6-M

architectures and have an

efficient instruction

pipeline

, with

low-latency Interrupt Service Routine

(ISR) entry and exit.

Procesor RISC

Cortex-M0/M0+

[2#3]

Cortex™-M0 Technical Reference Manual.

Rev. r0p0. ARM DDI 0432C, p.2-2

Cortex™-M0+ Technical Reference Manual.

Rev. r0p1. ARM DDI 0484C, p.2-2

Cortex-M0

Cortex-M0+

32-bit processor core

,

von Neumann architecture

3-stage pipeline

2-stage pipeline

ARMv6-M Thumb

®

instruction set; Thumb-2 technology

Optional

ARMv6-M compliant 24-bit SysTick timer

32-bit hardware multiplier

:

– single-cycle multiplier, in designs optimized for high performance

– 32-cycle multiplier, in designs optimized for low area

The ability to have deterministic, fixed-latency, interrupt handling

NVIC features

:

– 1, 2, 4, 8, 16, 24, or 32 external interrupt inputs, each with four levels of priority

– dedicated Non-Maskable Interrupt (NMI) input

– support for both level-sensitive and pulse-sensitive interrupt lines

–

optional Wake-up Interrupt Controller (WIC), providing ultra-low power sleep

mode support

—

optional Memory Protection Unit (MPU)

Low power sleep-mode entry using

Wait For Interrupt

(WFI),

Wait For Event

(WFE) instructions, or the return from interrupt sleep-on-exit feature

Procesor RISC

Cortex-M0/M0+

[3#3]

Cortex™-M0 Technical Reference Manual.

Rev. r0p0. ARM DDI 0432C, p.2-2

Cortex™-M0+ Technical Reference Manual.

Rev. r0p1. ARM DDI 0484C, p.2-2

Optional

Wakeup

Interrupt

Controller

(WIC)

Optional

Memory

Protection

Unit

(MPU)

Cortex-M0

Cortex-M0+

processor

core

Nested

Vectored

Interrupt

Controller

(NVIC)

Breakpoint

&

Watchpoint

Units

Optional

Debug

Access

Port

Debugger

interface

Bus matrix

Cortex-M0/

M0+

Components

Cortex-M0/

M0+

Processor

Interrupts

Optional

single cycle

I/O port

Optional

Serial-Wire or

JTAG debug port

Execution Trace Interface

System

timer

(SysTick

Timer)

AHB-Lite

interface

to system

Procesor typu CRISC

Procesory firmy Intel’s z serii Pentium nazwano

CRISC

(

C

omplex-

R

educe

I

nstruction

S

et

C

omputers)

Procesory serii Pentium s

ą

hybryd

ą

procesorów CISC i RISC

64-bitowe procesory serii x86

Intel Core 2 Duo

(2006 – dwurdzeniowe i

2007 – czterordzeniowe) s

ą

oparte na architekturze Intel Core

microarchitecture (291 million of transistors)

Hasan Krad, Aws Yousif Al-Taie: A New Trend for CISC and RISC Architectures.

Asian Journal of Information Technology 6(11), 2007, p.1128

Pravin R. Lakhe: A Technology In Most Recent Processor Instruction Set Computers (CRISC):

A Survey. International Journal of Innovative Research & Studies, June 2013, Page 710 – 716

Intel

®

64 and IA-32 Architectures Software Developer’s Manual. Volume 1: Basic Architecture.

Intel, December 2009

Optymalizacja

Przetwarzanie Danych

Optymalizacja kompilatorów

:

rozkazy wykonywane przez procesor realizuj

ą

funkcje, które najcz

ęś

ciej

powtarzaj

ą

si

ę

podczas kompilacji

lista rozkazów dostosowana do potrzeb kompilatorów, a nie własno

ś

ci

procesora

zało

ż

enia przydatne przy projektowaniu nowych konstrukcji procesorów

Sposób przetwarzania danych

- obci

ąż

enie rejestrów procesora i pami

ę

ci:

register-to-register

→

przestrzeni

ą

robocz

ą

s

ą

rejestry ogólnego

przeznaczenia:

– accumulator-based

CPU, z akumulatorem zwi

ą

zana jest

wi

ę

kszo

ść

instrukcji arytmetyczno-logicznych i wymiany danych

– register-based

CPU (register-to-register), rol

ę

akumulatora pełni

ą

rejestry ogólnego przeznaczenia

memory-to-memory

→

bloki pami

ę

ci traktowane s

ą

jako przestrze

ń

robocza, zast

ę

puj

ą

ca rejestry ogólnego przeznaczenia

Przetwarzanie rozkazów

Przetwarzanie rozkazów

– sposób wykonania rozkazu w procesorze:

podział

wykonywanego

rozkazu

na

standardowe fazy

:

– pobierania

(

Fetch

)

rozkazu z pami

ę

ci i umieszczenia w wewn

ę

trznym

rejestrze rozkazów lub pami

ę

ci buforuj

ą

cej,

– dekodowania

(

Reg/Dec

)

rozkazu, ustalenie typu wykonywanej operacji,

np. pobrania argumentów,

– wykonania

(

Exec

)

rozkazu, np. wymaganej operacji arytmetyczno-

logicznej, obliczenia adresu itp.

– zapisu

(

Wr

)

wyniku w rejestrach lub pami

ę

ci,

w przetwarzaniu

sekwencyjnym

(skalarnym) ka

ż

da faza wykonywana jest

oddzielnie, niezale

ż

nie od pozostałych,

w przetwarzaniu

potokowym

,

strumieniowym (pipeline processing)

poszczególne fazy ró

ż

nych rozkazów s

ą

w zasadzie wykonywane

równocze

ś

nie.

4

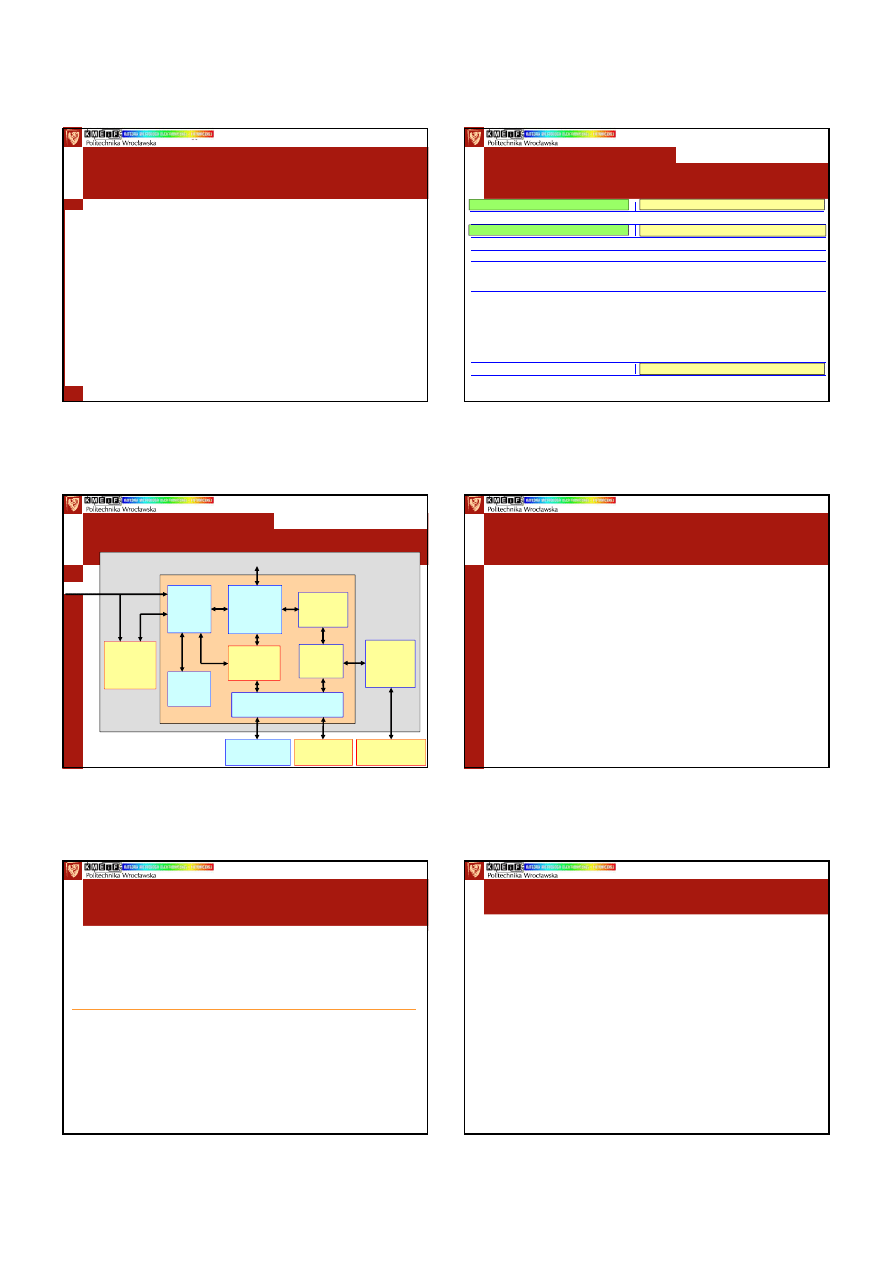

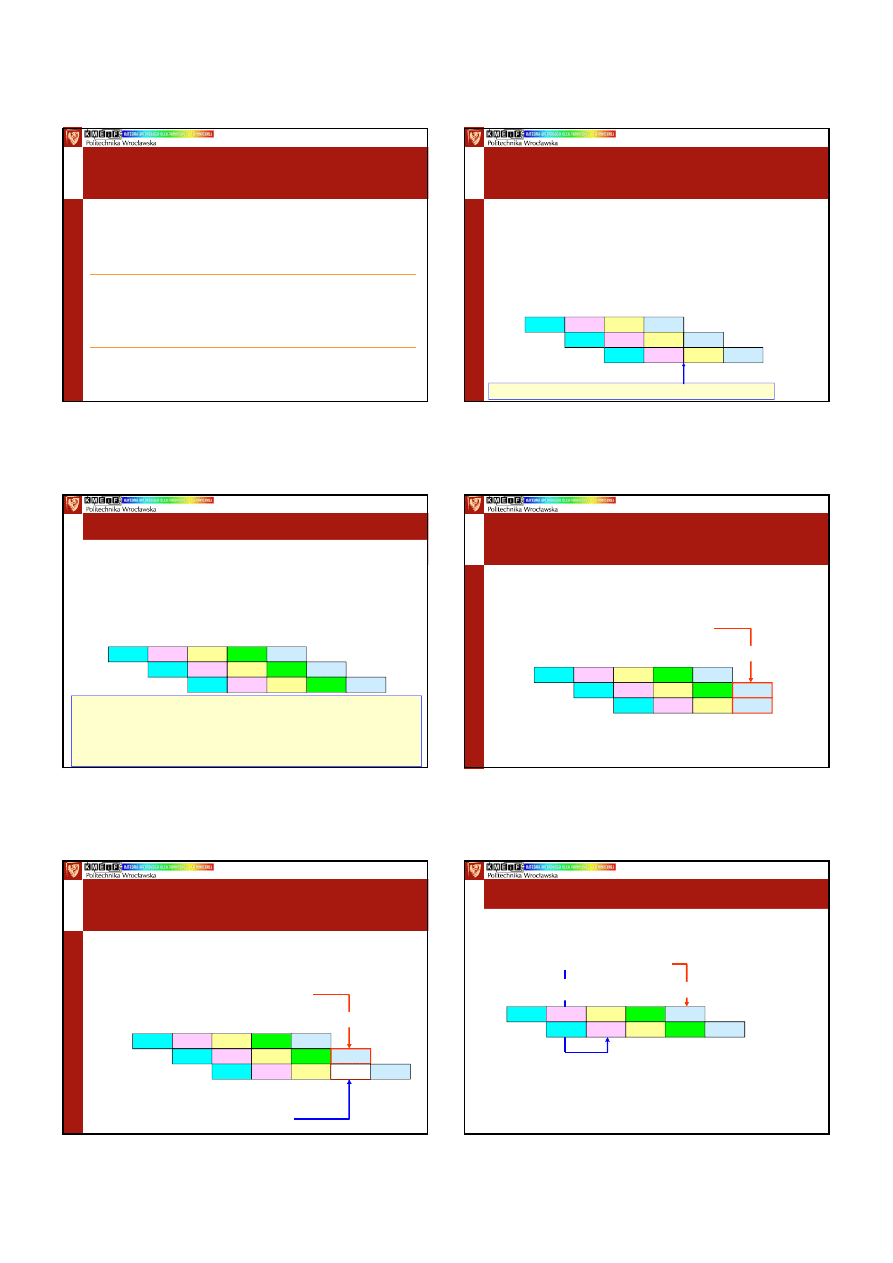

Sekwencyjne przetwarzanie rozkazów

Sekwencyjne

(skalarne) - ka

ż

da faza wykonywana jest oddzielnie,

niezale

ż

nie od pozostałych.

Fetch

Cycle

1

Exec

Cycle

3

Wr

Cycle

4

Cycle

5

Fetch

Exec

Cycle

7

Wr

Cycle

8

Fetch

Cycle

9

Fetch

Reg/Dec

Exec

Wr

pobierania

(

Fetch

)

rozkazu

dekodowania

(

Reg/Dec

)

rozkazu

wykonania

(

Exec

)

rozkazu

zapisu

(

Wr

)

wyniku

Reg/Dec

Cycle

2

Reg/Dec

Cycle

6

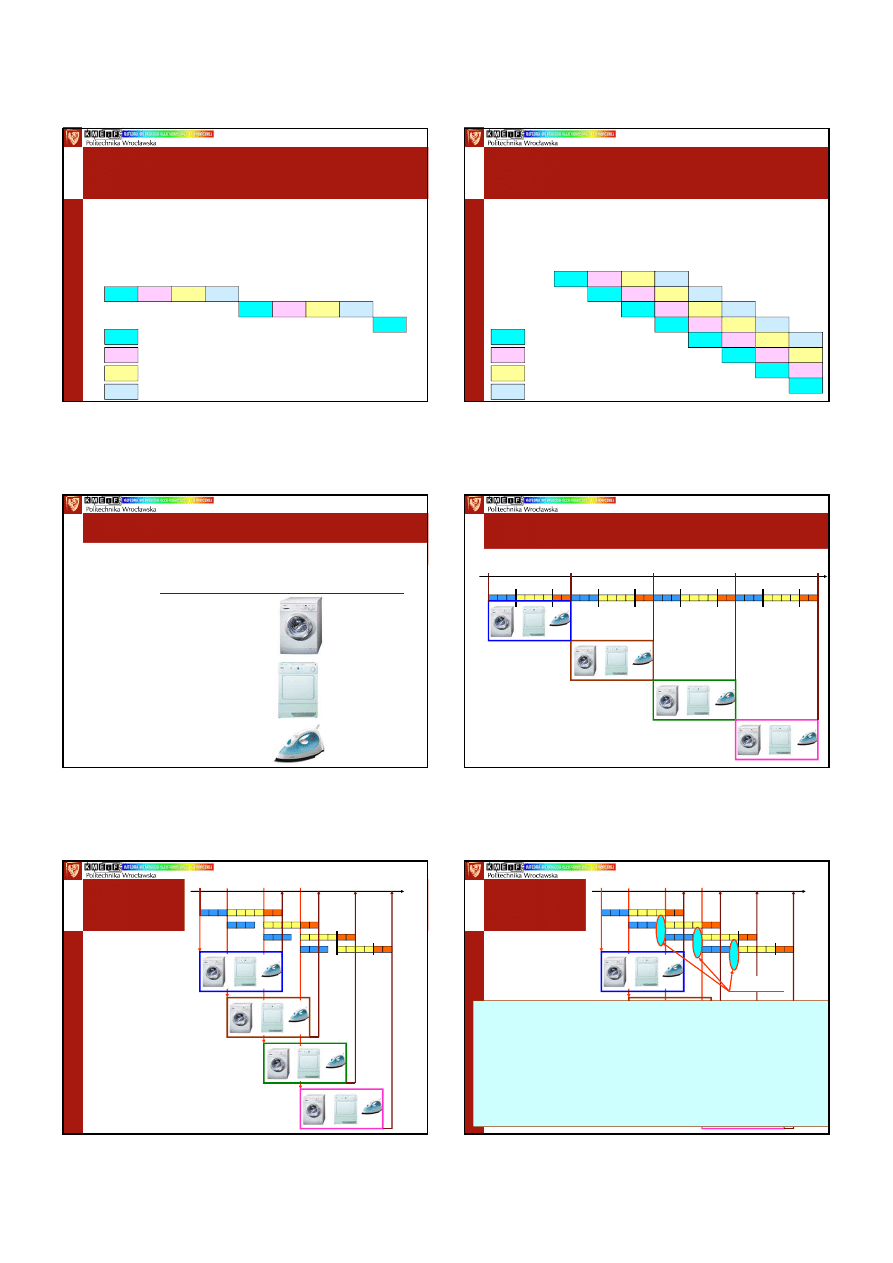

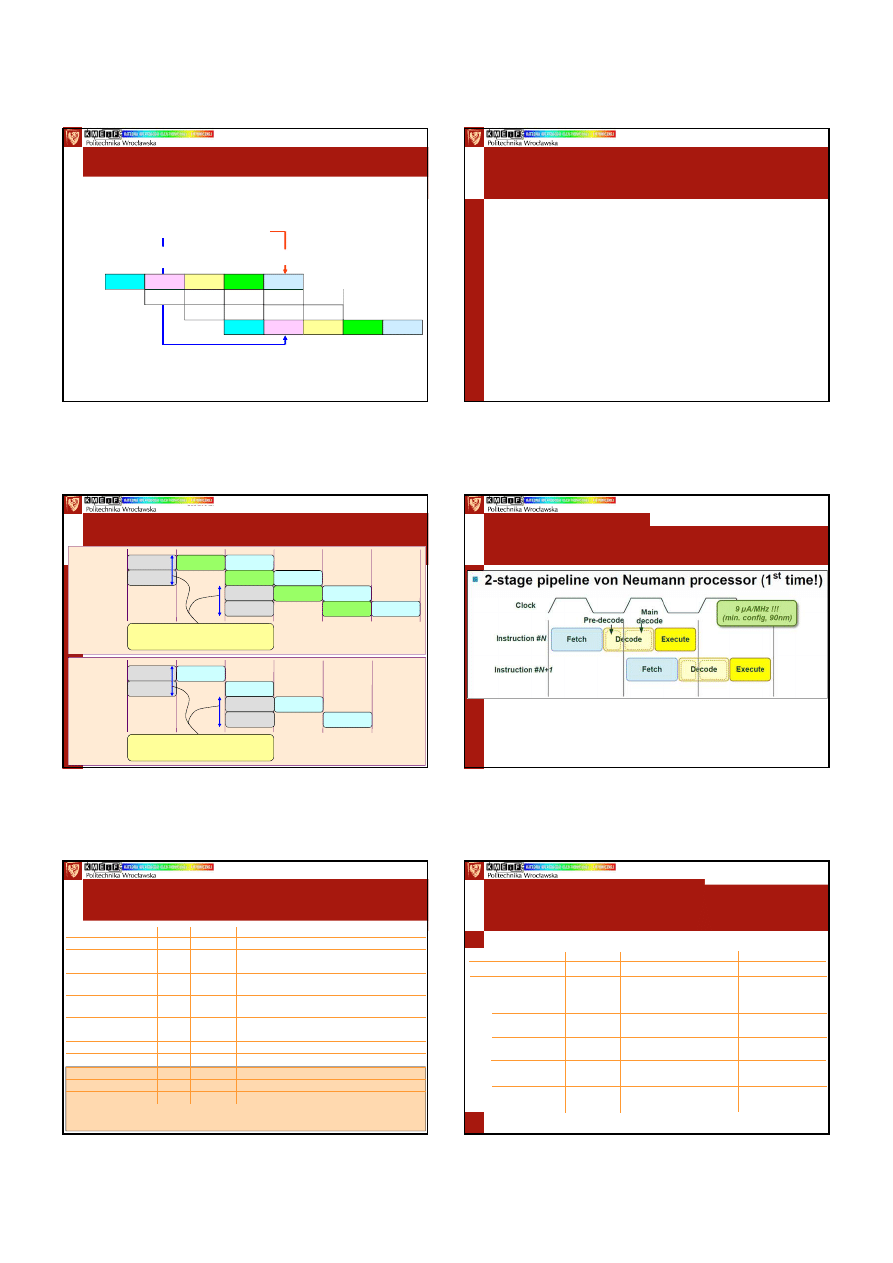

Potokowe przetwarzanie rozkazów

Fetch

Cycle

1

Fetch

Reg/Dec

Exec

Wr

pobierania

(

Fetch

)

rozkazu

dekodowania

(

Reg/Dec

)

rozkazu

wykonania

(

Exec

)

rozkazu

zapisu

(

Wr

)

wyniku

Fetch

Reg/Dec

Cycle

2

Potokowe

(strumieniowe, pipeline processing) - poszczególne fazy

ró

ż

nych rozkazów s

ą

wykonywana równocze

ś

nie.

Exec

Cycle

3

Reg/Dec

Fetch

Wr

Cycle

4

Exec

Reg/Dec

Fetch

Cycle

5

Wr

Exec

Reg/Dec

Fetch

Cycle

6

Wr

Exec

Reg/Dec

Fetch

Cycle

7

Wr

Exec

Reg/Dec

Reg/Dec

Fetch

Cycle

8

Wr

Exec

Exec

Reg/Dec

Fetch

Problem

czynno

ść

czas trwania

pranie

30 minut

suszenie

40 minut

prasowanie + składanie

20 minut

Ala

,

Bartek

,

Czesiek

i

Dorota

pior

ą

, susz

ą

, prasuj

ą

i składaj

ą

:

Czynności wykonywane szeregowo

Ala

Bartek

Dorota

30

40

20

30

40

20

Czesiek

30

40

20

30

40

20

16

00

17

00

18

00

19

00

20

00

21

00

22

00

sumaryczny czas

wynosi

6

godzin

przetwarzanie sekwencyjne

Czynności

wykonywane

równolegle

Ala

Bartek

Dorota

30

Czesiek

16

00

17

00

18

00

19

00

20

00

sumaryczny czas

wynosi

3,5

godziny

40

40

Czynności

wykonywane

równolegle

Ala

Bartek

Dorota

30

Czesiek

16

00

17

00

18

00

19

00

20

00

sumaryczny czas

wynosi

3,5

godziny

• przetwarzanie

równoległe,

potokowe

(

pipeline

) nie skraca czasu trwania

poszczególnych faz ale skraca czas trwania całego zadania

• czas trwania poszczególnych faz w przetwarzaniu potokowym jest równy

najdłu

ż

ej trwaj

ą

cej fazie

• przetwarzanie potokowe umo

ż

liwia równoczesne wykonywanie

niezale

ż

nych zada

ń

(

multiple tasks

)

• teoretyczna szybko

ść

jest równa liczbie niezale

ż

nych faz (

pipe stages

)

• ró

ż

ne długo

ś

ci niezale

ż

nych faz ograniczaj

ą

szybko

ść

przetwarzania

40

40

?

?

?

konflikt

5

Konflikty przy przetwarzaniu

potokowym

zasobów

– ten sam zasób wykorzystywany jest przez dwie lub wi

ę

cej

faz równocze

ś

nie (ALU, rejestry lub pami

ęć

):

– ka

ż

da operacja zapisu do rejestrów lub pami

ę

ci mo

ż

e by

ć

w

konflikcie z faz

ą

pobrania rozkazu lub argumentów

danych

– je

ś

li argumentem nast

ę

pnego rozkazu jest wynik

poprzedniego, który nie został obliczony:

– wykonanie nast

ę

pnego rozkazu musi by

ć

wstrzymane z powodu

niedost

ę

pno

ś

ci argumentu

sterowania

– gdy wykonywany jest rozkaz skoku warunkowego zale

ż

ny

od wska

ź

ników ustalanych przez poprzednie, jeszcze nie zako

ń

czone

rozkazy

Przetwarzanie potokowe - typ R

Instrukcja typu

R

(dost

ę

p do rejestru) zło

ż

ona z

4

cykli maszynowych:

• Fetch

:

pobranie kodu instrukcji z pami

ę

ci programu

• Reg/Dec

: pobranie zawarto

ś

ci rejestru i dekodowanie instrukcji

• Exec

:

ALU wykonuje operacj

ę

na zawarto

ś

ci 2 rejestrów

• Wr

:

wpis warto

ś

ci zmiennej do rejestru

Fetch

Reg/Dec

Exec

Wr

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5

Fetch

Reg/Dec

Exec

Wr

Fetch

Reg/Dec

Exec

Wr

Cycle 6

– typ instrukcji znany po jej zdekodowaniu (

Fetch

&

Reg/Dec

)

Przetwarzanie potokowe - LOAD

Instrukcja typu

LOAD

zło

ż

ona z

5

cykli maszynowych:

• Fetch

:

pobranie kodu instrukcji z pami

ę

ci programu

• Reg/Dec

: pobranie zawarto

ś

ci rejestru i dekodowanie instrukcji

• Exec

:

obliczenie adresu zmiennej w pami

ę

ci danych

• Mem

:

odczyt warto

ś

ci zmiennej z pami

ę

ci danych

• Wr

:

wpis warto

ś

ci zmiennej do rejestru

Fetch

Reg/Dec

Exec

Mem

Wr

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5

Fetch

Reg/Dec

Exec

Mem

Wr

Fetch

Reg/Dec

Exec

Mem

Wr

Cycle 6 Cycle 7

– instrukcja wykonywana w 5 niezale

ż

nych blokach funkcjonalnych

– ka

ż

da instrukcja korzysta tylko 1 raz z pojedynczego bloku funkcjonalnego

– pobranie kodu nast

ę

pnej instrukcji mo

ż

liwe po zako

ń

czeniu poprzedniego

– czas trwania pojedynczej instrukcji wynosi 5 cykli maszynowych

–

ś

redni czas trwania instrukcji w programie wynosi 1 cykl maszynowy

Konflikt zasobów

Fetch

Reg/Dec

Exec

Mem

Wr

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5

Fetch

Reg/Dec

Exec

Mem

Wr

Cycle 7

Fetch

Reg/Dec

Exec

LOAD

LOAD

typ R

Cycle 6

• zasobów

– ten sam zasób wykorzystywany jest przez dwie lub wi

ę

cej

faz równocze

ś

nie (ALU, rejestry lub pami

ęć

):

– ka

ż

da operacja zapisu do rejestrów lub pami

ę

ci mo

ż

e by

ć

w

konflikcie z faz

ą

pobrania rozkazu lub argumentów

Wr

Konflikt zasobów

Fetch

Reg/Dec

Exec

Mem

Wr

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5

Fetch

Reg/Dec

Exec

Mem

Wr

Cycle 7

Fetch

Reg/Dec

Exec

LOAD

LOAD

typ R

Cycle 6

• zasobów

– ten sam zasób wykorzystywany jest przez dwie lub wi

ę

cej

faz równocze

ś

nie (ALU, rejestry lub pami

ęć

):

– ka

ż

da operacja zapisu do rejestrów lub pami

ę

ci mo

ż

e by

ć

w

konflikcie z faz

ą

pobrania rozkazu lub argumentów

Wr

Wr

NOP

– w jednej z faz musi wyst

ą

pi

ć

dodatkowy

cykl oczekiwania (

NOP

)

Konflikt danych

Fetch

Exec

Mem

Wr

Cycle 1

Cycle 3 Cycle 4

Reg/Dec

Exec

Mem

Wr

LOAD

LOAD

Cycle 6

• danych

– je

ś

li argumentem nast

ę

pnego rozkazu jest wynik poprzedniego,

który nie został obliczony:

– wykonanie nast

ę

pnego rozkazu (zatrzymanie potoku) wstrzymane z

powodu niedost

ę

pno

ś

ci argumentu

Cycle 5

Reg/Dec

Cycle 2

Fetch

6

Konflikt danych

Fetch

Exec

Mem

Wr

Cycle 1

Cycle 3 Cycle 4

Reg/Dec

Exec

Mem

Wr

LOAD

LOAD

Cycle 6

• danych

– je

ś

li argumentem nast

ę

pnego rozkazu jest wynik poprzedniego,

który nie został obliczony:

– wykonanie nast

ę

pnego rozkazu (zatrzymanie potoku) wstrzymane z

powodu niedost

ę

pno

ś

ci argumentu

Cycle 5

Reg/Dec

Cycle 2

Ifetch

– rozwi

ą

zaniem konfliktu jest umieszczenie mi

ę

dzy rozkazami instrukcji

niezale

ż

nej od argumentów, np.

NOP

lub innej (problem

optymalizacji

kompilatorów

– rozkazy s

ą

wykonywane nie w takiej kolejno

ś

ci jak

zostały napisane w programie)

Reg/Dec

Exec

Mem

Wr

Reg/Dec

Exec

NOP

NOP

LOAD

Fetch

Reg/Dec

Fetch

Fetch

Exec

wstrzymanie

potoku

Wr

Wr

Eliminacja konfliktów

• powielenie

niektórych wewn

ę

trznych układów i

równoległe

wykonywanie tych samych operacji prowadzi do struktury

superskalarnej

,

• czasy realizacji

poszczególnych faz mog

ą

si

ę

ró

ż

ni

ć

w zale

ż

no

ś

ci od

typu wykonywanej operacji,

• takty zegarowe

musz

ą

by

ć

tak dobrane, aby dłu

ż

ej trwaj

ą

ce fazy były

wykonywane przez całkowit

ą

liczb

ę

tych taktów, np. jałowe takty

oczekiwania,

• do

skrócenia czasu

wykonywanych operacji przyczynia si

ę

umieszczenie argumentów w wewn

ę

trznych rejestrach, a nie w pami

ę

ci;

procesor musi by

ć

wyposa

ż

ony w du

żą

liczb

ę

wewn

ę

trznych rejestrów,

• zmniejszeniu liczby rozkazów

potrzebnych do wykonania zadania

sprzyja du

ż

a długo

ść

słowa maszynowego.

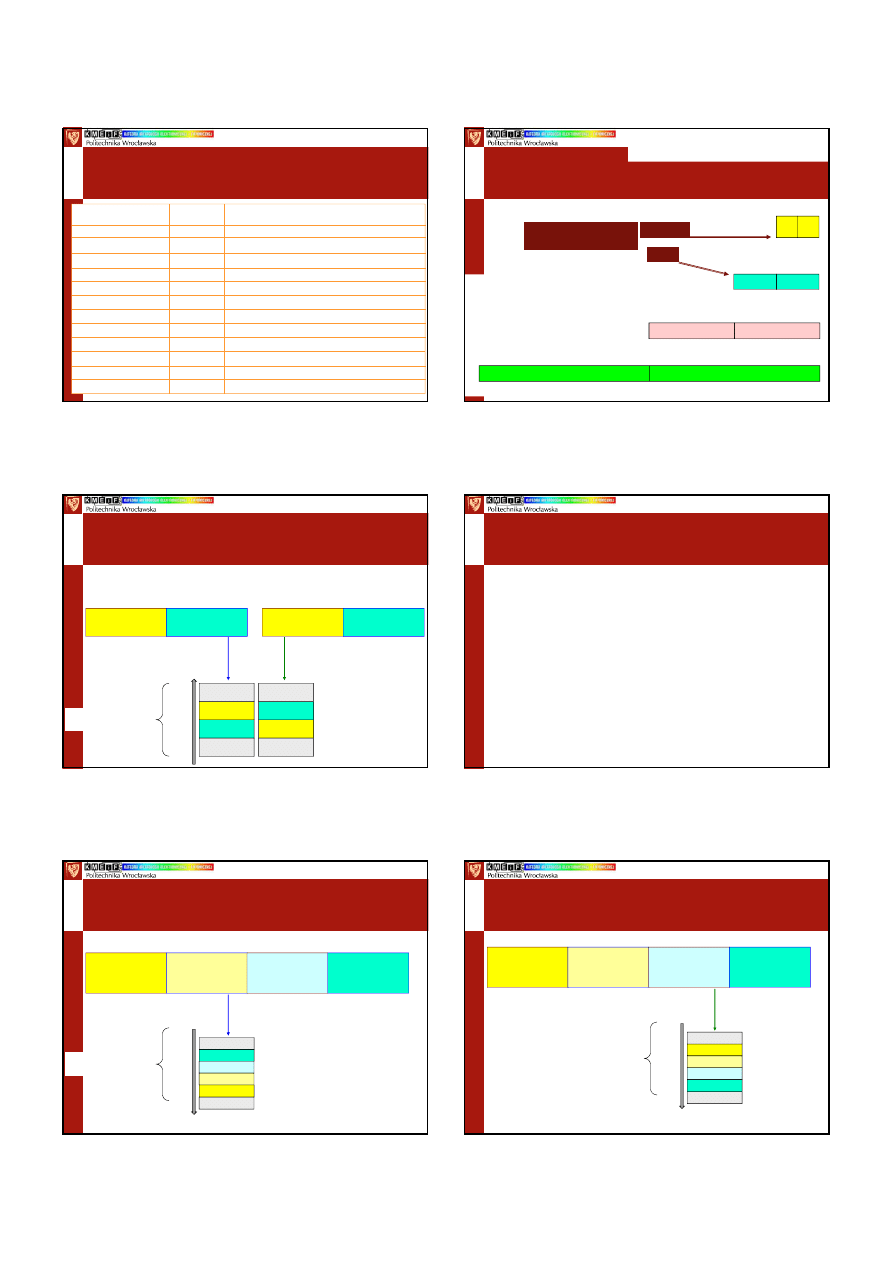

Procesor RISC: Cortex-M0/M0+

ARM Cortex™-M Programming Guide to

Memory Barrier Instructions. Application Note 321. ARM DAI 0321A, p.16

dwie (16-bitowe) instrukcje s

ą

pobierane równocze

ś

nie

pobranie

(fetch)

dekodowanie

(decode)

wykonanie 1

(execution)

pobranie

(fetch)

dekodowanie

(decode)

wykonanie 2

(execution)

pobranie

(fetch)

dekodowanie

(decode)

wykonanie 3

(execution)

pobranie

(fetch)

dekodowanie

(decode)

wykonanie 4

(execution)

Rysunek 3

Przetwarzanie potokowe

w procesorze Cortex-M0

instrukcja 1

instrukcja 2

instrukcja 3

instrukcja 4

dwie (16-bitowe) instrukcje s

ą

pobierane równocze

ś

nie

pobranie

(fetch)

wykonanie 1

(execution)

pobranie

(fetch)

wykonanie 2

(execution)

pobranie

(fetch)

wykonanie 3

(execution)

pobranie

(fetch)

wykonanie 4

(execution)

Rysunek 4

Przetwarzanie potokowe

w procesorze Cortex-M0+

instrukcja 1

instrukcja 2

instrukcja 3

instrukcja 4

Skrócenie cykli maszynowych

:

szybsza reakcja na przerwania (Interrupt entry) oraz skoki (Branch)

szybsze GPIO oraz dost

ę

p do układów peryferyjnych (peripheral access)

Mark Dunnett, Senior Field Application Engineer:

ARM Cortex-M0+ Core. Technical Introduction.

Hitex: ARM – The New Standard Across the Board ?

Freescale, May 2012, p.17

Cortex-M0+

Przetwarzanie potokowe

(Pipelining)

MCS51

Typy danych

Typ danej

Bity

Bajty

Zakres warto

ś

ci

bit

1

0 or 1

signed

char

8

1

–128 .. 0 ...... +127

unsigned

char

8

1

0 ......... 255

signed

short int

16

2

–32 768 .. 0 .. +32 767

unsigned

short int

16

2

0 .... 65 535

signed

int

16

2

–32 768 .. 0 .. +32 767

unsigned

int

16

2

0 .... 65 535

signed

long int

32

4

–2 147 483 648 .. 0 .. +2 147 483 647

unsigned

long int

32

4

0 .... 4 294 967 295

float

32

4

±1.175494E–38 .. 0 .. ±3.402823E+38

double

32

4

±1.175494E–38 .. 0 .. ±3.402823E+38

sbit

1

0 or 1

sfr

8

1

0 ......... 255

sfr16

16

2

0 .... 65 535

Uwaga: dane typu:

bit

,

sbit

,

sfr

oraz

sfr16

nie wyst

ę

puj

ą

w standardzie

ANSI C. To unikatowa cecha kompilatora Cx51.

Cx51 User's Guide.

ARM Ltd and ARM Germany GmbH.

MSP430

Typy danych

Typ danej

Rozmiar

Zakres warto

ś

ci

Uporz

ą

dkowanie

bool

8 bitów

0 lub 1

1

char

8 bitów

0 ...... 255

1

signed

char

8 bitów

–128 .. 0 ...... 127

1

unsigned

char

8 bitów

0 ...... 255

1

signed

short

16 bitów

–32 768 .. 0 .. 32 767

2

unsigned

short

16 bitów

0 .. 65 535

2

signed

int

16 bitów

–32 768 .. 0 .. 32 767

2

unsigned

int

16 bitów

0 .. 65 535

2

signed

long

32 bity

–2

31

.. 0 .. 2

31

–1

2

unsigned

long

32 bity

0 .. 2

32

–1

2

signed

long long

64 bity

–2

63

.. 0 .. 2

63

–1

2

unsigned

long long

64 bity

0 .. 2

64

–1

2

MSP430 IAR C/C++ Compiler Reference Guide

for Texas Instruments’ MSP430 Microcontroller Family.

IAR Systems, Tab. 30 – Integer types

7

ARM

Typy danych

RealView

®

Compilation Tools. Compiler Reference Guide.

Version 4.0. ARM DUI 0348C, Tab.5.2

Rozmiar

Typ

w bitach

Uporz

ą

dkowanie w bajtach

char

8

1 bajt (byte-aligned)

short

16

2 pół-słowo (halfword-aligned)

int

32

4 słowo (word-aligned)

long

32

4 słowo (word-aligned)

long long

64

8 podwójne-słowo (doubleword-aligned)

float

32

4 słowo (word-aligned)

double

64

8 podwójne-słowo (doubleword-aligned)

long double

64

8 podwójne-słowo (doubleword-aligned)

All pointers

32

4 słowo (word-aligned)

bool (C++ only)

8

1 bajt (byte-aligned)

_Bool (C only)

8

1 bajt (byte-aligned)

wchar_t (C++ only)

16

2 pół-słowo (halfword-aligned)

Bajt, pół-słowo

(half-word)

, słowo

(word)

,

podwójne słowo

(double word)

..

0

15

N

Word

Low

Byte

N+1

High

Byte

8 7

0

15

N

Doubleword

Low Word

16

31

N+2

High Word

0

N

Double Quardword

Low Quardword

63

64

N+8

High Quardword

127

32-bit microprocessor

ARM core

2)

word

halfword

1)

Figure 4-1. Fundamental

DataTypes

1)

Intel

®

64 and IA-32 Architectures Software Developer’s

Manual. Volume 1: Basic Architecture. Intel, December 2009

2)

Steve Furber: ARM System-on-chip Architecture.

Second edition. Addison-Wesley, 2000

0

N

Quardword

Low Doubleword

31

32

N+4

High Doubleword

63

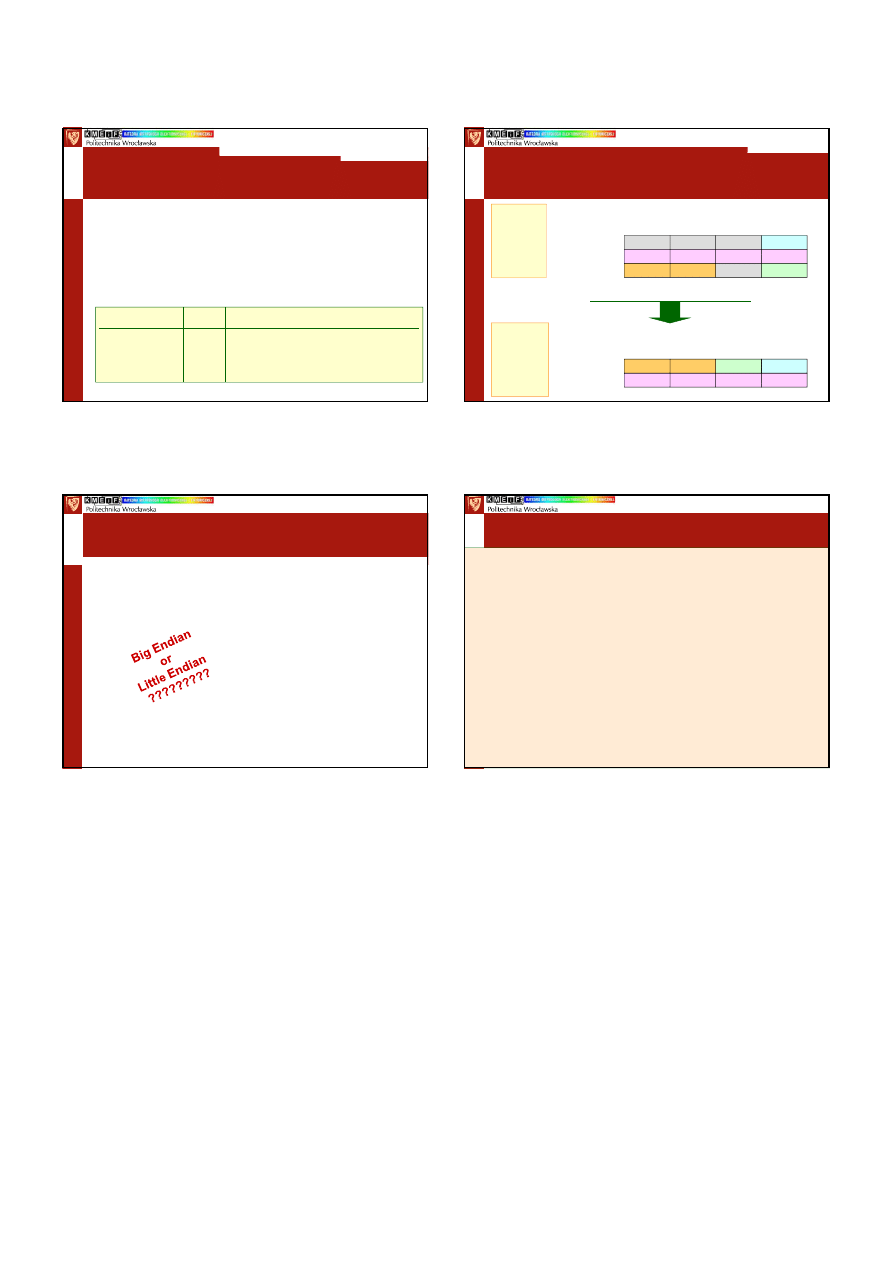

Kolejność bajtów

(Byte order / Endianness)

Format: Little / Big Endian

0

7

A

8

15

A+1

bardziej

znacz

ą

cy bajt

(High-order Byte)

Low Byte

High Byte

?

?

A

A+1

A+2

A

−

1

format: Little Endian

adres pami

ę

ci

(memory address)

A+1

A

format: Big Endian

High Byte

?

?

Low Byte

mniej

znacz

ą

cy bajt

(Low-order Byte)

0

7

8

15

bardziej

znacz

ą

cy bajt

(High-order Byte)

mniej

znacz

ą

cy bajt

(Low-order Byte)

Cortex-M0

Kolejność zapisu bajtów

(Endianness)

Cortex™-M0 Devices. Generic User Guide.

ARM DUI 0497A, p.2-17

Cortex-Mx

taktuje pami

ęć

jak liniowy zbiór bajtów ponumerowanych

narastaj

ą

co od warto

ś

ci zerowej

Bajty

o numerach 0-3 przechowuj

ą

pierwsze (32–bitowe) zapisane

słowo, bajty o numerach 4-7 przechowuj

ą

drugie (32–bitowe) zapisane

słowo itp.

Kolejno

ść

zapisywanych bajtów w pami

ę

ci zale

ż

y od implementacji

zastosowanej przez producenta mikrokontrolera

Stosowane dwa

formaty zapisów

:

–

little-endian

(LPC1114–Cortex-M0, STM32L053–Cortex-M0+, ..)

–

byte-invariant big-endian

jako big-endian (zachowanie zgodno

ś

ci z

procesorami ARM7TDMI i ujednolicenie sposobu przesyłania danych

we wn

ę

trzu procesora)

Cortex-M0

Format little endian

16

23

A+2

24

31

A+3

B3

najbardziej

znacz

ą

cy b

ajt

(most significant byte)

(msbyte)

B0

?

B2

bardziej

znacz

ą

cy bajt

0

7

A

8

15

A+1

B1

mniej

znacz

ą

cy b

ajt

B0

najmniej

znacz

ą

cy bajt

(least significant byte)

(lsbyte)

A

A

−

1

adres pami

ę

ci

(memory address)

B1

A+1

B2

A+2

B3

A+3

?

A+4

Cortex™-M0 Devices. Generic User Guide.

ARM DUI 0497A, p.2-18

format

little-endian

lsbyte

msbyte

Implementacja przez

producentów

mikrokontrolerów

Cortex-M0

Format byte-invariant big-endian

(BE8)

16

23

A+2

24

31

A+3

B0

najbardziej

znacz

ą

cy b

ajt

(most significant byte)

(msbyte)

B1

bardziej

znacz

ą

cy bajt

Cortex™-M0 Devices. Generic User Guide.

ARM DUI 0497A, p.2-18

0

7

A

8

15

A+1

B2

mniej

znacz

ą

cy b

ajt

B3

najmniej

znacz

ą

cy bajt

(least significant byte)

(lsbyte)

A

A

−

1

adres pami

ę

ci

(memory address)

A+1

A+2

A+3

A+4

B0

?

B1

B2

B3

?

w procesorach Cortex-Mx

format big-endian zast

ą

piono

formatem

byte-invariant big-endian

lsbyte

msbyte

8

sposób składowania danych w pami

ę

ci tak, by mogły by

ć

efektywnie

wykorzystane

procesory

ARM

maj

ą

bajtowy

(8-bitowy),

pół-słowowy

(16-bitowy) i

słowowy

(32-bitowy) dost

ę

p do danych w pami

ę

ci

1)

kompilator

procesorów

ARM

rozmieszcza dane w pami

ę

ci wg. zasady:

2)

ARM Uporządkowanie danych

(Data alignment)

typ

liczba

rozmieszczenie w pami

ę

ci

bajtów

char

1

od dowolnego adresu

short

2

od adresu podzielnego przez 2 bez reszty

float, int, long

4

od adresu podzielnego przez 4 bez reszty

long long, double

8

od adresu podzielnego przez 4 bez reszty

1)

Big and Little Endian Byte Addressing. App Note 61

.

ARM,

DAI 0061A, p.4

2)

ARM

®

Compiler toolchain. Using the Compiler. Version 4.1.

ARM DUI 0472C, p.6-43

ARM - efektywne programowanie w C

Struktury danych w pamięci

(Little-Endian Memory System)

struct {

char

a;

int

b

;

char

c

;

short d

;

}

b

23 .. 16

wolne

d

7 .. 0

b

31 .. 24

wolne

d

15 .. 8

b

15 .. 8

wolne

wolne

b

7 .. 0

a

c

+0

+1

+2

+3

+0

+4

+8

Adres

uporz

ą

dkowanie zmiennych w pami

ę

ci

struct {

char

a;

char

c

;

short d

;

int

b

;

}

b

23 .. 16

d

7 .. 0

b

31 .. 24

d

15 .. 8

b

15 .. 8

b

7 .. 0

a

c

+0

+1

+2

+3

+0

+4

Adres

uporz

ą

dkowanie zmiennych w pami

ę

ci

efektywne wykorzystanie pami

ę

ci

A. Sloss, D. Symes, C. Wright: ARM System Developer’s

Guide. Desining and Optimizing System Software.

Morgan Kaufmann, 2004

USB Device Descriptor

Example

code struct usb_st_device_descriptor usb_device_descriptor =

{

0x12,

/* Size of this descriptor in bytes

*/

0x01,

/* DEVICE descriptor type

*/

0x1001,

/* Binay Coded Decimal Spec. release

*/

0x00,

/* Class code assigned by the USB

*/

0x00,

/* Sub-class code assigned by the USB

*/

0x00,

/* Protocol code assigned by the USB

*/

0x08,

/* Max packet size for EP0 (8, 16, 32, 64)

*/

0x

EB03

,

/* Vendor ID (

0x03EB

- Atmel)

*/

0x

0320

,

/* Product ID assigned by the manufacturer

(

0x2003

- HID Keyboard)

*/

0x0001,

/* Device release number

*/

0x01,

/* Index of manu. string descriptor

*/

0x02,

/* Index of prod. string descriptor

*/

0x03,

/* Index of S.N. string descriptor

*/

0x01

/* Number of possible configurations

*/

};

Problemy i pytania

1. Jakie typy danych okre

ś

laj

ą

skróty: char, short, int, float ?

2. Jaki jest zakres zmienno

ś

ci danych typu: char, short, int, float ?

3. Ile bajtów licz

ą

zmienne typu: bajt, half-word, word, double-word ?

4. Jaka jest kolejno

ść

bajtów zmiennej typu word przy zapisie typu little-endian ?

5. Jaka jest kolejno

ść

bajtów zmiennej typu word przy zapisie typu big-endian ?

6. Jaki jest wpływ uporz

ą

dkowania danych w pami

ę

ci na szybko

ść

działania CPU ?

7. Jakie fazy mo

ż

na wyró

ż

ni

ć

w trakcie wykonywania rozkazu przez procesor ?

8. Na czym polega przetwarzanie sekwencyjne (skalarne) ?

9. Jakie s

ą

wady i zalety przetwarzania sekwencyjnego ?

10. Na czym polega przetwarzanie potokowe (strumieniowe) ?

11. Jakie s

ą

wady i zalety przetwarzania potokowego ?

12. Jakie typy konfliktów wyst

ę

puj

ą

przy przetwarzaniu potokowym ?

13. Co oznaczaj

ą

poj

ę

cia: CISC oraz RISC ?

14. Jakie s

ą

wady i zalety procesorów typu CISC ?

15. Jakie s

ą

wady i zalety procesorów typu RISC ?

Wyszukiwarka

Podobne podstrony:

3 Przetw danych Typy proces 201 Nieznany (2)

Proces przetwarzania danych analogowych na cyfrowe, SPRAWOZDANIA czyjeś

4 Typy instrukcji Tryby adresowania 2015 www (1)

11 Przetworniki 2015 www

11 Przetworniki 2015 www

upowaznienie-do-przetwarzania-danych-osobowych, Prawo Pracy, Druki

Logistyka produkcji zajmuje się procesami transportowymi(2)-[ www.potrzebujegotowki.pl ], Ściągi i w

9 Liczniki 2015 www

PHP i Oracle Tworzenie aplikacji webowych od przetwarzania danych po Ajaksa

10 Serial Interface 2015 www

13 Power 2015 www

Wzor-upowaznienia-do-przetwarzania-danych-osobowych, Prawo Pracy, Druki

Upoważnienie do przetwarzania danych osobowych

Socjologia dla stosunków miedzynarodowych, Procesy kształtujące stosunki międzynarodowe - próba typo

ABC zasad bezpieczenstwa przetwarzania danych osobowych przy uzyciu systemow

L2 przetwarzanie danych

więcej podobnych podstron