1

Podstawy techniki

mikroprocesorowej

ETE006

Redukcja mocy

EMC

Andrzej Stępień

Katedra Metrologii Elektronicznej i Fotonicznej

Urządzenia medyczne

małe rozmiary układów to zmniejszony pobór mocy

zwi

ę

kszenie skali integracji (

wi

ę

cej funkcji w jednym układzie

) to

miniaturyzacja urz

ą

dze

ń

medycznych i wydłu

ż

enie okresu pracy przez

obni

ż

enie zu

ż

ycia energii

baterie głównym

ź

ródłem energii w aplikacjach małej mocy

mniejsza pojemno

ść

lub wi

ę

ksza waga akumulatorów do aplikacji o

wysokich pr

ą

dach wyj

ś

ciowych (

mniejsza rezystancja wewn

ę

trzna

) ni

ż

podobnej wielko

ś

ci akumulator o wysokiej rezystancji wewn

ę

trznej

szeroki zakres napi

ęć

zasilaj

ą

cych MCU, np. zasilanie napi

ę

ciem 1,8 V to

zazwyczaj dwie baterie alkaliczne o napi

ę

ciu 0,9 V

Kennelly s.: Reducing Power Consumption in Embedded

Medical Electronics. Medical Electronics Manufacturing, Spring 2007

Power

Consumption

in Golf

(das Auto)

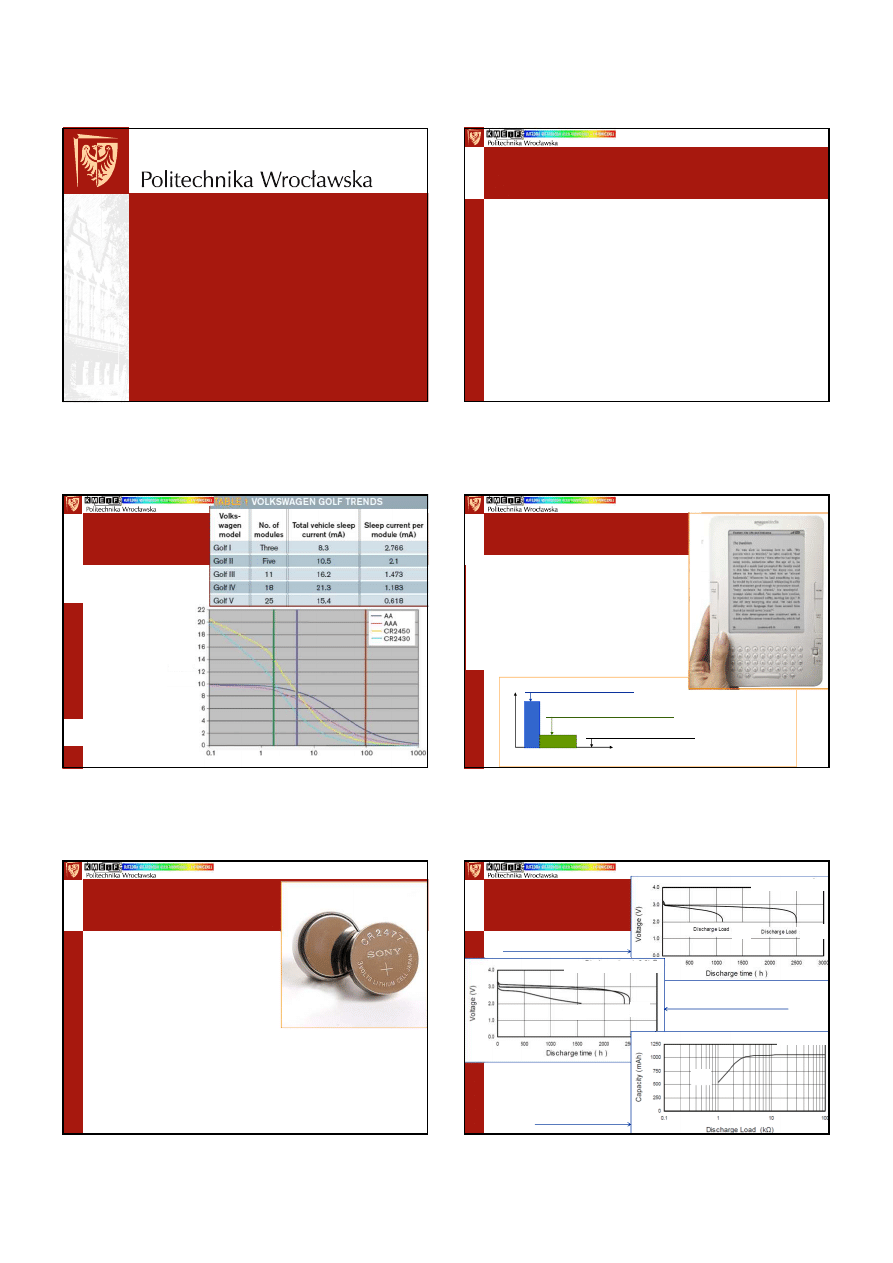

Rys. 4 wpływ poboru pr

ą

du

na

ż

ywotno

ść

baterii

Matt Ruff (Freescale Semiconductor)

Reducing power consumption in

batterypowered applications.

EDN, 2007, may 24, p. 81

ś

rednia warto

ść

pr

ą

du (

µ

A)

lata

eReader

Freescale

Phillips D. (Freescale): eReader System Design Overview.

IQ ARM (Information Quarterly), Volume 10, Number 1, 2011

Time

P

o

w

e

r

RUN: Page Update (5%)

WAIT: Display Update (10%)

STOP: No activity (85%)

Figure1 : Bistable design allows systems

to work and shut off to extend battery life

Freescale

proponuje czytnik

eReader

struktura: procesor

i.MX508, układ

zarz

ą

dzania energi

ą

MC13892,

3-osiowy

akcelerometr

MMA7660,

zbli

ż

eniowy

czujnik pojemno

ś

ciowy

MPR121 oraz

codec audio

SGTL5000

wsparcie dla

OS Linux

®

,

Android™

i

Windows

®

CE

.

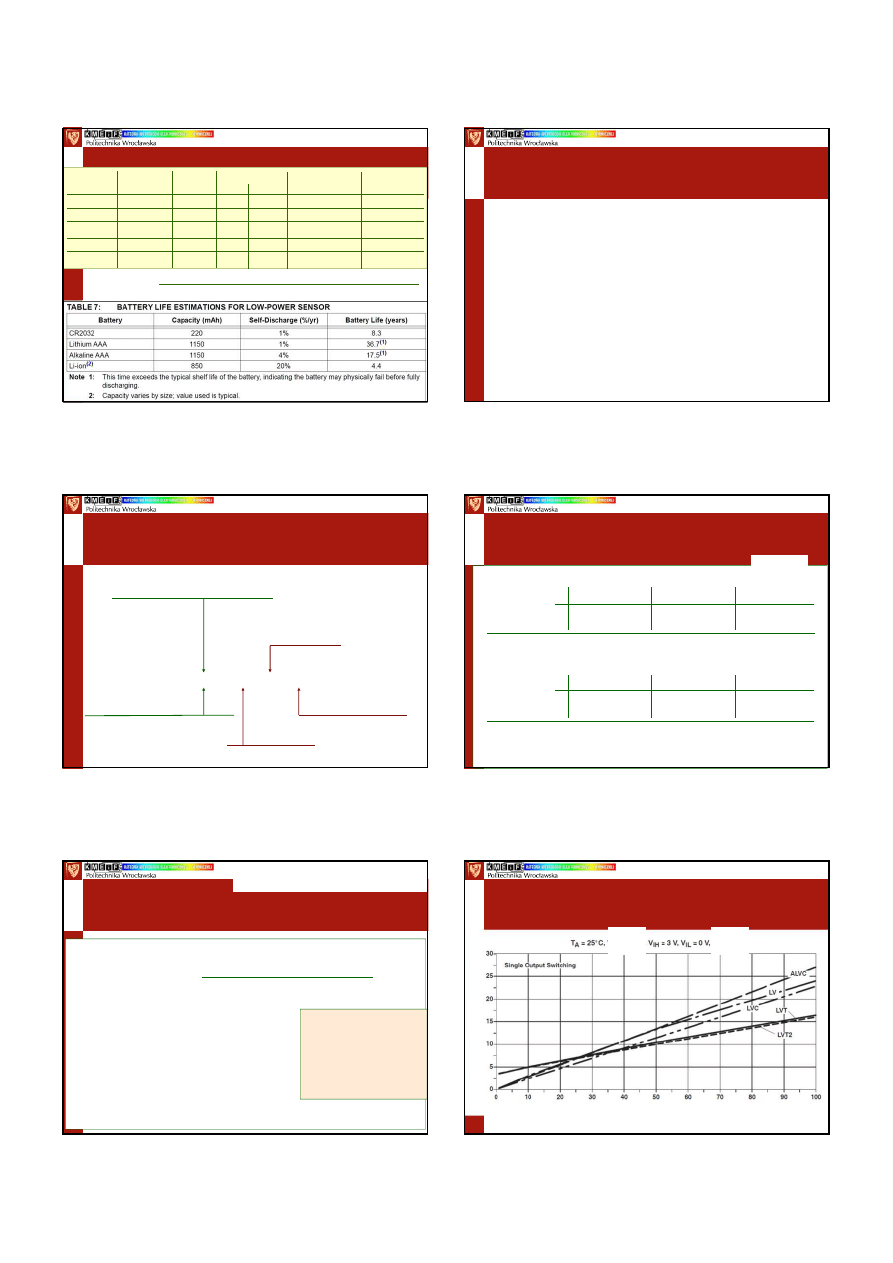

Battery

CR2477

[1#2]

Lithum Manganese Dioxide Battery. CR2477.

Data Sheet, Sony Corp.

Specifications:

Nominal Voltage

3V

Nominal Capacity

( 2.0V cutoff)

1000mAh

Standard Discharge

Current

0.4mA

Weight

10.0g

Applications:

Memory Back-up Power

Source for SRAM or Real Time Clock (RTC)

Battery

CR2477

[2#2]

Lithum Manganese Dioxide Battery. CR2477.

Data Sheet, Sony Corp.

Discharge Load vs.

Discharge Capacity

Discharge Characteristics

on Temperature

Discharge Characteristics

on Load

6.8k

Ω

3k

Ω

23

℃

℃

℃

℃

-10

℃

℃

℃

℃

60

℃

℃

℃

℃

23

℃

℃

℃

℃

Discharge Load 6.8k

Ω

Temperature 23

℃

℃

℃

℃

2.0V cut off

2

Battery

AN1416. Low-Power Design Guide.

Microchip, 2011, DS01416A, Tab. 6, 7

Chemistry

Type

Form

TYP

Voltage

Self_Discharge

Internal

value

profile

%/mo

resistance

NOM

Alkaline

Primary

AA/AAA 1.5V

Sloped

0.08%

150-300 m

Ω

Li/MnO

2

Primary

Coin Cell 3,0V

Flat

0.05%

10k-40k m

Ω

Li/FeS

2

Primary

AA/AAA 1.5V

Flat

0.30%

90-150 m

Ω

Lithium-ion Secondary

Varies

3.6V

Flat

20%

30-40 m

Ω

Ni/MH

Secondary AA/AAA 1.2V

Sloped

30%

30-40 m

Ω

Life

(

hours

) =

Capacity

(

mAh

)

System Current + Battery Self_Discharge Current

(

mA

)

Statyczny pobór mocy

(Static power consumption)

I

CC

– pr

ą

d zasilania (

supply current

)

moc statyczna:

P

S

=

V

CC

∗

I

CC

gdzie:

V

CC

=

napi

ę

cie zasilaj

ą

ce (

supply voltage

)

I

CC

= pr

ą

d zasilania urz

ą

dzenia, suma

pr

ą

dów upływno

ś

ciowych

(

leakage current

)

∆∆∆∆

I

CC

– dodatkowy pr

ą

d zasilania (

extra supply current

) dla ka

ż

dego z

wej

ść

, na których wyst

ę

puj

ą

napi

ę

cia inne ni

ż

0 lub 5V,

niepodł

ą

czone, ’pływaj

ą

ce’ wej

ś

cia (brak nasycenia tranzystorów

wej

ś

ciowych dla niepodł

ą

czonych wej

ść

)

CMOS Power Consumption and Cpd Calculation.

Texas Instruments, SCAA035B, June 1997, p.3

Dynamiczny pobór mocy

(Dynamic power consumption)

CMOS Power Consumption and Cpd Calculation.

Texas Instruments, SCAA035B, June 1997, p.4

P

D

=

∑

C

Ln

∗

V

CC

2

∗

f

I

∗

N

SW

liczba przeł

ą

czanych bitów

(

number of bits switching

)

polaryzowane pojemno

ś

ci wewn

ę

trzne układu

(

dynamic power-dissipation capacitance

)

napi

ę

cie zasilaj

ą

ce

(

supply voltage

)

cz

ę

stotliwo

ść

sygnału przeł

ą

czaj

ą

cego

(

signal frequency

)

wyj

ś

ciowe pojemno

ś

ci obci

ąż

enia

(

external/load capacitance

)

Cortex-M0/M0+ CORE

Typical supply current

http://arm.com/products/processors/cortex-m/cortex-m0.php

http://arm.com/products/processors/cortex-m/cortex-m0plus.php

ARM Cortex-M0 Implementation Data

180ULL

90LP

40LP

typical 1.8v, 25C typical 1.2v, 25C

typical 1.1v, 25C

Dynamic Power

64.3µW/MHz

12.5µW/MHz

5.1µW/MHz

Floorplanned Area

0.109 mm

2

0.03 mm

2

0.007 mm

2

ARM Cortex-M0+ Implementation Data

180ULL

90LP

40LP

typical 1.8v, 25C typical 1.2v, 25C

typical 1.1v, 25C

Dynamic Power

47.4 µW/MHz

9.37µW/MHz

3.8 µW/MHz

Floorplanned Area

0.098 mm

2

0.028 mm

2

0.0066 mm

2

ULL – ARM

®

Ultra Low Power Platform enables best-in-class; energy efficient

32-bit MCU processor implementations

LP – ARM

®

Low Power platform; best-in-class processor implementations

mniejsze

pojemno

ś

ci

wewn

ę

trzne

Ultra-Low Power

MCU

Ultra-Low Power MCU (“Apollo”). Ambiq Micro. Data Brief

http://www.embedded.com/electronics-news/4438424/

Sub-threshold-voltage--low-power-ARM-MCUs-are-here

Features

:

Ultra-low supply current

:

30

µ

A/MHz

executing from flash

High-performance ARM

Cortex-M4F

Processor,

24MHz

MAX

clock frequency

Ultra-low power memory

:

─

512kB of flash memory for code/data

─

64kB of low leakage RAM for code/data

Ultra-low power interface

for off-chip sensors:

─

10b

, 13-channel, 1MS/s

ADC

─

Temperature sensor with +/-2ºC accuracy

Wide operating range

: 1.8 – 3.8V, –40 to 85°C

32-bit ARM Cortex-M4F

microcontrollers have

energy consumption that

is

typically five to ten

times lower

than that of

MCUs of comparable

performance

Power Consumption With a Single

Output Switching for TI’s ’245

Figure 8. Power Consumption With a Single Output Switching for TI’s ’245

I

C

C

[m

A

]

Frequency [MHz]

CMOS Power Consumption and Cpd Calculation.

Texas Instruments, SCAA035B, June 1997

V

CC

=

3.3 V

No

Load

3

CMOS Power Consumption

[1#2]

Application Note. PCB-Design for Improved EMC. Guideline

for Applications with NEC Microcontroller. NEC, May 2006

Power

consumption of a

CMOS circuit

once operated at

2 MHz (red)

and

once

at 8 MHz

(blue)

.

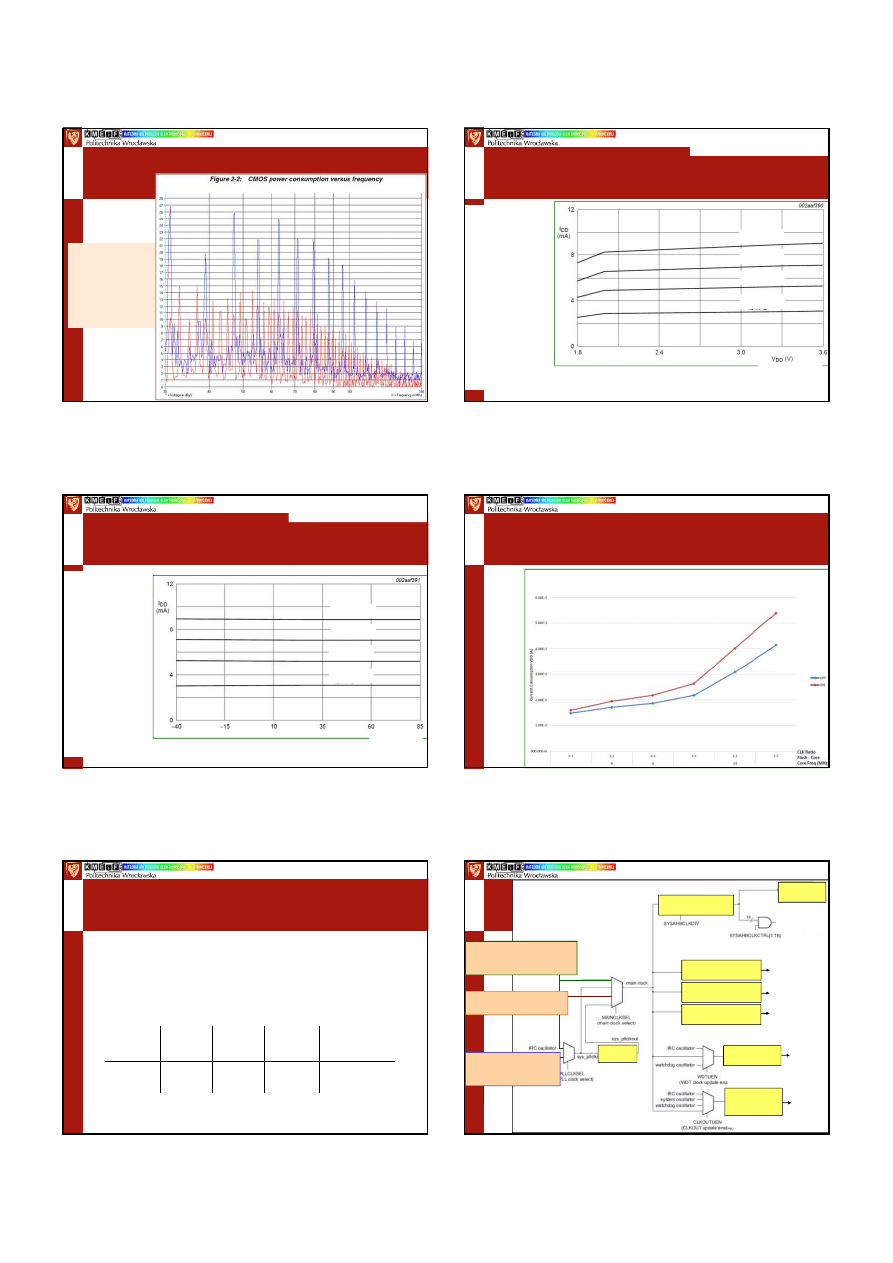

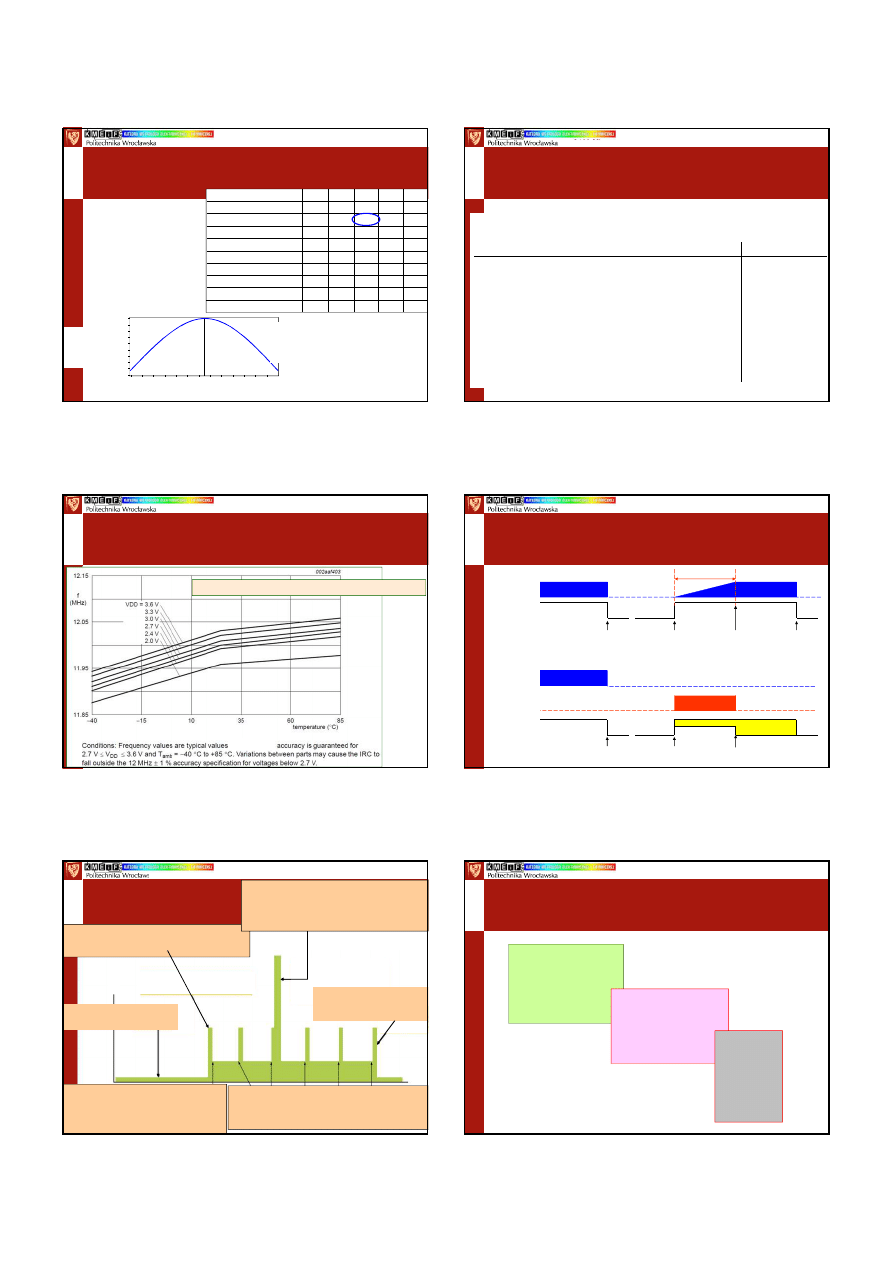

Cortex-M0

Typical supply current

[1#2]

LPC1110/11/12/13/14/15.

32-bit ARM Cortex-M0 microcontroller; up to 64 kB flash and 8 kB SRM.

NXP, Rev. 9.2 — 26 March 2014, Fig. 19

(1)

System oscillator and system PLL disabled; IRC enabled;

(2)

System oscillator and system PLL enabled; IRC disabled.

Conditions:

- T

amb

= 25

°

C;

active mode

entered executing

code while(1){}

from flash;

- all peripherals

disabled in the

SYSAHBCLKCTRL

register;

- all peripheral

clocks disabled;

- internal pull-up

resistors disabled;

- BOD disabled;

12MHz

(1)

24MHz

(2)

36MHz

(2)

48MHz

(2)

supply valtage

Cortex-M0

Typical supply current

[2#2]

LPC1110/11/12/13/14/15.

32-bit ARM Cortex-M0 microcontroller; up to 64 kB flash and 8 kB SRM.

NXP, Rev. 9.2 — 26 March 2014, Fig. 18

(1)

System oscillator and system PLL disabled; IRC enabled;

(2)

System oscillator and system PLL enabled; IRC disabled.

Conditions:

- T

amb

= 25

°

C;

active mode

entered executing

code while(1){}

from flash;

- all peripherals

disabled in the

SYSAHBCLKCTRL

register;

- all peripheral

clocks disabled;

- internal pull-up

resistors disabled;

- BOD disabled;

12MHz

(1)

24MHz

(2)

36MHz

(2)

48MHz

(2)

temperature

Power vs. Clock Frequency

Kinetis KL13 Microcontroller. 48 MHz ARM

®

Cortex

®

-M0+

and 64 KB Flash. Freescale, Rev. 2, 03/2015, Fig. 2

Run mode supply current vs. core frequency

Temperature = 25, VDD = 3, while loop located in Flash

All

Peripheral

CLK Gates

OFF

ON

3

12 MHz

48

Power vs. Clock Frequency

Burst Mode Operation

Energy consumed vs. processor speed for a 500 machine cycle task,

active mode (

MCS51

):

Clock

Machine

Total

Current

Frequency

Cycle

Time

I

CC

-Time

Period

Product

10 MHz

400 ns

200 ms

12,41 mA

248 mAs

30 MHz

133 ns

66,5 ms

34,66 mA

230 mAs (

–6%

)

Kevin Self: Microcontrollers Applications Engineer.

Dallas Semiconductor Corporation

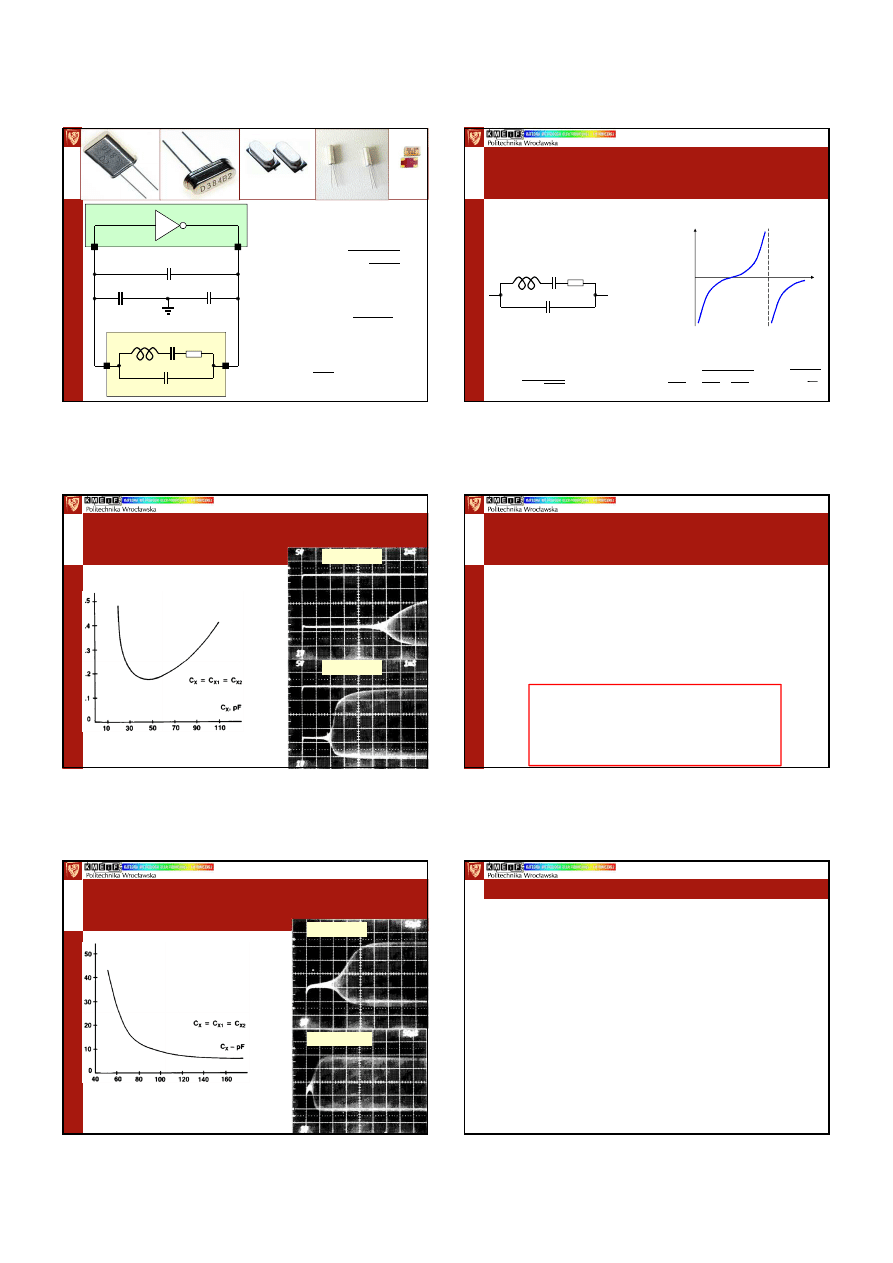

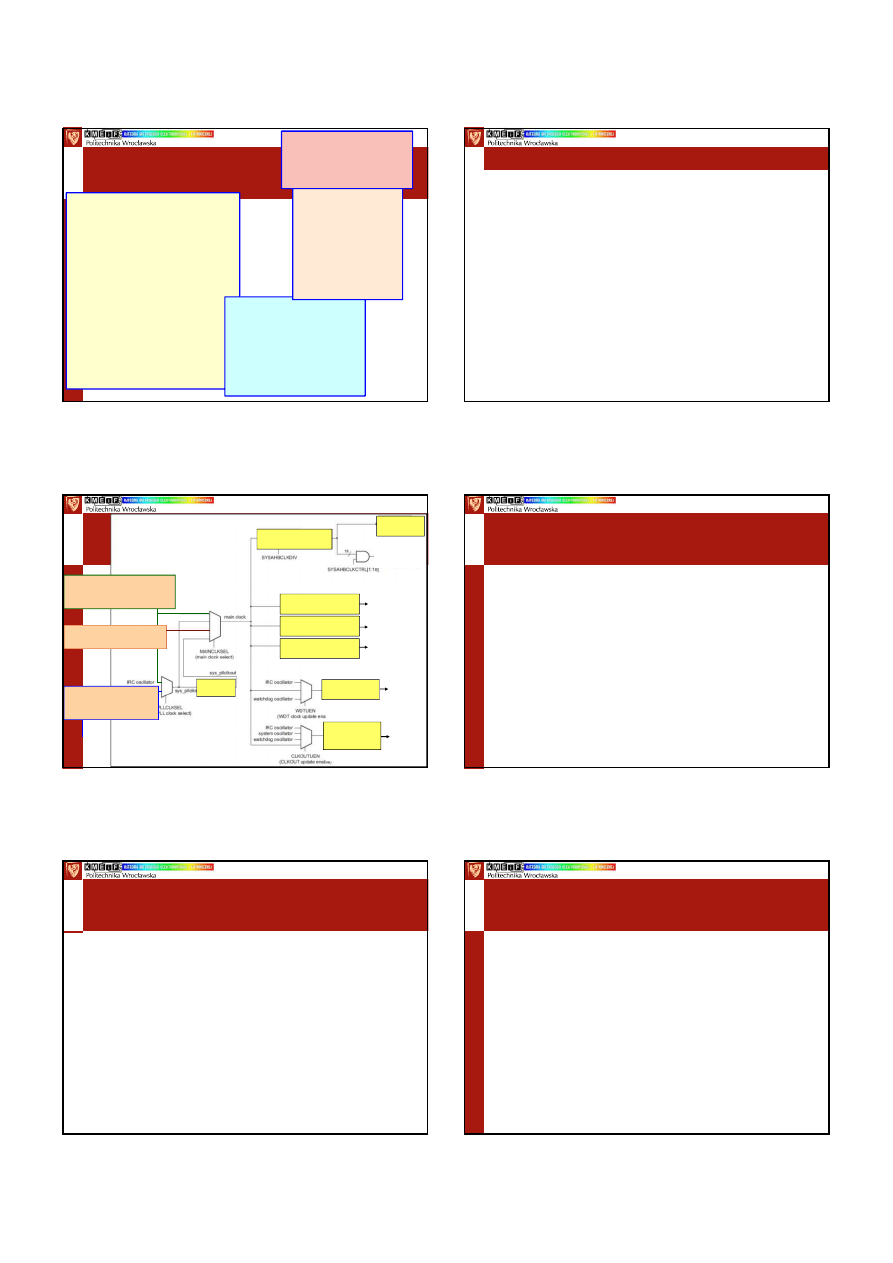

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, Fig. 8

4 MHz

Internal RC Oscillator

trimmed to 1%

LP

C1114

Clo

ck Generation

System

PLL

System

Clock Divider

ARM

Cortex-M0

WDCLK

SPI1_PCLK

SPI0_PCLK

UART_PCLK

SPI0 Peripheral

Clock Divider

UART Peripheral

Clock Divider

SPI1 Peripheral

Clock Divider

WDT Clock

Divider

CLKOUT

pin

CLKOUT pin

Clock

Divider

Watchdog Oscillator

(32.768 kHz)

On-chip

Crystal Oscillator

range: 1 to 25 MHz

AHB clocks

1 to 18

(memories &

peripherals)

4

Rezonator kwarcowy

(2/3)

L

1

C

1

R

1

C

0

A

B

C

X1

C

X2

C

X

MCU

Cz

ę

stotliwo

ść

rezonansu

równoległego:

f

a

= f

S

√

C

1

C

L

+ C

0

+

1

C

L

= C

X

+

C

X1

C

X2

C

X1

+ C

X2

gdzie:

f

a

- f

S

f

S

< 0,01 .. 0,5 %

HC 49U

HC 49S

HC 49S/SMD

HC 49S

/SMD

TF206

Crystal Oscillator

(1/2)

L

1

C

1

R

1

C

0

f

S

=

1

2

Π √

L

1

C

1

Układ zast

ę

pczy

rezonatora kwarcowego

bez obudowy i mocowania

Cz

ę

stotliwo

ść

rezonansu

szeregowego:

Cz

ę

stotliwo

ść

rezonansu

równoległego:

f

a

=

1

2

Π

√

1

L

1

C

1

1

L

1

C

0

+

= f

S

√

C

1

C

0

+

1

B. Gniewi

ń

ska, C. Klimek: Rezonatory i generatory

kwarcowe. WKiŁ, Warszawa 1980

Reaktancja

X

L

X

C

f

f

S

f

a

Start-Up

Crystal Oscillator

Oscillator Start-Up (4.608 MHz Crystal

from Standard Crystal Corp.)

V

CC

V

CC

X2

X2

C

X1,2

= 30 pF

C

X1,2

= 50 pF

T

S

, ms

TOM WILLIAMSON: Oscillators for Microcontrollers

APPLICATION NOTE AP-155, June 1983, Intel Corp.

Startup Time

Crystal Oscillator

COP8CBR9/COP8CCR9/COP8CDR9. 8-Bit CMOS Flash Microcontroller with 32k

Memory, Virtual EEPROM, 10-Bit A/D and Brownout.

DS101374, April 2002, National Semiconductor

CKI Frequency Startup Time

10 MHz

1 – 10 ms

3.33 MHz

3 – 10 ms

1 MHz

3 – 20 ms

455 kHz

10 – 30 ms

32 kHz

2 – 5 sec (low speed oscillator)

Clay Turner: Use of the TMS320C5x Internal Oscillator With External Crystals or Ceramic

Resonators. SPRA054, October 1995, Texas Instruments

„

Startup time

is dependent on the external components used, but

generally requires at last

100 ms

after power-up for the oscillator to

stabilize. For this reason, a

reset delay

of

150-200 ms

is recommended

following power-up.”

Ceramic Resonator

Start-Up

Oscillator Start-Up

(3.58 MHz Ceramic Resonator

from NTK Technical Ceramics)

T

S

,

µµµµ

s

TOM WILLIAMSON: Oscillators for Microcontrollers

APPLICATION NOTE AP-155, June 1983, Intel Corp.

C

X1,2

= 50 pF

C

X1,2

= 150 pF

X2

X2

Parametry rezonatorów kwarcowych

Nominal frequency range

f

32.768 kHz

Temperature

storage

T

STG

−

55

°

C to +125

°

C

range

operating

T

OPR

−

40

°

C to +85

°

C

Maximum drive level

GL

1,0

µ

W

MAX

Soldering condition

T

SOL

Twice at under 260

°

C within 10 s

or under 230

°

C within 3 min.

Frequency tolerance (standard)

∆

f/f

±

20ppm or

±

50ppm

(Ta=25

°

C, DL=0.1

µ

W)

Peak temperature (frequency)

θ

T

25

°

C

±

5

°

C

Temperature coefficient (frequency)

α

−

0.04ppm/

°

C

MAX

Load capacitance

C

L

6pF

Series resistance

R

1

50k

Ω

MAX

Motional capacitance

C

1

1.8pF

MAX

Shunt capacitance

C

0

0.9pF

MAX

Insulation resistance

IR

500M

Ω

MIN

Aging

fa

±

3ppm/Y

MAX

(Ta=25

°

C

±

3

°

C, first year)

Shock resistance

S.R.

±

5ppm

MAX

(test with: 3000G x 1/2 sine wave x 3 directions)

5

Crystal Specifications

Crystal Considerations with Dallas Real Time Clocks.

APP58, Dallas Semiconductor, 1995

Nominal Frequency

Parameter

Load Capacitance

Symbol

Min

Typ

Max

Units

Temperature Turnover Point

Parabolic Curvature Constant

Quality Factor

Series Resistance

Shunt Capacitance

Capacitance Ratio

Drive Level

32,768

kHz

6

pF

25

30

20

C

ppm/ C

0,042

Q

70.000

40.000

45

k

Ω

pF

1,1

1,8

430

600

1

µ

W

C

L

F

0

T

0

k

R1

C

0

D

L

C / C

0

1

o

o

Daiwa DS-26S Crystal

Specifications

0

-20

-40

-80

-60

-100

-120

-160

-140

-180

-40

-30

-20

-10

0

10

20

30

40

50

60

70

80

Temperature [

°

C]

Delta

frequency

[ppm]

DS1485

(25

°

C):

±

30 seconds / month (C

L

= 6 pF)

±

4 minutes / month (C

L

= 12 pF)

Quartz Crystals

&

Ceramic Resonators

Mariutti P.: Ceramic Resonator Oscillators and the C500,

C166 Microcontroller Families. ApNote AP242401, Infineon Technologies,1999

Principal technical Differences between Quartz Crystals and Ceramic

Resonators

Ceramic Resonator

Quartz Crystal

Price Factor (depends on quality)

1

2

Mechanical Shock Resistance

very good

good

Integrated Caps available

yes

no

Aging (for 10 years at room temperature) ± 3000 ppm

± 10 ppm

Initial Frequency Tolerance

± 2000 ... 5000 ppm

± 20 ppm

Temperature Characteristics

± 20 ... 50 ppm/°C

± 0.5 ppm/°C

Load Capacitance Characteristics

± 100 ... 350 ppm/pF

± 15 ppm/pF

Oscillation Rise Time

0.01 ... 0.5 msec

1 ... 10 msec

Quality Factor (Qm)

100 ... 5 000

10 000 ... 500 000

LPC111x

Internal RC osc. temperature characteristics

IRC-start-up time

(maximum of

6

µµµµ

s

on power-up)

12 MHz

±±±±

1%

LPC111x 32-bit ARM Cortex-M0 microcontroller;

up to 64 kB flash and 8 kB SRAM. NXP, Rev. 9.2 — 26 March 2014

Exit from Stop Mode

Cristal

Oscillator

Power

µ

C operating

µ

C enters

Stop Mode

Ext. Interrupt

Clock starts

Clock

stabile

µ

C enters

Stop Mode

µ

C operating

4 .. 10 ms

Power saved

RC

Oscillator

Cristal

Oscillator

Power

µ

C operating

µ

C enters

Stop Mode

Ext. Interrupt

Clock starts

µ

C enters

Stop Mode

µ

C operating

Zapotrzebowanie

na energię

Matt Ruff (Freescale Semiconductor): Reducing power

consumption in batterypowered applications. EDN, 2007, May 24, p. 82

RUN MODE

szybka reakcja programu

Szybki start, cz

ę

stotliwo

ść

taktowania 4 MHz

Porównanie

poboru energii

STOP 2

działa RTC, wł

ą

czony wewn. 2-kHz

generator budzenia rdzenia (WAKE-UP)

zasilane układy I/O i RAM

pobór pr

ą

du typowo, 700 nA @ 2V

RUN MODE

RTC wyznacza moment aktywnego trybu rdzenia

test zapotrzebowania na wydajno

ść

rdzenia

je

ś

li nie to powrót do trybu

STOP 2

STOP 1

DEVICE TIMES OUT, ENTER

STANDBY POWERDOWN,

TYPICALLY 20 nA AT 2V

Fig. 2 The power-

consumption profile

for stop and run

modes includes a

periodic wake-up

STOP 1

STANDBY POWERDOWN,

TYPICALLY, 20 nA AT 2V

RUN MODE

wymagana bardzo szybka reakcja programu

magistrale taktowane z maksymaln

ą

(20 MHz)

cz

ę

stotliwo

ś

ci

ą

z wewn

ę

trznego generatora

po zako

ń

czeniu tryb

STOP-2

MCU

Low-Power Mode

MSP430

(Texas Instruments)

:

–

low Power Mode 0

–

low Power Mode 1

–

low Power Mode 2

–

low Power Mode 3

–

low Power Mode 4

PIC32MZ

(Microchip)

:

–

CPU running: reducing

CPU clock frequency

–

CPU halted:

→

sleep mode

→

idle mode

V850

(Renesas)

:

–

idle

–

watch

–

sub-watch

–

halt

–

stop

6

Kinetis

(Freescale)

:

–

normal WAIT via WFI

–

Normal STOP via WFI

–

VLPR

(Very Low Power Run)

–

VLPW

(Very Low Power Wait) via WFI

–

VLPS

(Very Low Power Stop) via WFI

–

LLS

(Low Leakage Stop)

–

LLS3

(Low Leakage Stop3)

–

LLS2

(Low Leakage Stop2)

–

VLLS3

(Very Low Leakage Stop3)

–

VLLS2

(Very Low Leakage Stop2)

–

VLLS1

(Very Low Leakage Stop1)

–

VLLS0

(Very Low Leakage Stop0)

–

BAT

(backup battery only)

MCU - Cortex-Mx

Low-Power Mode

STM32L053

(STMicroelectronics)

:

–

sleep mode

–

low-power run mode

–

low-power sleep mode

–

stop mode with RTC

–

standby mode with RTC

–

standby mode without RTC

EFM32

(Silicon Labs)

:

–

EM0 Run Mode

–

EM0 Run Mode

–

EM1 Sleep Mode

–

EM2 Deep Sleep

Mode

–

EM3 Stop Mode

–

EM4 Shutoff Mode

LPC1114

(NXP)

:

–

sleep mode

–

deep-sleep mode

–

deep power-down mode

Tryby redukcji mocy

aktywny

(

Active Mode

) – aktywny cały procesor, CPU, układy peryferyjne

spowolnienia

(

Slow–Down Mode

) – zmniejszenie cz

ę

stotliwo

ś

ci taktowania

całego procesora i układów peryferyjnych (w poł

ą

czeniu z trybem

jałowy, bezczynno

ś

ci

(

Idle Mode

) – brak taktowania rdzenia (CPU nie

wykonuje programu), taktowanie wszystkich układów peryferyjnych (działaj

ą

);

programowy pocz

ą

tek trybu, zako

ń

czenie sygnałem RESET lub przez

przerwanie (je

ś

li zaprogramowane)

Atmel: tryb u

ś

pienia, w którym cz

ęść

MCU działa, a cz

ęść

nie działa

oczekiwania

(

Wait Mode

) – zatrzymanie CPU, aktywne oscylatory (Renesas)

gotowo

ś

ci

(

Standby Mode

) – niskoenergetyczny tryb 3 w MSP430 (LPM3),

blokada: CPU, MCLK, SMCLK, stałopr

ą

dowy generator DCO; aktywny sygnał

ACLK

wył

ą

czenia/zatrzymania

(

Power Down Mode

/

Stop Mode

/

Halt Mode

–

sprz

ę

towo lub programowo) – blokada wszystkich układów MCU (wyłaczenie

wszystkich generatorów), podtrzymanie zasilania rejestrów i wewn

ę

trznej

pami

ę

ci RAM

dynamiczne skalowanie napi

ę

ciem zasilania

(

Dynamic Voltage Scaling

)

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, Fig. 8

4 MHz

Internal RC Oscillator

trimmed to 1%

LP

C1114

Clo

ck Generation

System

PLL

System

Clock Divider

ARM

Cortex-M0

WDCLK

SPI1_PCLK

SPI0_PCLK

UART_PCLK

SPI0 Peripheral

Clock Divider

UART Peripheral

Clock Divider

SPI1 Peripheral

Clock Divider

WDT Clock

Divider

CLKOUT

pin

CLKOUT pin

Clock

Divider

Watchdog Oscillator

(32.768 kHz)

On-chip

Crystal Oscillator

range: 1 to 25 MHz

AHB clocks

1 to 18

(memories &

peripherals)

LPC1114

Tryb uśpienia

(Sleep Mode)

zatrzymanie taktowania rdzenia

(

clock to the core is stopped

) –

zawieszenie wykonywania instrukcji do czasu wyst

ą

pienia przerwania

lub zerowania procesora

redukcja mocy

(cz

ęś

ci dynamicznej) przez wył

ą

czenie działania

pami

ę

ci i wewn

ę

trznych magistral współpracuj

ą

cych z pami

ę

ci

ą

utrzymanie taktowania układów peryferyjnych

(

SYSAHBCLKCTRL

);

mog

ą

generowa

ć

przerwania – układy analogowe i cyfrowe pozostaj

ą

w

trybie aktywnym

podtrzymanie stanu rejestrów rdzenia, rejestrów układów

peryferyjnych, wewn

ę

trznej pami

ę

ci SRAM i statycznych stanów

wyprowadze

ń

(pinów)

UM10398. LPC111x/LPC11Cxx User manual

NXP, Rev. 12.3 — 10 June 2014, p. 48

LPC1114

Tryb głębokiego uśpienia

(Deep-sleep Mode)

zatrzymanie taktowania rdzenia

(

clock to the core is stopped

) – zawieszenie

wykonywania instrukcji do czasu wyst

ą

pienia przerwania lub zerowania

procesora (jak w trybie u

ś

pienia)

generator kwarcowy

(

system oscillator

)

generator RC

(

IRC

),

p

ę

tla

powielacza cz

ę

stotliwo

ś

ci

(

PLL

)

s

ą

wył

ą

czone

;

działa tylko generator

Watchdog’a

(

WDT

)

wszystkie układy analogowe s

ą

wył

ą

czane

(z wyj

ą

tkiem

BOD

i

WDT

) przez

wył

ą

czenie działania pami

ę

ci i wewn

ę

trznych magistral współpracuj

ą

cych z

pami

ę

ci

ą

tryb redukuje energi

ę

pobieran

ą

przez pami

ęć

Flash i układy analogowe

podtrzymanie stanu rejestrów rdzenia, rejestrów układów peryferyjnych,

wewn

ę

trznej pami

ę

ci SRAM i statycznych stanów wyprowadze

ń

(pinów)

UM10398. LPC111x/LPC11Cxx User manual

NXP, Rev. 12.3 — 10 June 2014, p. 49

LPC1114

Tryb całkowitego wyłączenia

(Deep power-down mode)

zatrzymanie taktowania procesora

(wszystkich układów, tak

ż

e

peryferyjnych)

z wyj

ą

tkiem systemu wybudzania

(

Wake-Up pins

)

linie PIO0_0 .. PIO0_11 oraz PIO1_0 umo

ż

liwiaj

ą

wybudzenie

procesora

(

Wake-Up pins

)

utrata zawarto

ś

ci rejestrów i pami

ę

ci SRAM z wyj

ą

tkiem 5

32-bitowych

rejestrów ogólnego przeznaczenia w układzie

PMU

(

GPREG0 .. GPREG4

)

wszystkie wyj

ś

cia alternatywne pozostaj

ą

w stanie wysokiej impedancji

(

tri-state

)

UM10398. LPC111x/LPC11Cxx User manual

NXP, Rev. 12.3 — 10 June 2014, p. 50

7

LPC1114

Zakończenie trybów redukcji mocy

zerowanie procesora

(

SYSRSTSTAT – SYStem ReSeT STATus register

)

─

zewn

ę

trzne:

sygnał RESET (

SYSRSTSTAT[1]

)

─

wewn

ę

trzne:

WDT (

Watchdog; SYSRSTSTAT[2]

)

BOD (

Brown–Out Detect; SYSRSTSTAT[3]

)

programowe zerowanie (

System reset; SYSRSTSTAT[4]

)

przerwanie

(je

ś

li zostało uaktywnione)

linie PIO0_0 .. PIO0_11 oraz PIO1_0 pełni

ą

rol

ę

wej

ść

wybudzaj

ą

cych

procesor

(

inputs to the start logic

)

wskazane jest taktowanie procesora z wewn

ę

trznego generatora RC

(

IRC

)

przed wł

ą

czeniem trybów redukcji mocy

(

czas wzbudzenia

maksymalnie 6

µµµµ

s

)

UM10398. LPC111x/LPC11Cxx User manual

NXP, Rev. 12.3 — 10 June 2014, p. 47 .. 51

LPC1110/11/12/13/14/15. 32-bit ARM Cortex-M0 microcontroller;

up to 64 kB flash and 8 kB SRAM. Data Sheet. NXP, Rev. 9.2 - 2014, Tab. 16

[1]

Typical ratings are not guaranteed. The values listed are at

temperature 25

°°°°

C

,

V

DD

= 3.3 V

[2]

T

amb

= 25

°°°°

C

[3]

I

DD

measurements were performed with all pins configured as GPIO outputs driven LOW

and pull-up resistors disabled

[4]

IRC enabled; system oscillator disabled; system PLL disabled

[5]

BOD disabled

[6]

All peripherals disabled in the SYSAHBCLKCTRL register. Peripheral clocks to UART

and SPI0/1 disabled in system configuration block

[7]

IRC disabled; system oscillator enabled; system PLL enabled

[8]

All oscillators and analog blocks turned off in the PDSLEEPCFG register (= 0x0000 18FF)

[9]

WAKEUP pin and RESET pin are pulled HIGH externally

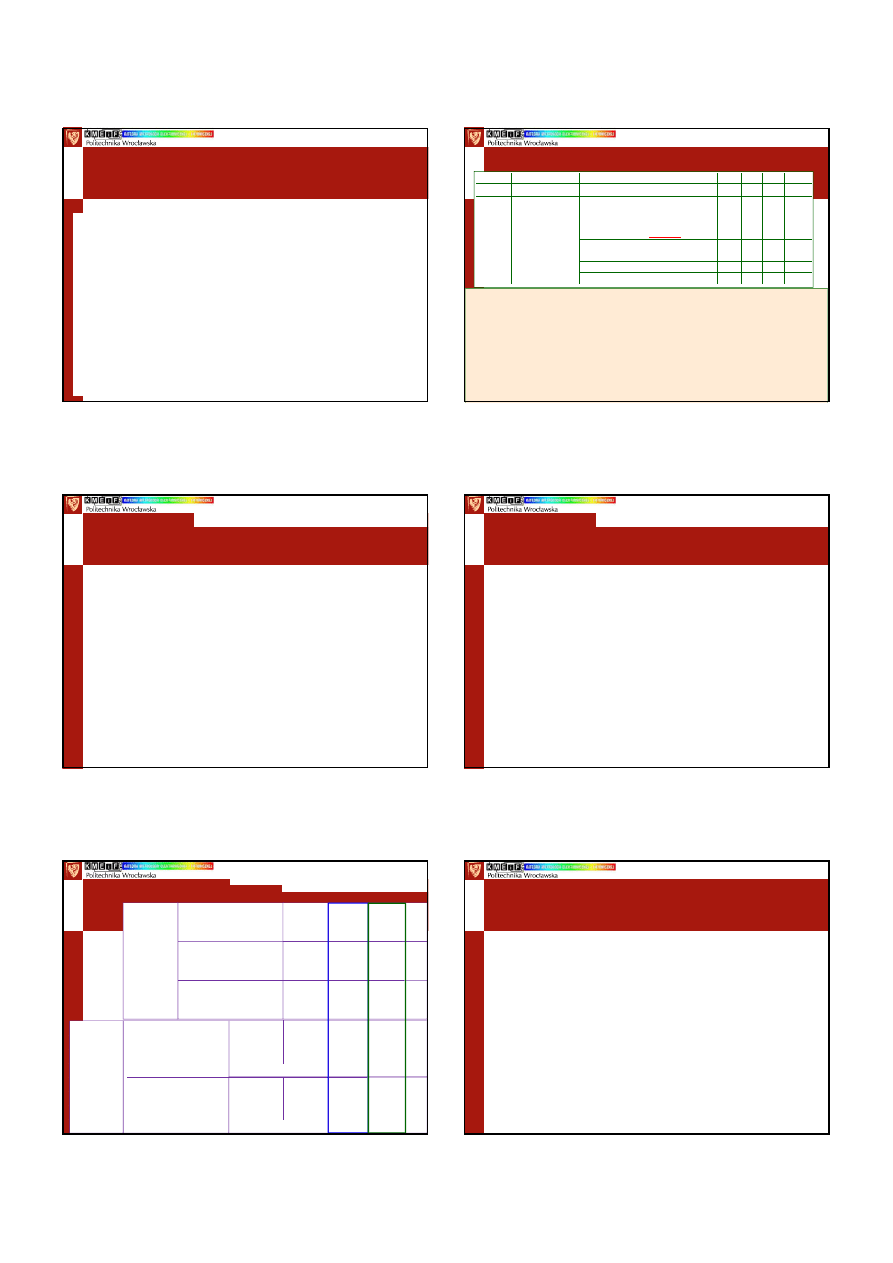

LPC1114 - parametry

Symbol Parameter

Conditions

Min Typ Max Unit

V

DD

supply voltage

1.8

3.3

3.6

V

I

DD

supply current

Active mode

,

code while(1) { }

executed from Flash

system clock = 12 MHz

[2..6]

3

mA

system clock =

50 MHz

[2, 3, 5..7]

9

mA

Sleep mode

2

mA

system clock = 12 MHz

[2..6]

Deep-sleep mode

[2, 3, 8]

6

µµµµ

A

Deep power-down mode

[2, 9]

220

nA

STM32L053xx

Low-Power Modes

[1#8]

The ultra-low-power STM32L053x6/8

support dynamic voltage

scaling

to optimize its power consumption in Run mode.

The voltage from the

internal low-drop regulator

that supplies the

logic can be adjusted according to the system’s maximum operating

frequency and the external voltage supply.

There are

three power consumption ranges

(

standard operating voltage V

DD

= 1.65 – 3.6 V

)

–

Range 1

: range limited, V

DD

= 1.71 – 3.6 V,

CPU running at up to 32 MHz

–

Range 2

: full V

DD

range,

maximum CPU frequency of 16 MHz

–

Range 3

: full V

DD

range,

maximum CPU frequency limited to 4.2 MHz

STM32L053xx.

Ultra-low-power 32-bit MCU ARM

®

-based Cortex

®

-M0+,

up to 64KB Flash, 8KB SRAM, 2KB EEPROM, LCD, USB, ADC, DAC.

Data Sheet. STMicroelectronics, September 2014, p. 14

STM32L053xx

Low-Power Modes

[2#8]

Seven low-power modes

are provided to achieve the best compromise

between low-power consumption, short startup time and available

wakeup sources:

Sleep mode

Low-power run mode

Low-power sleep mode

Stop mode with RTC

Standby mode with RTC

Standby mode without RTC

STM32L053xx.

Ultra-low-power 32-bit MCU ARM

®

-based Cortex

®

-M0+,

up to 64KB Flash, 8KB SRAM, 2KB EEPROM, LCD, USB, ADC, DAC.

Data Sheet. STMicroelectronics, September 2014, p. 14

Run mode, code with

data processing running from

Flash

&

RAM

STM32L051x6 STM32L051x8 Access line ultra-low-power

32-bit MCU ARM

®

-based Cortex®-M0+, up to 64 KB Flash,

8 KB SRAM, 2 KB EEPROM, ADC. Datasheet - production

data. STMicroelectronics, June 2014, Rev 3

Range 3, V

CORE

=1.2 V

VOS[1:0]=11

Range 2, V

CORE

=1.5 V,

VOS[1:0]=10

Range 1, V

CORE

=1.8 V,

VOS[1:0]=01

1 MHz

165

Flash

135

RAM

µ

A

2 MHz

290

240

µ

A

4 MHz

555

450

µ

A

4 MHz

0.665

0.52

mA

8 MHz

1.3

1.0

mA

16 MHz

2.6

2.0

mA

8 MHz

1.55

1.25

mA

16 MHz

3.1

2.45

mA

32 MHz

6.3

5.1

mA

I

DD

f

HSE

= f

HCLK

up to

16 MHz

included

Range 3, V

CORE

=1.2 V

VOS[1:0]=11

Range 1, V

CORE

=1.8 V,

VOS[1:0]=0

1

Dhrystone f

HCLK

=

555

Flash

450

RAM

µ

A

CoreMark =4MHz

585

575

µ

A

Fibonacci

440

370

µ

A

while(1)

355

340

µ

A

while(1), prefetch off

353

─

µ

A

I

DD

f

HSE

= f

HCLK

up to

16 MHz

included

Dhrystone f

HCLK

=

6.3

5.1

mA

CoreMark =32MHz

6.3

6.25

mA

Fibonacci

6.55

4.4

mA

while(1)

5.4

4.7

mA

while(1), prefetch off

5.2

─

mA

Dynamic Voltage Scaling

dynamiczne przeł

ą

czanie napi

ęć

zasilaj

ą

cych w układach, które nie

pracuj

ą

z pełn

ą

moc

ą

(np. odtwarzacz MP3, internetowe audio, kamera

cyfrowa itp.)

obni

ż

enie napi

ę

cia zasilania rdzenia (V

CC

), zmniejszenie cz

ę

stotliwo

ś

ci

taktuj

ą

cej (f

CLK

) w mikroprocesorach, procesorach sygnałowych (DSP)

pobór energii proporcjonalny do (V

CC

)

2

∗

F

CLK

, zmiana cz

ę

stotliwo

ś

ci

taktuj

ą

cej

wydłu

ż

enie czasu

ż

ycia baterii o ok. 15-25% przy oszcz

ę

dnym

gospodarowaniu energi

ą

wła

ś

ciwe zaprojektowanie struktury mikroprocesora, układu steruj

ą

cego

stabilizatorem napi

ę

cia

8

Current consumption

in Low-Power Run Mode

STM32L051x6 STM32L051x8 Access line ultra-low-power

32-bit MCU ARM

®

-based Cortex

®

-M0+, up to 64 KB Flash,

8 KB SRAM, 2 KB EEPROM, ADC. Datasheet - production

data. STMicroelectronics, June 2014, Rev 3

I

DD

(LP Run)

All peripherals

off,

code

executed from

RAM

, Flash

switched off,

V

DD

from 1.65 V

to 3.6 V

All peripherals

off,

code

executed from

Flash

, V

DD

from

1.65 V to 3.6 V

MSI (multispeed internal RC

oscillator)

clock, 65 kHz

f

HCLK

= 32 kHz,

T

A

=

─

40 °C to 25 °C

8.5

typ

µ

A

10

typ

µ

A

23

typ

µ

A

MSI clock, 65 kHz

f

HCLK

= 65 kHz

MSI clock, 131 kHz

f

HCLK

= 131 kHz

MSI (multispeed internal RC

oscillator)

clock, 65 kHz

f

HCLK

= 32 kHz,

T

A

=

─

40 °C to 25 °C

22

typ

µ

A

27.5

typ

µ

A

39

typ

µ

A

MSI clock, 65 kHz

f

HCLK

= 65 kHz

MSI clock, 131 kHz

f

HCLK

= 131 kHz

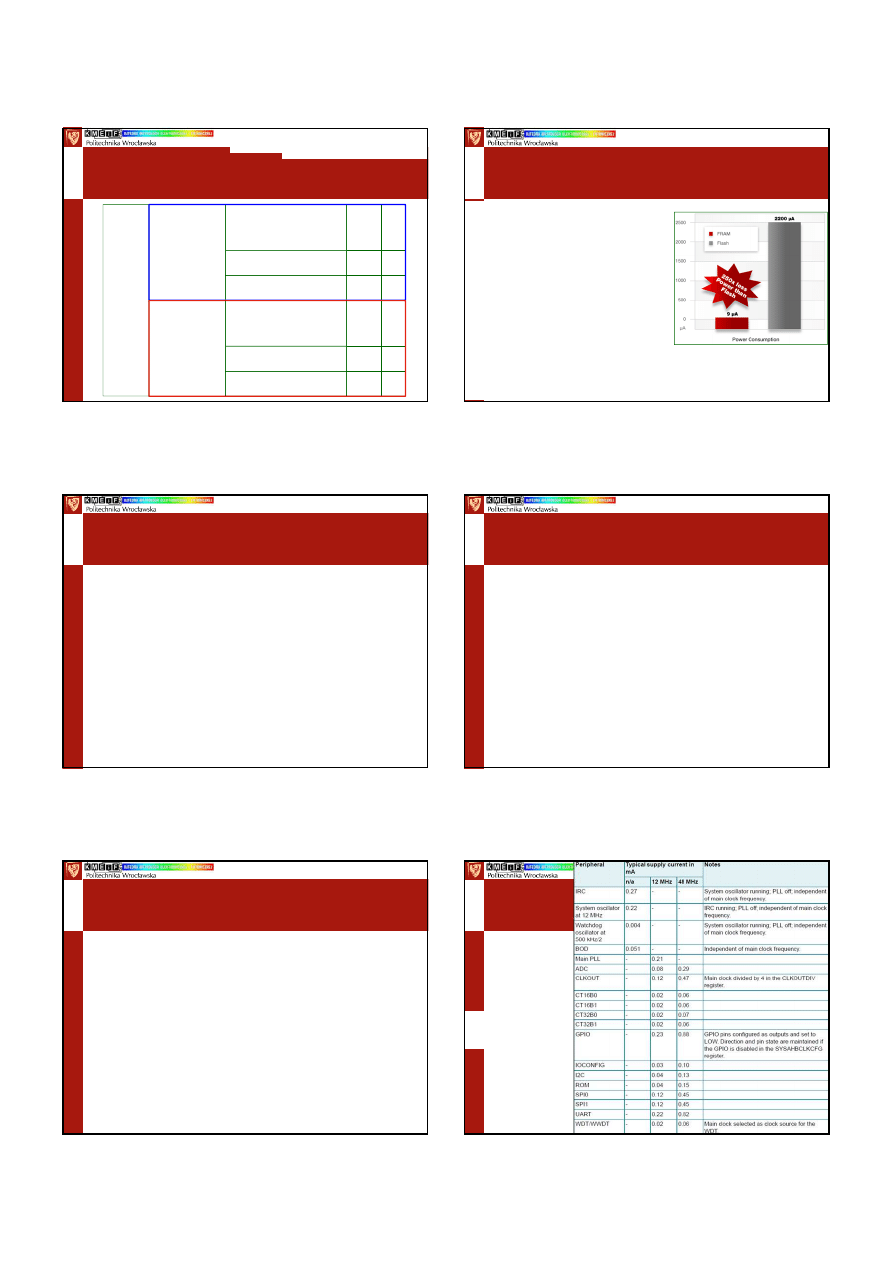

FRAM Technology MSP430FR57xx

Ultra-low-power Read/Write

Texas Instruments:

FRAM – Ultra-Low-Power Embedded Memory

Power Consumption

Both writing to memory at 12kB/s

MSP430 devices with embedded

FRAM

are cutting the industry’s best active power

consumption

Read and writes require just 1.5V

, so it is

able to operate without a charge pump,

unlike Flash and EEPROM

FRAM consumes 250x less power than

Flash-based devices

when running at

equal speed (12kB/s):

– CPU speed @ 8MHz

– Both memory options capped @ 12kB/s

throughput (typical application)

– FRAM consumes 9

µ

A

@ 12kB/s

– Flash consumes 2200

µ

A

@ 12kB/s

Metody redukcji mocy w MCU

specjalne funkcje zarz

ą

dzania energi

ą

w MCU; kontrola zu

ż

ycia energii

przez urz

ą

dzenia peryferyjne, okresowe u

ś

pienie MCU (

sleep mode

),

manipulowania oscylatorem (

oscillator start-up

)

kontrola zasilania urz

ą

dze

ń

peryferyjnych MCU - kardynalna zasada

zarz

ą

dzania energi

ą

w przeno

ś

nych systemach wbudowanych to

sterowanie poborem pr

ą

du

(wł

ą

czanie/wył

ą

czanie)

wewn

ę

trznych i

zewn

ę

trznych urz

ą

dze

ń

peryferyjnych

; np. wył

ą

czenie funkcji

’brownout’ w zastosowaniach akumulatorowych

tryb u

ś

pienia MCU

w czasie

małego zapotrzebowania

systemu na

zasoby lub moc obliczeniow

ą

wybudzenie MCU

przez

przerwanie

lub po

czasie

wyznaczonym przez

licznik – ni

ż

sze

ś

rednie zu

ż

ycie energii

Tryby redukcji mocy

Generatory

procedura Start-Up

– MCU w stanie bezczynno

ś

ci (

idle mode

), tzn. nie

wykonuje instrukcji:

─

w okresie stabilizacji drga

ń

oscylatora, mikrokontroler w stanie

zerowania, nie wykonuje instrukcji, a zu

ż

ywa energi

ę

─

czas trwania procedury

Start-Up

zale

ż

ny od typu rezonatora

ceramicznego lub kwarcowego, pojemno

ś

ci kondensatorów, typu

wewn

ę

trznego generatora MCU itp.

skrócenie procedury Start-Up

przez u

ż

ycie dwóch generatorów:

─

generatora RC o krótkim czasie startu

(~6

µµµµ

s)

– natychmiastowe

rozpocz

ę

cie wykonywania kodu (instrukcji)

─

zast

ą

pienie generatora RC stabilnym generatorem kwarcowym

(ceramicznym) o długim czasie startu (

~10ms

)

Tryby redukcji mocy

Porty

(Bidirectional I/O pins)

zu

ż

ycie energii

zale

ż

ne od sposobu sterowania wej

ś

ciami (pinami)

nieu

ż

ywane piny

portu skonfigurowane jako:

─

wej

ś

cia z wewn

ę

trznym/zewn

ę

trznym rezystorem pull-up (do zasilania

V

DD

) lub pull-down (do masy V

SS

)

─

wyj

ś

cia, w stanie niskim lub wysokim

port

skonfigurowany jako

wej

ś

cie

– pobór pr

ą

du = pr

ą

d upływu (leakage

current); taki sam przepływ pr

ą

du w przypadku poł

ą

czenia wej

ś

cia (pinu)

bezpo

ś

rednio z V

DD

(zasilanie) lub V

SS

(masa)

pó

ź

niejsze wykorzystanie wej

ś

cia (pinu) jako wej

ś

cie lub wyj

ś

cie bez

wi

ę

kszych zmian sprz

ę

towych

LPC1114

Power

Consumption

LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0

microcontroller; up to 64 kB

flash and 8 kB SRAM.

NXP, Rev. 9.2 — 26 March 2014

9

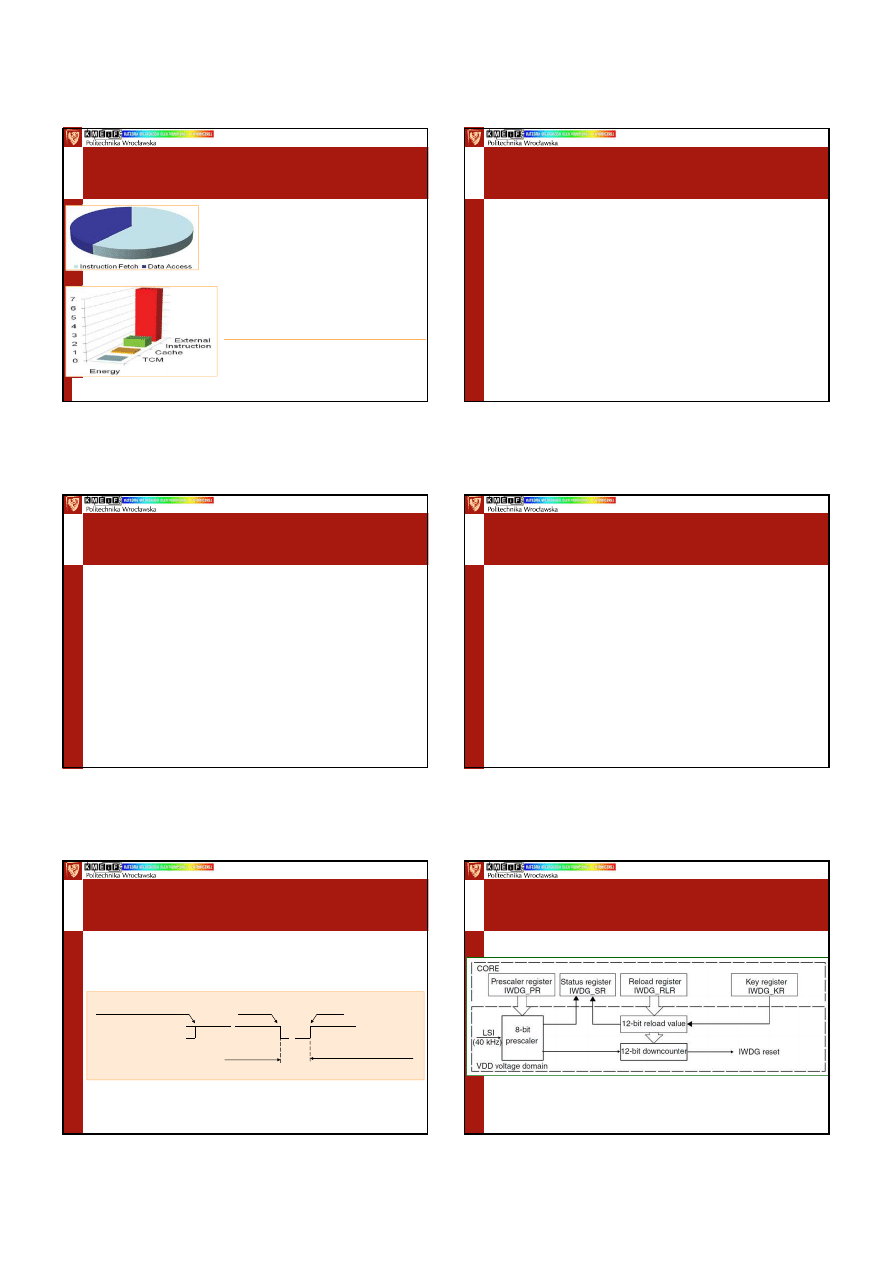

Computation is cheap

Communication is expensive

C. Shore: Developing Power-Efficient

Software Systems on ARM Platforms. Technology In-Depth, p.48-52

Figure 1: Memory access distribution

Cost of using

:

– 1

for

instruction

– 1/25

for access

Tightly Coupled

Memory

(TCM)

– 1/6

for access

cache

– 7

for access an

external RAM

In other words, for

each external RAM

access

,

we can execute 7 instructions,

access cache 40 times or TCM around

170 times for the same energy cost

Figure 2: Energy cost of

memory accesses

Minimize data memory access

Bezpieczeństwo

urz

ą

dzenia programowane, mikrokontroler, to automat do okre

ś

lonego,

zaprogramowanego zadania, wykonywanego w okre

ś

lonych warunkach

warunki te nie zawsze s

ą

brane pod uwag

ę

; niektóre zdarzenia s

ą

pomijane jako nieistotne (

?

)

nieprzewidziane zdarzenia, skutkuj

ą

ce bł

ę

dnym działaniem urzadzenia:

─

bł

ę

dy programisty

─

bł

ę

dy, awarie sprz

ę

tu

─

zakłócenia

ST7. 8-BIT MCU FAMILY USER GUIDE.

STMicroelectronics, July 2002

Bezpieczne programowanie

Watchdog

Pisa

ć

lepszy kod

sprawdza

ć

warunki pracy programu, podj

ąć

wszelkie

ś

rodki ostro

ż

no

ś

ci,

aby zapobiec awariom; przewidzie

ć

wahania zasilania, wpływ zakłóce

ń

elektromagnetycznych

nie istniej

ą

jednoznaczne metody wykrywania awarii procesora

za pomoc

ą

ś

rodków elektronicznych s

ą

praktycznie nie istnieje

popularn

ą

metod

ą

jest zastosowanie licznika-budzika (z okre

ś

lonym

opó

ź

nieniem) i wła

ś

ciwej reakcji programu

stosowa

ć

watchdog

, licznik wywołuj

ą

cy sprz

ę

towy

RESET

procesora

WATCHDOG

licznik okresowo od

ś

wie

ż

any

(ustawiany)

nie chroni w pełni działaj

ą

cego programu

:

─

niektóre cz

ęś

ci programu ulegaj

ą

awarii

─

cz

ęść

programu funkcjonuje poprawnie

zerowanie procesora/programu nie jest dobrym sposobem, poniewa

ż

ś

wiat zewn

ę

trzny mo

ż

e generowa

ć

problemy; wadliwe oprogramowanie

nie zeruje procesora

periodycznie zerowanie procesora przy braku wcze

ś

niejszego

od

ś

wie

ż

enia

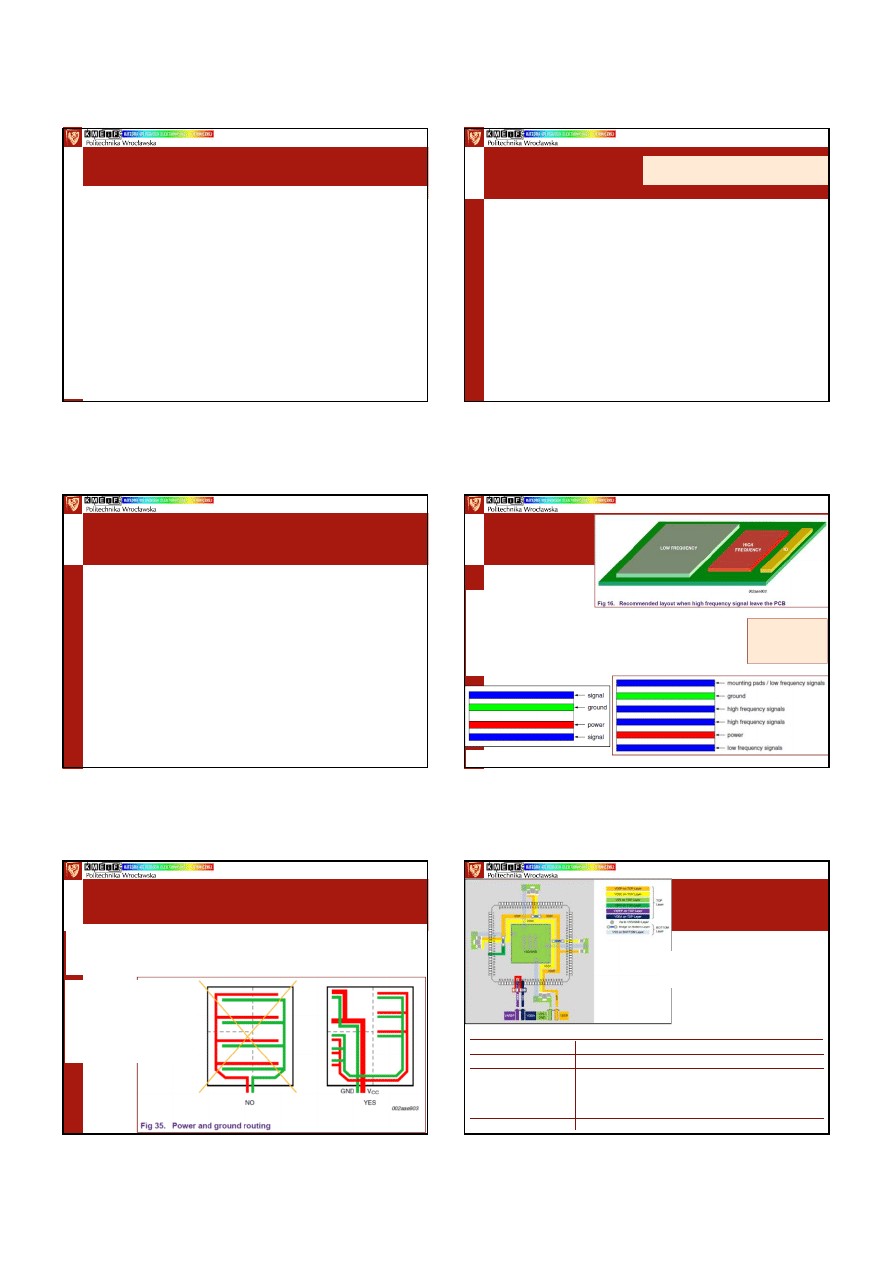

Jak działa

Watchdog

Start / Od

ś

wie

ż

anie

Watchdoga

Wewn

ę

trzny RESET

Przerwanie

????

?

?

Watchdog

RM0367. Reference manual. Ultra-low-power STM32L0x3

advanced ARM

®

-based 32-bit MCUs. STMicroelectronics, April 2014

Watchdog taktowany przez generator Low-Speed Internal RC

(

Low Speed Internal

)

10

Watchdog = ochrona

okre

ś

lenie wła

ś

ciwej warto

ś

ci

watchdoga

(opó

ź

nienia) jest trudne

rady

dla korzystaj

ą

cych z watchdoga:

─

nie aktywowa

ć

watchdoga podczas debugowania programu

– w

przeciwnym wypadku mo

ż

e pojawi

ć

si

ę

pewne nieoczekiwane zerowania

procesora

─

gdy program jest bez bł

ę

dów

, test kilku warto

ś

ci czasów od

ś

wie

ż

ania:

•

najpierw warto

ść

równa połowie maksimum

•

w przypadku wyst

ą

pienia resetu (który jest wykrywany przez

umieszczenie pułapki), podwoi

ć

warto

ść

i ponowny test

•

je

ś

li nie nast

ą

pi zerowanie, przyj

ąć

połow

ę

tej warto

ś

ci i ponowny test

•

zmniejsza

ć

warto

ść

w ten sposób jak najdłu

ż

ej, wykonuj

ą

c test programu

z wszystkimi jego funkcjami

•

po znalezieniu najmniejszej warto

ś

ci, która nie wywołuje resetu, nale

ż

y

pomno

ż

y

ć

t

ę

warto

ść

przez współczynnik bezpiecze

ń

stwa

ElectroMagnetic

Compatibility

kompatybilno

ść

elektromagnetyczna

(

ElectroMagnetic Compatibility

–

EMC

) – zdolno

ść

danego urz

ą

dzenia elektrycznego lub

elektronicznego do poprawnej pracy w okre

ś

lonym

ś

rodowisku

elektromagnetycznym i nieemitowanie zaburze

ń

pola

elektromagnetycznego zakłócaj

ą

cego poprawn

ą

prac

ę

innych urz

ą

dze

ń

pracuj

ą

cych w tym

ś

rodowisku

[Jarosław Szóstka: Fale i anteny. WKiŁ, Warszawa 2001]

oznacza to,

ż

e:

─

urz

ą

dzenie (system)

nie powoduje zakłóce

ń

w pracy

innych

urz

ą

dze

ń

(systemów),

─

urz

ą

dzenie (system)

nie jest wra

ż

liwe na zakłócenia

emitowane

przez

inne

urz

ą

dzenia (systemy),

─

urz

ą

dzenie (system)

nie powoduje zakłóce

ń

w swojej pracy

.

http://pl.wikipedia.org/wiki/Kompatybilnso

ść

_elektromagnetyczna

http://www.mg.gov.pl/Wspieranie+przedsiebiorczosci/

Bezpieczenstwo+produktow+i+uslug/Dyrektywy+

Bezpieczenstwa+Przemyslowego+i+Technicznego

Zakłócenia elektromagnetyczne

oddziaływanie zewn

ę

trznego pola elektromagnetycznego:

• przepi

ę

cia indukowane w zewn

ę

trznych doprowadzeniach,

ś

cie

ż

kach drukowanych

• przepi

ę

cia indukowane w wewn

ę

trznych doprowadzeniach

(indukcyjno

ś

ci i pojemno

ś

ci poł

ą

cze

ń

struktury wewn

ę

trznej z

wyprowadzeniami)

emisja własnego pola elektromagnetycznego:

• bł

ę

dne wykonanie poł

ą

cze

ń

dla du

ż

ych pr

ą

dów obci

ąż

e

ń

• nadmiarowe, bezzasadne generowanie dodatkowych sygnałów

wyładowania elektrostatyczne

podział komponentów na

grupy: analogowe, cyfrowe,

zasilanie, emituj

ą

ce silne zaburzenia, układy oraz we/wy –

rozmieszczenie ich z uwzgl

ę

dnieniem tej klasyfikacji

ś

cie

ż

ki przynale

ż

ne do ka

ż

dej z grup nie b

ę

d

ą

si

ę

przecinały,

poza tymi, które je ze sob

ą

ł

ą

cz

ą

.

PCB

M. Jaworska: EMC mikrokontrolerów – metody sprz

ę

towe i

programowe. ElektronikaB2B, 23 kwiecie

ń

2014

AN10897. A guide to

designing for ESD and

EMC.

NXP, Application note

Rev. 02 — 19 January

2010

Fig 20. Recommended stack-ups for 6-layer board

Fig 18. Recommended stack-ups

for 4-layer board

PCB ─ EMC

[1#2]

AN10897. A guide to designing for ESD and EMC.

NXP, Application note Rev. 02 — 19 January 2010

unikanie przesłuchów (

crosstalk

) lub sprz

ę

gni

ęć

(

coupling

),

ś

cie

ż

ki z du

ż

ymi

pr

ą

dami, z szybkimi czasami narostu / opadania (poni

ż

ej 10 ns) – utrzymanie

prawidłowego odst

ę

pu od innych

ś

cie

ż

ek, które biegn

ą

równolegle do nich lub

ś

cie

ż

kami masy

ś

cie

ż

ki zasilaj

ą

ce i masy

prowadzone równolegle –

minimalizacja impedancji

p

ę

tli

szczególnie wa

ż

ne dla

płytek 2-warstwowych

PCB ─

EMC

[2#2]

XMC4000. Microcontroller Series for Industrial Applications.

Infineon, Application Note, V1.0, 2013-11

Table 2 Decoupling / Stabilization

Capacitor Values

Power Supply Domain Number and Sizes of Decoupling / Stabilization capacitors

Pad Domain V

DDP

/V

SS

100 nF to each V

DDP

pin, 20

µ

F or higher to one pin

Analog Domain V

DDA

/V

SSA

100 nF to V

DDA

pin

Core Domain V

DDC

/V

SS

XMC4500: 100 nF to each V

DDC

pin,

10

µ

F ±10% X7R to one pin

XMC4400/XMC4200: 100 nF to each V

DDC

pin,

4.7

µ

F ±10% X7R to one pin

Hibernate Domain VBAT

Any value, depends on hibernate time

Figure 2 2-layer PCB Layout Example

for Decoupling of XMC4000

(single sided assembly)

11

EMC Test Summary

mbed NXP LPC1768

https://mbed.org/blog/entry/EMC-Testing-mbed

Only one unit (LPCXpresso1768) connected to

IBM Thinkpad via USB.

USB running mass storage class

Internal oscillators and PLLs all powered

Running test program to toggle I/O pins

szereg tryboelektryczny - zestawienie materiałów pod wzgl

ę

dem biegunowo

ś

ci

i wielko

ś

ci ładunku wytwarzanego podczas zetkni

ę

cia i rozdzielenia dwóch

materiałów:

L. Baranowski: Systemy kontroli ESD.

Elektronik, kwiecie

ń

2003

ludzka r

ę

ka:

+

• azbest

• futro królika

• włókno octanowe

• szkło

• mika

• ludzki włos

• nylon

• wełna

• ołów

• jedwab

• aluminium

• papier

stal

drewno

bursztyn

guma utwardzona

nikiel, mied

ź

srebro, mosi

ą

dz

złoto, platyna

jedwab octanowy

celuloid

poliester

akryl

polietylen

polipropylen

silikon

teflon

—

bawełna

Wyładowania elektrostatyczne

[1#2]

czynno

ś

ci i odpowiadaj

ą

ce im przykładowe ładunki w Voltach dla ró

ż

nych

poziomów wilgotno

ś

ci:

czynno

ś

ci

chodzenie po dywanie

chodzenie po podło

ż

u wykonanym z materiałów

syntetycznych

poruszanie si

ę

w obr

ę

bie stanowiska roboczego

wyci

ą

ganie układu scalonego z szyny z tworzywa

sztucznego

wyci

ą

ganie układu scalonego z podstawki

wyci

ą

ganie układu scalonego ze styropianu

wyci

ą

ganie płytki elektronicznej z opakowania z

tworzywa sztucznego

zapakowanie płytki elektronicznej w wytłoczk

ę

z

tworzywa sztucznego

10%

35.000

12.000

6.000

2.000

11.500

14.500

26.000

21.000

40%

15.000

5.000

800

700

4.000

5.000

20.000

11.000

55%

7.500

3.000

400

400

2.000

3.500

7.000

5.500

wilgotno

ść

wzgl

ę

dna

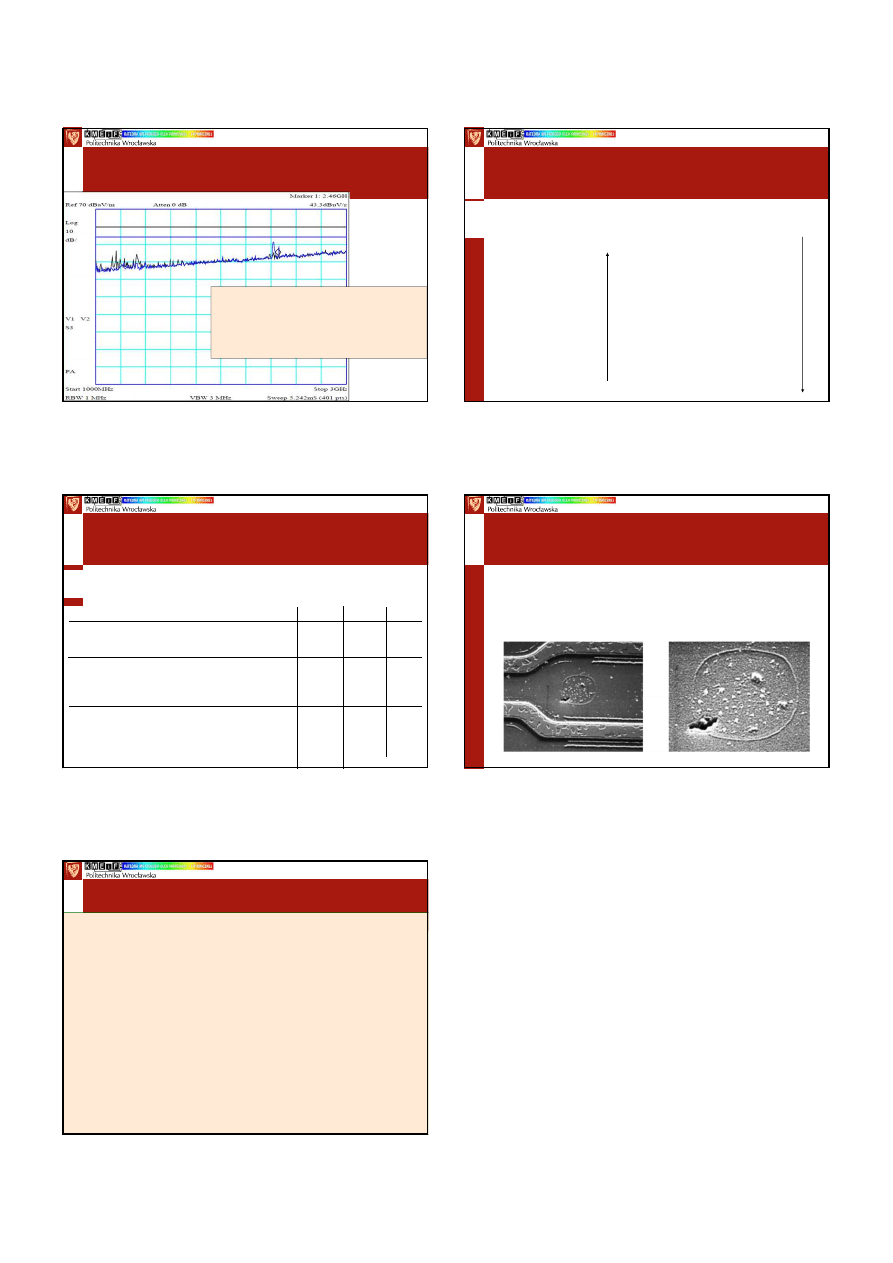

Wyładowania elektrostatyczne

[2#2]

L. Baranowski: Systemy kontroli ESD.

Elektronik, kwiecie

ń

2003

What Voltage Levels of ESD are Possible ?

It has been shown that human beings can be charged up to 38,000 volts

just by walking across a rug on a low-humidity day. In order for an ESD

pulse to be seen, felt, or heard, it must be in the range of 3000–4000 volts.

Many devices can be damaged well below this threshold

.

Punctured Barrier Junction After

ESD Test at 4000 V

Electrostatic Discharge (ESD) Application Report.

SSYA008 Texas Instruments, 1999

Problemy i pytania

1. Jaki jest wpływ temperatury na pojemno

ść

energetyczna baterii ?

2. Jaki jest wpływ pr

ą

du obci

ąż

enia na pojemno

ść

energetyczna baterii ?

3. Od czego zale

ż

y statyczne zapotrzebowanie na energi

ę

elektryczn

ą

?

4. Od czego zale

ż

y dynamiczne zapotrzebowanie na energi

ę

elektryczn

ą

?

5. Czy liczba przeł

ą

czanych wyj

ść

układu zwi

ę

ksza pobór mocy ?

6. Co nale

ż

y zrobi

ć

z nieu

ż

ywanymi wej

ś

ciami (pinami) procesora ?

7. Na czym polega start/stopowa praca procesora ?

8. Dlaczego w pracy start/stopowej zmniejsza si

ę

zapotrzebowanie na energi

ę

?

9. Jak redukowane jest zapotrzebowanie na energi

ę

w trybie slow-down ?

10. Jak redukowane jest zapotrzebowanie na energi

ę

w trybie idle ?

11. Jak redukowane jest zapotrzebowanie na energi

ę

w trybie power-down ?

12. Jak redukowane jest zapotrzebowanie na energi

ę

w trybie standby ?

13. Jak redukowane jest zapotrzebowanie na energi

ę

w trybie wait ?

14. Jaki jest czas wzbudzenia i stabilno

ść

pracy rezonatora kwarcowego ?

15. Jaki jest czas wzbudzenia i stabilno

ść

pracy układu RC ?

Wyszukiwarka

Podobne podstrony:

9 Liczniki 2015 www

10 Serial Interface 2015 www

FIiE-13.03.2015, UEK FIR, licencjat, 6 semestr, fundusze inwestycyjne i emerytalne Kania

Fundusze inwestycyjne i emerytalne wykład 8 13 04 2015

9. Wykład z językoznawstwa ogólnego - 13.01.2015, Językoznawstwo ogólne

9 bankowosc wyklad 9 13 01 2015

4 Typy instrukcji Tryby adresowania 2015 www (1)

3 Przetw danych Typy proces 2015 www (1)

7 Stos 2015 www

13 Power WDT 2010

12 DMA 2015 www

Lokalny program rewitalizacji osiedla „Stara Kolonia” w Brzeszczach 2005 2015 www old brzeszcze pl

6 Pamieci ROM RAM 2015 www

11 Przetworniki 2015 www

Przekazywanie ciepła S Pietrowicz 13 06 2015 temrin II

Chirurgia naczyniowa W3 13 01 2015 Żylaki kończyn dolnych

Chirurgia naczyniowa W3 13 01 2015 Zakrzepica żył głębokich

2 Architektura 2015 www

więcej podobnych podstron