Systemy sterowania

w elektronice przemysłowej

Wykład 4

dr inż. Bartosz Pękosławski

Łódź, dn. 12.04.2012

Katedra Mikroelektroniki i Technik Informatycznych

Politechnika Łódzka

Plan wykładu

2

1. Interfejsy urządzeń peryferyjnych – informacje podstawowe

2. Interfejs USART – komunikacja za pomocą RS232

3. Interfejs SPI

4. Interfejs Two-Wire (magistrala I

2

C)

5. Interfejs JTAG

6. Interfejs USB

Interfejsy urządzeń peryferyjnych

3

Rodzaj transmisji – szeregowa lub równoległa

Medium – przewód, fale radiowe, podczerwień

Prędkość transmisji

Kierunkowość transmisji – simpleks (simplex),

półdupleks (half duplex), dupleks (full duplex)

Kodowanie kanałowe

Kontrola poprawności transmisji

Transmisja szeregowa:

–

synchroniczna lub asynchroniczna

–

ramka

4

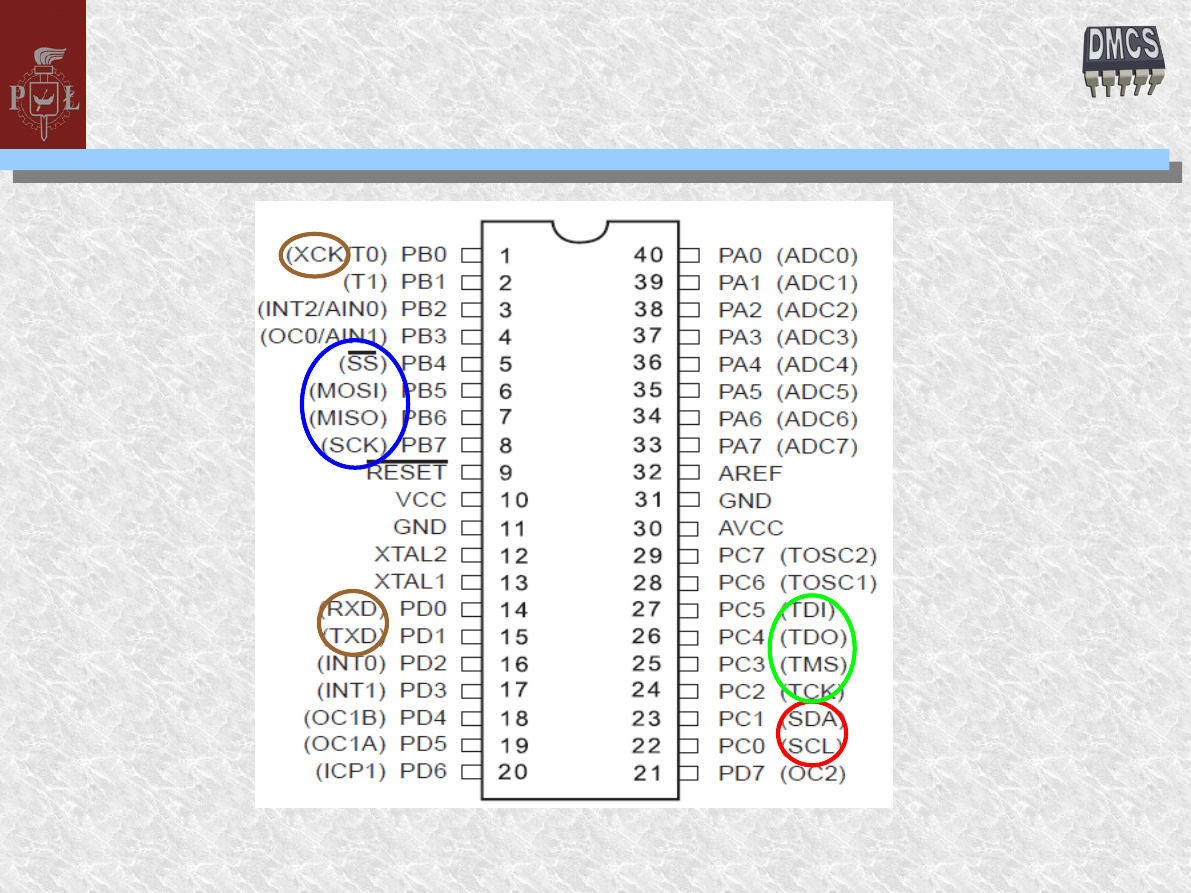

ATmega 32 –

wyprowadzenia interfejsów szeregowych

Interfejs Two-Wire

Interfejs SPI

Interfejs JTAG

Interfejs USART

Interfejs USART

5

Universal Synchronous and Asynchronous Receiver and Transmitter

Połączenie z innym mikrokontrolerem lub komputerem PC (RS232)

Możliwość wykorzystania dla RS232, RS422, RS485, IrDA, Bluetooth, itd.

Komunikacja szeregowa, synchroniczna lub asynchroniczna

Full-duplex lub half-duplex

Kontrola poprawności transmisji (parzystość)

Prędkość transmisji maks. 2,5 Mbps dla ATmega32

Linie:

RXD

TXD

XCK (transmisja synchroniczna)

dodatkowe – np. CTS, RTS, … dla RS232 (opcjonalnie)

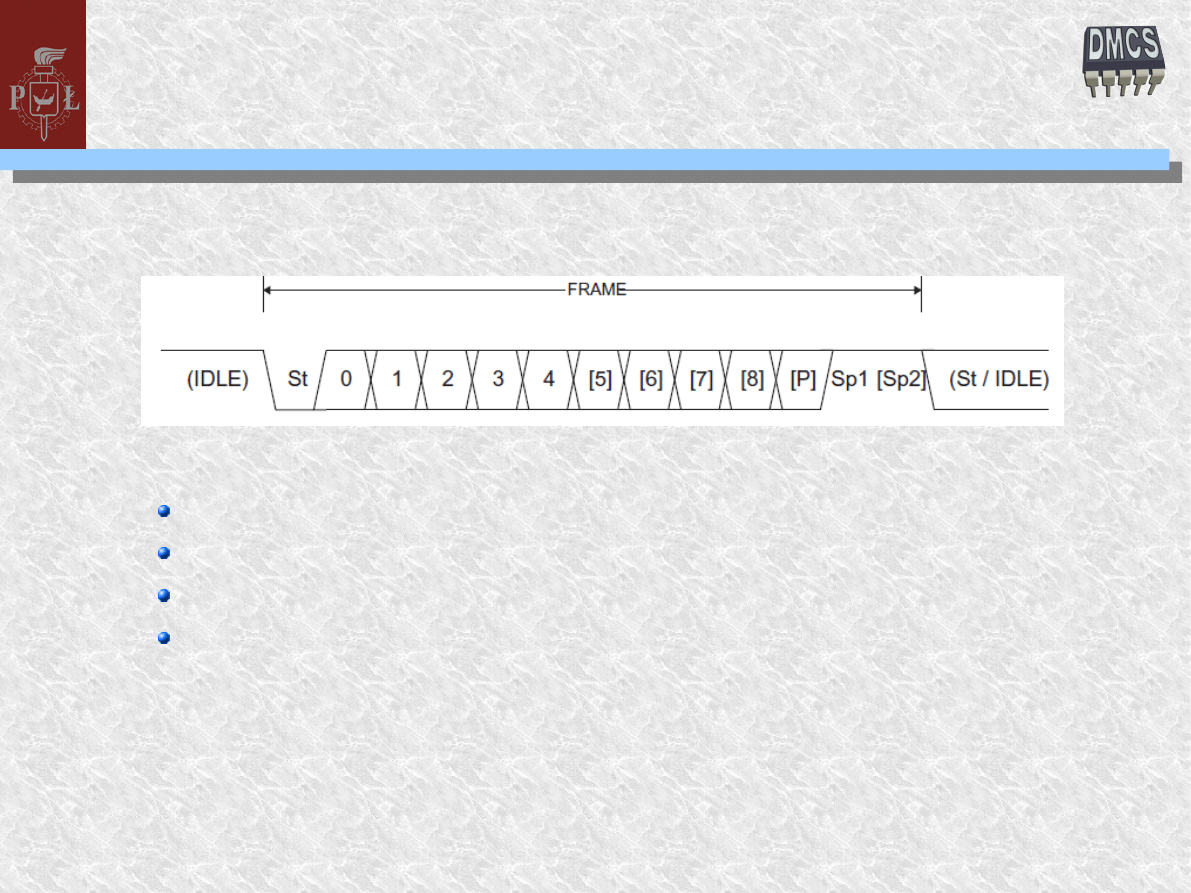

Interfejs USART – ramka

6

1 bit startu St

5-9 bitów danych

1 bit parzystości/nieparzystości [P] (opcjonalny)

1 lub 2 bity stopu Sp1 [Sp2]

Jednakowe ustawienia prędkości transmisji i liczby bitów dla nadajnika i odbiornika

Transmisja asynchroniczna

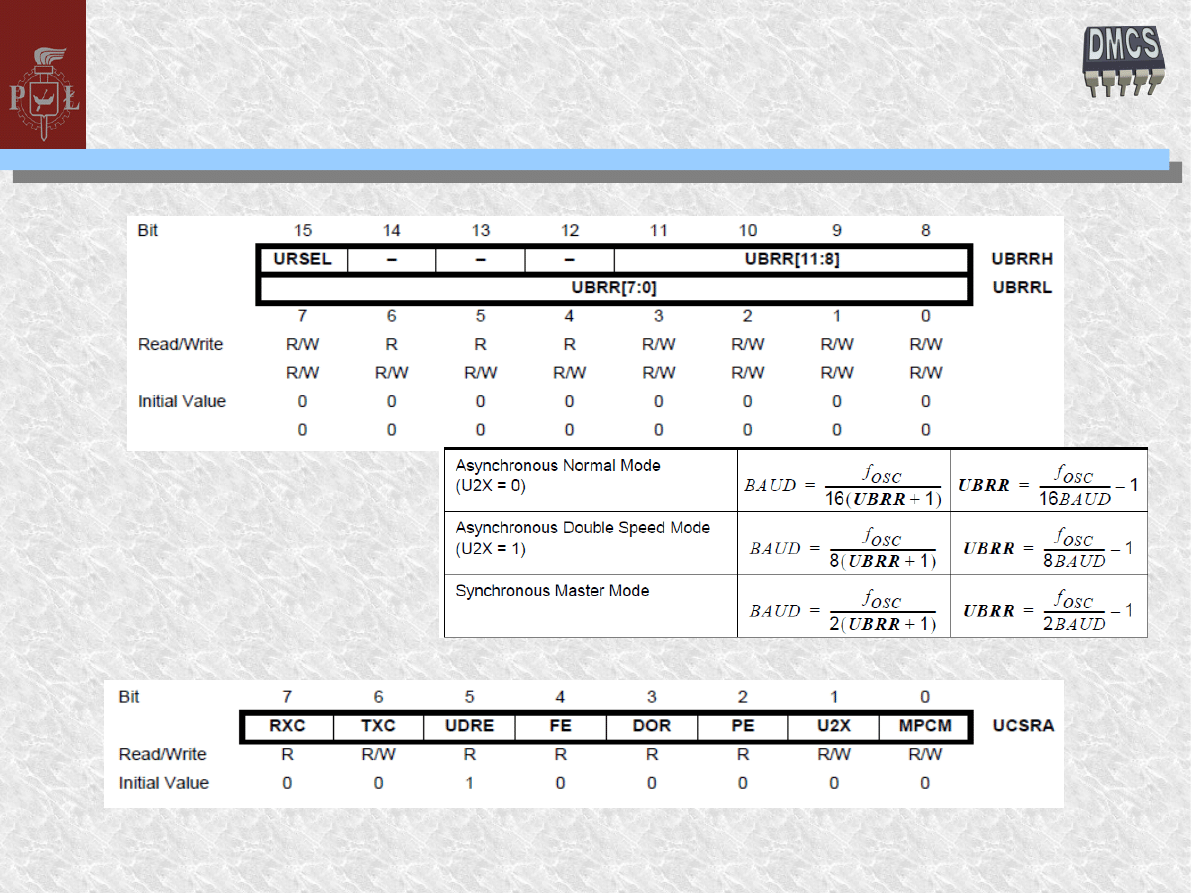

Interfejs USART – rejestry

7

Rejestr prędkości transmisji

URSEL – register select,

UBRR11:0 – baud rate

Rejestr kontrolno-statusowy A

RXC – receive complete, TXC – transmit complete, UDRE – data register empty, FE – frame error,

DOR – data overrun, PE- parity error, U2X – double speed, MPCM – multiprocessor communication

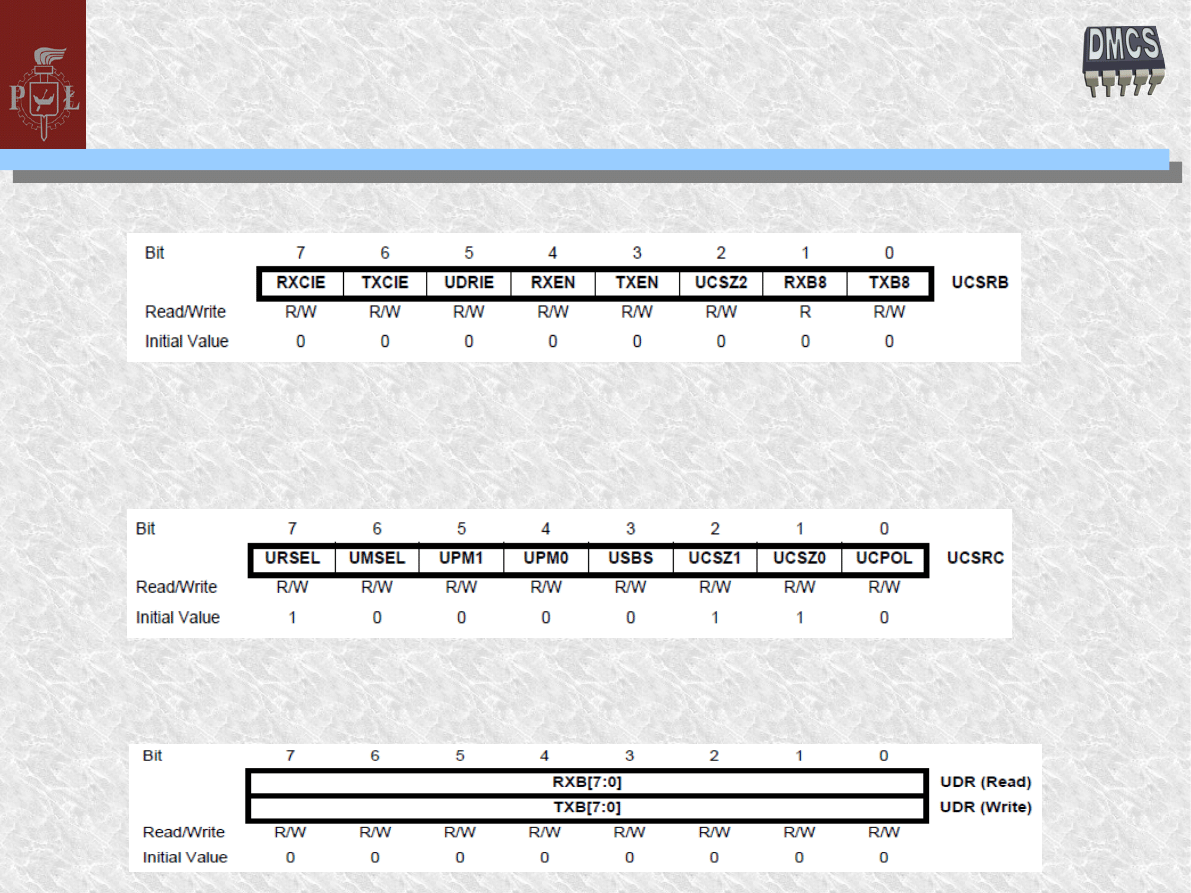

Interfejs USART – rejestry

8

Rejestr danych

Rejestr kontrolno-statusowy B

RXCIE – RXC interrupt enable, TXCIE – TXC interrupt enable, UDRIE – UDRE interrupt enable,

RXEN – receiver enable, TXEN – transmitter enable, UCSZ2 – character size,

RXB8 – receive data bit 8, TXB8 – transmit data bit 8

Rejestr kontrolno-statusowy C

URSEL – register select (UCSRC/UBBRH), UMSEL – mode select, UPM1:0 – parity mode,

USBS – stop bit select, UCSZ1:0 – character size, UCPOL – clock polarity (synchronous)

Interfejs USART – schemat transmisji

9

1. Inicjalizacja transmisji:

a) ustawienie rejestrów UBBRH i UBBRL

b) ustawienie rejestru UCSRB (TXEN, RXEN,...)

c) ustawienie rejestru UCSRC (USCZ1:0,...)

d) ustawienie bitu I w SREG (przy obsłudze przerwań)

e) zapis do rejestru UDR gdy UDRE=0 (rozpoczęcie transmisji)

2. Procedura obsługi przerwania / lub czekanie na flagę RXC/TXC:

a) odczyt danej z rejestru UDR (opcjonalne w przerwaniu)

b) wykonanie kolejnej transmisji gdy UDRE=0 (opcjonalne)

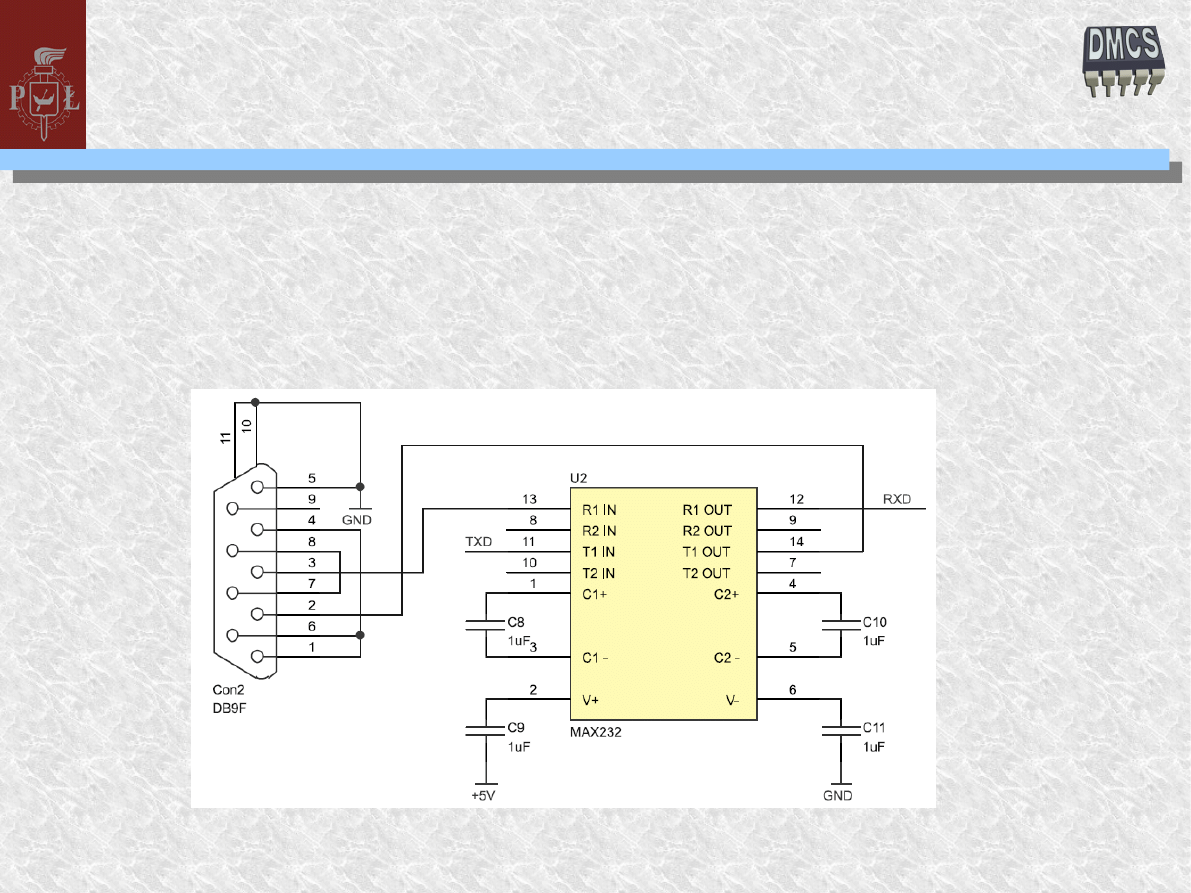

Interfejs USART – komunikacja RS232

10

Konieczność translacji napięć z poziomów TTL (0 ÷ 5V)

do poziomów mark (-15 do - 3V) i space (+3 do +15V)

Układ MAX232

Interfejs SPI

11

Serial Peripheral Interface (Motorola)

Połączenie mikrokontrolera z zewnętrznym zegarem RTC,

przetwornikiem A/C lub C/A, czujnikiem, innym mikrokontrolerem, itd.

Komunikacja szeregowa, synchroniczna

Full-duplex, do 10 Mbit/s (maks. 8 Mbit/s dla ATmega 32)

Magistrala master-slave

Linie:

MOSI (Master Output Slave Input)

MISO (Master Intput Slave Output)

SS (Slave Select)

SCK (Serial Clock)

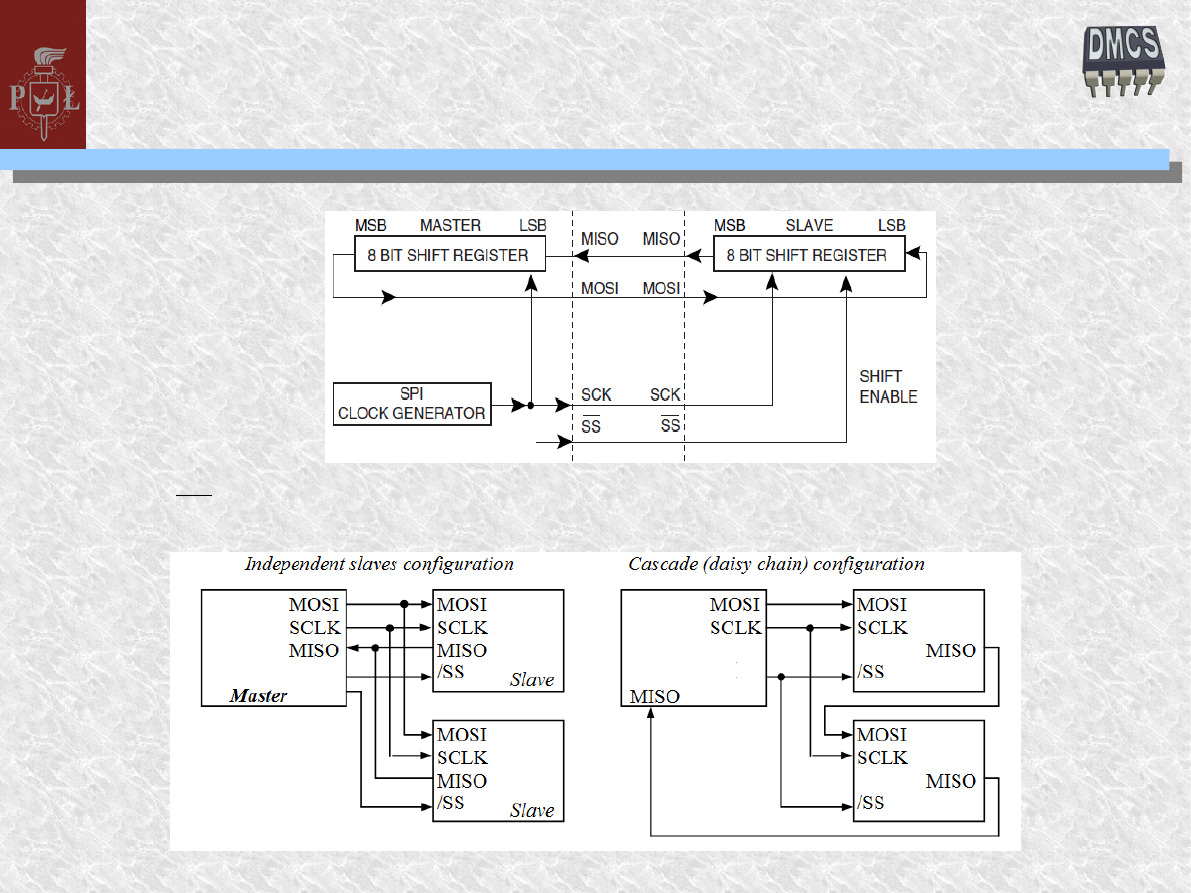

Interfejs SPI - magistrala

12

Rejestry przesuwne +

generator sygnału

zegarowego

Wejście SS tylko po stronie slave (sterowane po stronie master dowolnym wyjściem)

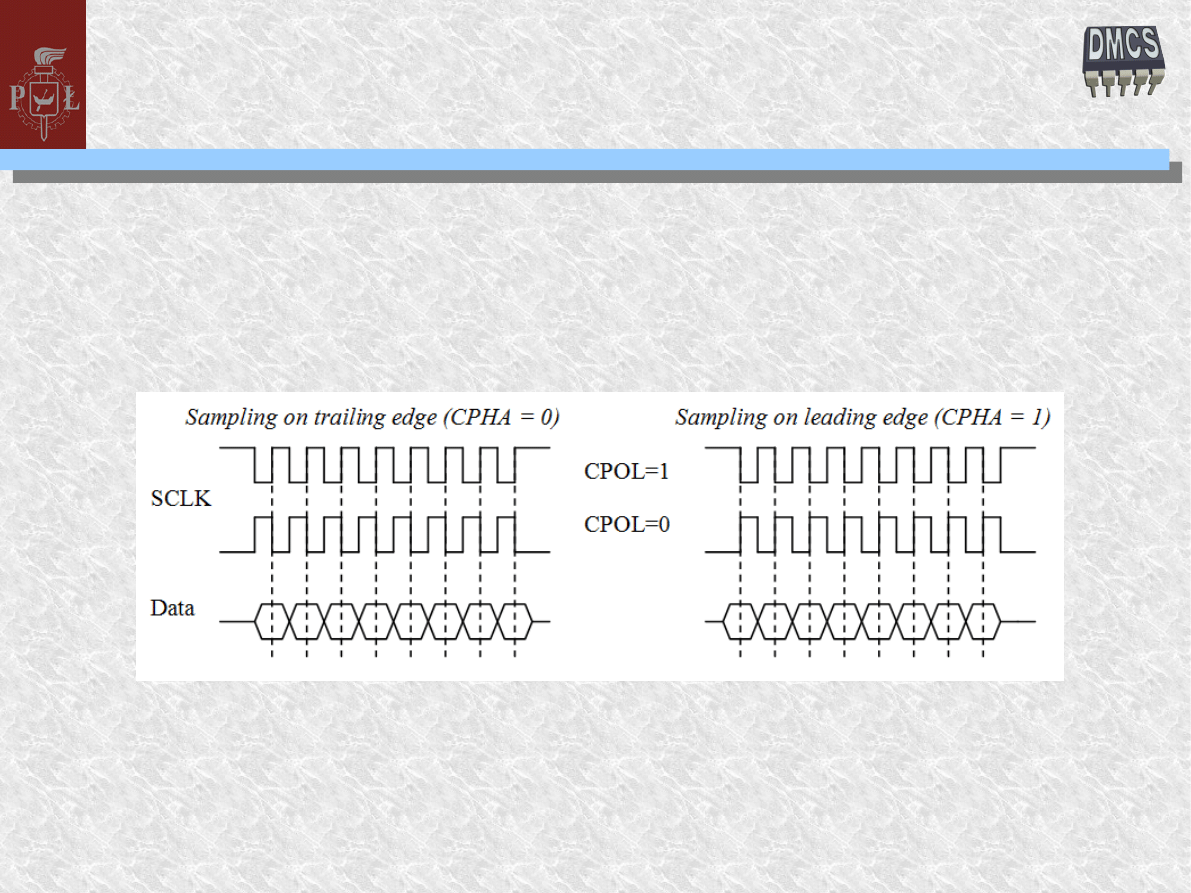

Interfejs SPI - przebiegi

13

CPHA (Clock Phase) – próbkowanie/zmiana stanu linii danych

na pierwszym lub drugim zboczu w cyklu zegara

CPOL (Clock Polarity) – stan linii SCK w stanie spoczynku

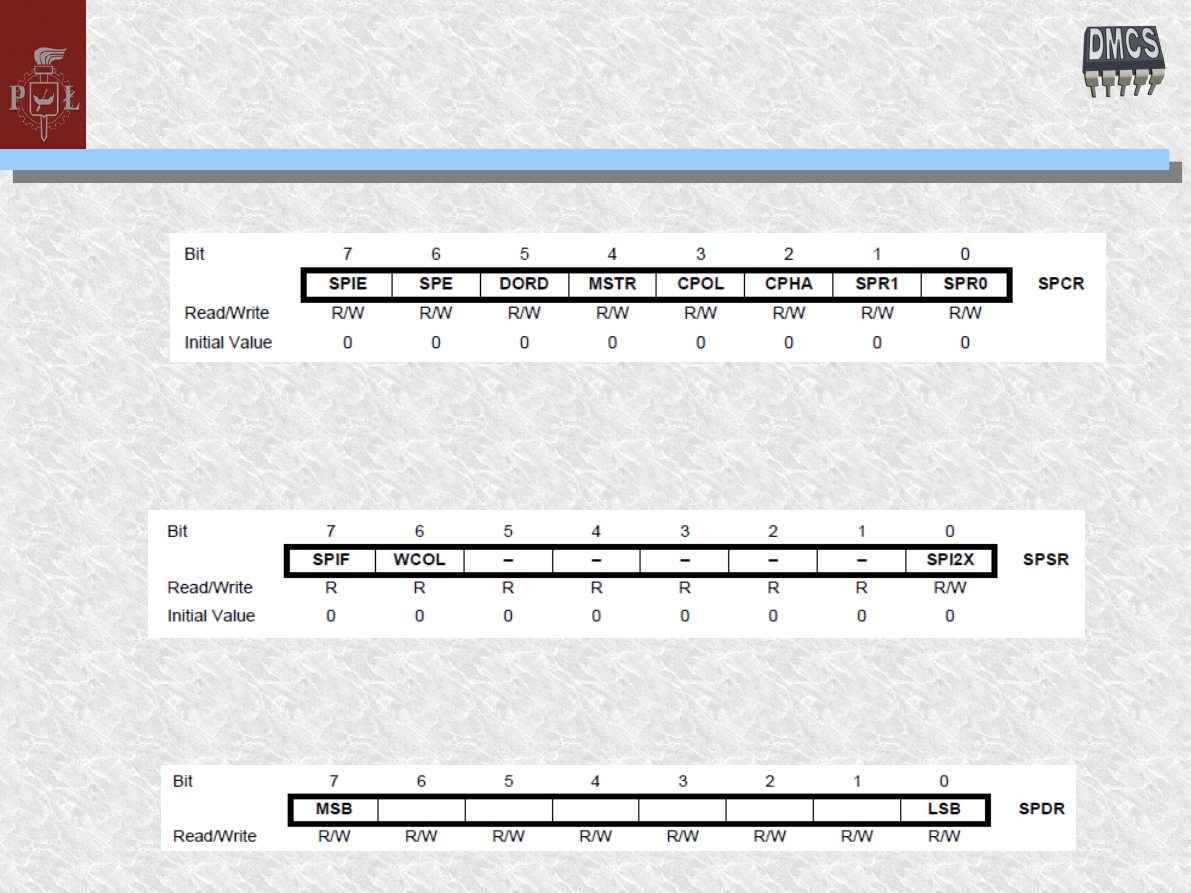

Interfejs SPI – rejestry

14

Rejestr kontrolny

SPIE – interrupt enable; SPE – SPI enable; DORD – data order; MSTR – master/slave;

CPOL – clock polarity; CPHA – clock phase; SPR1:0 – clock rate select (f

osc

/128 - f

osc

/2)

Rejestr statusowy

Rejestr danych

SPIF – interrupt flag; WCOL – write collision flag; SPI2X – double speed (maks. f

osc

/2)

Interfejs SPI – schemat transmisji

15

1. Inicjalizacja transmisji:

a) ustawienie rejestru SPCR

b) ustawienie rejestru SPSR (opcjonalne)

c) ustawienie bitu I w SREG (przy obsłudze przerwań)

d) zapis do rejestru SPDR (rozpoczęcie transmisji)

2. Procedura obsługi przerwania / lub oczekiwanie na flagę SPIF:

a) odczyt danej z rejestru SPDR (opcjonalne w przerwaniu)

b) wykonanie kolejnej transmisji (opcjonalne)

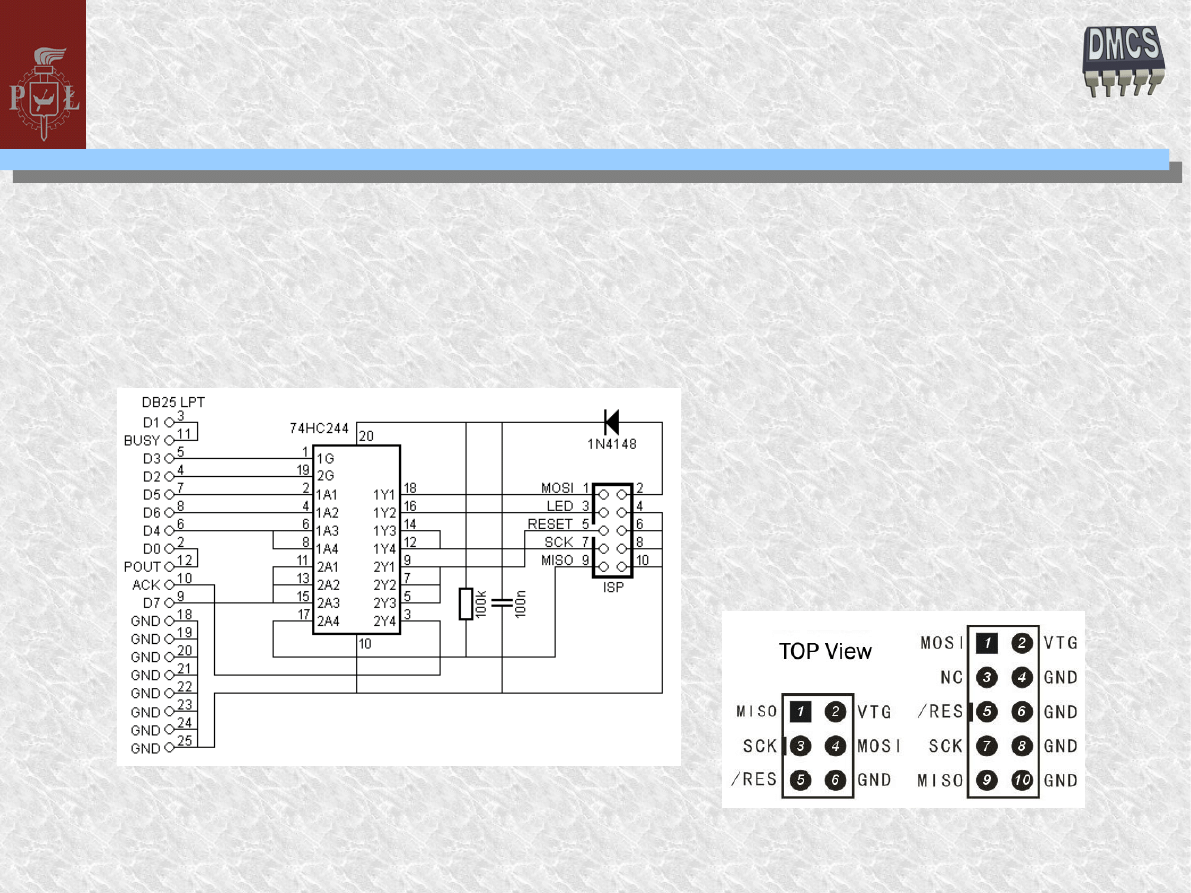

Interfejs SPI – programowanie ISP

16

Linie MOSI, MISO, SCK i RESET

(mogą być wykorzystywane w systemie nie tylko do programowania)

Gniazdo (header) dla programatora

Programator STK200

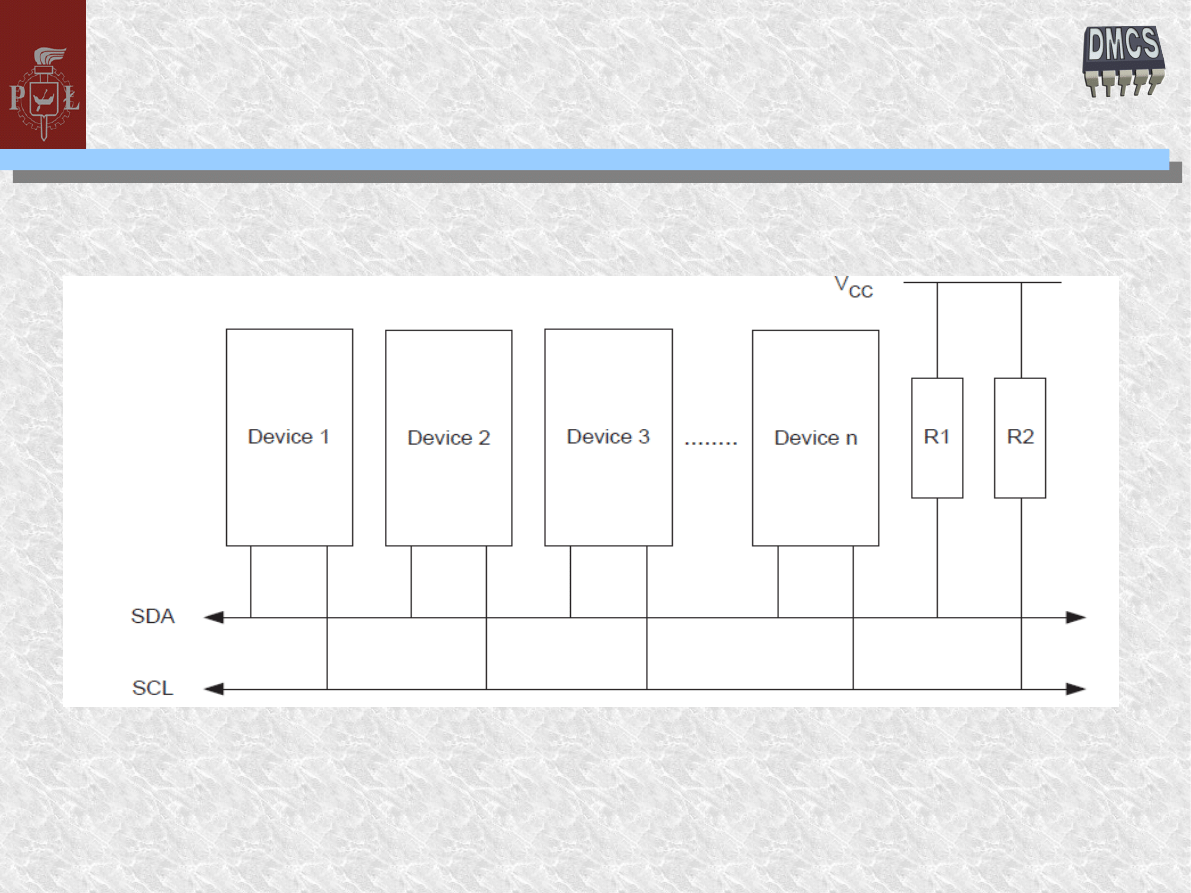

Interfejs Two-Wire (TWI)

17

Odpowiednik I

2

C (Inter-Integrated Circuit, Philips, lata 80-te)

Podobnie jak SPI komunikacja z peryferiami

Komunikacja szeregowa synchroniczna, half-duplex

Brak złożonej logiki przy wielu slave (adresowanie, mniejsza liczba linii)

Do 128 urządzeń

Mniejsza prędkość transmisji – maksymalnie 400 kbit/s

Linie:

SDA (Serial Data)

SCL (Serial Clock)

Interfejs Two-Wire (TWI) - magistrala

18

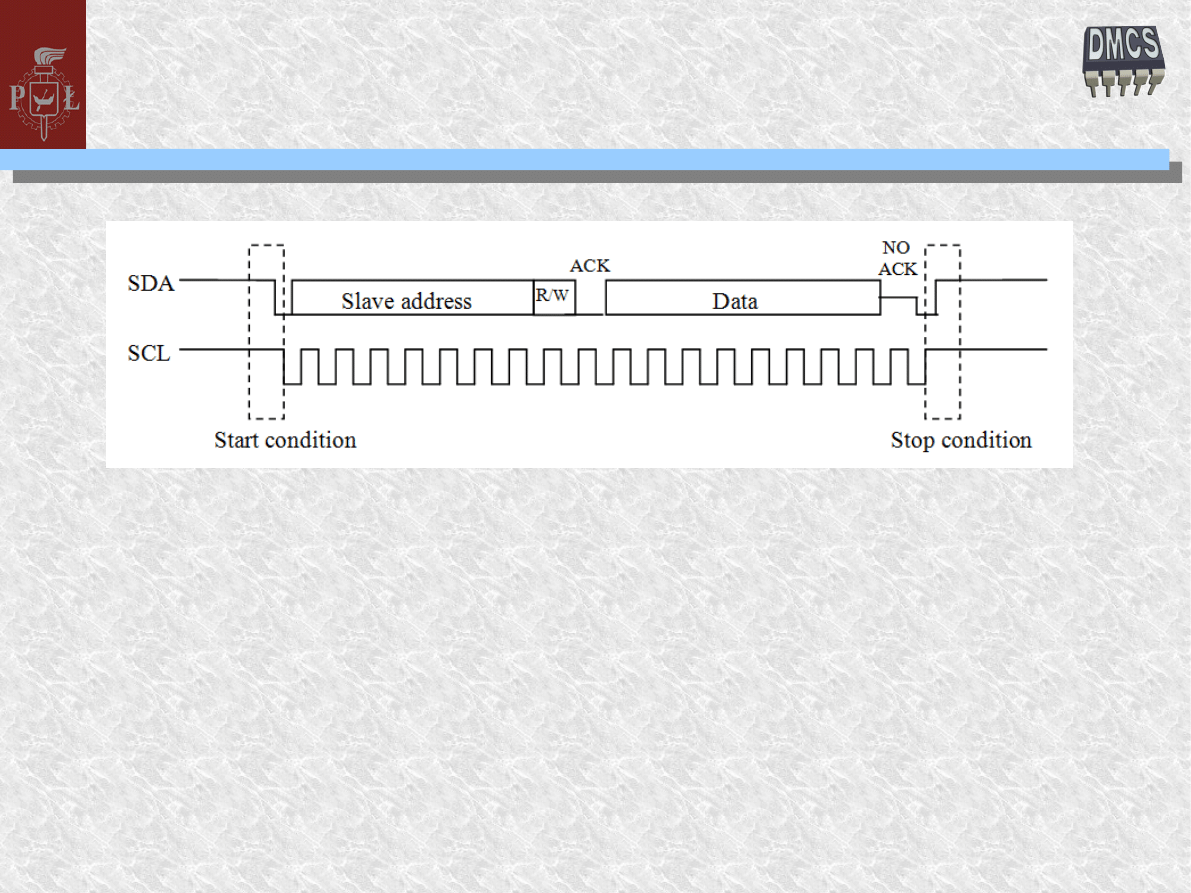

Interfejs Two-Wire (TWI) - ramka

19

Bit kontrolny R/W – kierunek transmisji (odczyt/zapis)

Bit potwierdzenia – stan niski na SDA wymuszany przez slave

Adres (7 bitów + 1 bit kontrolny R/W + 1 bit potwierdzenia)

Pakiet danych (8 bitów + 1 bit potwierdzenia)

Adres zerowy - adres rozgłoszeniowy (general call)

Możliwa transmisja kilku bajtów danych po transmisji adresu

i przed sygnalizacją końca transmisji

MSB

LSB

MSB

LSB

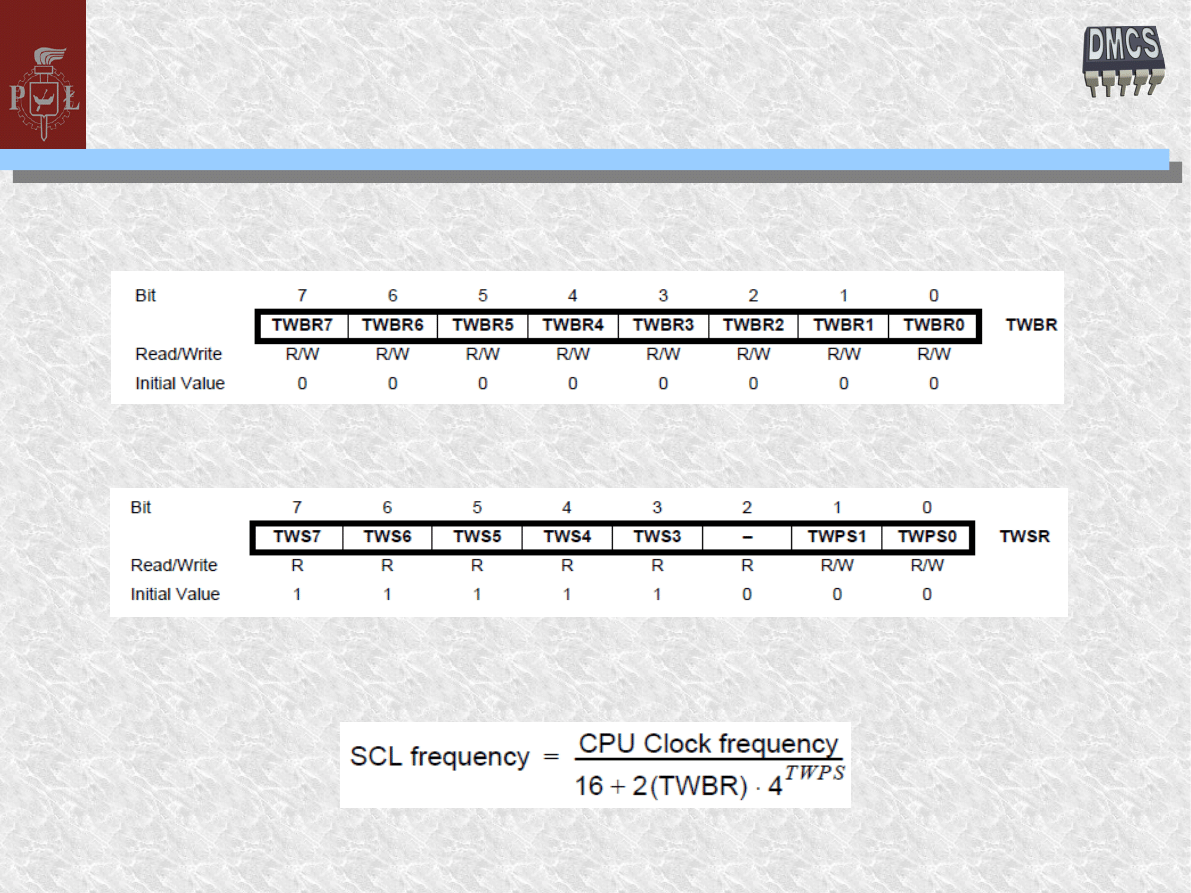

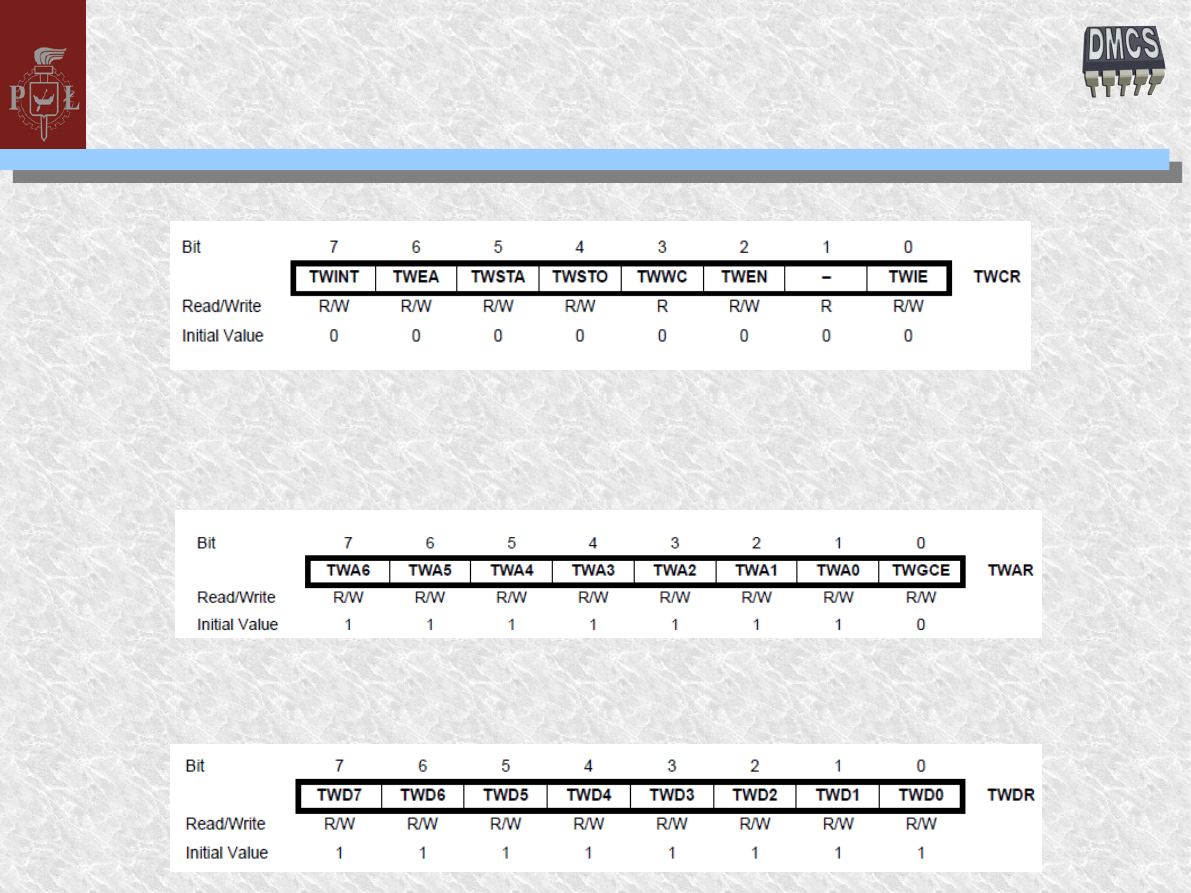

Interfejs Two-Wire – rejestry

20

Dzielnik częstotliwości sygnału zegarowego

Rejestr statusowy

TWS7:3 – status zależny od zdarzenia i trybu (master/slave)

Interfejs Two-Wire – rejestry

21

Rejestr adresowy

TWA6:0 – slave address, TWGCE – general call recognition enable

Rejestr kontrolny

Rejestr danych

TWINT – interrupt flag, TWEA – enable acknowledge bit, TWSTA – start condition,

TWSTO – stop condition, TWWC – write collision flag, TWEN – enable,

TWIE – interrupt enable

Interfejs Two Wire – schemat transmisji

22

1. Inicjalizacja transmisji:

a) ustawienie rejestru TWBR

b) ustawienie rejestru TWCR (z TWSTA=1 i TWINT = 1)

c) oczekiwanie na flagę TWINT

d) zapisanie wartości do wysłania do rejestru TWDR (adres slave)

e) ustawienie bitu I w SREG (przy obsłudze przerwań)

f) ustawienie rejestru TWCR (z TWINT = 1)

2. Procedura obsługi przerwania / lub oczekiwanie na flagę TWINT:

a) sprawdzenie rejestru TWSR (przy nadawaniu)

b) odczyt danej z rejestru TWDR (przy odbiorze)

c) wykonanie kolejnej transmisji (opcjonalne)

3. Zakończenie transmisji

a) ustawienie rejestru TWCR (z TWSTO=1 i TWINT = 1)

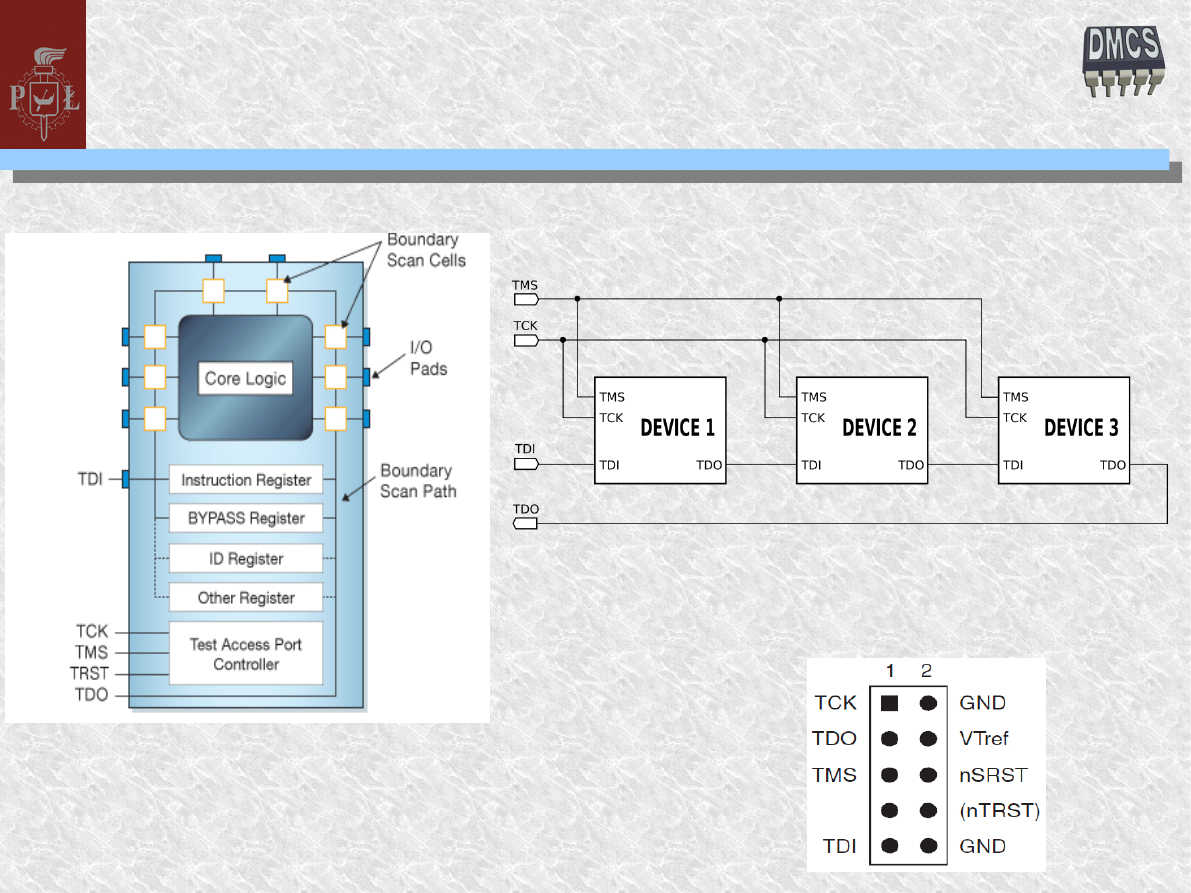

Interfejs JTAG

23

Joint Test Action Group

Protokół zgodny z IEEE 1149.1

Dostęp do zasobów wewnętrznych (rejestry, RAM, EEPROM, pamięć

programu, jednostka sterująca wykonaniem programu) i portów I/O

Używany do:

testowania połączeń na płytce drukowanej (boundary scan),

programowania pamięci flash, EEPROM i bitów konfiguracyjnych

(fuse/lock bits) w systemie (ISP),

uruchamiania i debugowania programów.

Interfejs JTAG

24

Gniazdo (header) dla JTAGa

(widok z góry)

Interfejs USB

25

Universal Serial Bus (1996 r.)

Port komunikacyjny - połączenie urządzeń z komputerem (hostem)

i zasilanie urządzeń (5V, 500mA w USB 1.0, 1.1, 2.0; 900 mA w USB 3.0)

Sieć o topologii drzewa, do 127 urządzeń

Komunikacja szeregowa, synchroniczna, kodowanie NRZI

Half-duplex (USB 1.0, 1.1, 2.0) lub full-duplex (USB 3.0)

Kontrola poprawności transmisji

Prędkość transmisji: 1,5 Mbps, 12 Mbps (USB 1.0, 1.1),

480 Mbps (USB 2.0), 5 Gbps (USB 3.0)

Linie (sygnalizacja różnicowa, dwie dodatkowe linie w USB 3.0):

+5V

D-

D+

GND

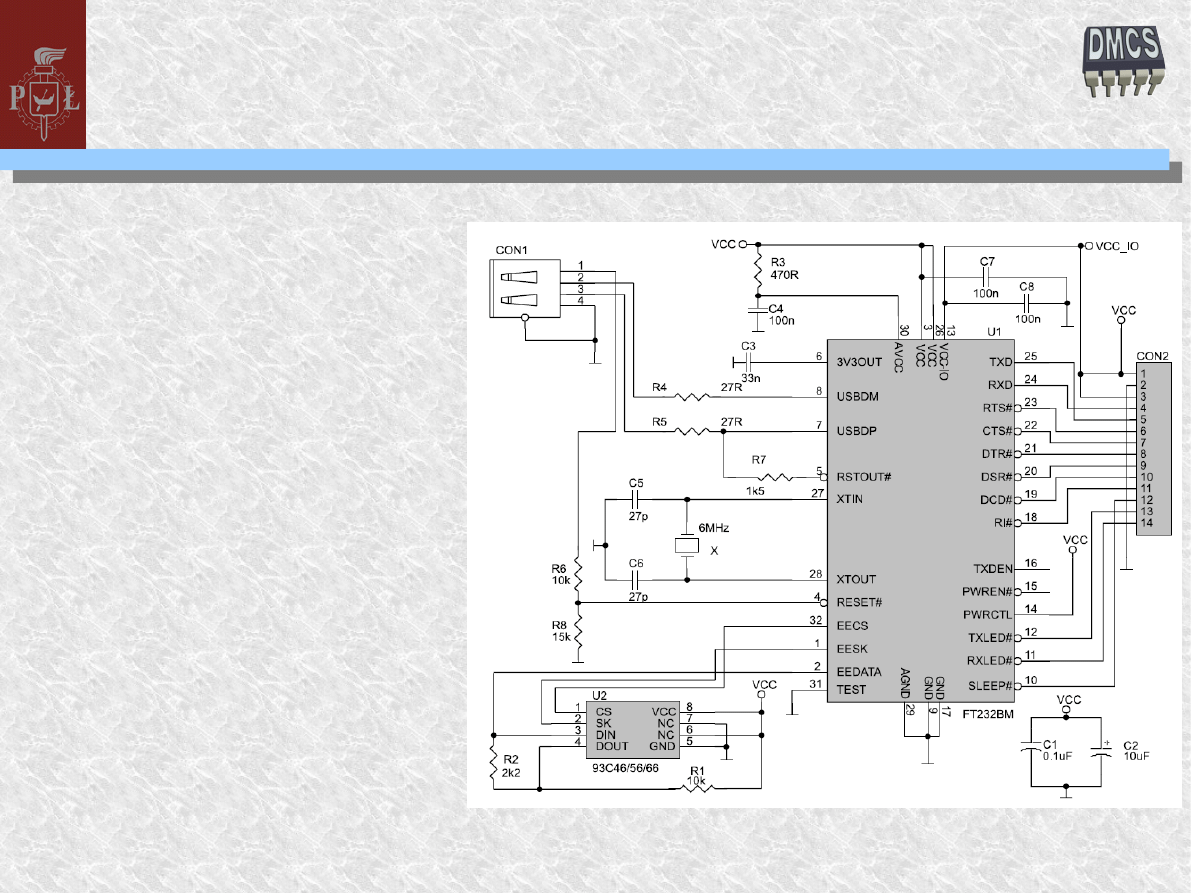

Interfejs USB

26

Brak w ATmega32

Rozwiązanie:

układ FTDI FT232 jako

konwerter USB ↔ UART

Gotowe sterowniki dla PC

(wirtualny port COM lub

bezpośredni dostęp przez DLL)

BTC ZL1USB

Dziękuję za uwagę.

Document Outline

- Slajd 1

- Slajd 2

- Slajd 3

- Slajd 4

- Slajd 5

- Slajd 6

- Slajd 7

- Slajd 8

- Slajd 9

- Slajd 10

- Slajd 11

- Slajd 12

- Slajd 13

- Slajd 14

- Slajd 15

- Slajd 16

- Slajd 17

- Slajd 18

- Slajd 19

- Slajd 20

- Slajd 21

- Slajd 22

- Slajd 23

- Slajd 24

- Slajd 25

- Slajd 26

- Slajd 27

Wyszukiwarka

Podobne podstrony:

BP SSEP wyklad6 id 92513 Nieznany (2)

BP SSEP wyklad1

BP SSEP wyklad11

BP SSEP wyklad2

BP SSEP wyklad5

BP SSEP wyklad7 id 92514 Nieznany

BP SSEP wyklad13

BP SSEP wyklad6 id 92513 Nieznany (2)

Zal-lab-BP-zaoczne, politechnika lubelska, budownictwo, 3 rok, semestr 5, fizyka budowli, wykład

Wykład 2 BP PLAN FINANSOWY, ZASADY SPORZĄDZANIA PROGNOZ FINANSOWYCH

Wykład 3 BP PLAN FINANSOWY – PROGNOZA PRZEPŁYWÓW PIENIĘŻNYCH

Wykład 5 BP PREZENTACJA PRZEDSIĘBIROSTWA I PLANOWANEGO PRZEDSIĘWZIĘCIA W BIZNESPLANIE

Wykład 1 BP PLANOWANIE W PRZEDSIĘBIORSTWIE, STRUKTURA I FUNKCJE BIZNESPLANU

tematyka wykładów bp czII regulacja, Studia, Budownictwo wodne I

Wykład 6 BP PLAN MARKETINGOWY

Wykład 8 BP OCENA OPŁACALNOŚCI PRZEDSIĘWZIĘCIA BIZNESOWEGO

Wykład 7 BP PLAN DZIAŁALNOŚCI OPERACYJNEJI PLAN ZASOBÓW LUDZKICH

Zal-lab-BP-zaoczne, politechnika lubelska, budownictwo, 3 rok, semestr 5, fizyka budowli, wykład

więcej podobnych podstron