Kamila Zybura

Robert Paliszkiewicz

Tomasz Kamioski

Łukasz Niedźwiecki

Ćw.6 „Elektronika cyfrowa”

1. Cel dwiczenia

Zad 1)

Wyznaczyd tablice prawdy dla bramek logicznych znajdujących się na makiecie (Rys 1)

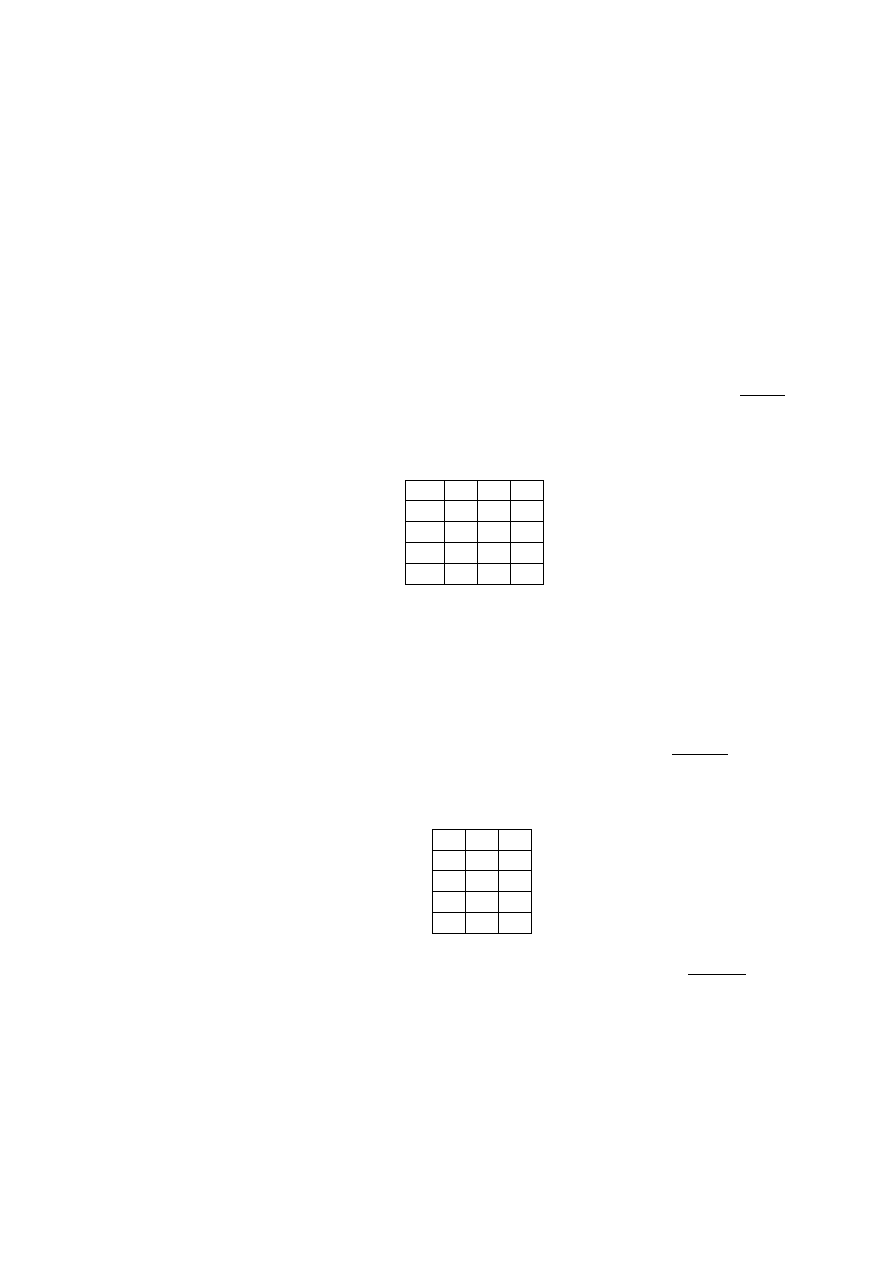

Zad 2)

Zbudowad układ pierwszego sumatora arytmetycznego, którego tablica prawdy

znajduje się poniżej

X1

X2 Y1 Y2

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

Zad 3)

Zbudowad komórkę pamięci statycznej w postaci przerzutnika

2. Przebieg dwiczenia

Zad 1)

a) Bramka NAND - 2 zmienne wejściowe (x1 i x2) i jedna na wyjściowa (y1) (Rys 1.a)

𝑥

1

∙ 𝑥

2

= 𝑦

1

X1 X2 Y1

0

0

1

0

1

1

1

0

1

1

1

0

b) Bramka NAND - 4 zmienne wejściowych (x1, x2, x3, x4) i 1 wyjściowa (y1) (Rys 1.b)

𝑥

1

∙ 𝑥

2

∙ 𝑥

3

∙ 𝑥

4

= 𝑦

1

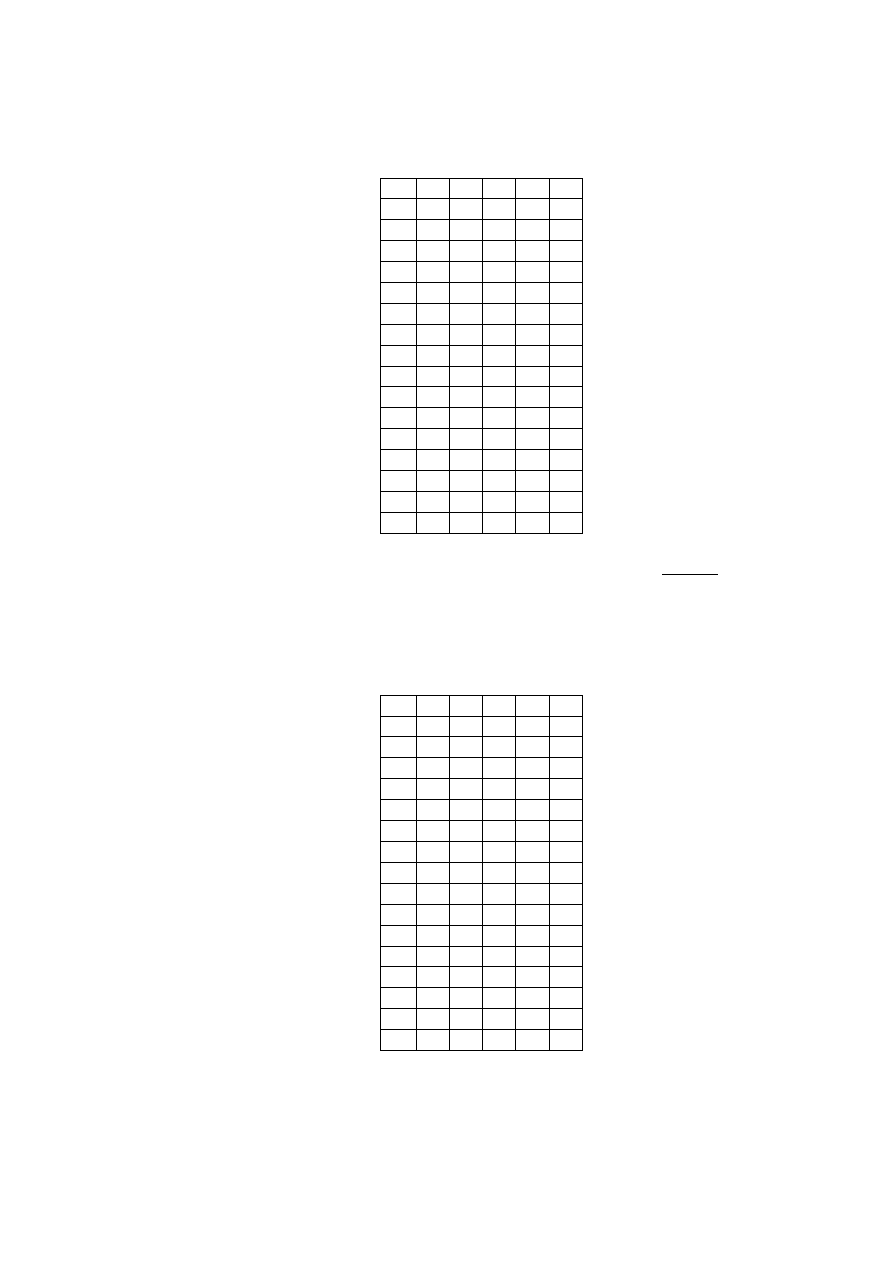

Lp. X1 X2 X3 X4 Y1

0

0

0

0

0

1

1

0

0

0

1

1

2

0

0

1

0

1

3

0

0

1

1

1

4

0

1

0

0

1

5

0

1

0

1

1

6

0

1

1

0

1

7

0

1

1

1

1

8

1

0

0

0

1

9

1

0

0

1

1

10 1

0

1

0

1

11 1

0

1

1

1

12 1

1

0

0

1

13 1

1

0

1

1

14 1

1

1

0

1

15 1

1

1

1

0

c) Bramka o 4 zmiennych wejściowych (x1, x2, x3, x4) i 1 wyjściowej (y1) (Rys 1.c)

𝑥

1

∙ 𝑥

2

+ 𝑥

3

∙ 𝑥

4

= 𝑦

1

Lp. X1 X2 X3 X4 Y1

0

0

0

0

0

1

1

0

0

0

1

1

2

0

0

1

0

1

3

0

0

1

1

0

4

0

1

0

0

1

5

0

1

0

1

1

6

0

1

1

0

1

7

0

1

1

1

0

8

1

0

0

0

1

9

1

0

0

1

1

10 1

0

1

0

1

11 1

0

1

1

0

12 1

1

0

0

0

13 1

1

0

1

1

14 1

1

1

0

0

15 1

1

1

1

0

Zad 2)

Wykorzystując dostępne na makiecie bramki logiczne (Rys 1 a, b i c)

zbudowaliśmy pierwszy sumator arytmetyczny, o tablicy prawdy:

X1

X2 Y1 Y2

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

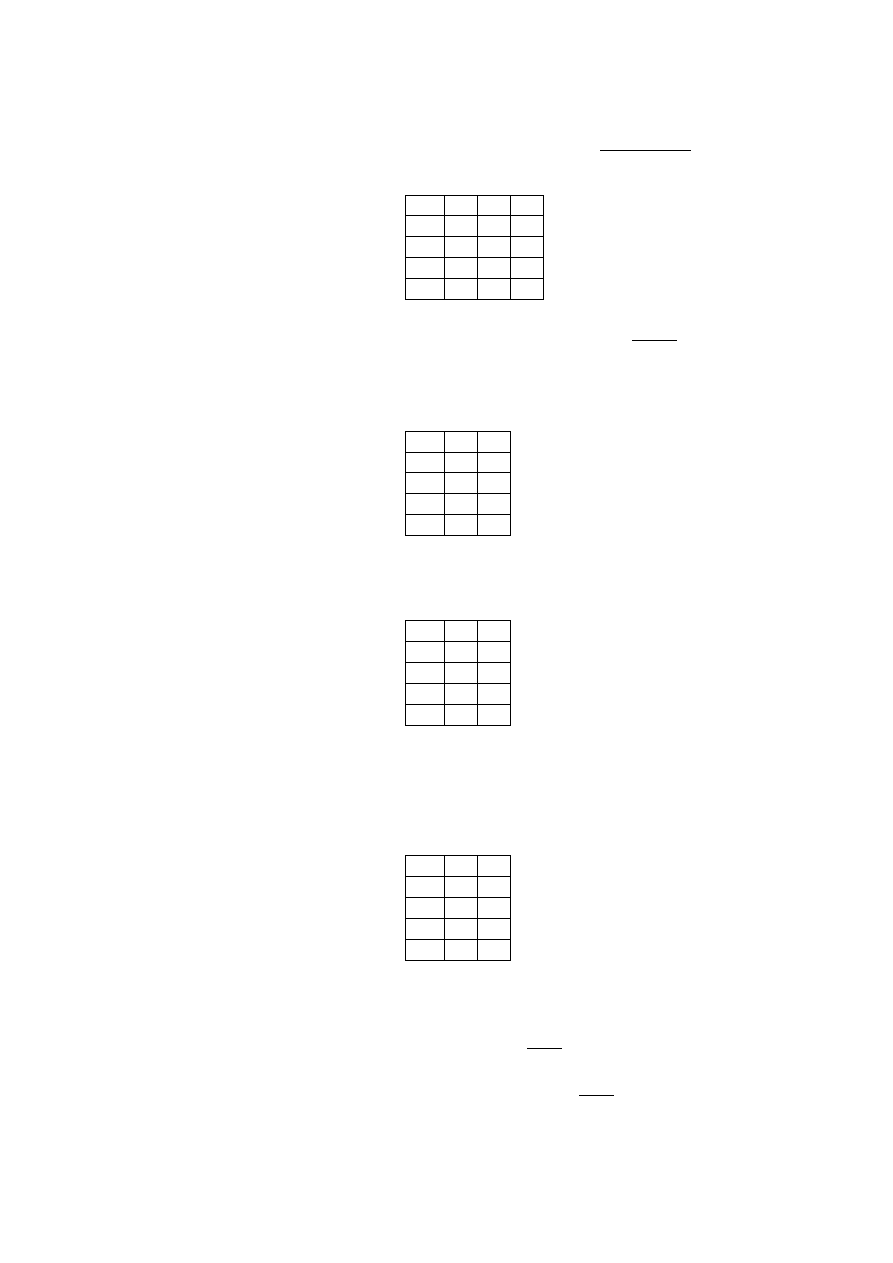

Tablica zmiennej wyjściowej y1 jest tożsama z tablicą bramki AND (Rys 2) i w układzie

zmienna wyjściowa y1 jest realizowana przez tę bramkę.

Tablica prawdy bramki AND:

X1

X2 Y1

0

0

0

0

1

0

1

0

0

1

1

1

Tablica zmiennej wyjściowej y2 jest podobna do tablicy jednej z przykładowych funkcji z

instrukcji do dwiczenia:

X1

X2 Y

0

0

1

0

1

0

1

0

0

1

1

1

Funkcja ta opisana jest wzorem:

𝑦 = 𝑥

1

+ 𝑥

2

∙ 𝑥

1

+ 𝑥

2

Z tablicy zmiennej wyjściowej y2 wynika, że jest ona negacją przykładowej funkcji:

X1

X2 Y1

0

0

0

0

1

1

1

0

1

1

1

0

𝑦

2

= 𝑥

1

+ 𝑥

2

∙ 𝑥

1

+ 𝑥

2

Układ realizujący tę funkcję jest przedstawiony na Rys 3.

Cały układ – Sumator arytmetyczny jest przedstawiony na Rys 4.

Uwagi:

Na makiecie nie było bramki NOT. Zrealizowaliśmy ją poprzez zwarcie dwóch zmiennych

wejściowych w bramce NAND (Rys 5).

Zad 3)

Zbudowaliśmy komórkę pamięci statycznej w postaci przerzutnika RS (Rys 6).

Przerzutnik RS (R-reset, S-set) jest układem sekwencyjnym. W układzie takim wartośd

zmiennych wyjściowych zależy, nie tylko od aktualnych zmiennych wejściowych, ale

również od ich poprzedniego stanu.

Wyszukiwarka

Podobne podstrony:

El sprawko 5 id 157337 Nieznany

plastiki sprawko id 362078 Nieznany

przetwarzanie sprawko 3 id 4066 Nieznany

automatyka sprawko 2 id 73363 Nieznany

elektra chyba 5 11 id 157768 Nieznany

elektro wyklad 03b id 157928 Nieznany

elektro wyklad 08 id 157932 Nieznany

3 Sprawko id 34095 Nieznany

elektronika teoria liczb id 158 Nieznany

DC impulsowo sprawko id 132337 Nieznany

Metrologia Sprawko id 297285 Nieznany

IG, sprawko 4 5 id 209607 Nieznany

elektro wyklad 04 id 157929 Nieznany

Elektryk budowlany 741104 id 15 Nieznany

Elektra sem 1 5z5 id 157804 Nieznany

elektromagnetyzm 76 87 id 15810 Nieznany

F II Elektr wyklad 09 id 16722 Nieznany

jeszcze raz sprawko5 (1) id 227 Nieznany

więcej podobnych podstron