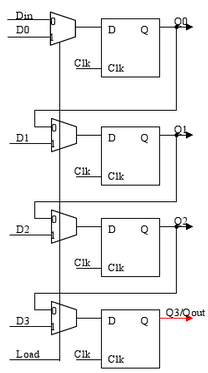

1.Narysuj 4-bitowy asynchroniczny licznik zliczający w tył. Jakie są konsekwencje stosowania licznika asynchronicznego?

Trzeba dorysować jeszcze w analogiczny sposób Q3

W liczniku asynchronicznym przerzutniki są sterowane wyjściami przerzutników poprzedzających. Powoduje to, iż stan licznika nie ustala się od razu, lecz kolejno na poszczególnych przerzutnikach z opóźnieniem równym czasowi propagacji sygnału w przerzutniku. Jeśli impulsy zegarowe mają dużą częstotliwość i ich okres jest porównywalny z czasem propagacji przerzutnika, to sygnały wyjściowe licznika mogą podawać złe wartości zliczonych impulsów - sygnał wyjściowy nie ma czasu na odpowiednie ustalenie się

2.Narysuj schemat układu dodającego dwie liczby 2-bitowe

3. Wymień i przedstaw problemy dynamiczne przerzutników.

a) wyścigi logiczne:

Właściwie w każdej sytuacji, gdy bramki są odblokowane sygnałami przychodzącymi z przerzutników (lub innych układów taktowanych zegarem), trzeba się upewnić, że żadna z nich nie zostaje odblokowana i ponownie zablokowana po opóźnieniu odpowiadającym czasowej propagacji sygnału przez przerzutnik. Podobnie trzeba się upewnić, że sygnały na wejściach przerzutników nie są opóźnione w stosunku do impulsów taktujących.

B) Problem nachylenia zboczy pojawia się, gdy wspólny sygnał o długim czasie narastania taktuje kilka połączonych urządzeń. Przykładem mogą być dwa rejestry przesuwające taktowane tym samym sygnałem zegarowym o zboczach impulsów spowolnionych w skutek istnienia pojemności obciążającej wyjście układu CMOS o stosunkowo dużej impedancji (500Ω dla napięcia zasilania +5V). Problem polega na tym, że próg przełączenia drugiego rejestru, może być wyższy niż próg przełączania pierwszego rejestru, co będzie powodować wcześniejsze przesuwanie danych umieszczonych w pierwszym rejestrze, wskutek czego można stracić informację znajdującą się na ostatniej pozycji pierwszego rejestru.

c)stany metastabilne- istnieje prawdopodobieństwo, że napięcie wejściowe będzie się zmieniać w najbardziej niekorzystnym przedziale czasu, gdy stan wejściowy oddziałuje na stan przerzutnika. Wtedy przerzutnik nie jest w stanie powziąć żadnej decyzji i poziom napięcia na jego wyjściu może trwać w zawieszeniu w okolicy progu przełączenia nawet przez kilka mikrosekund (podczas gdy normalny czas propagacji wynosi dla układu HCT i LS-TTL ok. 20 ns), lub przerzutnik może ustalić jakiś stan na wyjściu, lecz po chwili samoistnie może zmienić ten stan na przeciwny.

4. Narysuj schemat bramki typu OC. Jak można łączyć bramki typu OC?

5. Zaprojektuj przerzutnik RS wykorzystując przerzutnik D

6. Wyprowadź wzór na czas narastania układu całkującego RC.

7.PISO

8. EEPROM

9. Opisz zależność pomiędzy rozdzielczością bitową przetwornika AC a stosunkiem sygnału do szumu

10.podwójne całkowanie

Wyszukiwarka

Podobne podstrony:

Mechanika grA zadania

Wybaczanie Rodzicom, SATORI GRA, Wybaczanie

Tusk gra Polska, Film, dokument, publcystyka, Dokumenty dotyczące spraw bieżących

Gra uproszczona z zastosowaniem nauczonych i doskonalonych umiejętności, AWF Wro, koszykówka

gra Rozkaz specjalny, Prywatne, Przedszkole, Powstanie Warszawskie

plikus[1].pl Super gra online

fiz odp na pyt grA i B, Politechnika Poznańska, ZiIP, Semestr I, Fizyka

II gra nocna

GRA POLITYCZNA

KOLOS grA

Gra komputerowa

gra bramkarza przy wrzutkach

Prom gra

Edukacja zdrowotna w nowej podstawie programowej Gra yna Skirmuntt

Gra terenowa Terenowy Wierszokleta id 194338

całki grA

Ryzykowna gra Joanny

więcej podobnych podstron