Wykład mikroprocesory 30.03.2008r.

Rodzina procesorów 680x0.

Rys.1

Rozwiązania z rodziny 6800 stały się w wielu obszarach up niejako standardami.

Mimo zakończenia linii rozwojowej, jednostka centralna przeszła do rodziny kontrolerów jedno

układowych MCF oraz występuje w 8 bitowych kontrolerach jako opcja jednostki centralnej. Od

samego początku przyjęto architekturę wewnętrzną 32 bitowa. Na KO przeznaczono 2 bajty, nie

wystąpił więc problem braków wolnych kodów. Na poziomie nadzorcy pojawiały się kolejne

rejestry (w ilości niezbędnej do obsługi pamięci podręcznej i układu zarządzania pamięcią).

uP 68k są przystosowane do pracy w systemach NN poza tym konsekwentnie stosują wyrównanie

binarne. Wyrównanie binarne to kontakt z argumentami w ten sposób ze adres jest podzielny przez

rozmiar.

68000

68010

AB

24b

68020

68030

68040

68060

32b

A/D

Ukł.

Zarządzani

a

pamięcią,

pamięć

podręczna

Identyczny

model

rejes tru(32b),

poziom

użytkownika

Wnętrze

RIS C

Zew nętrz

ny CP

Jądro uC

68HC 08

(wymienne)

R odzina MC F

C oldfire

68008 (8bit D B)

20bit AB

680X

Rys.2

Rys. 3

Przy braku wyrównania, może dojść do niepotrzebnych cykli magistrali, ponieważ nie da się

równocześnie wystawić dwóch różnych adresów. Linia A1, A0 nie występuje ponieważ transfer

może być 4 bajtowy. Zamiast tego pojawiają się sygnały informujące o konfiguracji aktywnych

bajtów w 32 bitowym słowie. Rozkazy uP 68k maja rozmiar 2,4,6 itd. bajtów, a więc próba

wprowadzania do PC adresu nieparzystego jest z góry skazana na niepowodzenie- uP zgłasza wtedy

stan wyjątkowy błędu adresowania. Większość rozwiązań (artykuł i sprzęt została omówiona w

postaci ogólnej wcześniej). Skoncentrujemy się tylko na rozwiązaniach specyficznych.

O C

O C

O C

148

2

1

0

enkoder priorytet.

Praca z magistralą.

DP jest dwu bajtowe a więc znika A0. Zamiast tego mamy stroby UDS/LDS informujące o

wykorzystaniu dwu bajtowej DB. Atrybutami transferu są Linia R=nieW, Linie FC0 do FC2,

(określają rodzaj przestrzeni adresowej).

Mamy 4 takie przestrzenie:

1) SP – program nadzorcy

2) SD - Dane nadzorcy

3) UP - Program użytkownika

4) UD – Dane użytkownika.

Oprócz tego dla FC=111 występuje tzw. cykl wewnętrzny – dla pierwszych uP rodziny był

to wyłącznie CAP (cykl akceptacji przerwania). Ważność adresów i atrybutów potwierdza niski stan

linii nieAS. Generalnie stan linii R/nieQ jest identyczny w czasie całego CM.

Mamy jednak CM typu: odczyt, modyfikacja, zapis odnoszące się do tej samej lokacji adresowej. W

cyklach RMW linia R/nieW zmienia się zaś akceptacja transferu występuje dwukrotnie dla odczytu

i zapisu. uP rodziny az do 68030 normalnie korzystają z magistrali. Odebranie magistrali to sygnał

DR do uP. uP natychmiast potwierdza gotowość zwrotna sygnałem BG.

Arbiter może przekazać magistralę innemu uP jeśli oprócz BG zajdą następujące warunki:

a) nieAS=1 (cykl zakończony)

b) nieDTACK=1 karty przestały potwierdzać transfer.

Jeśli to jest spełnione to do uP podawany jest sygnał BGACK który równocześnie odcina bufory

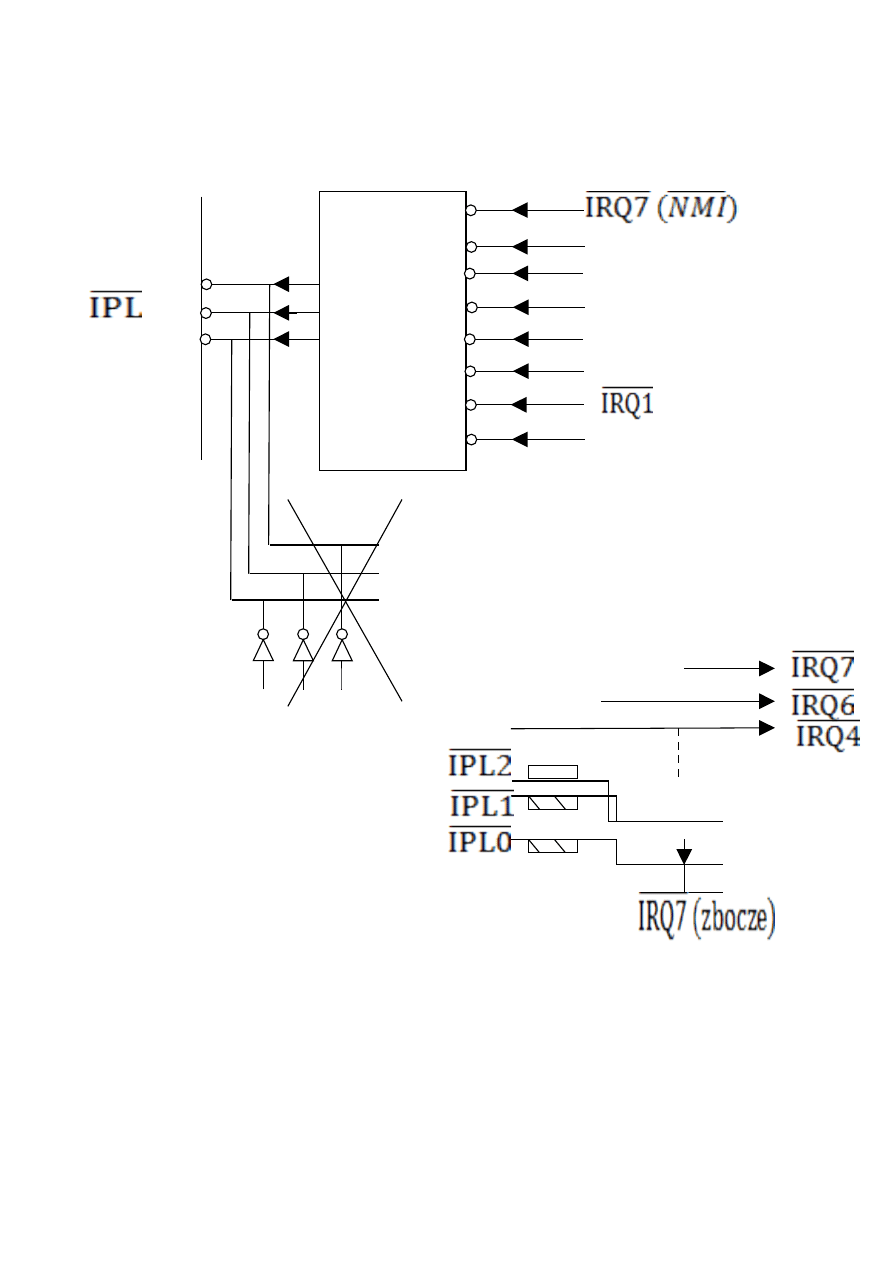

pomiędzy uP a magistralą. Zamiast zgłoszeń nieIRQ1 do nieIRQ7 mamy linie IPL0 do 2 przy

pomocy których informujemy uP jaki poziom żądania jest aktualnie zgłoszony ( najwyższy

priorytet). Musimy stosować enkoder priorytetowy.

Linie magistralne IQ są typu OC co umożliwia podpięcie większej ilości zgłoszeń do jednej

linii. Enkoderem priorytetu nie możemy wyeliminować i np. pojedynczej linii IPL wyprowadzić

na magistrale bo dochodziło by do podbijania poziomu żądania.

Rys.3

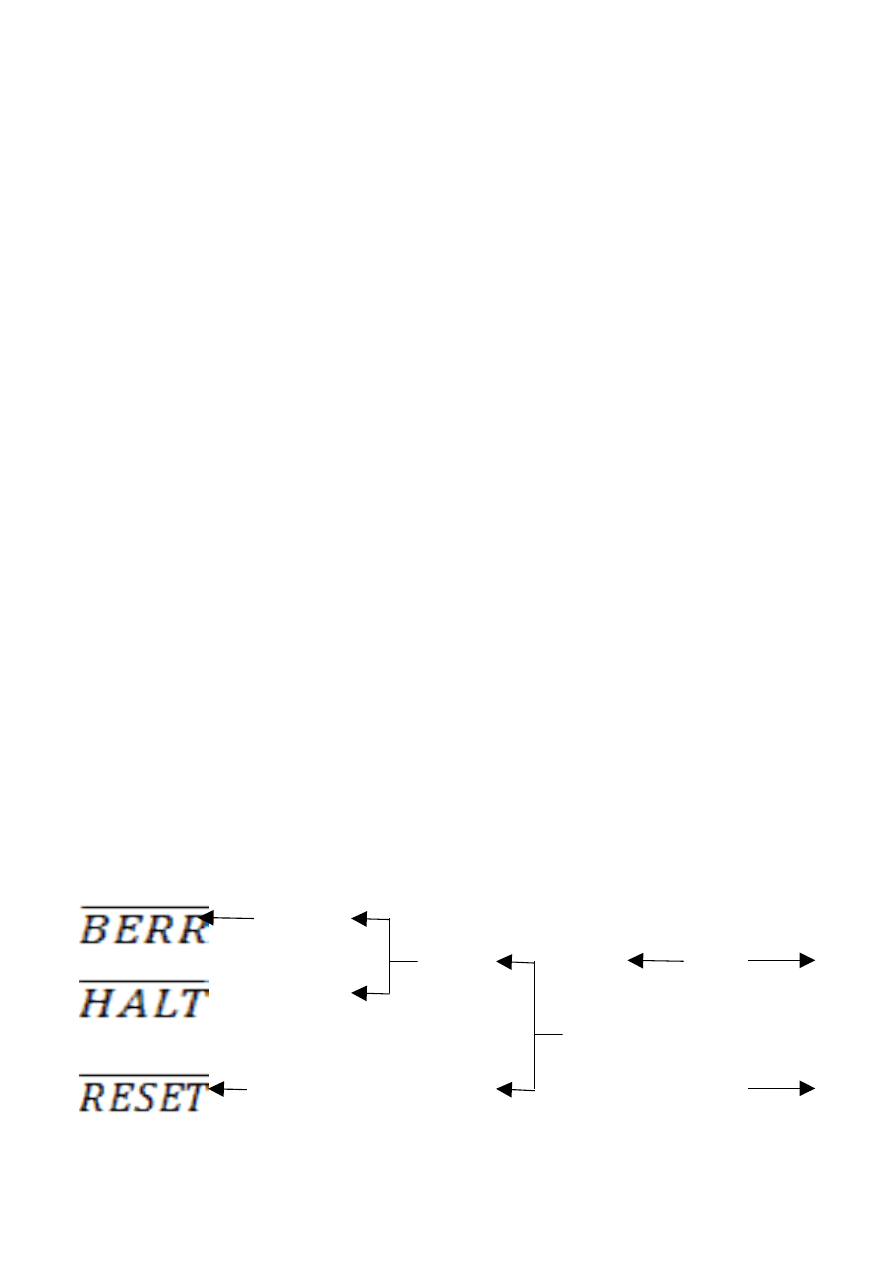

Wykorzystanie linii sterujących jest następujące:

Rys. 4

błąd

magis trali

zerowanie

na ciepło

powtórze.

cyklu

zerow. na

zimno

praca

krokowa

co cykl

info. o

blokadzie

uP

rozkaz res et

$27 0 0 1 0 0 1 1 1

T - S - -

Zwróćmy uwagę ze uP może także wyzerować caly system oprócz siebie (wykonanie

rozkazu RESET). Zwykle ma to miejsce po stwierdzeniu dziwnego zachowania kart – zerowanie +

ponowna konfiguracja zwykle rozwiązuje problem. Jak wiemy na karcie znajduje się logika

przeterminowania dlatego tez krokowanie przy pomocy linii DTACK sprowokowało by błąd

magistrali z tych względów używamy rozkazu HALT do pracy krokowej co CM zatrzymaniem uP

po kolejnym cyklu. Jeżeli uP stwierdzi ze dalsze działanie jest niemożliwe to blokuje się i wystawia

aktywny poziom na linii HALT na zewnątrz.

Grupa sygnałów E, nieVMA i VPA umożliwia współpracę uP z układami peryferyjnymi starszej

rodziny 6800 gdzie był stosowany cykl synchroniczny.

Struktura ta lokowana jest od początku przestrzeni w obszarze danych nadzorcy. Po

wyzerowaniu uP odczytuje z dwóch pierwszych lokacji stale początkowe dla wskaźnika stosu

nadzorcy IPC. Dopiero teraz można obsłużyć przerwanie typu NMI. Po wyzerowaniu maska

przerwań ustawiana jest na najwyższy poziom (111), uP startuje z poziomu nadzorcy S=1, zaś

śledzenie programowe jest wyłączone (T=0). Śledzenie programowe to wykonanie procedury po

zakończeniu kolejnej instrukcji. Procedura taka zwykle prezentuje na ekranie stan rejestrów, stosu,

umożliwia dostęp do danych i postaci źródłowych kodu. Stan bajtu SB w związku z tym wynosi po

wyzerowaniu $27. Struktura ta jest obsadzana pamięcią typu RAM.

Pierwsze 64 adresy dotyczą stanów wyjątkowych wewnętrznych, pozostałe zaś może

wykorzystywać użytkownik przy przerwaniu. Dwa pierwsze adresy nie możemy oczywiście czytać

z pamięci RAM ustawionej przypadkowo. W tej sytuacji uP wyjątkowo wystawia linię FC na

dostęp do obszaru programu nadzorcy – musi tam być pamięć stała.

Obsługa każdego wyjątku dokonywana jest na poziomie nadzorcy. Wśród stanów

wyjątkowych wewnętrznych mamy dwa najpoważniejsze. Są to:

a) błąd magistrali

b) błąd adresacji.

Błędy te nie mogą wystąpić równocześnie. Załóżmy ze uP zapisuje dane do lokacji:

a) obsadzonej nieparzystej

b) nieobsadzonej parzystej

c)nieparzystej nieobsadzonej

Przy adresie nieparzystym do CM nie dochodzi a więc nie może wystąpić błąd magistrali tylko błąd

adresacji.

UP blokuje się w sytuacji wystąpienia tzw. podwójnego błędu. Ma to miejsce jeśli podczas

wchodzenia w obsługę błędu adresu lub magistrali pojawi się błąd z tej samej grupy.

Proces wchodzenia w obsługę to:

a) zapis stosu

b) odczyt stanu

A więc przy zapisie stosu może pojawić się błąd magistrali( uszkodzenie sprzętu).

Podobna sytuacja może mieć miejsce przy kontakcie z obszarem TAP. Oprócz tego adres odczytany

z TAP może być nieparzysty. W każdym z tych przypadków pojawia się ponownie błąd z tzw. grupy

zerowej (adresu/magistrali) i uP blokuje się. Blokada może nastąpić przy błędzie pojedynczym

adresu bądź magistrali w sytuacjach szczególnych:

a) błąd magistrali przy początkowym ładowaniu stanu rejestrów SSP/PC

b) początkowy PC załadowany po resecie jest nieparzysty

c) doszło do użycia stosu nadzorcy, a zawartość SSP jest nieparzysta.

Wyszukiwarka

Podobne podstrony:

Z Wykład 30.03.2008, Zajęcia, II semestr 2008, Teoria informacji i kodowania

Systemy bankowe wyklad z 30[1].03.2008 (poprawione), pliki zamawiane, edukacja

prawo konstytucyjne cwiczenia 30 03 2008

Historia PRL (7) 30-03-2009, Historia PRL Wykł

KOMPLEKSY POLAKOW wykl 29 03 2012

ZiIP%20Fiz1%20pytania%20z%20I%20sprawdzianu%2030%20kwietnia%202008

27 letni żołnierz USA skazany za zamordowanie więźniów (30 03 2009)

cwiczenia 14 28.03.2008, cwiczenia - dr skladowski

03 2008 CHLEB WILENSKI

kurs wprow.cz.prakt.2008, Znieczulenie, Wykłady-Wprowadz. do spcjalizacji w anestezjologii i int.ter

Z Wykład 15.03.2008, Zajęcia, II semestr 2008, Analiza matematyczna

Z Ćwiczenia 29.03.2008, Zajęcia, II semestr 2008, Wstęp do kryptologii

wyklad 15 5.03.2008, wyklady - dr krawczyk

ASTRO 4 03 2008 r

30 03 Pytania testowe

Z Ćwiczenia 15.03.2008, Zajęcia, II semestr 2008, Analiza matematyczna

EIE Wyk ad V1 03 2008

więcej podobnych podstron