Realizacja dostępu do pamięci

DRAM

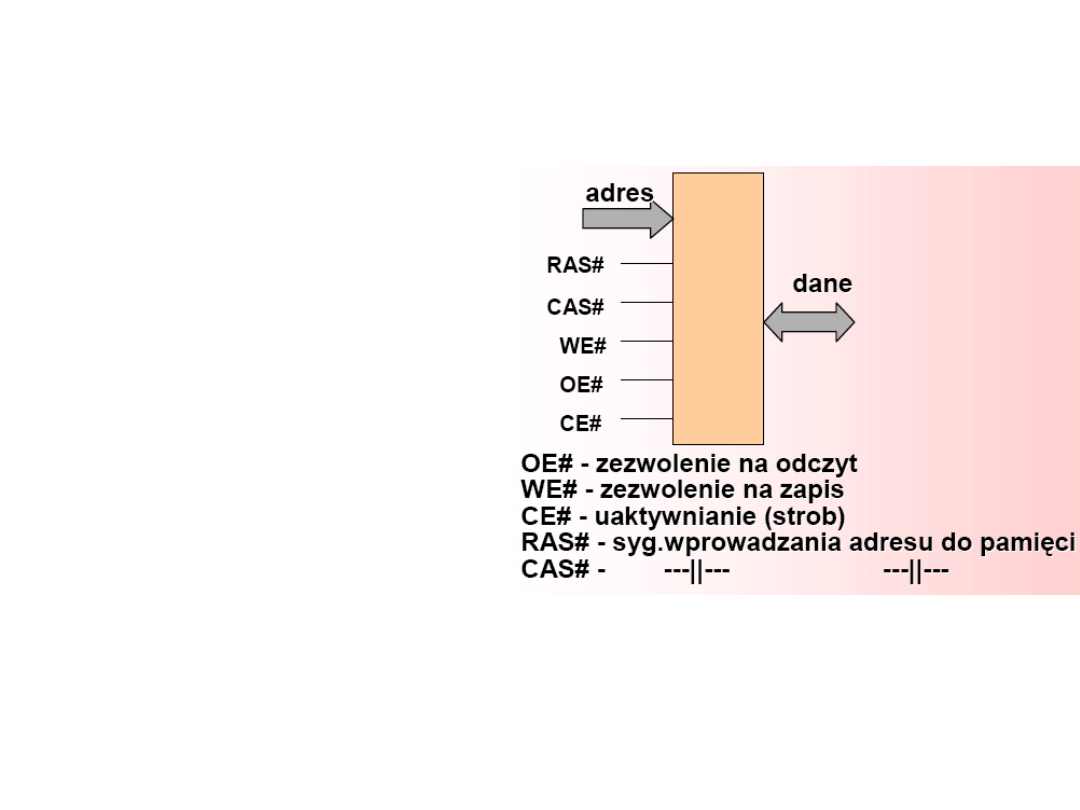

Pamięć dynamiczna RAM

(DRAM)

Pamięci te są pamięciami

pozwalającymi uzyskiwać

duże pojemności w

pojedynczym układzie

scalonym. Zasada działania

tych pamięci opiera się na

magazynowaniu ładunku

na określonej niewielkiej

pojemności. Pojemność

nienaładowana oznacza 0

logiczne, a naładowana

oznacza zapisaną 1

logiczną. Sposób

przechowywania tych

stanów wymaga

stosowania cykli

odświeżania.

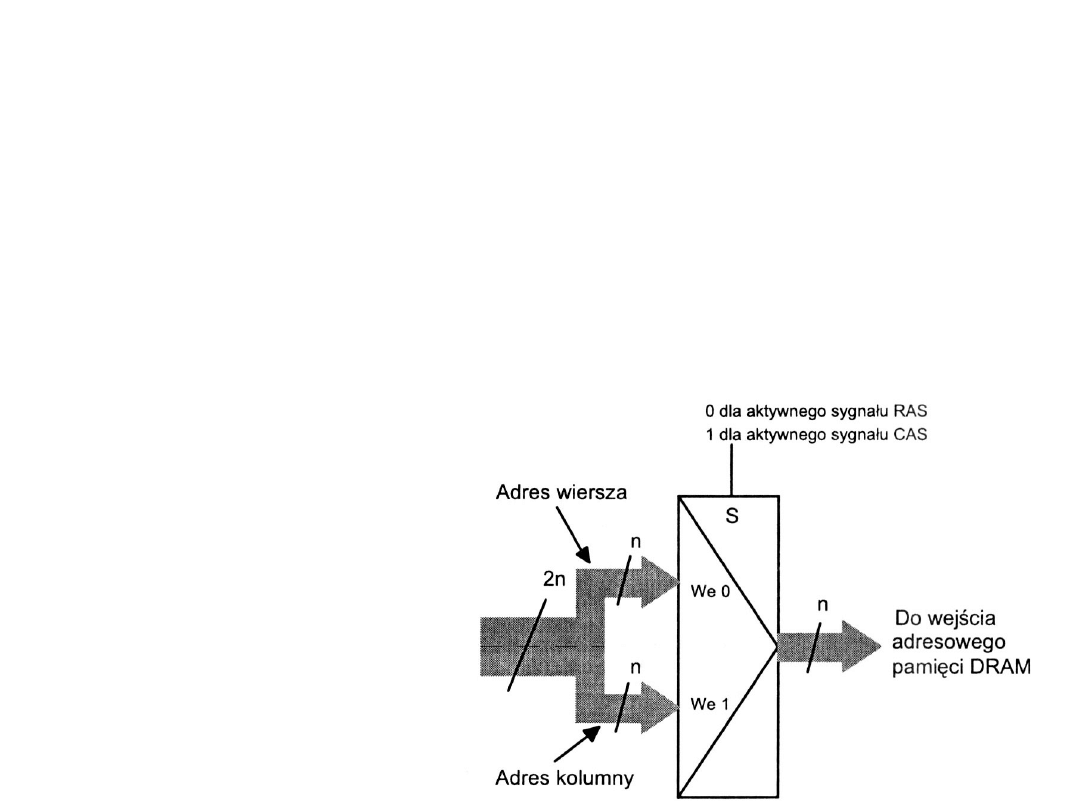

Adres słowa, na którym chcemy wykonać operację,

podawany jest w dwóch równych częściach zwanych

adresem wiersza i adresem kolumny. Zmniejsza

to ilość potrzebnych wyprowadzeń szyny adresowej i

upraszcza konstrukcję dekoderów adresu. Zatem

układy logiczne sterujące pracą pamięci muszą

dokonać konwersji adresu, podawanego przez

procesor lub innego zarządcę magistral, na postać

wymaganą przez pamięć DRAM.

Przykładowy układ

dokonujący takiej

konwersji pokazany jest

na rysunku. Sygnał

podany na wejście S

multipleksera wybiera,

czy starsza, czy też

młodsza część adresu

jest podawana na jego

wyjście.

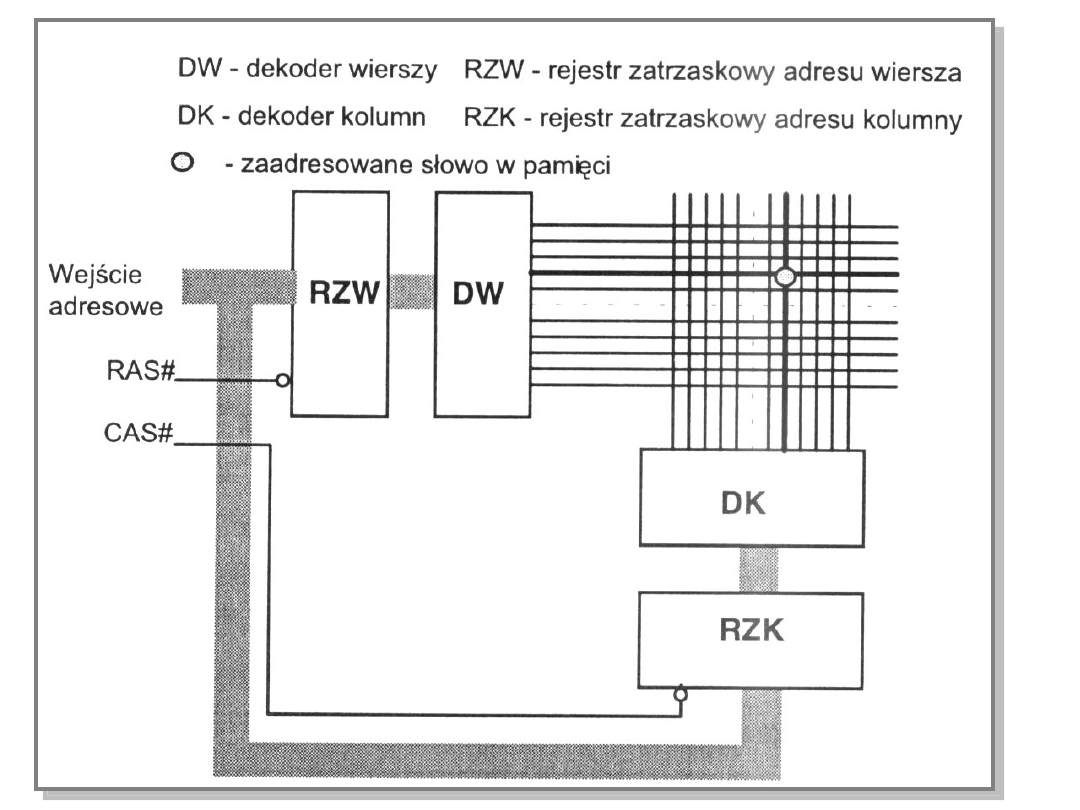

Poprawne zaadresowanie pamięci DRAM wymaga wykonania po

kolei następujących czynności:

1.

Podanie starszej części adresu na linie adresowe pamięci

DRAM jako adresu wiersza, a następnie wytworzenie

aktywnego zbocza sygnału RAS#, powodującego

zapamiętanie tego adresu w rejestrze zatrzaskowym adresu

wiersza.

2.

Odmierzenie określonego, wymaganego opóźnienia

czasowego.

3.

Podanie młodszej części adresu na linie adresowe pamięci

DRAM jako adresu kolumny i wytworzenie aktywnego zbocza

sygnału CAS#, powodującego zapamiętanie tego adresu w

rejestrze zatrzaskowym adresu kolumny.

4.

Następnie, zgodnie z sygnałami OE# lub WE#, dokonywana

jest operacja odczytu lub zapisu na zaadresowanym słowie.

5.

Po operacji odczytu odmierzane jest kolejne opóźnienie

czasowe przed rozpoczęciem kolejnego cyklu, potrzebne do

doładowania komórek pamiętających odczytane słowo.

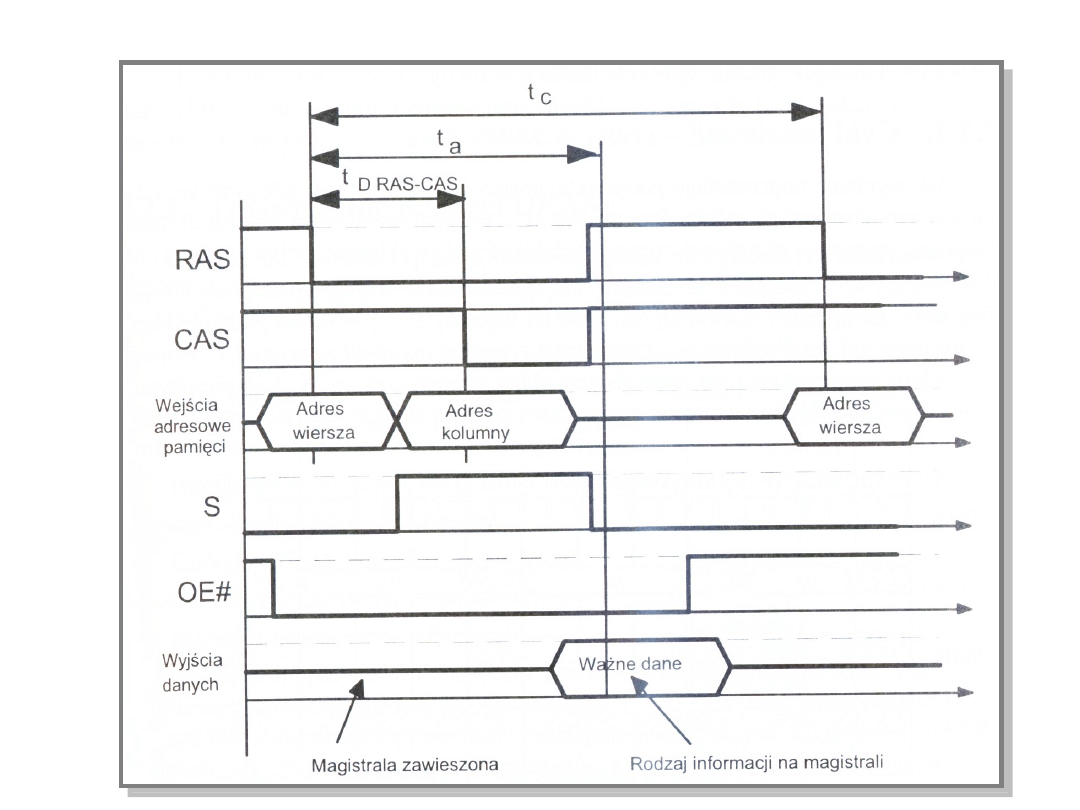

Operacja odczytu dla pamięci DRAM

OE# - stan niski oznacza operację zapisu.

S=1 - powoduje podanie na wejście adresowe pamięci

adresu kolumny

t

D RAS-CAS

- opóźnienie sygnału CAS# względem sygnału

RAS#

t

a

- czas dostępu

t

c

- minimalny czas pomiędzy dwoma kolejnymi

cyklami dostępu do pamięci

Document Outline

Wyszukiwarka

Podobne podstrony:

04 Dostęp do pamięci DRAM

04 Dostęp do pamięci DRAM

07-02 PAM-Dostęp do Waszego Makro-Ducha i do Waszej Świadomości, ezoteryka

07 02 PAM Dostęp do Waszego Makro Ducha i do Waszej świadomościid 7037

07-02 PAM-Dostęp do Waszego Makro-Ducha i do Waszej świadomości

Operacje I O z?zpośrednim dostępem do pamięci

07-02 PAM-Dostęp do Waszego Makro-Ducha i do Waszej Świadomości, ezoteryka

02.1.notatki całe do emocje-pamiec, Zniekształcenia, iluzje i niezwykłe zjawiska pamięciowe

02 Linux Prawa dostępu do plików i katalogów

Odblokowanie dostępu do wybranych folderów w Windows Vista, KOMPUTER - SERWIS - EDUKACJA, 02 Windows

Problemy telekomunikacyjne podstawowe dotyczące realizacji przewodowego dostępu do

Windows Vista - utrudniony dostęp do przycisku Zamknij, KOMPUTER - SERWIS - EDUKACJA, 02 Windows Vi

Windows Vista brak dostępu do Indeksu wydajności systemu, KOMPUTER - SERWIS - EDUKACJA, 02 Windows V

02.1.notatki całe do emocje-pamiec, Zniekształcenia, iluzje i niezwykłe zjawiska pamięciowe

Szerokopasmowy dostep do Internetu realizowany droga satelitarna

dostep do informacji publicznej Nieznany (2)

3 Parametry i usługi sieci dostępu do Internetu – teraz i w przyszłości

późniak koszałka,bazy?nych, Dostęp do?z?nych poprzez WWW

więcej podobnych podstron