WOJSKOWA AKADEMIA

TECHNICZNA

LABORATORIUM PODZESPOŁÓW

KOMPUTERÓW CYFROWYCH:

grupa: I0Y1S1

prowadzący: dr inż. Jan Chudzikiewicz

słuchacz : Adam Lipiński

Imię i Nazwisko

SPRAWOZDANIE Z PRACY LABORATORYJNEJ NR 4

Temat: Badanie układów sekwencyjnych.

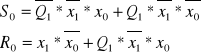

Zestaw: 8

ZAD. 2. Wykorzystując przerzutniki asynchroniczne RS zaprojektować układ sekwencyjny działający zgodnie z grafem przejść i wyjść podanym przez prowadzącego. Sprawdzić poprawność działania układu, wyniki przedstawić w postaci wykresów zmian odpowiednich wartości.

Aby zbudować ten układ sekwencyjny przepisałem odpowiednie wartości z grafu przejść do tabelki gdzie górny wiersz jest stanami przerzutników Q1 i Q0 natomiast pierwsza kolumna zawiera wektory wejściowe sterujące tymi przerzutnikami X1 i X0. Resztę komórek wypełniłem stanami jakie przerzutniki przechodzą przy danym wektorze wejściowym oraz stanach przerzutników (tab.2.1a). Aby rozróżnić sygnały które mają sterować danymi wejściami poszczególnych przerzutników napisałem tabelki o takiej samej budowie wypełnione stanami przechodzenia dla danego przerzutnika (tab.2.1b i 2.1c).Za pomocą tabelki przejść dla danego przerzutnika zapisałem stany w jakich powinny się znajdować dane przerzutniki oraz Zminimalizowałem funkcje dla każdego z wejść przerzutnika(tab.2.2a,b), zbudowałem adekwatne układy kombinacyjne i połączyłem je z odpowiednimi wejściami przerzutników po czym zbudowałem cały układ(rys.2.1a,b,c,d,e)

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

00 |

11 |

11 |

11 |

01 |

01 |

01 |

10 |

10 |

11 |

10 |

01 |

11 |

10 |

10 |

00 |

10 |

00 |

10 |

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

1 |

1 |

01 |

1 |

1 |

0 |

0 |

11 |

0 |

1 |

1 |

0 |

10 |

0 |

0 |

0 |

0 |

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

1 |

1 |

01 |

0 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

10 |

0 |

1 |

0 |

1 |

b) c)

tab.2.1 Stany w jakich powinny znajdować się przerzutniki.

S0 S1

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

0 |

-- |

-- |

1 |

01 |

1 |

-- |

-- |

0 |

11 |

0 |

-- |

-- |

0 |

10 |

0 |

-- |

-- |

0 |

R0

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

-- |

0 |

0 |

0 |

01 |

0 |

0 |

1 |

-- |

11 |

-- |

0 |

0 |

-- |

10 |

-- |

1 |

1 |

-- |

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

-- |

-- |

01 |

0 |

0 |

-- |

-- |

11 |

1 |

0 |

-- |

-- |

10 |

0 |

1 |

0 |

-- |

R1

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

-- |

0 |

0 |

0 |

01 |

-- |

-- |

0 |

0 |

11 |

0 |

-- |

0 |

0 |

10 |

-- |

0 |

1 |

0 |

b)

tab2.2 minimalizacja funkcji dla danych wejść przerzutników

a)

b)S0

c)R0

d)S1

e)R1

rys2.1 Zamodelowanie układu a) oraz poszczególnych układów kombinacyjnych b),c),d),e)

Wnioski:

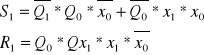

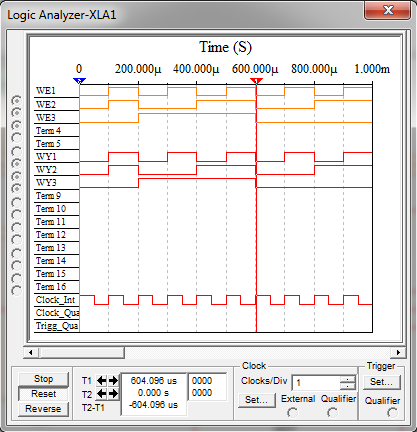

Zamodelowany układ został sprawdzony na diodach oraz przy pomocy analizatora stanów (rys2.2) jednakże nie można za pomocą analizatora przedstawić wszystkich stanów układu ponieważ układ wpada w nieskończoną pętle zgodną z zadanym grafem pomiędzy stanami Q1Q0={10} a Q1Q0={11} . w układzie nie występują hazardy ani wyścigi. Jednakże układ działa prawidłowo zachowując reguły przechodzenia do następnych stanów zgodnie z grafem.

rys.2.2 Przebieg pracy układu

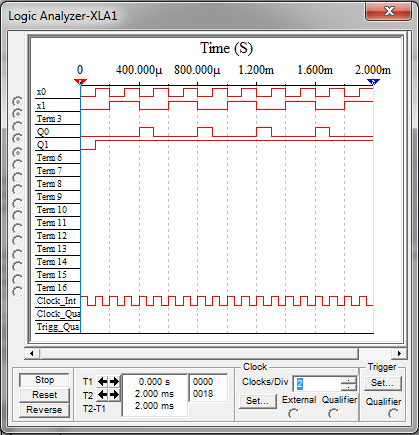

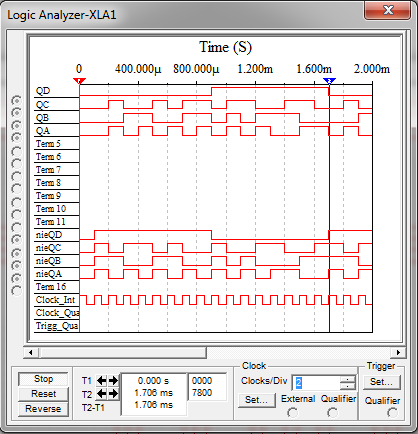

ZAD. 3. Wykorzystując przerzutniki typu D oraz niezbędne dodatkowe elementy logiczne zbudować licznik asynchroniczny o pojemności 24 wykorzystując metodę resetowania.Sprawdzić działanie zaprojektowanego licznika, wyniki przedstawić w postaci wykresów zmian odpowiednich wartości.

Aby zbudować ten licznik musiałem zamienić liczbę 23 na postać binarną ponieważ licznik ten jest o pojemności 24 czyli oznacza to ze będzie on mieć 24 stany i będzie liczyć w przód od stanu 00000(0 w dziesiętnym) do stanu 10111(23 dziesiętnie) i po stanie 24 ma przejść z powrotem do stanu zerowego. Użyłem do tego pięć przerzutnikach bo liczba 23 zajmuje 5 bitów w kodzie binarnym. Jednakże licznik składający się z 5 przerzutników będzie zliczać do 31. Aby zresetować do stanu 00000 aby licznik liczył od nowa metodą resetowania podłączyłem wyjścia przerzutników QbQc QdQe do bramki and dzieki temu jeśli na tych wejściach pojawią się jedynki licznik zostanie zresetowany i stan 25 jako liczba 24 binarnie się nie pojawi natomiast przejdzie z powrotem do stanu 0.

Rys3.1 Budowa układu licznika

Wnioski:

Zbudowany układ działa poprawnie w różnicy do poprzedniego układu dało się pokazać wszystkie stany układu. Układ nie generuje żadnych hazardów i wyścigów.

rys.3.2 Przebieg pracy układu licznika

ZAD. 4. Wykorzystując przerzutniki typu JK oraz niezbędne dodatkowe elementy logiczne zbudować rejestr równoległo-szeregowy z asynchronicznym wpisem informacji z wejść równoległych. Sprawdzić poprawność działania układu, wyniki przedstawić w postaci wykresów zmian odpowiednich wartości.

Za pomocą wejścia SET przerzutnika JK wprowadzam dane do rejestru gdzie potem przeniesienie jest propagowane przez szeregowe połączenie wejść Q z J i Q' z K. Gdy na wejściu pojawia się 0 to informacja zostaje skasowana ponieważ wejście RESET jest wysterowane przez zanegowaną daną wejściową. Rejestr zbudowałem na przerzutnikach JK i bramkach not.

Rys4.1 Budowa układu rejestru

Wnioski:

Układ działa poprawnie dla zadanych danych nie generuje żadnych hazardów czy wyścigów. Rys 4.2 w pełni pokazuje pracę rejestru.

Rys4.2 Praca rejestru.

ZAD. 5. Wykorzystując przerzutniki typu JK oraz niezbędne dodatkowe elementy logiczne zbudować licznik synchroniczny o pojemności 16 i kolejności zmian stanów zgodnie z tabelą zmian stanów.

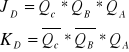

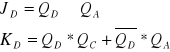

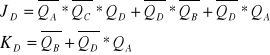

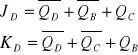

Aby zbudować ten licznik najpierw w tabeli 5.1 wpisałem sobie zmiany stanów dla wszystkich przerzutników potem za pomocą tabelki przejść przerzutnika JK napisałem tabele Karnaugh'a (tab.5.2) dla poszczególnych wejść przerzutników i zminimalizowałem funkcję. Zbudowałem adekwatne układy kombinacyjne do tych funkcji(rys 5.1 b, c, d ,e, f, g, h, i) i połączyłem je z odpowiednimi wejściami przerzutników (rys 5.1a).

Stan |

Qa |

QC |

QB |

QA |

Q'D |

Q'C |

Q'B |

Q'A |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

4 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

5 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

6 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

9 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

10 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

12 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

13 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

14 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

15 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

tab.5.1 tabela zmiany stanów układu

a) b)

JD JC

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

0 |

0 |

0 |

0 |

01 |

0 |

0 |

1 |

0 |

11 |

-- |

-- |

-- |

-- |

10 |

-- |

-- |

-- |

-- |

KD

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

-- |

-- |

-- |

-- |

01 |

-- |

-- |

-- |

-- |

11 |

0 |

0 |

0 |

0 |

10 |

0 |

1 |

0 |

0 |

c)

JB

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

-- |

-- |

01 |

0 |

1 |

-- |

-- |

11 |

1 |

0 |

-- |

-- |

10 |

1 |

0 |

-- |

-- |

KB

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

-- |

-- |

1 |

0 |

01 |

-- |

-- |

1 |

0 |

11 |

-- |

-- |

1 |

1 |

10 |

-- |

-- |

0 |

0 |

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

1 |

1 |

1 |

0 |

01 |

-- |

-- |

-- |

-- |

11 |

-- |

-- |

-- |

-- |

10 |

1 |

-- |

-- |

1 |

KC

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

-- |

-- |

-- |

-- |

01 |

1 |

1 |

1 |

0 |

11 |

1 |

1 |

0 |

0 |

10 |

-- |

-- |

-- |

-- |

d)

JA

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

1 |

-- |

-- |

1 |

01 |

1 |

-- |

-- |

1 |

11 |

1 |

-- |

-- |

1 |

10 |

1 |

-- |

-- |

0 |

KA

X1X0\ Q1Q0 |

00 |

01 |

11 |

10 |

00 |

-- |

1 |

1 |

-- |

01 |

-- |

1 |

1 |

-- |

11 |

-- |

0 |

1 |

-- |

10 |

-- |

1 |

1 |

-- |

Tab5.2 Minimalizacja funkcji za pomocą tebeli Karnaugh'a

a)

b)

c)

d)

e)

Rys5.1 a) Budowa układu licznika oraz poszczególnych układów kombinacyjnych sterujących wejściami b), c), d), e)

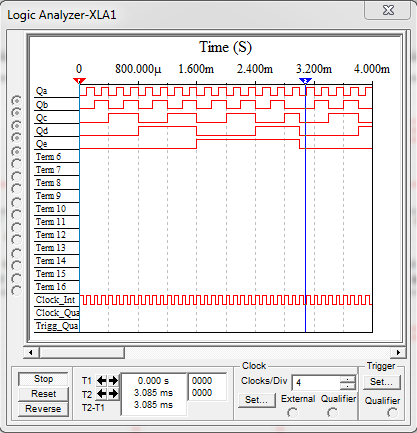

Wnioski:

Układ działa poprawnie nie generuje żadnych hazardów ani wyścigów. Na (rys5.2) przedstawiona jest praca tego układu. Za pomocą analiz era stanów przedstawiłem wszystkie stany na wyjściu układu.

Wyszukiwarka

Podobne podstrony:

laborki2-starsze, WAT, SEMESTR I, PKC

sprawozdanie z 2 laborki, WAT, SEMESTR I, PKC, do sprawozdania

WSTĘP 44, studia mechatronika politechnika lubelska, Studia WAT, semestr 2, FIZYKA 2, LABORKI, labor

SPRAWOZDANIE(2), WAT, SEMESTR I, PKC

strona tytułowa 1, gik, semestr 4, kartografia, Kartografia, Kartografia matematyczna - powtórka z s

III WYNIKI POMIARÓW, studia mechatronika politechnika lubelska, Studia WAT, semestr 2, FIZYKA 2, LAB

STRONA TYTUŁOWA, UG, 5. semestr, Semestr 5. STARSZE, sem 5, dydaktyka, gimnazjum

Labolatoria z fizyki - strona tytulowa, inf, I sem, Fizyka, Laborki

Zadania laboratoryjne dzienne(1), WAT, SEMESTR I, PKC

Sprawozdanie EOP, WAT Elektronika i telekomunikacja WAT, Semestr V, EOP, Laborki

lab. 27, studia mechatronika politechnika lubelska, Studia WAT, semestr 2, FIZYKA 2, LABORKI, labork

strona tytulowa pracy semestralnej, BHP

mmmm, WAT Elektronika i telekomunikacja WAT, Semestr V, EOP, Laborki

SPRAOZDANIE STRONA TYTUŁOWA, PWR, Semestr 5, Grafika komputerowa, Grafika komputerowa, SPRAWOZDANIE

zad21 WOJSKOWA AKADEMIA TECHNICZNA, studia mechatronika politechnika lubelska, Studia WAT, semestr 2

Sprawozdanie z drugiego zadania, WAT, SEMESTR I, PKC

więcej podobnych podstron