Numer ćwiczenia |

3 |

Tytuł ćwiczenia: Statyczne badanie przetworników |

||

Data wykonania ćwiczenia: |

07.11.2012 |

Nazwisko i imię: |

||

Data oddania sprawozdania: |

|

|

|

|

Numer grupy laboratoryjnej: |

8A |

|

|

|

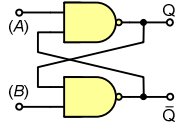

Asynchroniczny przerzutnik RS zbudowany z bramek NAND.

Rn-1 |

Sn-1 |

Qn-1 |

Qn |

0 |

0 |

0 |

1N |

0 |

0 |

1 |

1N |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

Schemat logiczny.

Tabela stanów logicznych.

A-1 |

Bn-1 |

Qn-1 |

Qn |

Opis |

0 |

0 |

X |

1N |

Zabroniony |

0 |

1 |

X |

1 |

Set |

1 |

0 |

X |

0 |

Reset |

1 |

1 |

Qn-1 |

Qn-1 |

Bez zmian |

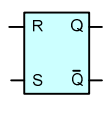

Symbol graficzny.

Uproszczona tabela stanów logicznych.

Synchroniczny przerzutnik RS zbudowany z bramek NAND.

Schemat logiczny. Symbol graficzny.

An-1 Bn-1 CKn-1 Qn-1 |

0 0 |

0 1 |

1 0 |

1 1 |

|||||

0 0 |

0 |

0 |

0 |

0 |

|||||

0 1 |

1 |

1 |

1 |

1 |

|||||

1 0 |

0 |

0 |

1 |

1N |

|||||

1 1 |

1 |

0 |

1 |

1N |

|||||

An-1 Bn-1 CKn-1 Qn-1 |

0 0 |

0 1 |

1 0 |

1 1 |

|||||

0 |

Qn-1 |

Qn-1 |

Qn-1 |

Qn-1 |

|||||

1 |

Qn-1 |

0 |

1 |

N |

|||||

Tabela stanów logicznych. Uproszczona tabela stanów logicznych

Synchroniczny przerzutnik D zbudowany z bramek NAND

Schemat logiczny. Symbol graficzny.

CK n-1 |

D n-1 |

Q n-1 |

Q n |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Tablica stanów logicznych.

Wnioski:

Za pomocą wejścia synchronizującego mamy możliwość zapisania dowolnego pożądanego sygnału na dowolną chwilę czasową, która zależy od podawanego sygnału synchronizującego.

W przerzutniku synchronicznym D wykluczone jest wstąpienie stanu zabronionego poprzez zastosowanie dodatkowej bramki NAND.

Wyszukiwarka