Jaworek Michał gr. 12

Sprawozdanie

(przerzutniki)

Przerzutnik jest układem elektronicznym wytwarzającym w sposób zamierzony i kontrolowany, okresowe lub nieokresowe przebiegi

elektryczne prostokątne w wyniku szybkich procesów przełączania (tzw. przerzutów) pomiędzy różnymi stanami. Proces przełączania zależy od

struktury i parametrów układu przerzutnikowego.

Przerzutniki dwustanowe dzieli się na trzy podstawowe grupy:

–

przerzutniki bistabilne - które charakteryzuje istnienie dwóch stanów równowagi trwałej (dwa stany stabilne), przy czym dla przejścia z

jednego stanu do drugiego konieczne jest doprowadzenie zewnętrznego sygnału wyzwalającego

–

przerzutniki monostabilne - istnieje tylko jeden trwały stan równowagi, w którym układ może utrzymać się przez czas nieograniczony.

Zewnętrzny sygnał wyzwalający powoduje przejście ze stanu stabilnego do quasi-stabilnego, a następnie po pewnym czasie układ samoistnie

powraca do stanu stabilnego.

–

przerzutniki astabilne - nie istnieje stan równowagi trwałej, w którym układ mógłby utrzymać się w czasie nieograniczonym. Przerzutniki takie

wytwarzają przebiegi samoczynnie, bez udziału sygnału zewnętrznego, podobnie do generatorów sinusoidalnych.

Przerzutniki stosuje się do przechowywania małych ilości danych, do których musi być zapewniony ciągły dostęp. Jest to spowodowane

fizycznymi i funkcjonalnymi cechami przerzutników. Są one większe od pojedynczej komórki pamięci, ale pozwalają pozostałym częściom układu na

bezpośredni dostęp do przechowywanych danych.

Ze względu na tryb pracy układy sekwencyjne dzielimy na:

–

Układy asynchroniczne – nie mają wejścia sterującego ich pracą (synchronizującego, zegarowego), zatem stany wyjść zmieniają się wraz

ze zmianą wejść układu.

–

Układy synchroniczne – reakcja takiego układu na wartości wejść jest determinowana, w dyskretnych chwilach czasowych, przez zewnętrzny

sygnał sterujący C (zegarowy, synchronizujący, taktujący).

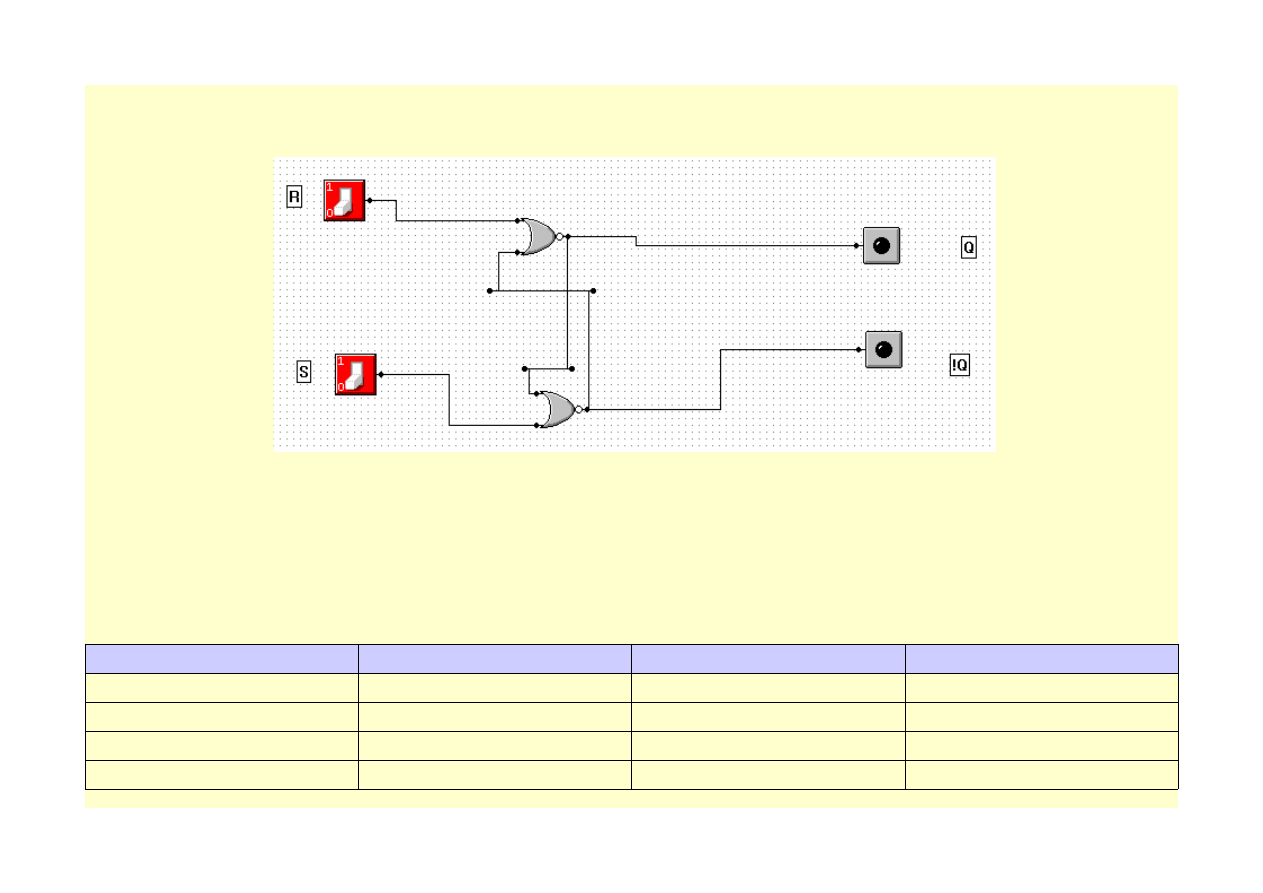

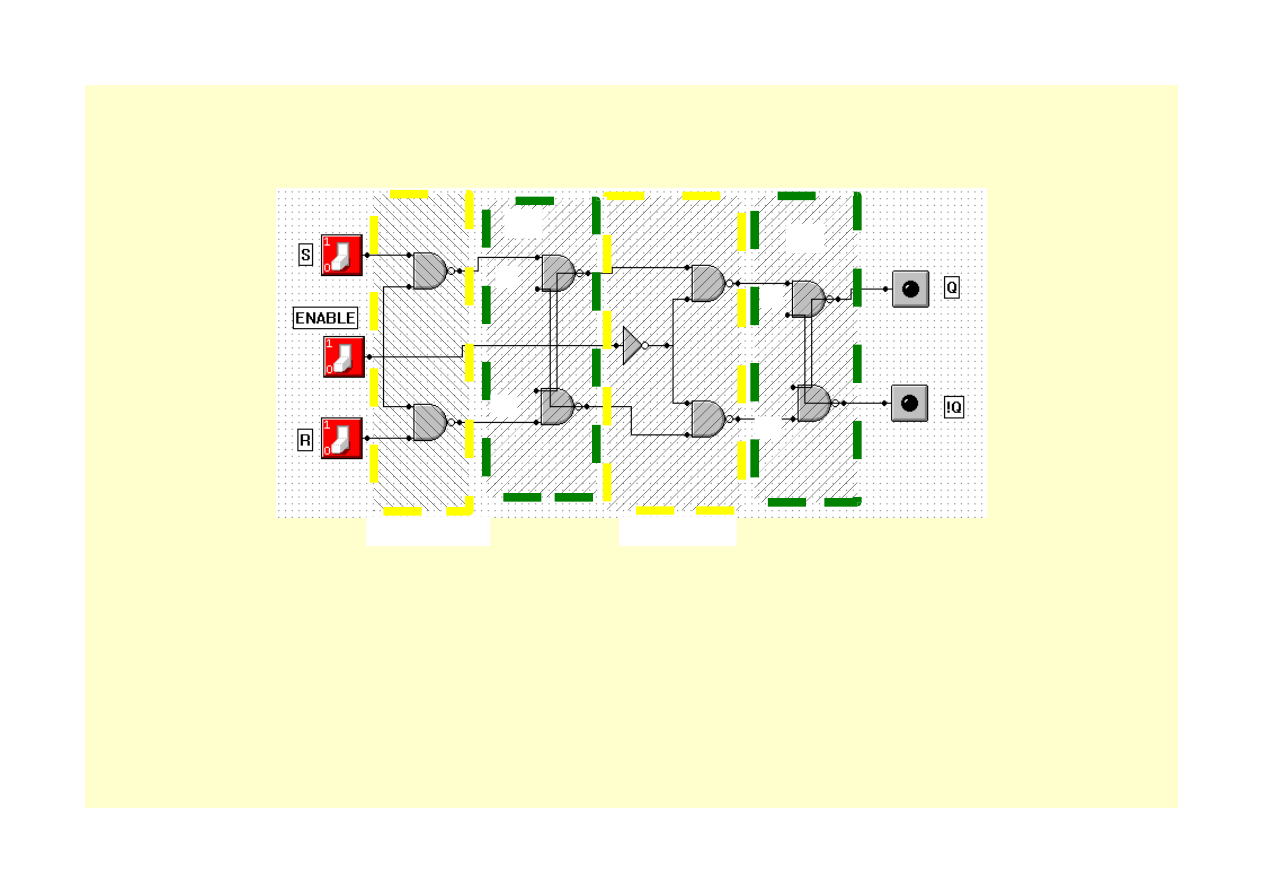

Zadanie 1

Zbudować i sprawdzić działanie przerzutnika RS na bramkach NOR

Idea działania asynchronicznego przerzutnika typu RS jest następująca. Przerzutnik niezależnie od tego w jakim stanie się znajduje jeżeli

dostanie sygnał SET = 1 , RESET = 0 przejdzie w stan 1. Podobnie niezależnie od tego w jakim stanie się znajduje jeżeli dostanie sygnał SET = 0 ,

RESET = 1 przejdzie w stan 0. Jeżeli na żadne z wejść nie zostanie podany sygnał wysoki przerzutnik nie zmieni swojego stanu. Niedozwolona jest

sytuacja w której na oba wejścia zostaną podane jedynki. W takim przypadku na obu bramkach NOR na jednym z wejść pojawi się 1. Znając zasadę

działania bramki NOR wiemy, że spowoduje to ustalenie na wyjściu obu bramek stanu 0. Ze względu na to, że jedno wyjście reprezentuje Q a drugie

~Q nie możemy zaakceptować sytuacji w której oba wyjścia wskazują ten sam stan logiczny. Dlatego uzupełniając tabele przy ostatniej kolumnie

piszemy „stan zabroniony”. Ostatecznie tabela wygląda następująco.

S

R

Q

n

~Q

n

0

0

Q

n-1

~Q

n-1

0

1

0

1

1

0

1

0

1

1

Stan zabroniony

Stan zabroniony

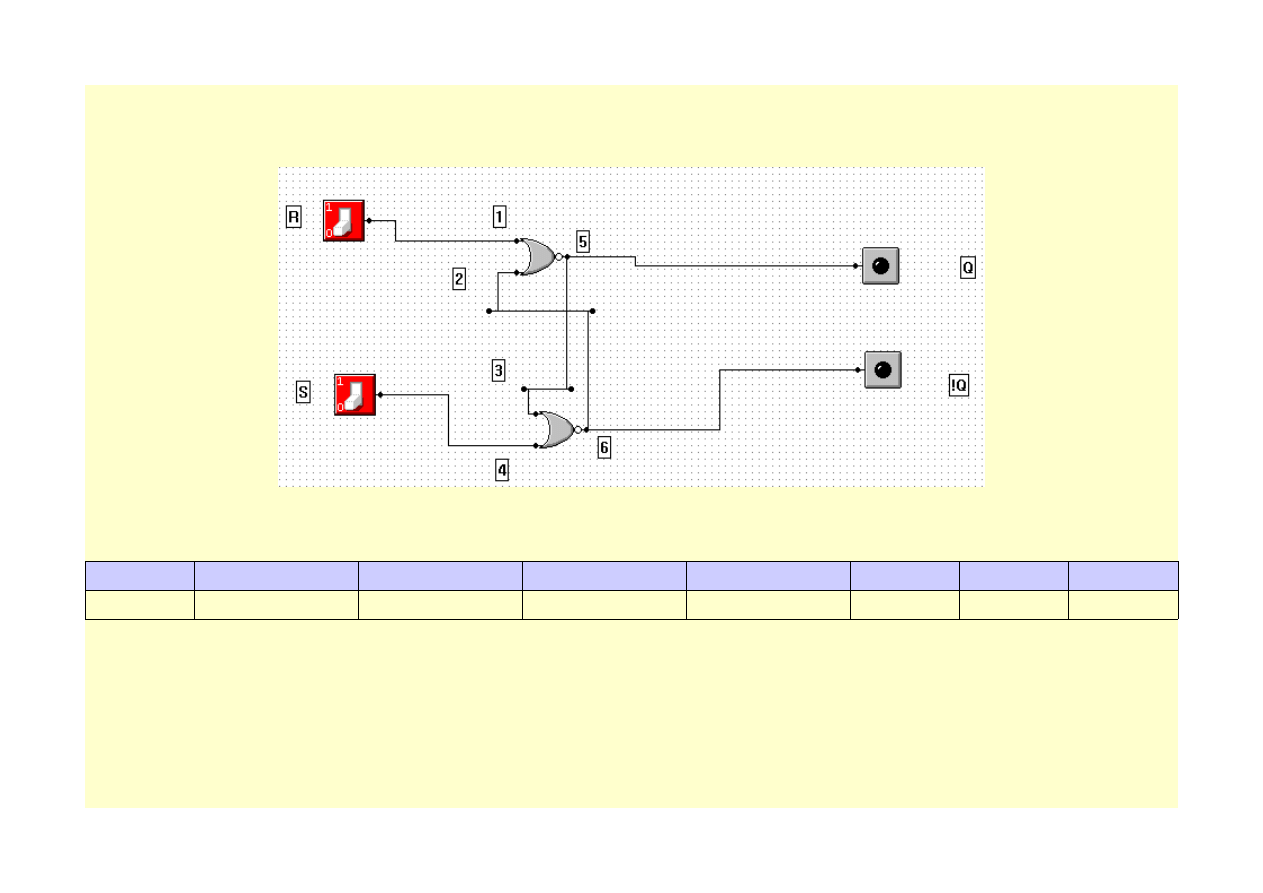

Sprawdzenie poprawności działania układu.

Dla celów analizy układu opisałem kolejne wejścia i wyjścia bramek logicznych jak na rysunku.

Przyjmijmy, że przerzutnik w stanie wysokim ma na obu wejściach podane stany niskie. Wówczas:

1

2

3

4

5

6

Q

~Q

0

0

1

0

1

0

1

0

Gdy zostaje przełączony na jedynkę przełącznik R kolejno będą następować poniższe zdarzenia:

–

punkt „1” wchodzi w stan wysoki

–

górna bramka NOR dostanie na wejście sygnały 1,0

–

górna bramka NOR zwróci na wyjściu 0 (punkty „3” i „5” wchodzi w stan niski)

–

dolna bramka NOR dostanie na wejście sygnały 0,0

–

dolna bramka NOR zwróci na wyjściu 1 (punkty „2” i „6” wchodzi w stan wysoki)

–

górna bramka NOR dostanie na wejście sygnały 1,1 (co nie zmieni jej sygnału wyjściowego)

Po tej serii operacji przerzutnik będzie w następującym stanie:

1

2

3

4

5

6

Q

~Q

1

1

0

0

0

1

0

1

Czyli Reset sygnał zadziałał poprawnie.

Gdy zostaje na powrót przełączony na zero przełącznik R kolejno będą następować poniższe zdarzenia:

–

punkt „1” wchodzi w stan niski

–

górna bramka NOR dostanie na wejście sygnały 0,1

–

górna bramka NOR zwróci na wyjściu 0 (punkty „3” i „5” nie zmieniają stanu i ciągle są w stanie niskim)

–

reszta układu nie reaguje

Jak widać oba niskie stany na wejściach nie powodują żadnej zmiany na wyjściu. Układ reaguje prawidłowo a jego stan przedstawia tabelka:

1

2

3

4

5

6

Q

~Q

0

1

0

0

0

1

0

1

Czyli w tym momencie mamy przerzutnik w stanie niskim w oboma stanami niskimi na wejściach. Sprawdźmy na koniec czy przerzutnik

prawidłowo zachowa się gdy zechcemy ustawić go na stan wysoki:

Gdy zostaje przełączony na jeden przełącznik S kolejno będą następować poniższe zdarzenia:

–

punkt „4” wchodzi w stan wysoki

–

dolna bramka NOR dostanie na wejście sygnały 0,1

–

dolna bramka NOR zwróci na wyjściu 0 (punkty „2” i „6” zmienią stan na niski)

–

górna bramka NOR dostanie na wejście sygnały 0,0

–

górna bramka NOR zwróci na wyjściu 1 (punkty „3” i „5” wchodzi w stan wysoki)

–

dolna bramka NOR dostanie na wejście sygnały 1,1 (co nie zmieni jej sygnału wyjściowego)

Po tych operacjach przerzutnik jest w stanie:

1

2

3

4

5

6

Q

~Q

0

0

1

1

1

0

1

0

Jak widać układ odpowiedział prawidłowo.

Zadanie 2

Zbudować i sprawdzić działanie przerzutnika RS na bramkach NAND

Idea działania tego przerzutnika jest taka sama jak poprzednio. Jedyna różnica polega na tym, że przerzutnik RS zbudowany na bramkach typu

NAND reaguję na sygnały niskie. Oznacza to, że cały czas na wejścia powinniśmy podawać sygnały wysokie, a gdy chcemy aby przerzutnik wszedł w

określony stan podajemy na odpowiednie wejście stan 0. Działanie tego układu obrazuje tabelka:

~S

~R

S

R

Q

n

~Q

n

1

1

0

0

Q

n-1

~Q

n-1

1

0

0

1

0

1

0

1

1

0

1

0

0

0

1

1

Stan zabroniony

Stan zabroniony

Sprawdzenie poprawności działania układu.

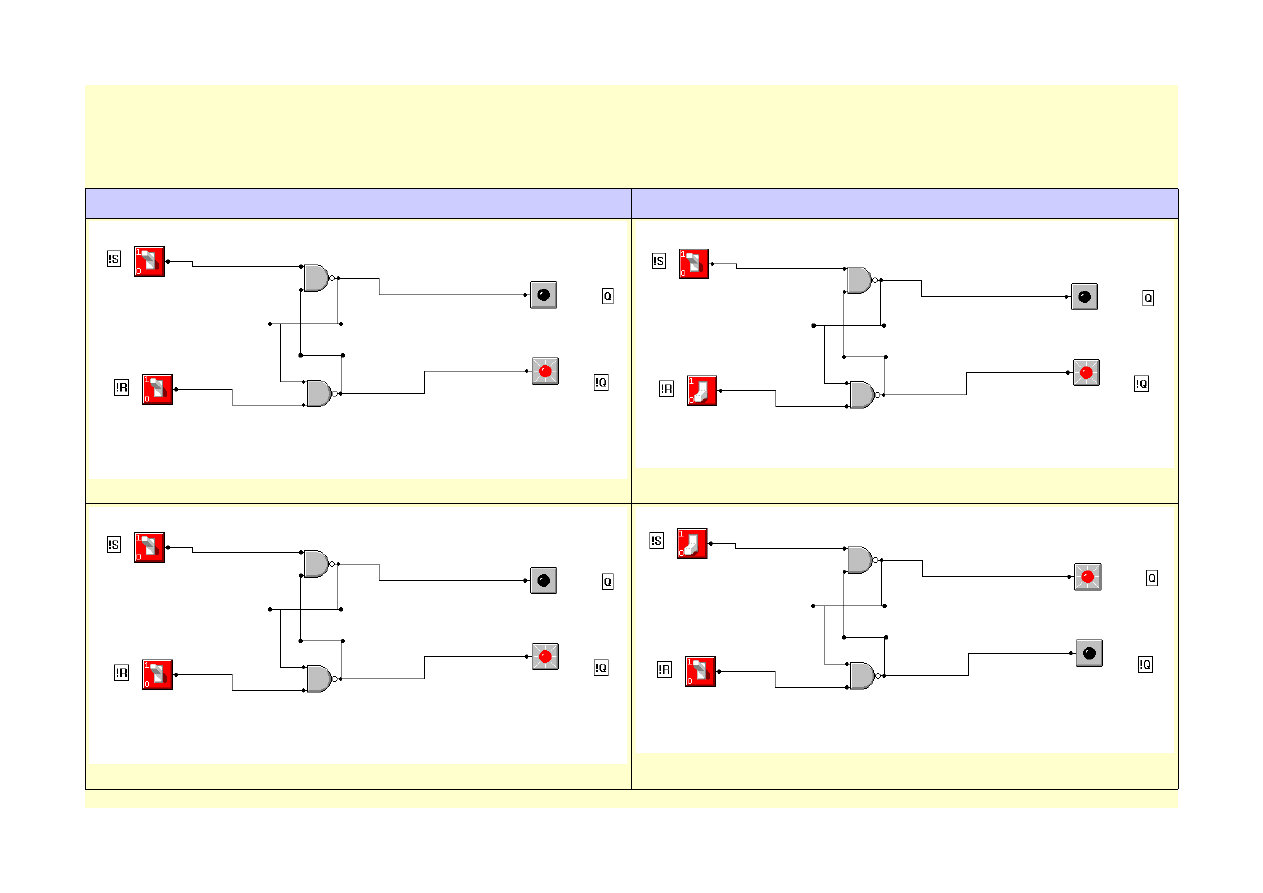

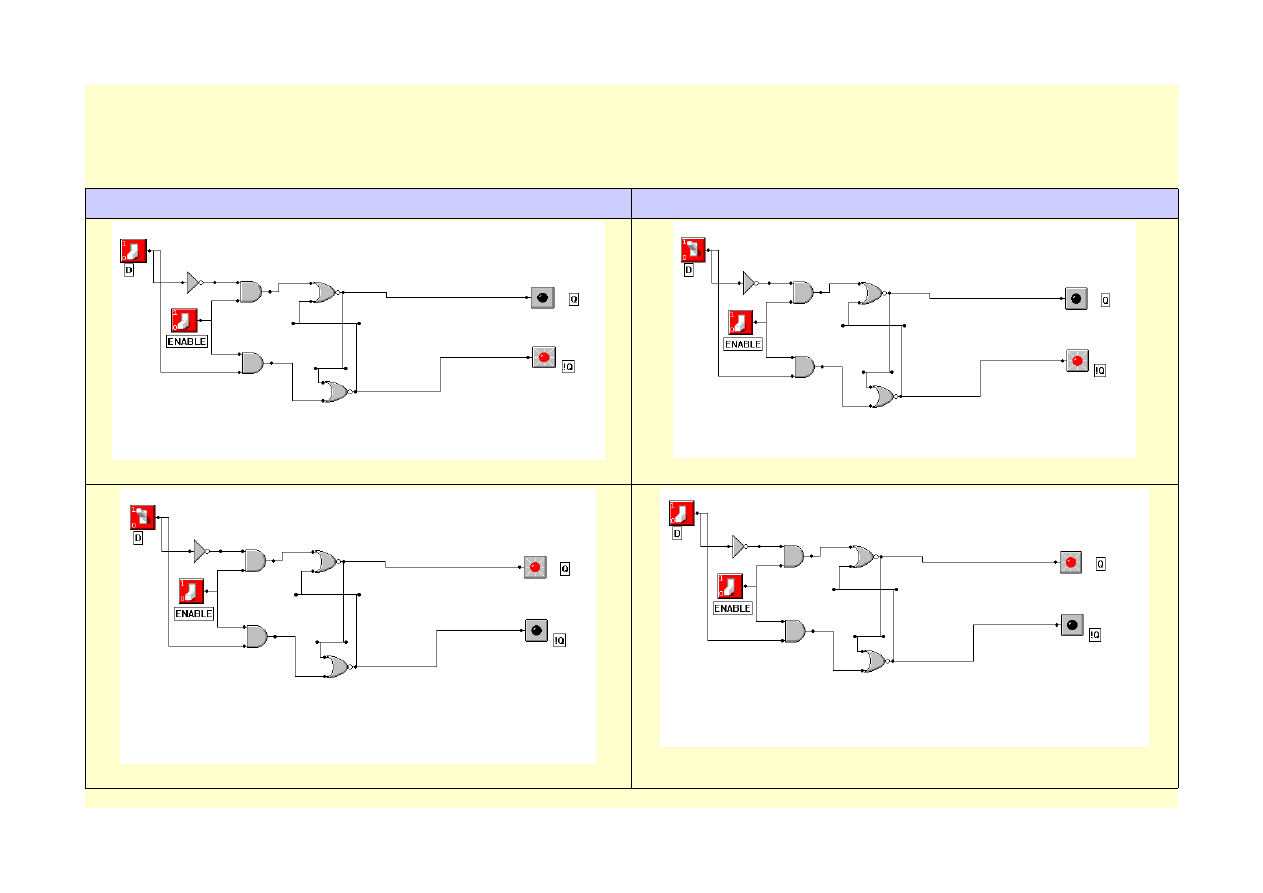

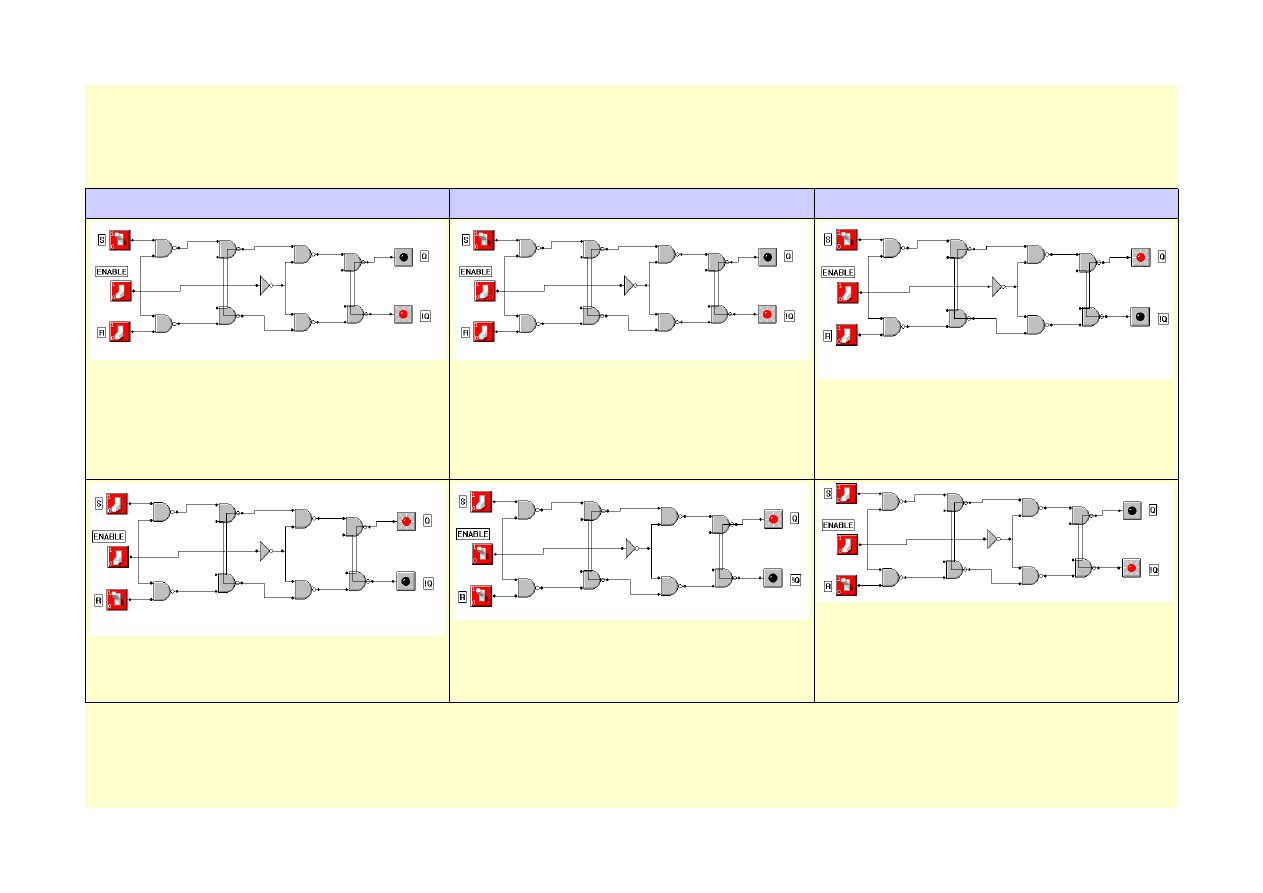

W tym przypadku do analizy układu skorzystałem z symulatora programu multimedia logic. W tabelce przedstawiono układ przed zmianą

sygnałów wejściowych i po tej zmianie:

Stan przed zmianą

Stan po zmianie

Początkowy stan: 0

Sygnał RESET – bez zmian stan: 0

Początkowy stan: 0

Sygnał SET – stan: 1

Stan przed zmianą

Stan po zmianie

Początkowy stan: 1

Sygnał SET – bez zmian stan: 1

Początkowy stan: 1

Sygnał RESET – stan: 0

Jak widać przy pomocy symulacji zaobserwowaliśmy, że układ odpowiada poprawnie.

Zadanie 3

Zbudować i sprawdzić działanie przerzutnika D typu zatrzask

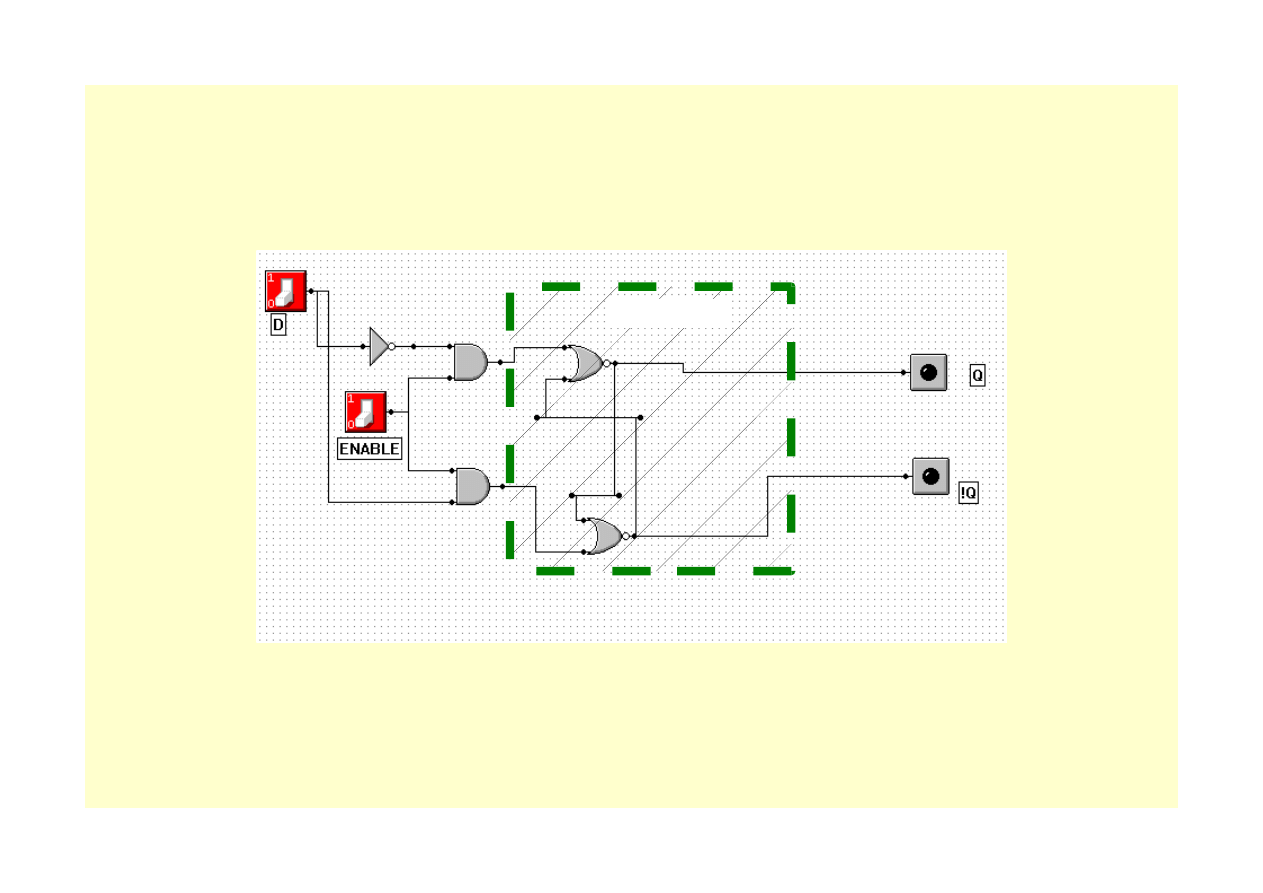

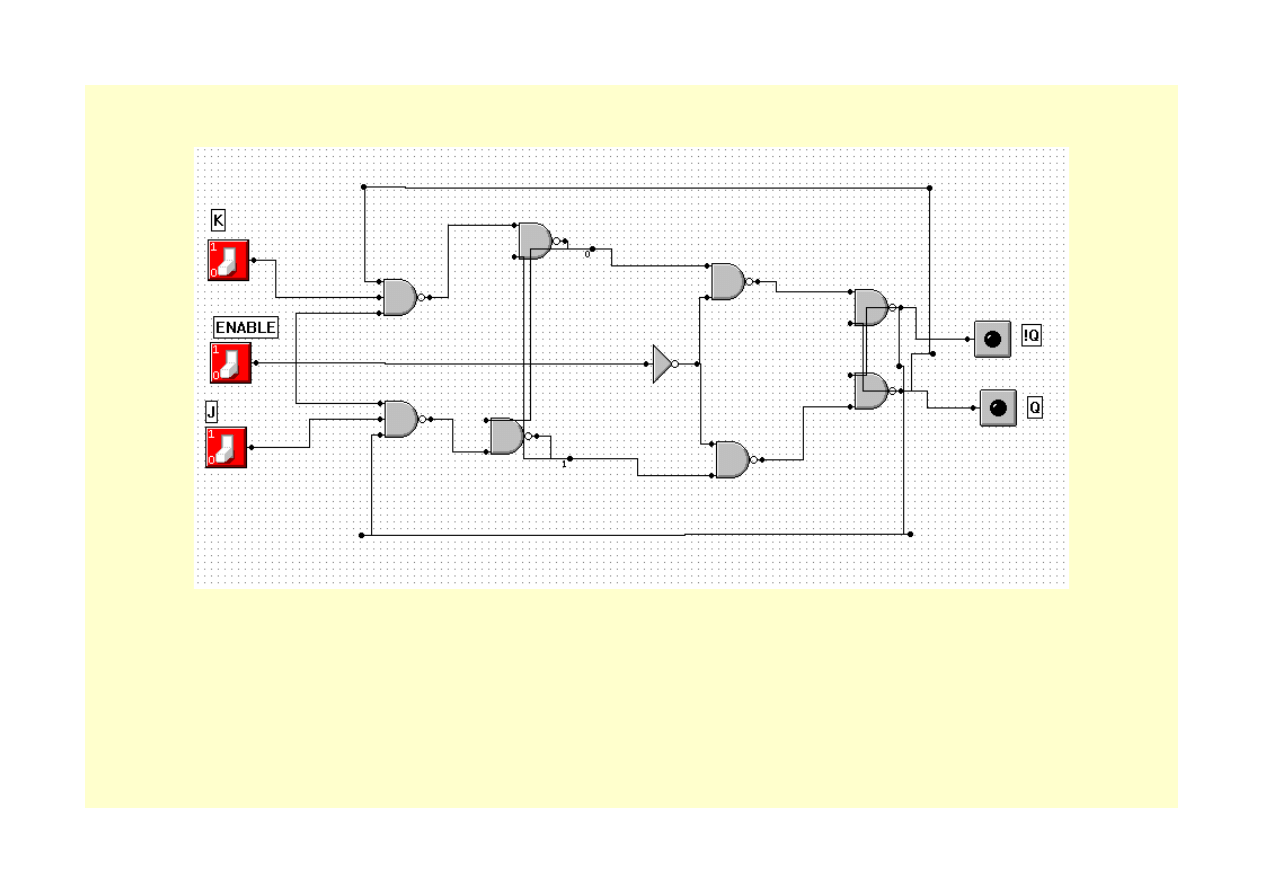

Idea działania przerzutnika typu D jest nieco odmienna od RS. Przerzutniki typu D są zawsze synchroniczne tzn. posiadają wejście

zegarowe(CLOCK lub ENABLE). Na wejście D podawane są dane (Data). Gdy na wejściu ENABLE jest jedynka przerzutnik przyjmuje stan wejścia

D. Gdy stan na wejściu ENABLE zmieni się na zero przerzutnik „zatrzaskuje się” (stąd nazwa). Od tego momentu niezależnie od wartości na wejściu

D przerzutnik utrzymuje wartość zapamiętaną wcześniej. Układ logiczny realizujący te założenia jest następujący:

Przerzutnik RS

R

S

Na rysunku przedstawiłem sposób w jaki można rozumieć ten układ. Częścią przerzutnika typu D jest asynchroniczny przerzutnik typu RS do

którego wprowadzamy D na wejście SET oraz ~D na wejście RESET. Oczywiście przekazujemy te wartości tylko jeżeli ENABLE jest w stanie

wysokim (służą temu bramki AND). Jeżeli ENABLE jest w stanie niskim przerzutnik RS otrzyma dwa zera na wejścia, a jak wiemy z poprzednich

podpunktów nie spowoduje to żadnej reakcji (przerzutnik zatrzaśnięty).

Ostatecznie zasadę działania układu obrazuje tabelka:

ENABLE

D

Q

n

~Q

n

0

0

Q

n-1

~Q

n-1

0

1

Q

n-1

~Q

n-1

1

0

0

1

1

1

1

0

Sprawdzenie poprawności działania układu.

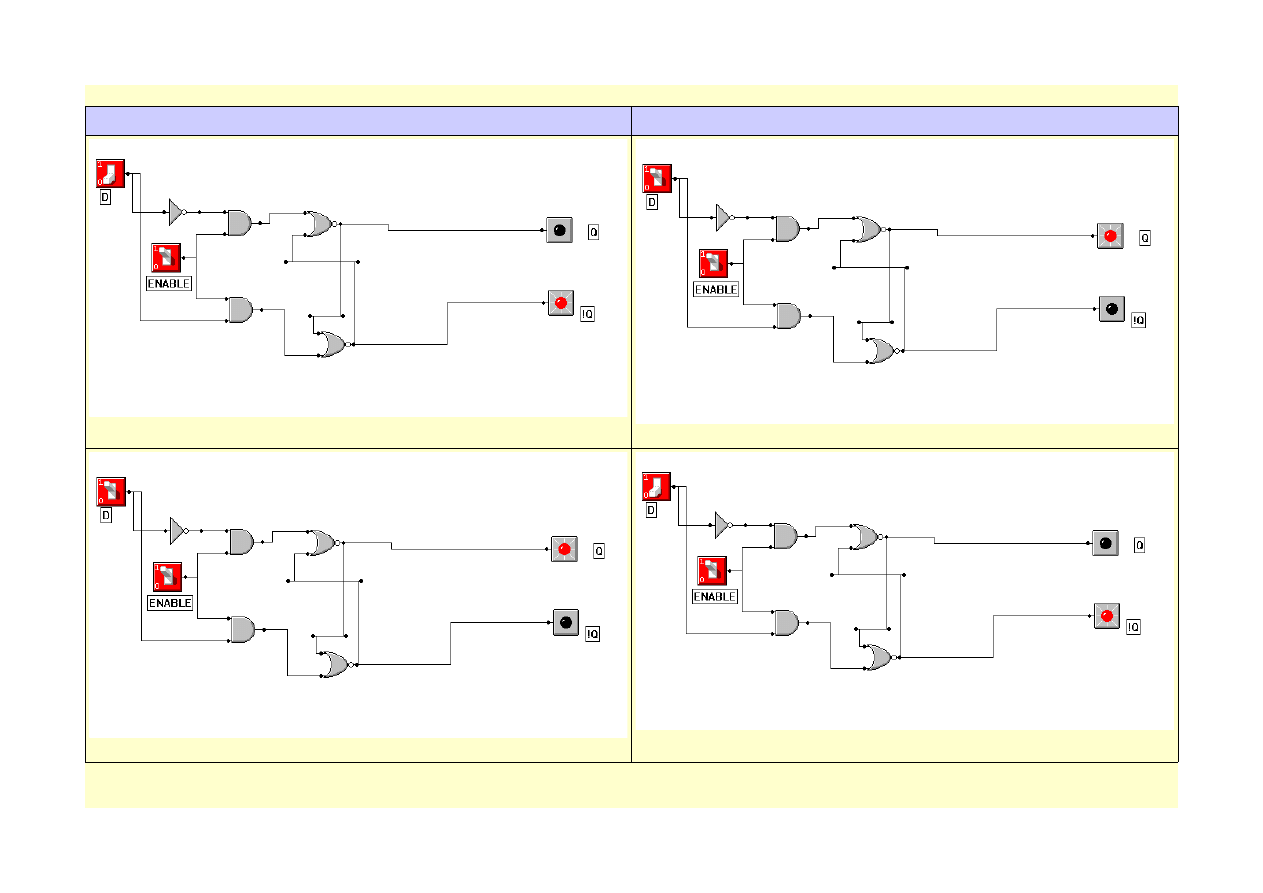

W tym przypadku do analizy układu skorzystałem z symulatora programu multimedia logic. W tabelce przedstawiono układ przed zmianą

sygnałów wejściowych i po tej zmianie:

Stan przed zmianą

Stan po zmianie

Mimo, że D=1 przerzutnik jest zatrzaśnięty i nie zmienia stanu.

Mimo, że D=0 przerzutnik jest zatrzaśnięty i nie zmienia stanu.

Stan przed zmianą

Stan po zmianie

Przerzutnik nie jest zatrzaśnięty więc przyjmuje wartość D.

Przerzutnik nie jest zatrzaśnięty więc przyjmuje wartość D.

Jak widać symulacja pokazuje, że układ działa poprawnie.

Zadanie 4

Zbudować i sprawdzić działanie przerzutnika RS master-slave (bramki NAND)

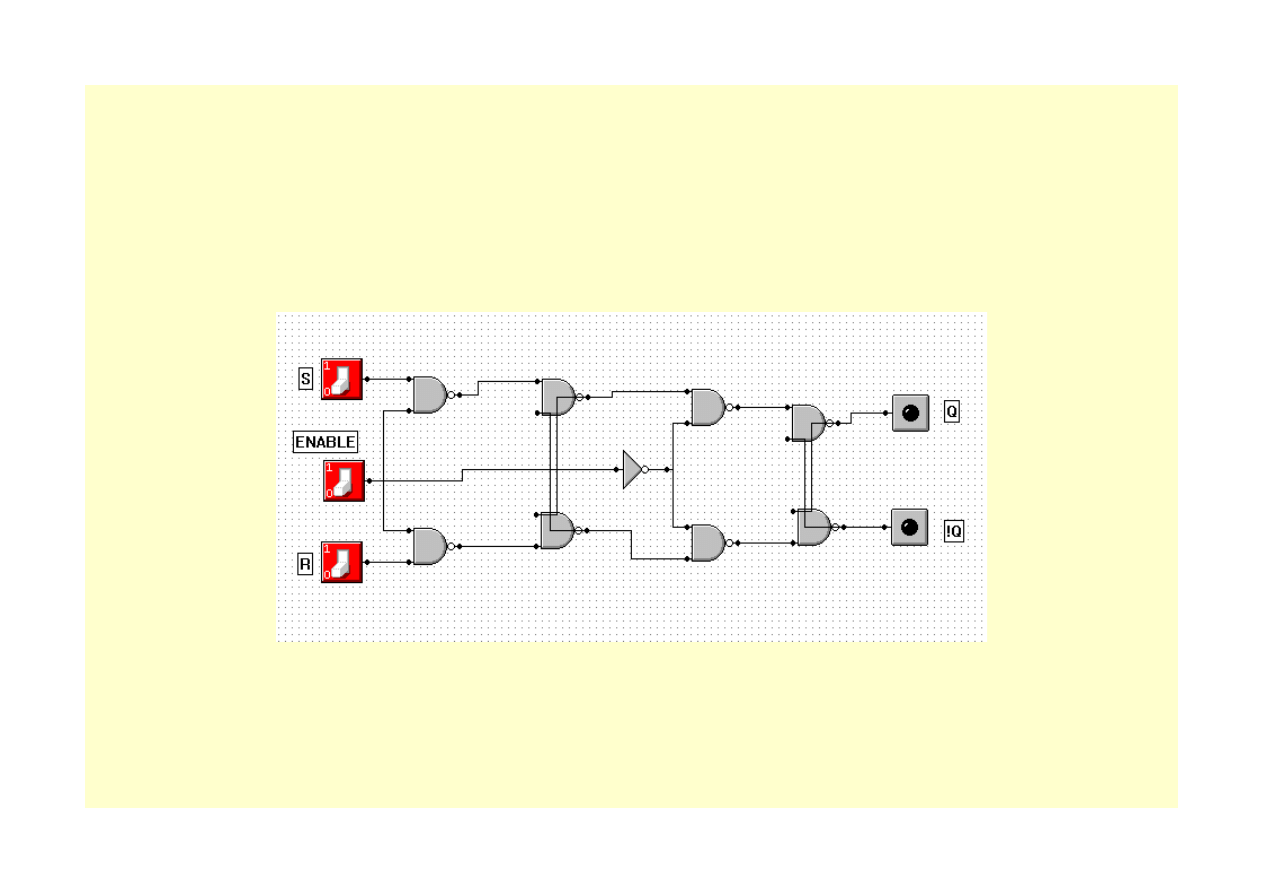

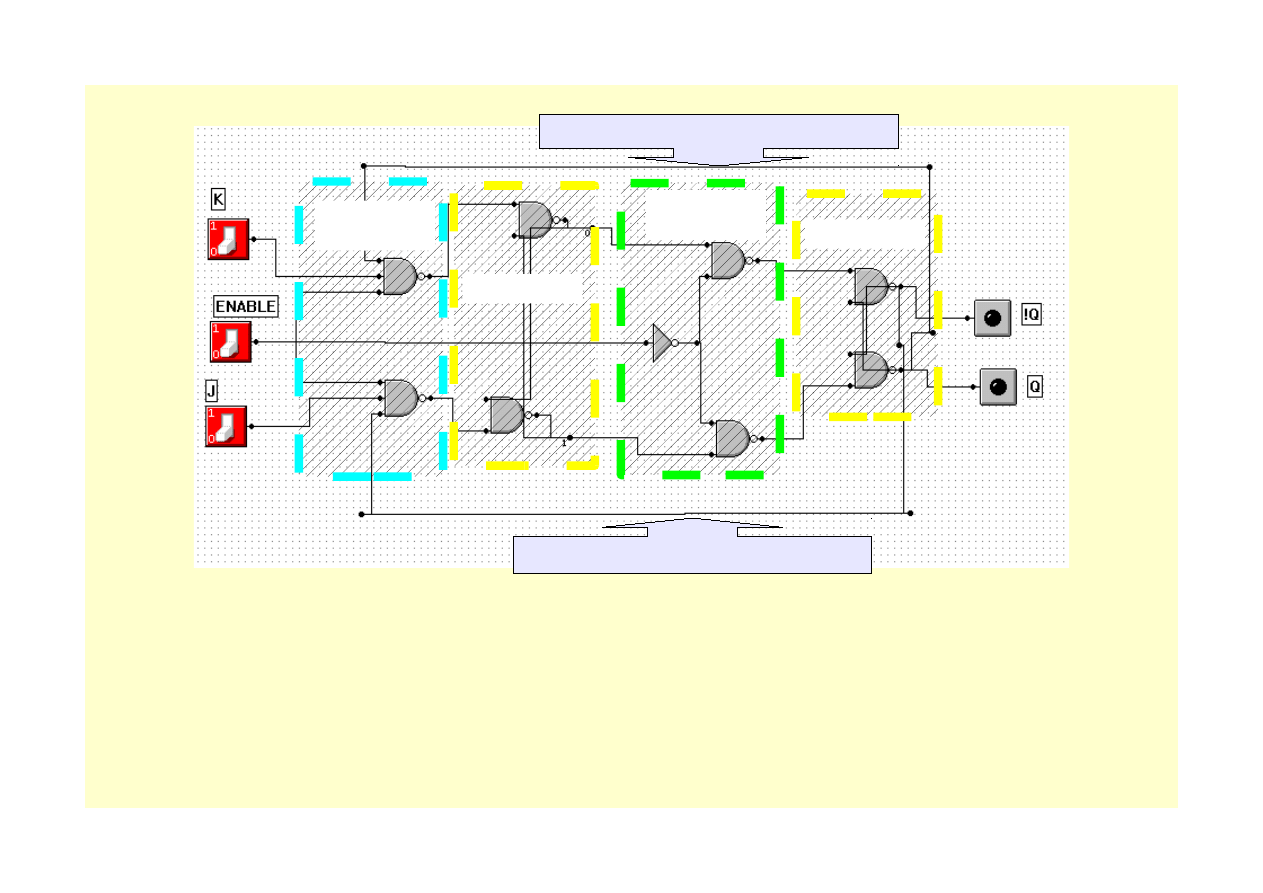

Idea działanie przerzutnika RS master-slave jest podobna do standardowego przerzutnika RS. Różnica polega na tym, że korzystamy tutaj z

rozwiązania synchronizującego (ENABLE) oraz, że wartość na wyjściu przerzutnika pojawia się dopiero gdy ENABLE przechodzi ze stanu wysokiego

na niski. Oznacza to, że przerzutnik reaguje na opadające zbocze sygnału. Aby to osiągnąć łączymy ze sobą szeregowo dwa przerzutniki RS sterowane

wejściem synchronizującym z tym zastrzeżeniem, że pierwszy przerzutnik synchronizowany jest sygnałem E a drugi jego zaprzeczeniem ~E. Dzięki

temu zabiegowi na wyjściu drugiego przerzutnika pojawia się sygnał z przesunięciem polowy okresu taktu zegara. Całą idee można zrozumieć

obserwując układ:

Aby lepiej zobrazować funkcje fragmentów układu zakreśliłem je kolorami:

RS

RS

synchronizacja

synchronizacja

~S

~S

~R

~R

Sposób działanie tego przerzutnika pokazuje tabelka:

R

S

C

Q

~Q

~q

0

0

0

q

~q

q

-1

~q

-1

0

1

0

q

~q

q

-1

~q

-1

1

0

0

q

~q

q

-1

~q

-1

1

1

0

q

~q

q

-1

~q

-1

0

0

1

q

-1

~q

-1

q

-1

~q

-1

0

1

1

q

-1

~q

-1

1

0

1

0

1

q

-1

~q

-1

0

1

1

1

1

q

-1

~q

-1

Stan zabroniony

Stan zabroniony

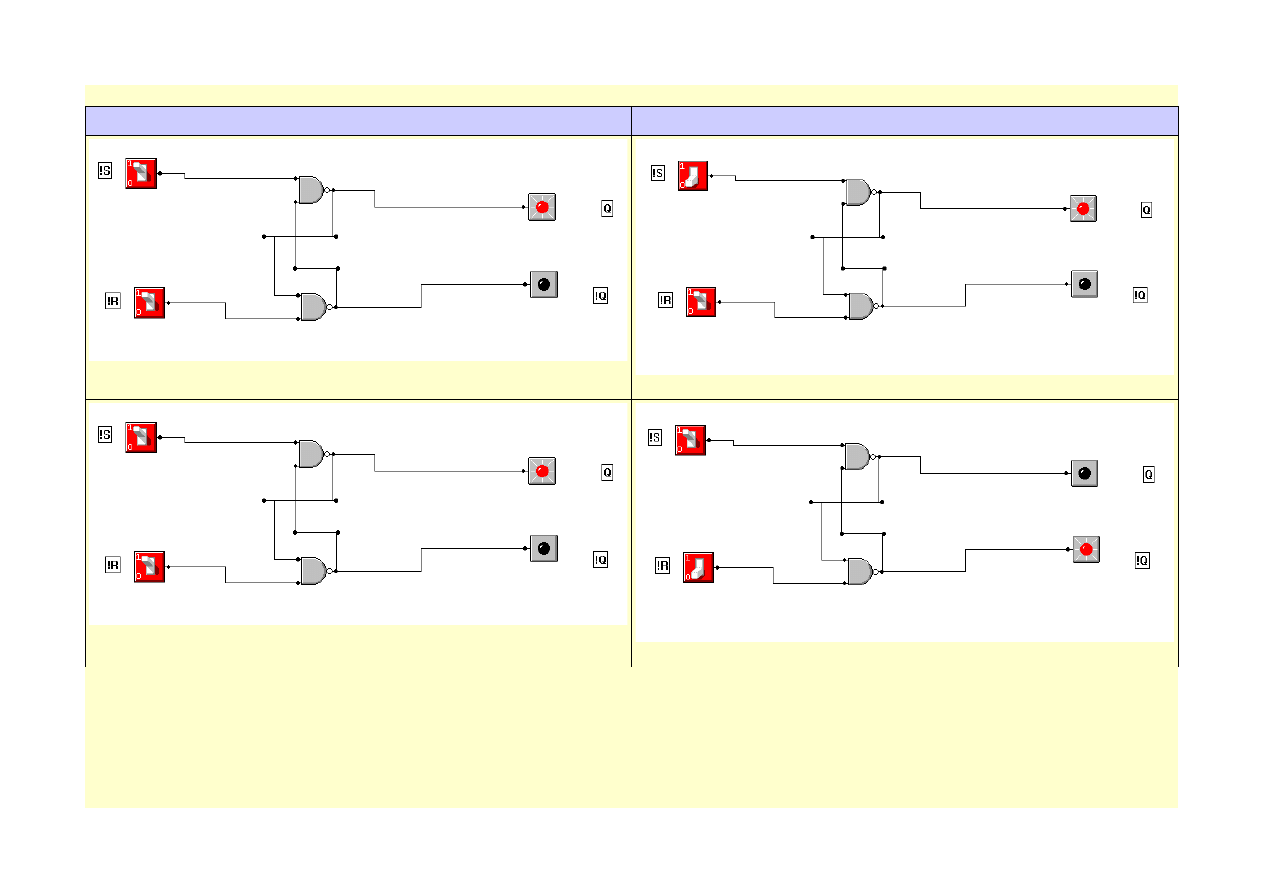

Sprawdzenie poprawności działania układu.

Do analizy układu skorzystałem z symulatora programu multimedia logic. W tabelce przedstawiono układ przed zmianą sygnałów wejściowych

i po tej zmianie:

Stan przed zmianą

Stan po zmianie 1

Stan po zmianie 2

Mimo iż SET = 1 układ nie reaguje bo

ENABLE = 0.

Mimo iż SET = 1 i ENABLE = 1 układ nie

reaguje.

Układ zareagował na zbocze opadające.

Mimo iż RESET = 1 układ nie reaguje bo

ENABLE = 0.

Mimo iż RESET = 1 i ENABLE = 1 układ nie

reaguje.

Układ zareagował na zbocze opadające.

Symulacja pokazuje, że przedstawiony układ działa poprawnie.

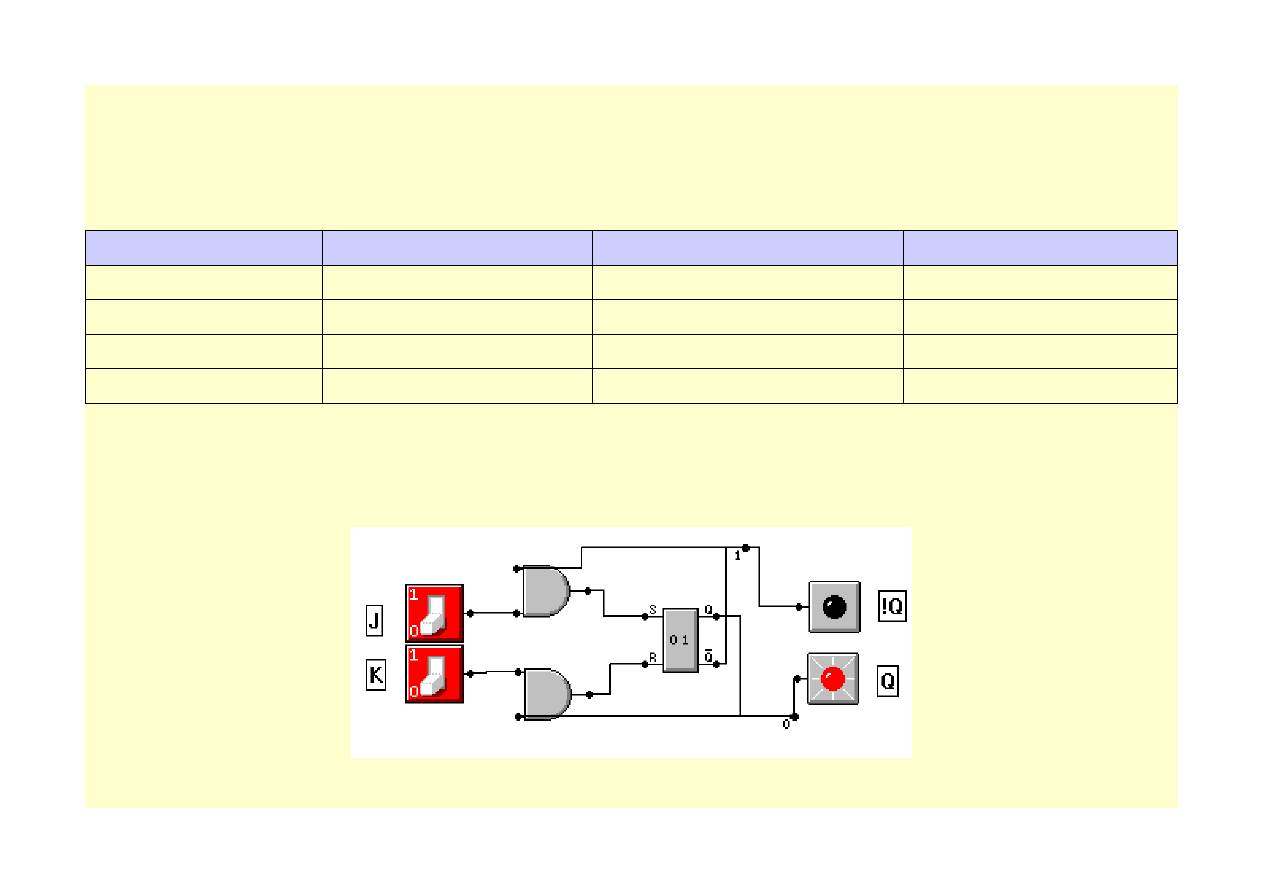

Zadanie 5

Zbudować i sprawdzić działanie przerzutnika JK master-slave (bramki NAND)

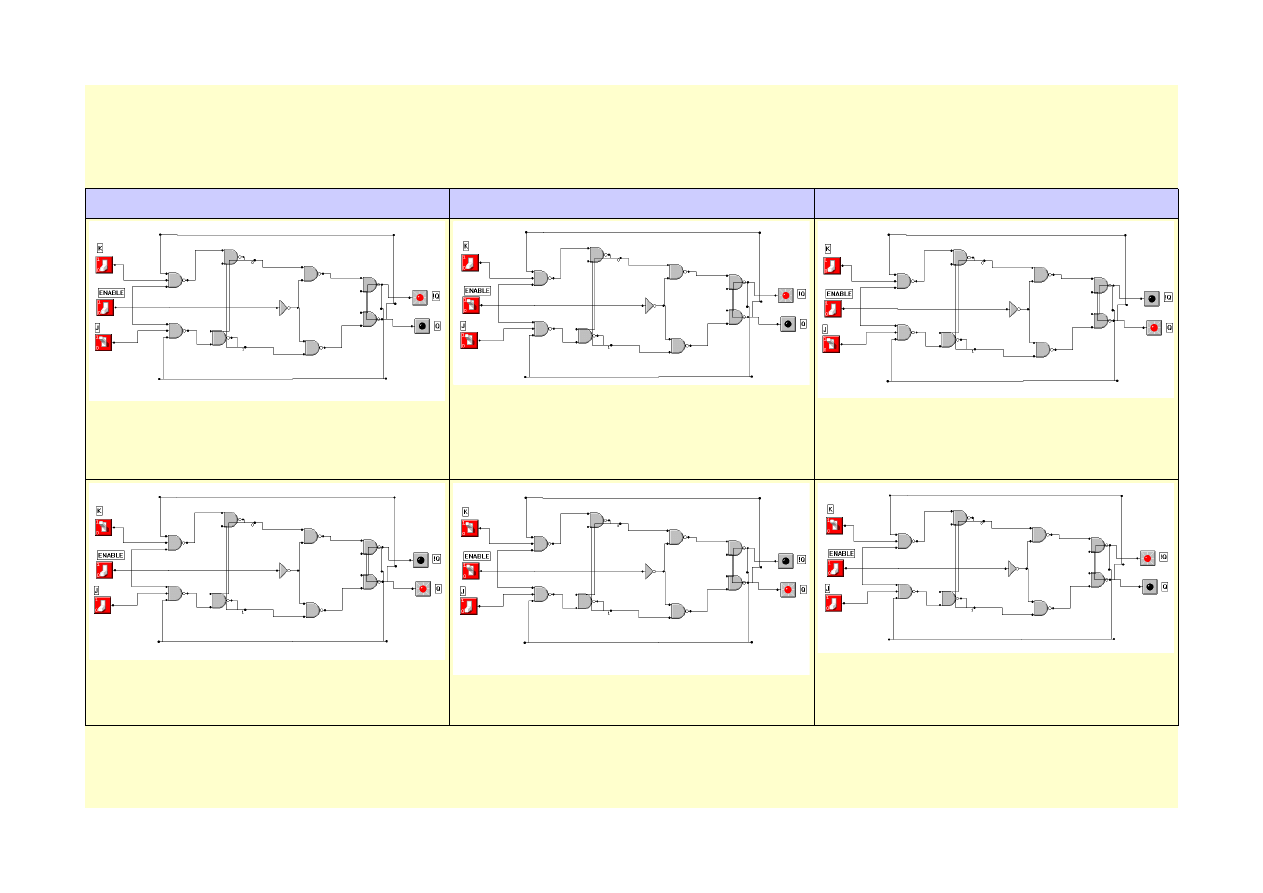

Idea działania przerzutnika JK master-slave łączy w sobie cechy przerzutnika JK i przerzutnika RS master-slave. Przerzutnik JK to przerzutnik

synchroniczny który działa według poniższej tabeli:

J

K

Q

~Q

0

0

Q

-1

~Q

-1

1

0

1

0

0

1

0

1

1

1

~Q

-1

Q

-1

Działa on niemal identycznie do przerzutnika RS, z tą jedną różnicą, że przy danych wejściowych 1,1 przerzutnik typu JK nie przebiera

błędnego stanu. W takim przypadku przerzutnik JK przechodzi to stanu odwrotnego do tego w którym się obecnie znajduje. Ten efekt wynika z

budowy przerzutnika JK. Jest on zbudowany z przerzutnika typu RS z którego wyjść poprowadzono przewody na bramki AND (lub NAND – w

zalesionych od realizacji) znajdujące się przed wejściami tego przerzutnika RS. Schematycznie wygląda to tak:

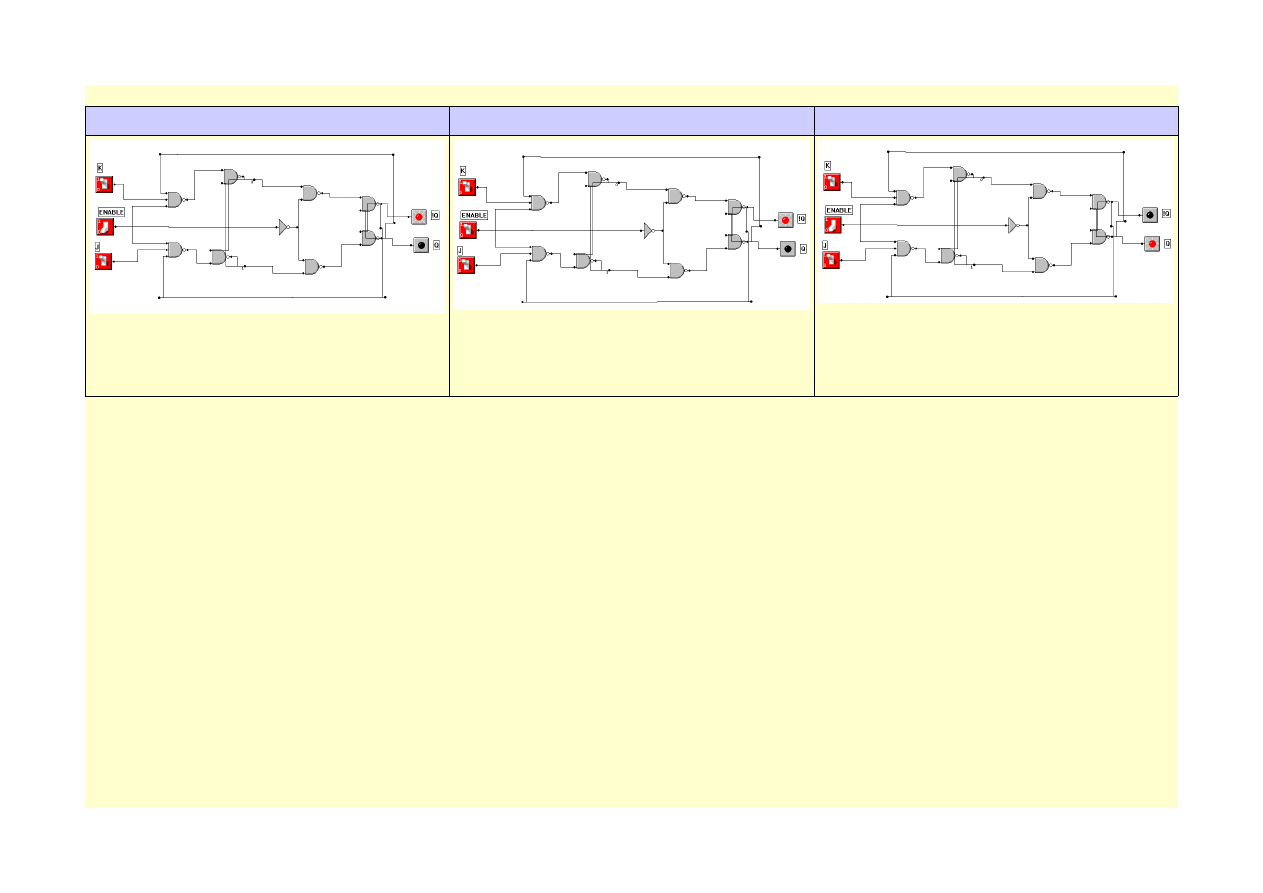

Jeżeli tak przemyślane przerzutniki ułożymy w konfiguracji Slave-Master (tzn. ustawimy je szeregowo i zsynchronizujemy zegarem, przy

zachowaniu warunku, że slave jest synchronizowany zanegowanym sygnałem synchronizującym mastera) otrzymamy następujący układ:

Poniżej przedstawiłem ten sam układ z zaznaczonymi fragmentami układu i ich funkcjami.

Przerzutnik RS

Przerzutnik RS

Synchronizacja

slave'a

Synchronizacja

mastera

Sprzężenie charakterystyczne dla JK

Sprzężenie charakterystyczne dla JK

Sprawdzenie poprawności działania układu.

Do analizy układu skorzystałem z symulatora programu multimedia logic. W tabelce przedstawiono układ przed zmianą sygnałów wejściowych

i po tej zmianie:

Stan przed zmianą

Stan po zmianie 1

Stan po zmianie 2

Mimo iż J = 1 układ nie reaguje bo

ENABLE = 0.

Mimo iż J = 1 i ENABLE = 1 układ nie reaguje. Układ zareagował na zbocze opadające.

Mimo iż K = 1 układ nie reaguje bo

ENABLE = 0.

Mimo iż K = 1 i ENABLE = 1 układ nie reaguje. Układ zareagował na zbocze opadające.

Stan przed zmianą

Stan po zmianie 1

Stan po zmianie 2

Mimo iż J = 1 i K = 1 układ nie reaguje bo

ENABLE = 0.

Mimo iż J = 1 i K = 1 i ENABLE = 1 układ nie

reaguje.

Układ zareagował na zbocze opadające.

(przerzutnik zmienił stan na przeciwny)

Symulacja pokazuje, że przedstawiony układ działa poprawnie.

Wnioski\uwagi:

–

korzystając z elementarnych składników (bramek) jesteśmy w stanie budować całą paletę przerzutników o różnych właściwościach/

–

w trakcie badania lub projektowania układu warto traktować mniejsze fragmenty jako oddzielny układ mający spełniać określoną funkcję.

Często okazuje się, że przy budowaniu bardziej skomplikowanych układów ich całe fragmenty są już nam znane z innych rozwiązań. (jak w

przypadku układu JK-MS korzystającego z JK, RS, oraz RS-MS)

–

w przypadku gdy chcemy zanalizować przerzutnik o trzech wejściach, którego zachowanie zależy od jego poprzedniego stanu używanie tabelki

staje się niewygodne. Ilość kombinacji do zbadania staje się zbyt duża aby robić to szybko. W takim przypadku wygodniejszą formą testowania

jest symulacja komputerowa.

–

We wszystkich przykładach zajmowaliśmy się przechowywaniem bardzo małej porcji informacji.

Wyszukiwarka

Podobne podstrony:

Jaworek Michal sprawozdanie uklady cyfrowe liczniki

Jaworek Michal sprawozdanie uklady cyfrowe dodawanie

Jaworek Michal sprawozdanie wzmacniacz operacyjny

Miernictwo 11 Michała , SPRAWOZDANIE

Sprawozdanie - Przerzutniki bistabilne, Studia, PEiTC, Sprawozdania

Sprawozdanie Przerzutniki

sprawozdanie chemia michał, Budownictwo UZ semestr I , II, Chemia budowlana, Sprawozdania od Seweryn

SPRAWOZDANIE NR 4 - Michał, pwr-eit, FIZYKA, LABORATORIUM[moje], Sprawozdania

PRZERZUTNIKI SYNCHRONICZNE, Sprawozdania

instrukcje do sprawozdań, cw8 przerzutniki, Laboratorium

Sprawozdania materialoznastwo, MLODY, KOSTECKI MICHAŁ

WEiP-MichalTurzynski-lab3, Sprawozdanie 3 (WEiP-2009)

sprawozdanie2, Michał Wilczak gr

sprawozdanie2, Michał Wilczak gr

Przerzutniki sprawozdanie

sprawozdanie ćw 4, Prz inf 2013, I Semestr Informatyka, Fizyka, [FIZYKA] Laborki, laboratorium stare

Sprawozdanie z ćw. 44, Prz inf 2013, I Semestr Informatyka, Fizyka, [FIZYKA] Laborki, laboratorium s

PrzerzutnikiKonspektKlim, Elektrotechnika AGH, Semestr IV letni 2013-2014, Podstawy Elektroniki, Pod

więcej podobnych podstron