Verilog

1/41

Verilog HDL

a[0]

b[0]

y[0]

a

b

y

cout

HA

a[1]

b[1]

y[1]

a

b

y

FA

cin

cout

a[2]

b[2]

y[2]

a

b

y

FA

cin

cout

a[3]

b[3]

y[3]

a

b

y

FA

cin

cout

y[4]

c[3]

c[2]

c[1]

c[0]

dr inż. Mariusz Kapruziak

mkapruziak@wi.ps.pl

pok. 107, tel. 449 55 44

1. Modelowanie struktury

2/41

1

2

3

4

5

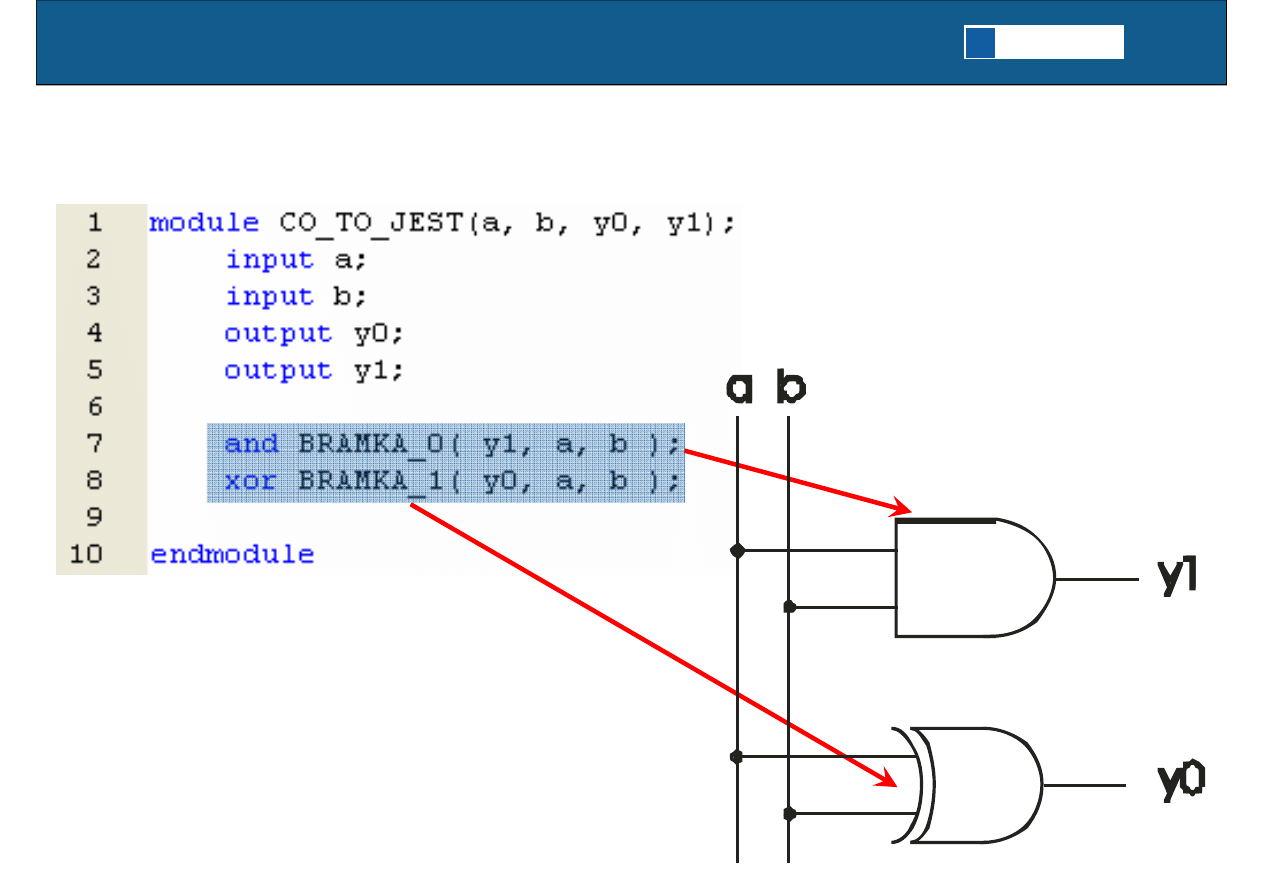

Ogólna struktura kodu

1. Modelowanie struktury

3/41

1

2

3

4

5

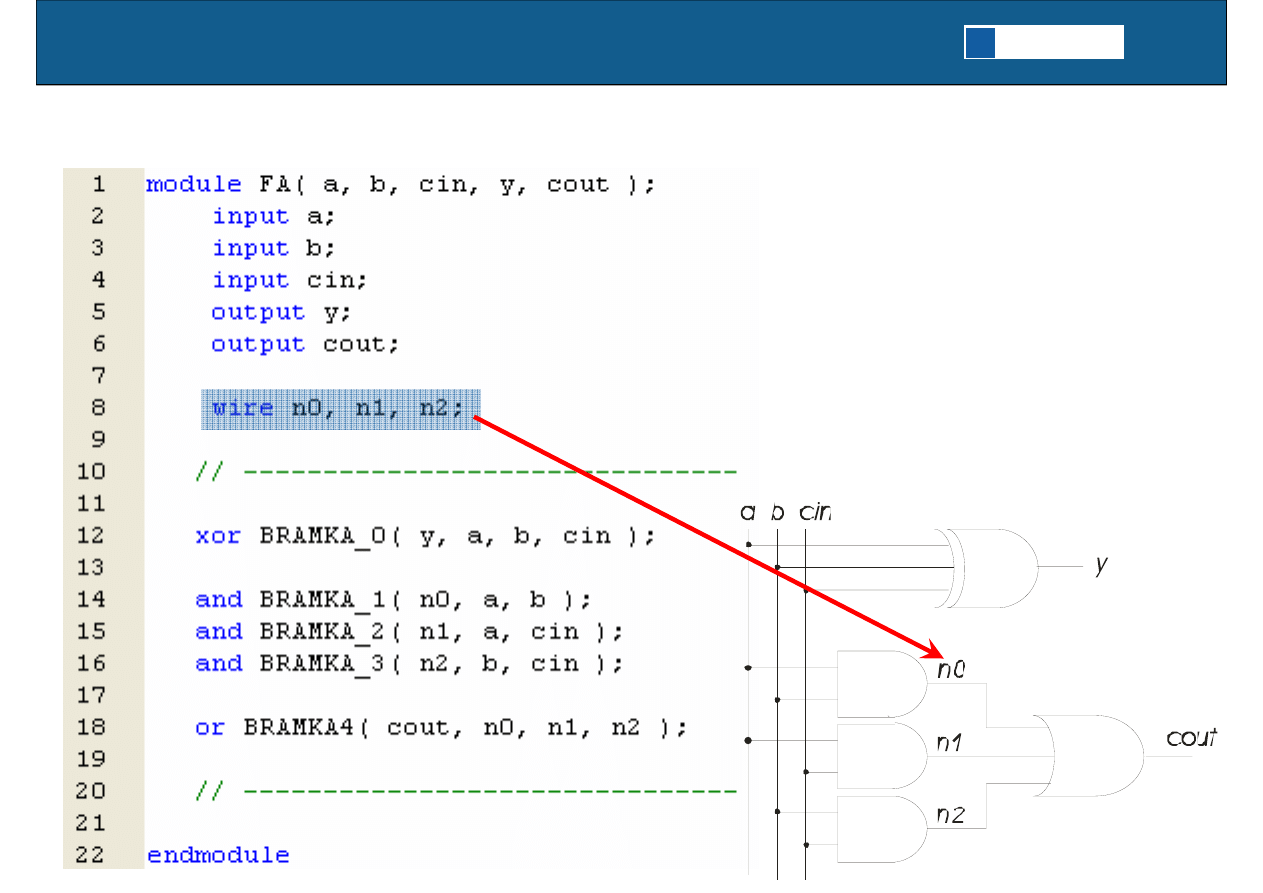

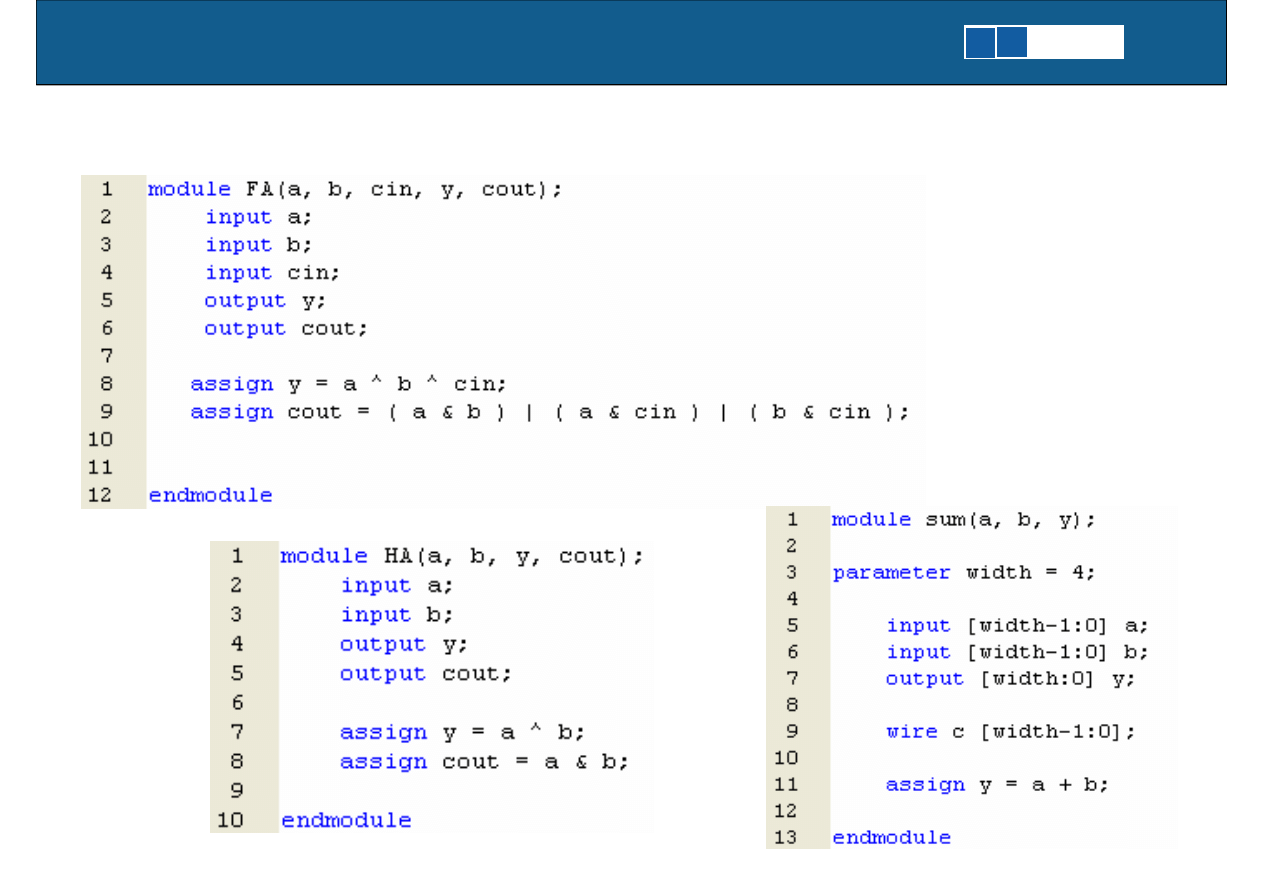

Pełny sumator

1. Modelowanie struktury

4/41

1

2

3

4

5

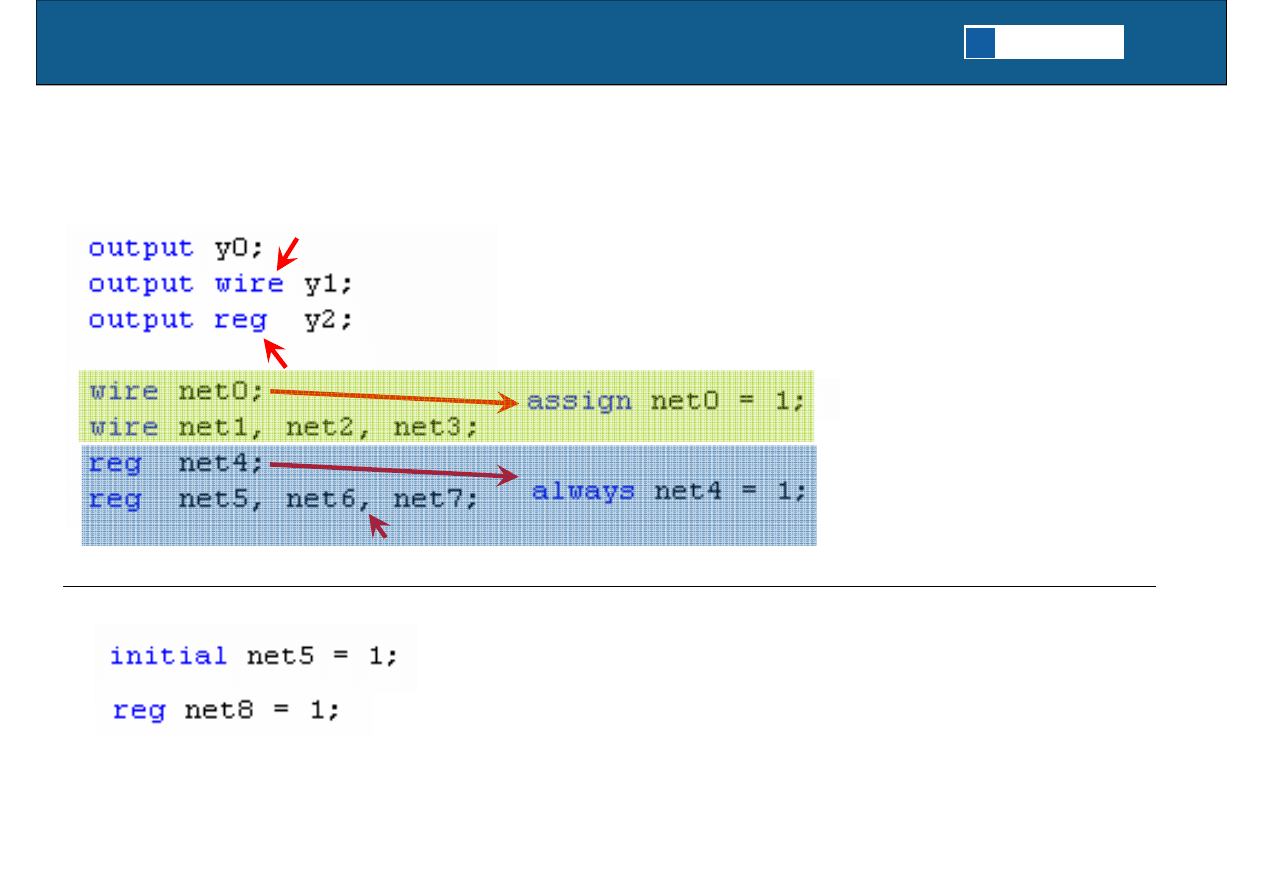

Sygnały: wire/reg, assign/always, initial

Inicjalizacja

1. Modelowanie struktury

5/41

1

2

3

4

5

Konkatenacja

Selekcja części słowa

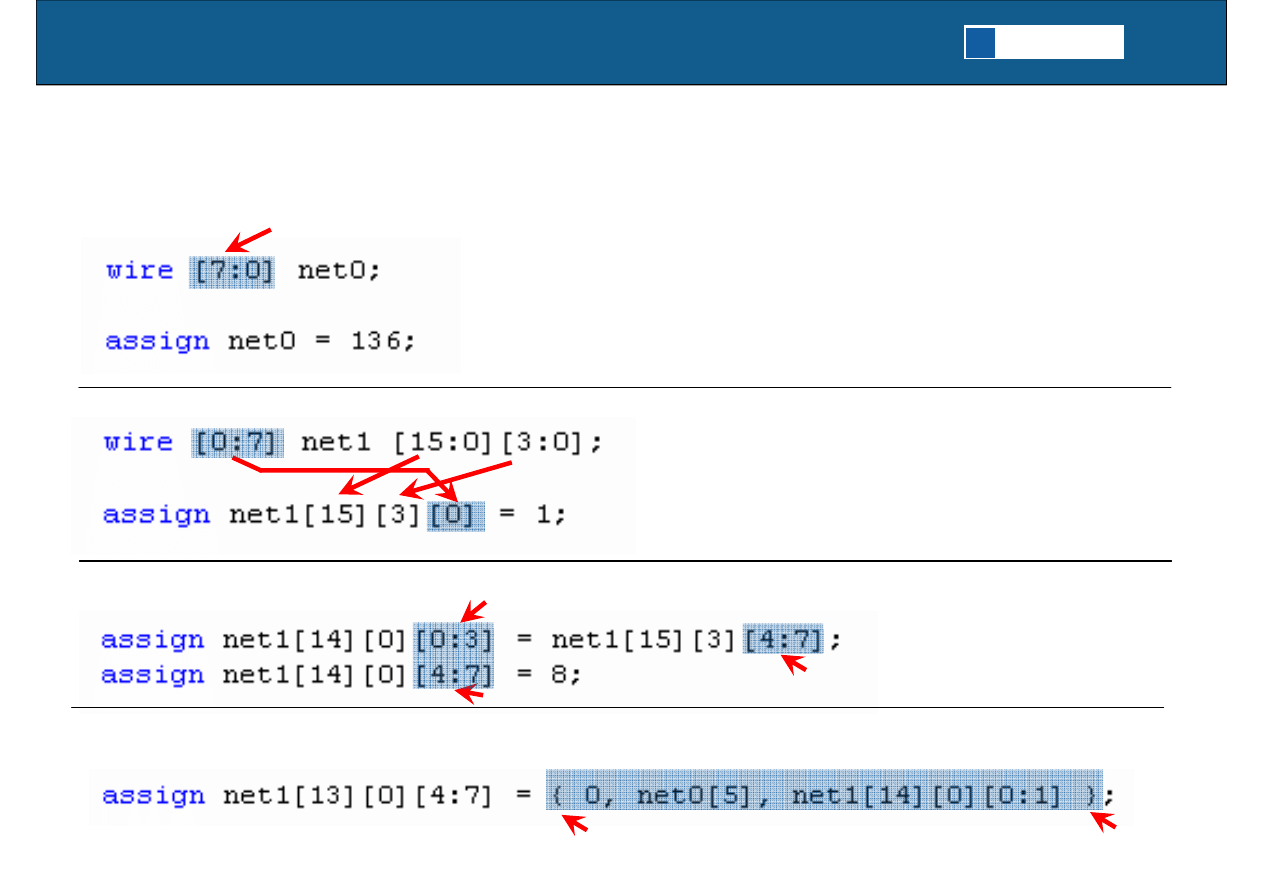

Tablice

Słowo

Słowa, tablice, konkatenacja

1. Modelowanie struktury

6/41

1

2

3

4

5

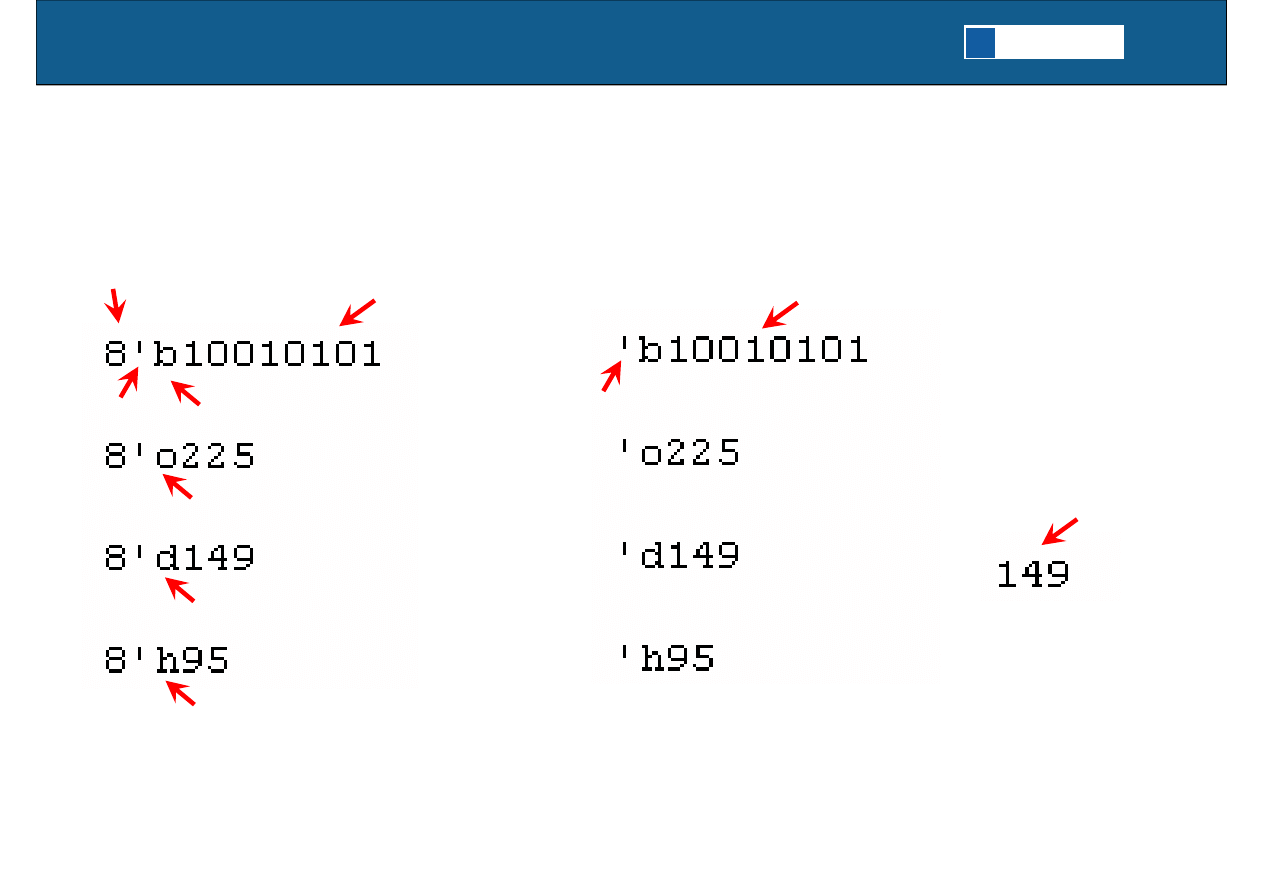

Stałe

Długość słowa /

liczba bitów

Format: b = binarny

Wartość stałej

Format: o = ósemkowy

Format: d = dziesiętny

Format: h = szesnastkowy

Wartość stałej

Wartość stałej

(dziesiętnie)

1. Modelowanie struktury

7/41

1

2

3

4

5

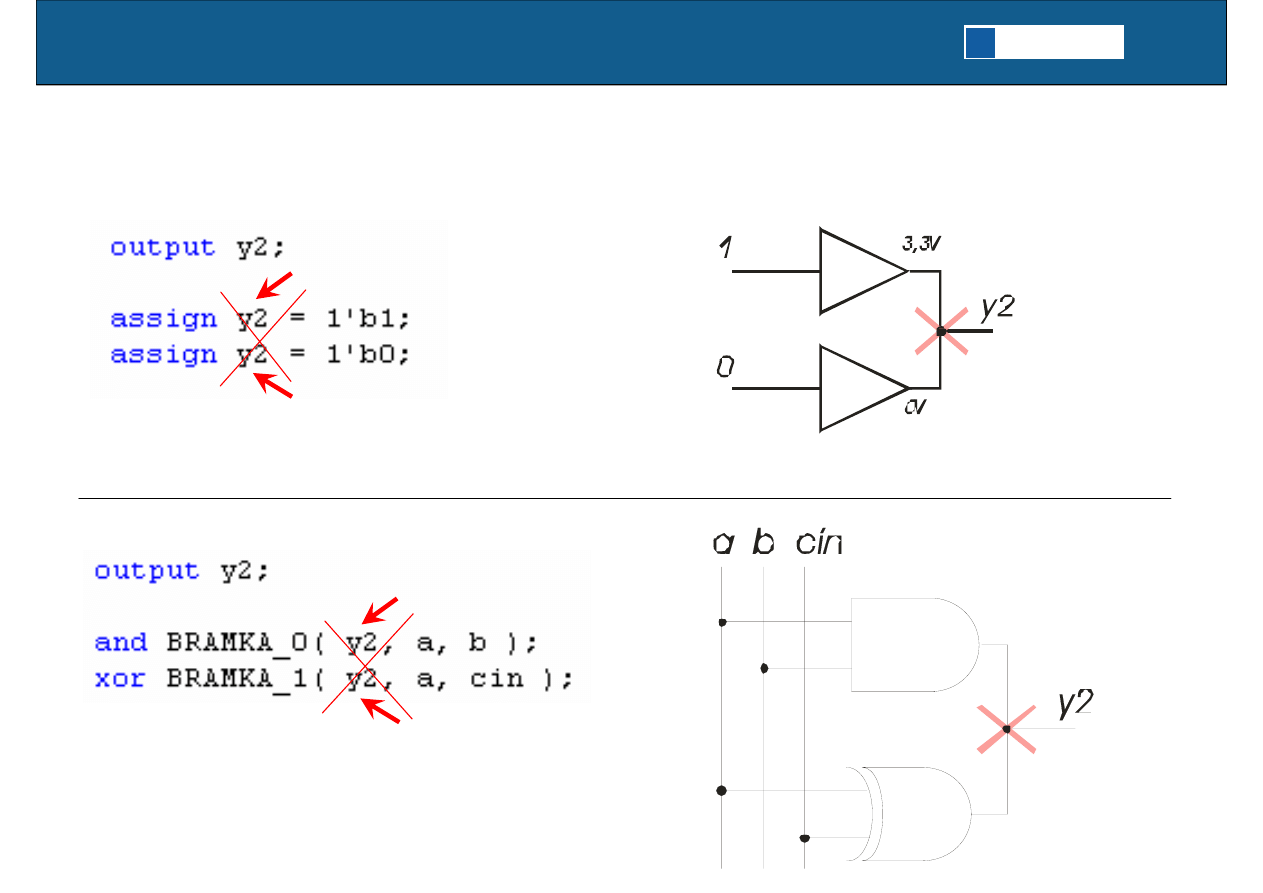

Multiple Driver Error

zwarcie

zwarcie

1. Modelowanie struktury

8/41

1

2

3

4

5

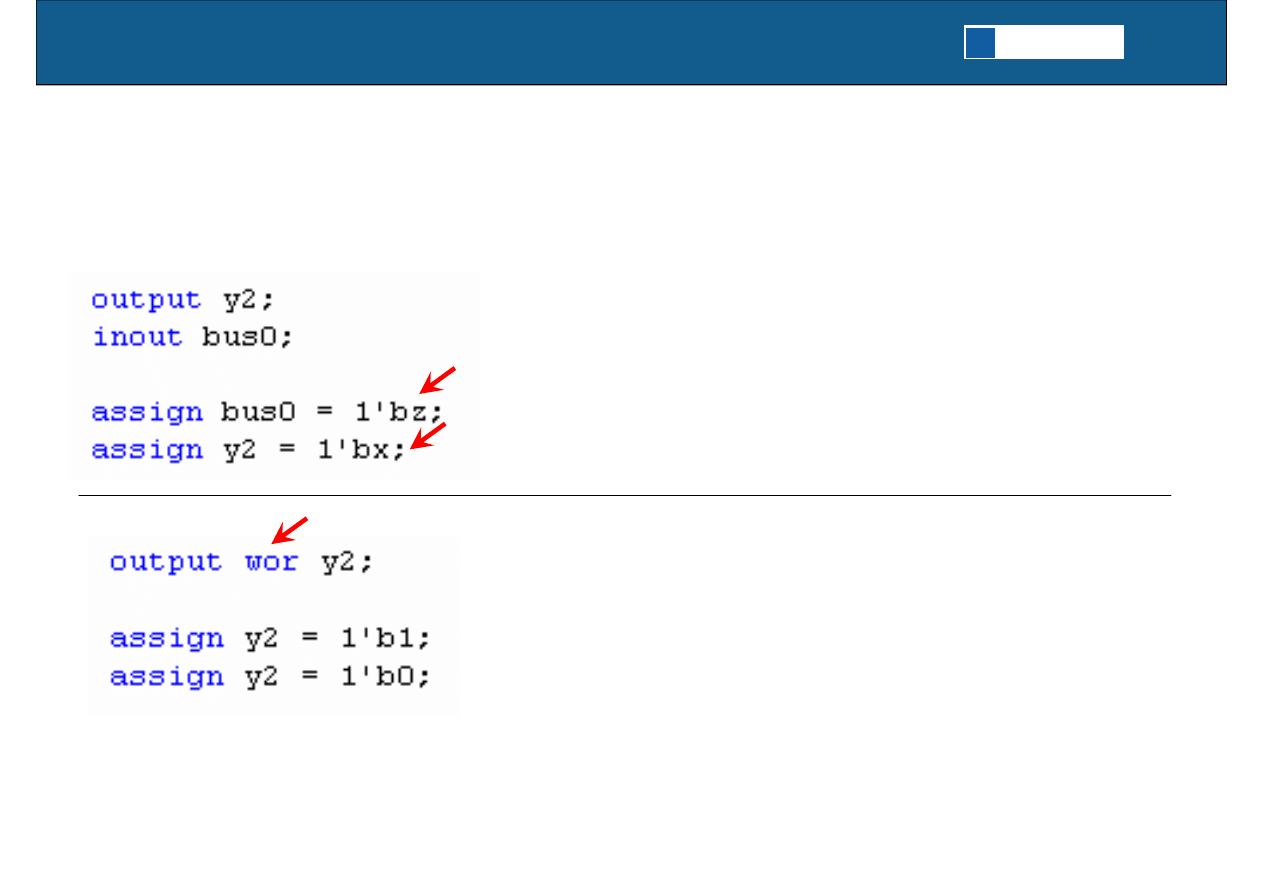

Stałe z, x

Sygnały wand/wor/tri/supply1/supply0

wand/wor

z, x

1. Modelowanie struktury

9/41

1

2

3

4

5

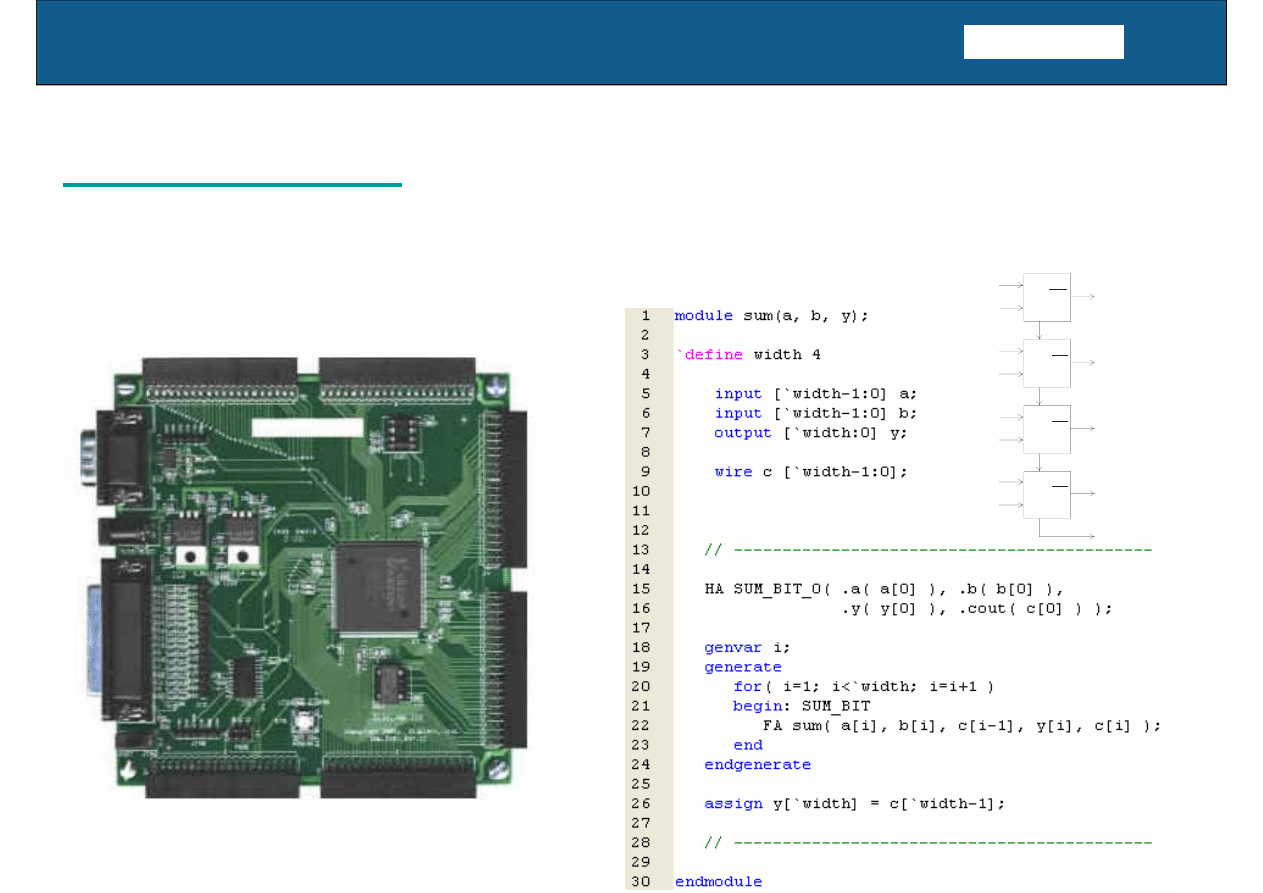

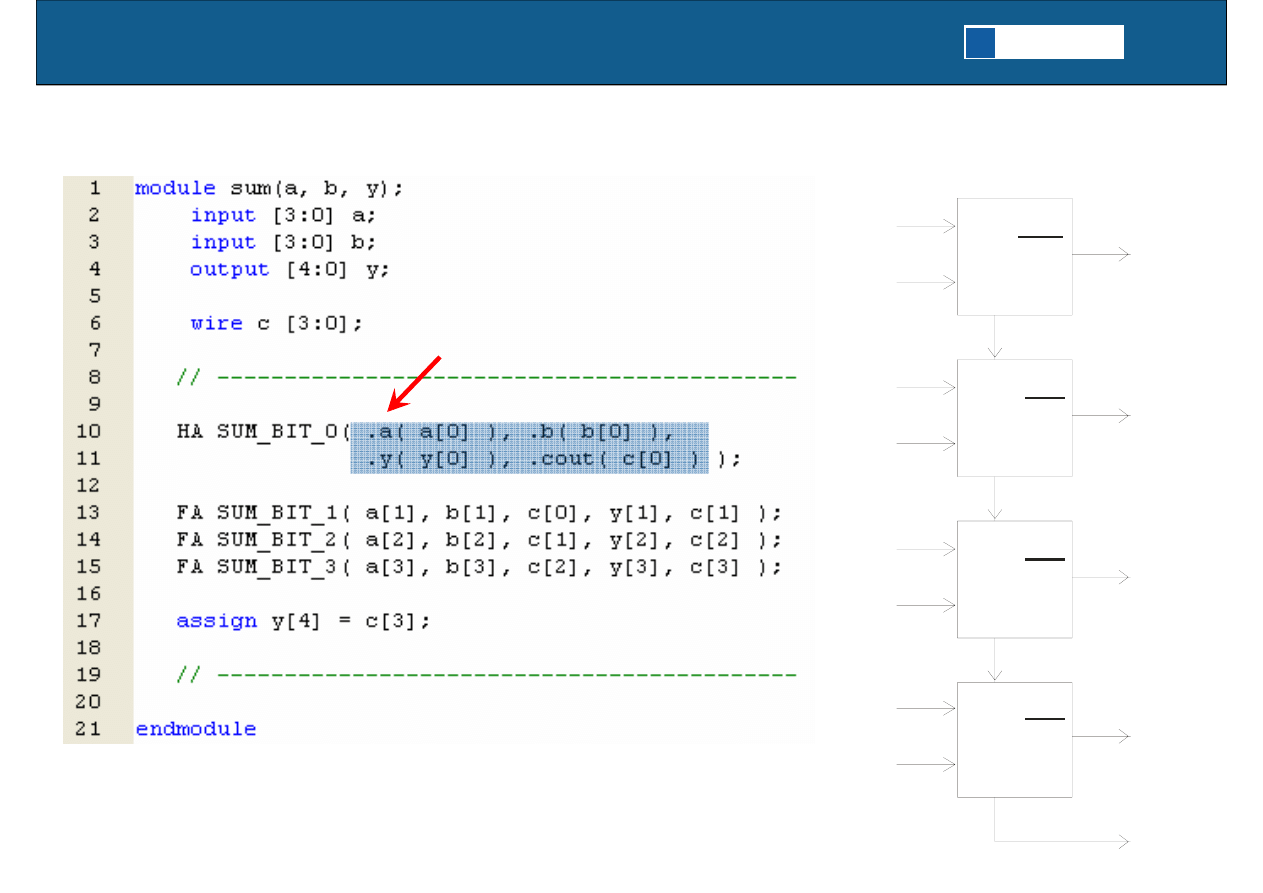

Sumator 4-bit

jawne przypisanie wyprowadzeń

a[0]

b[0]

y[0]

a

b

y

cout

HA

a[1]

b[1]

y[1]

a

b

y

FA

cin

cout

a[2]

b[2]

y[2]

a

b

y

FA

cin

cout

a[3]

b[3]

y[3]

a

b

y

FA

cin

cout

y[4]

c[3]

c[2]

c[1]

c[0]

1. Modelowanie struktury

10/41

1

2

3

4

5

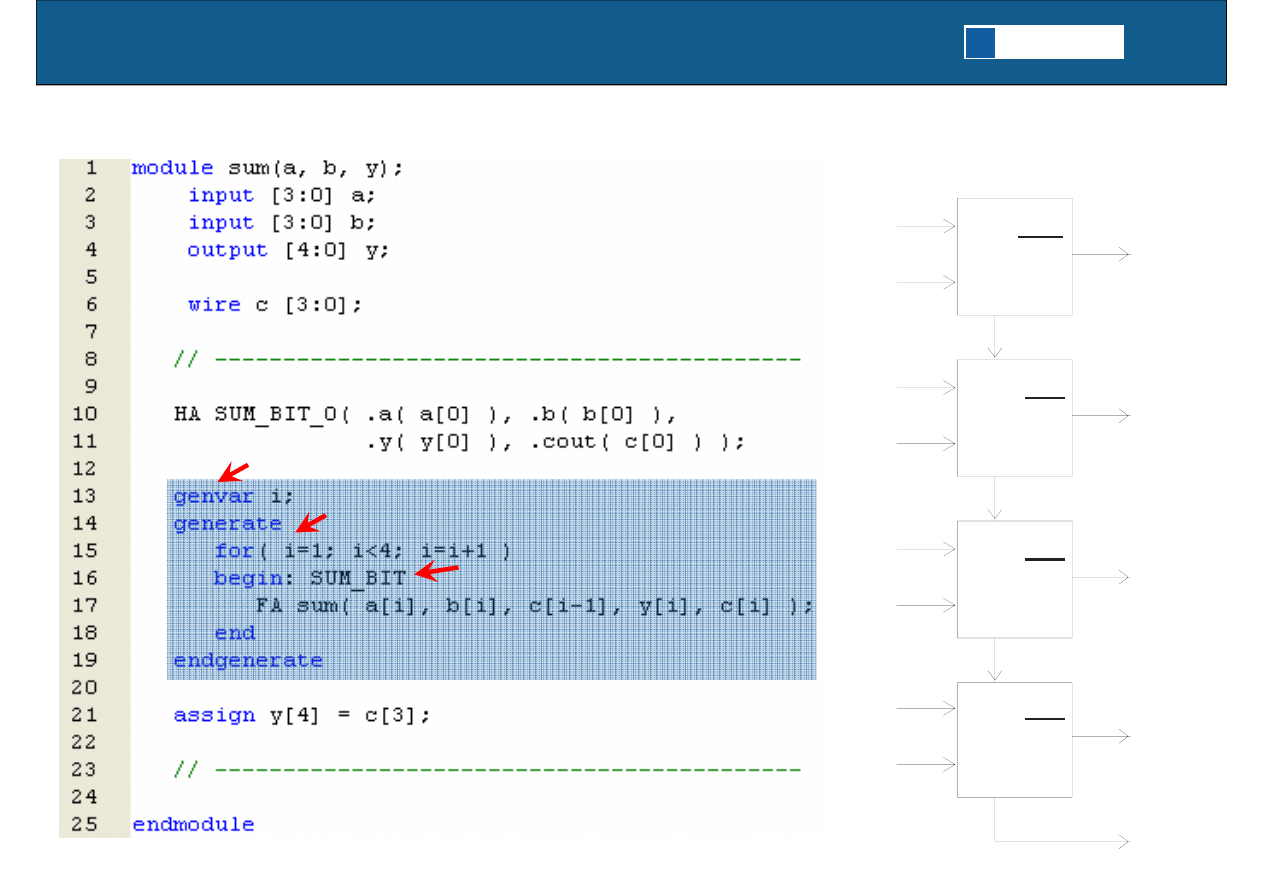

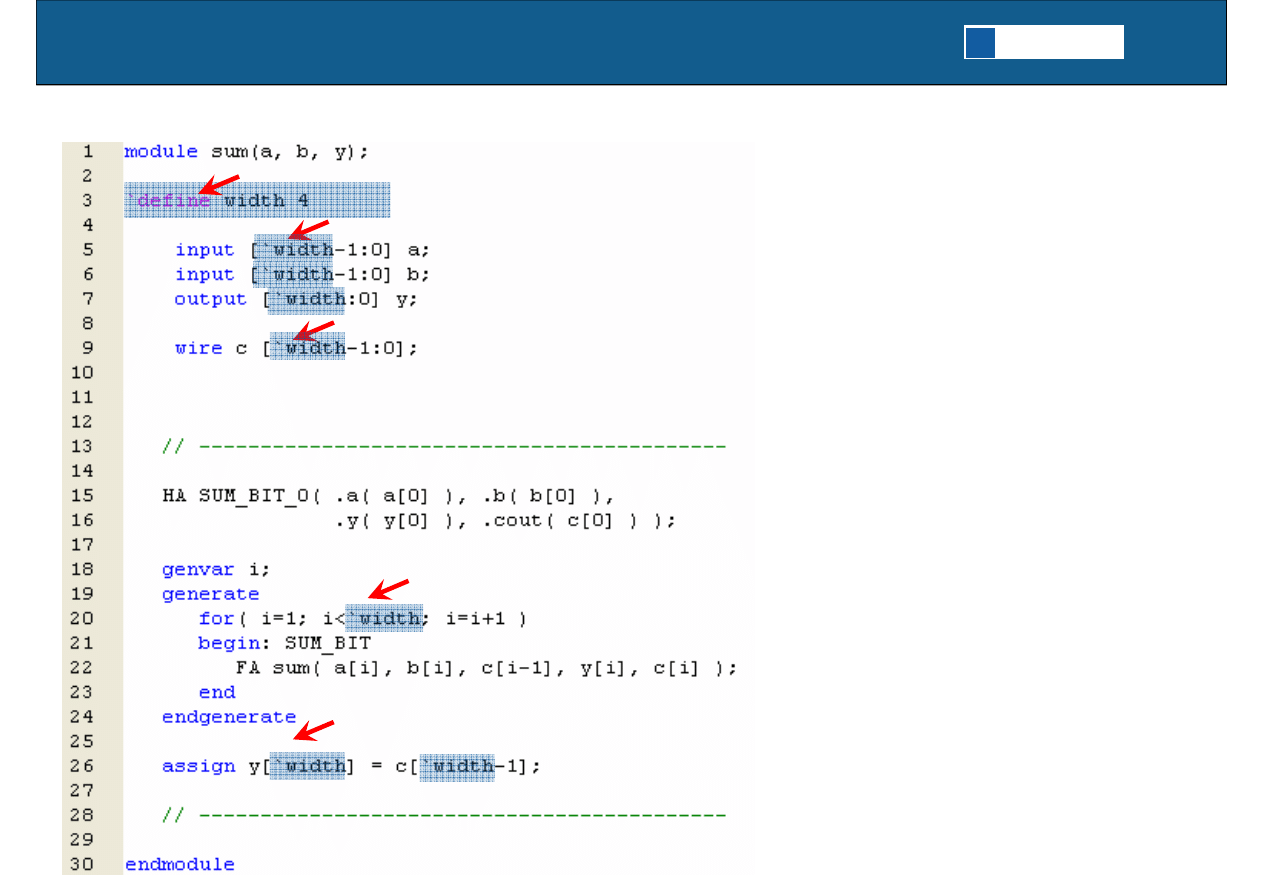

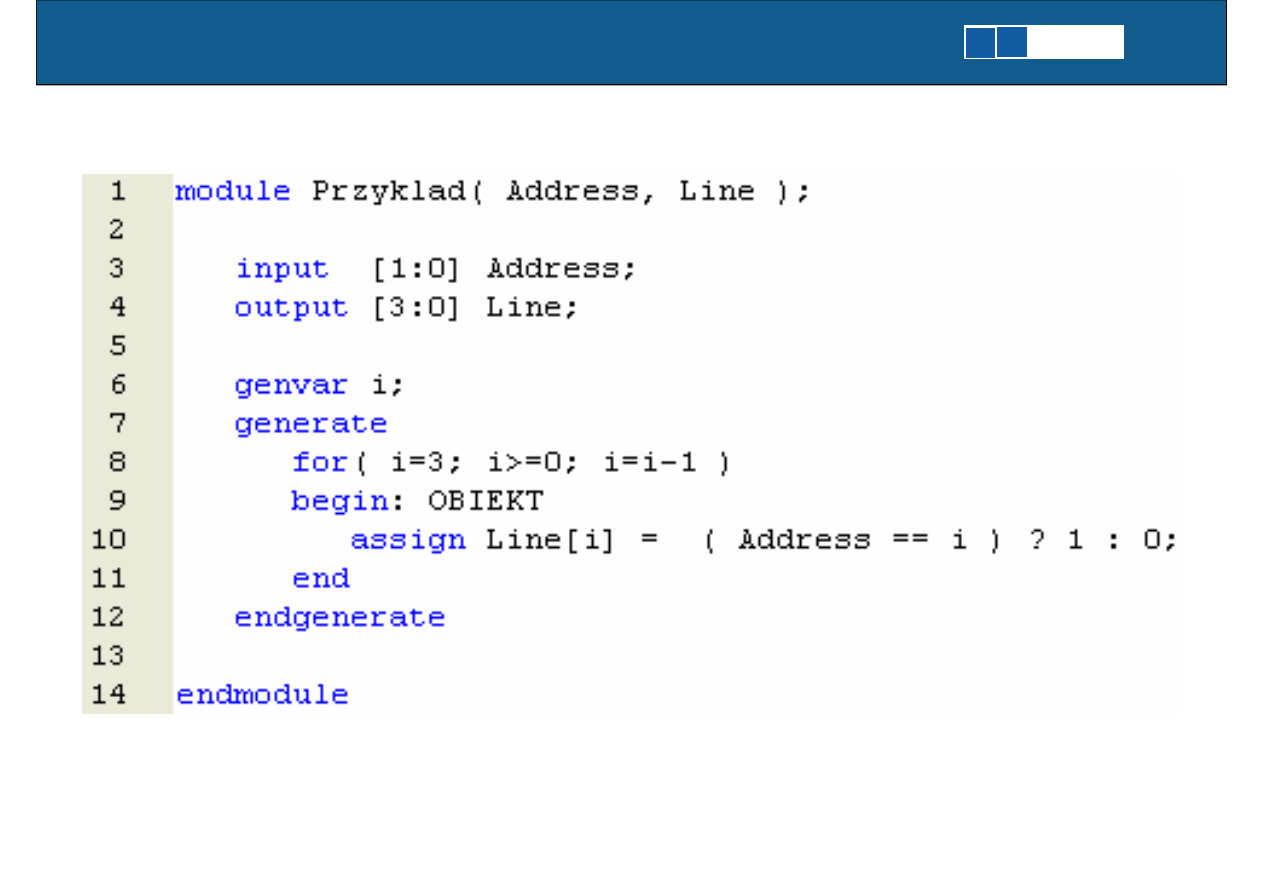

Generate, genvar

a[0]

b[0]

y[0]

a

b

y

cout

HA

a[1]

b[1]

y[1]

a

b

y

FA

cin

cout

a[2]

b[2]

y[2]

a

b

y

FA

cin

cout

a[3]

b[3]

y[3]

a

b

y

FA

cin

cout

y[4]

c[3]

c[2]

c[1]

c[0]

1. Modelowanie struktury

11/41

1

2

3

4

5

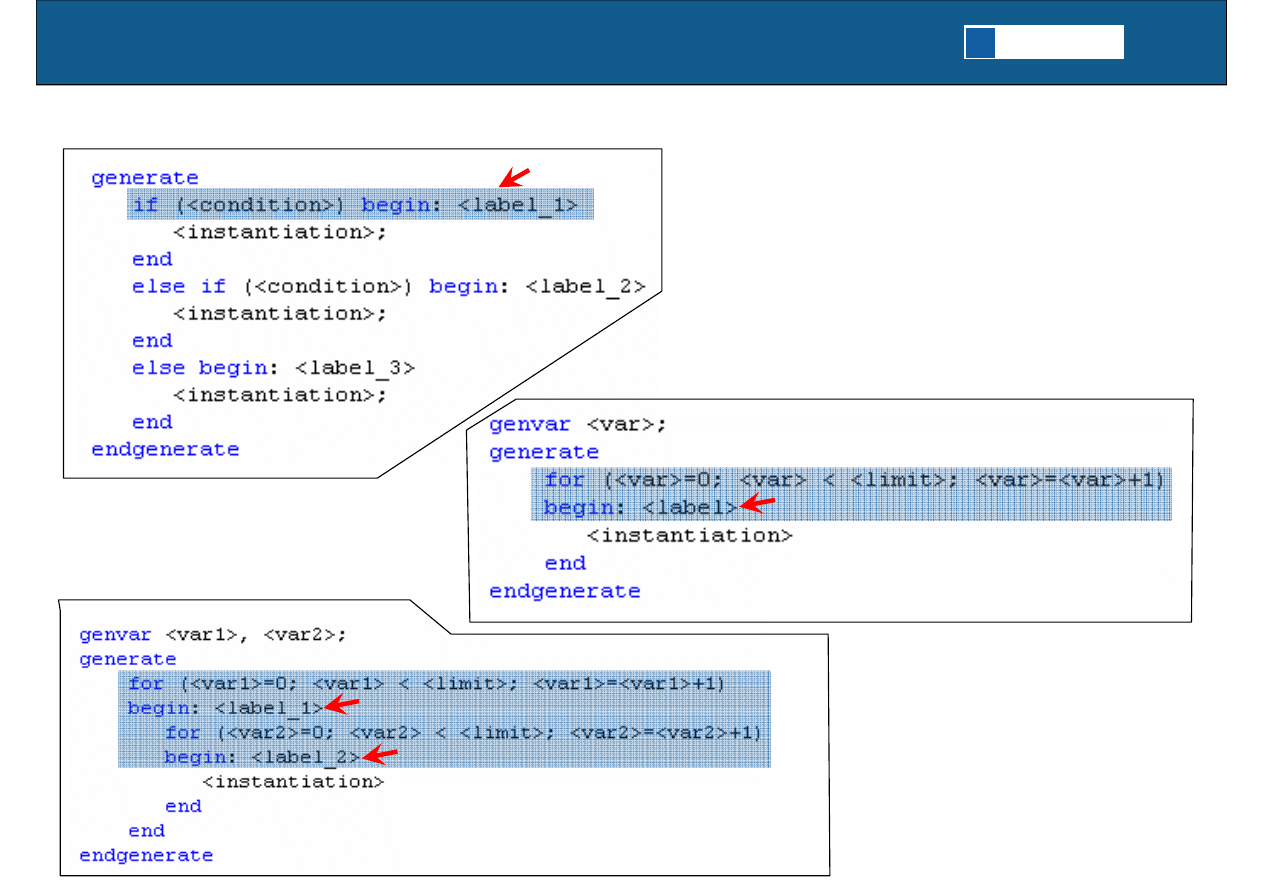

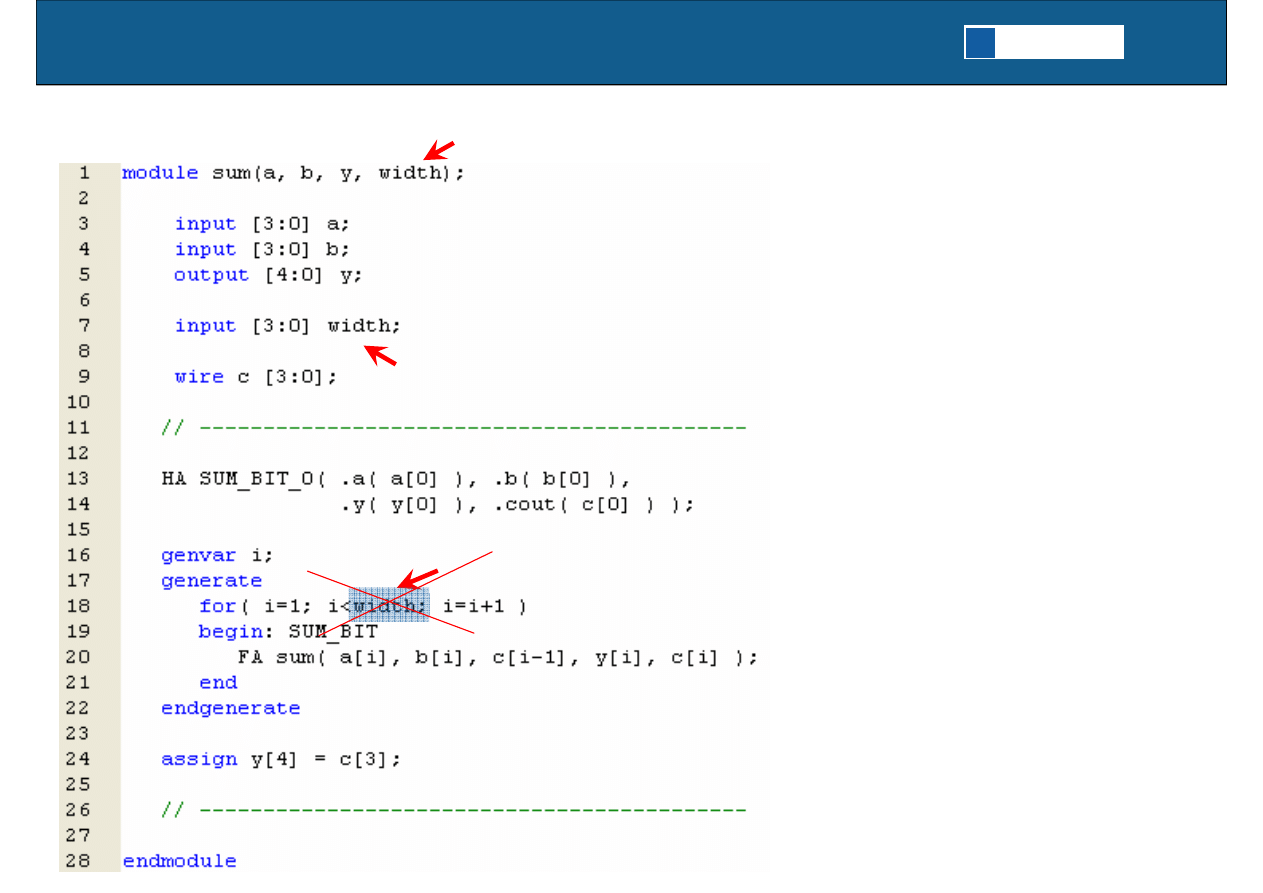

Składnia Generate

Wykorzystanie do bloków

warunkowych

Powielanie bloków

Powielanie bloków,

iteracje zagłębione

1. Modelowanie struktury

12/41

1

2

3

4

5

Kod nie syntezowalny na poziomie logicznym

1. Modelowanie struktury

13/41

1

2

3

4

5

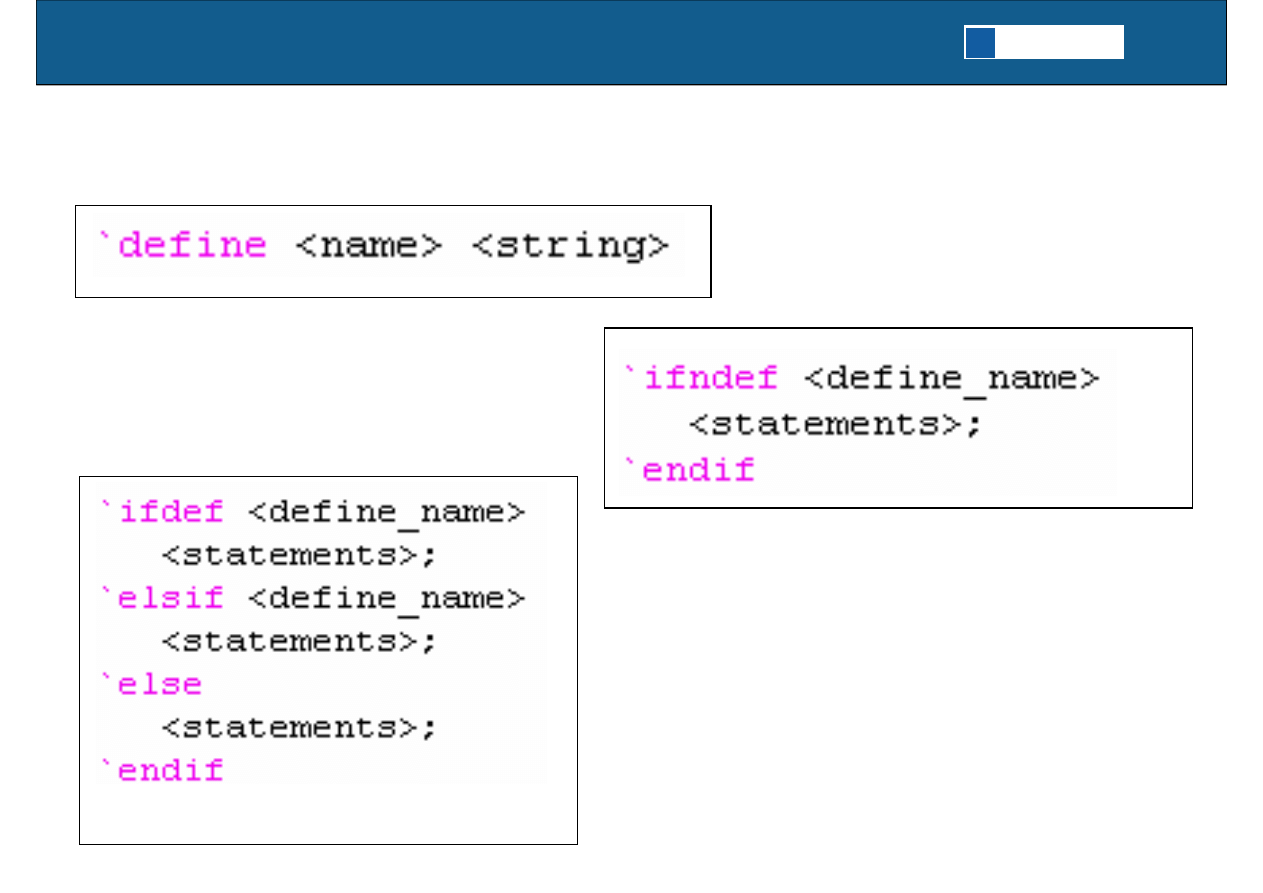

`define

1. Modelowanie struktury

14/41

1

2

3

4

5

Składania define

1. Modelowanie struktury

15/41

1

2

3

4

5

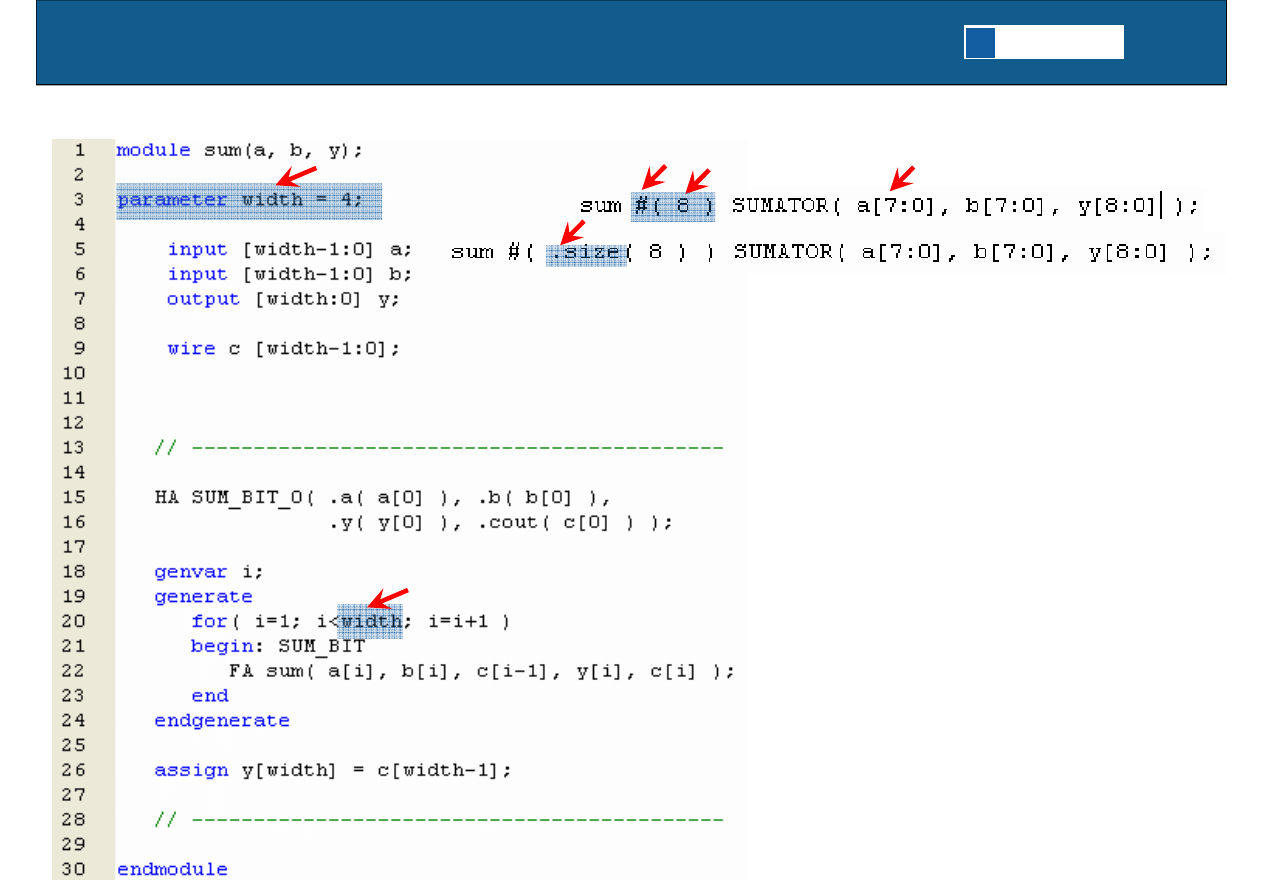

parameter

1. Modelowanie struktury

16/41

1

2

3

4

5

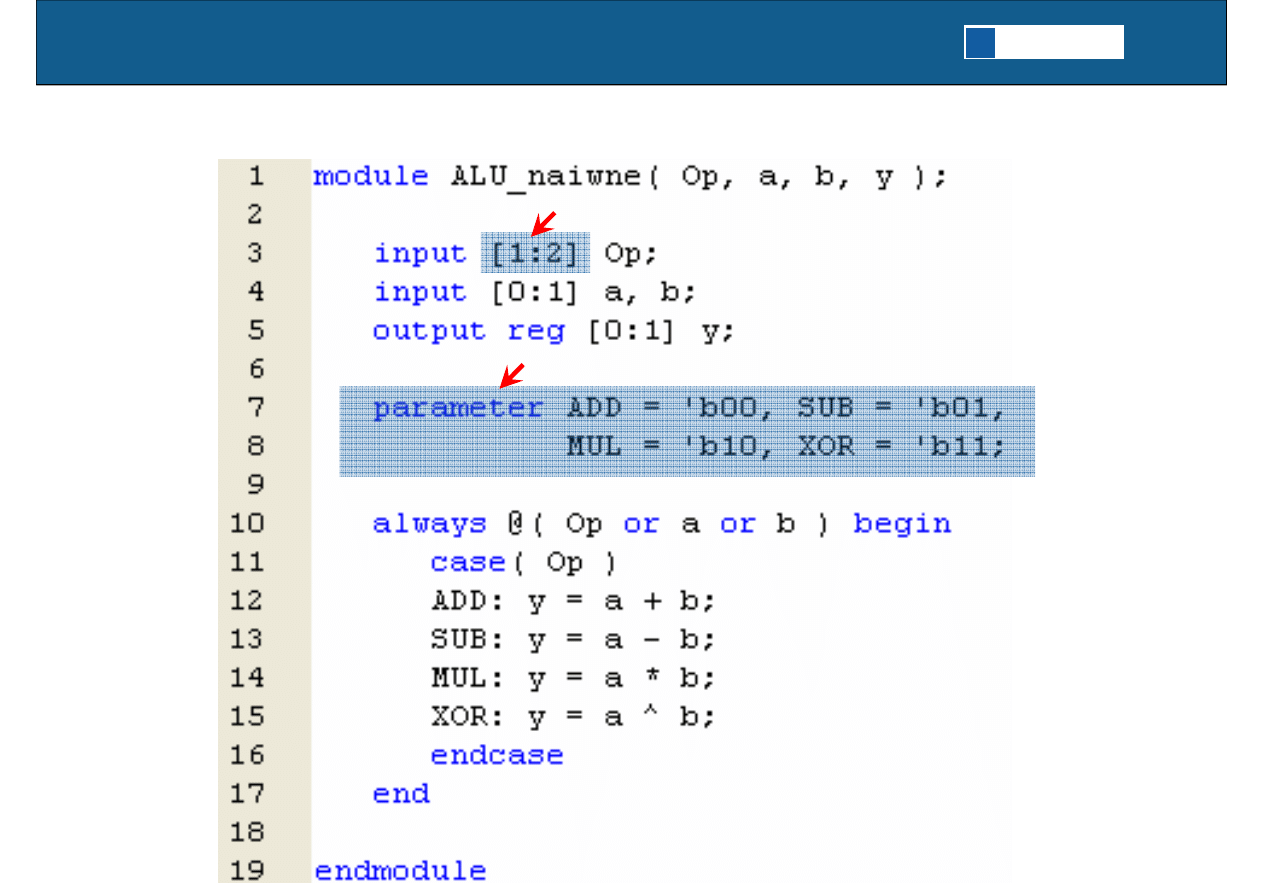

enumeracja

1. Modelowanie struktury

17/41

1

2

3

4

5

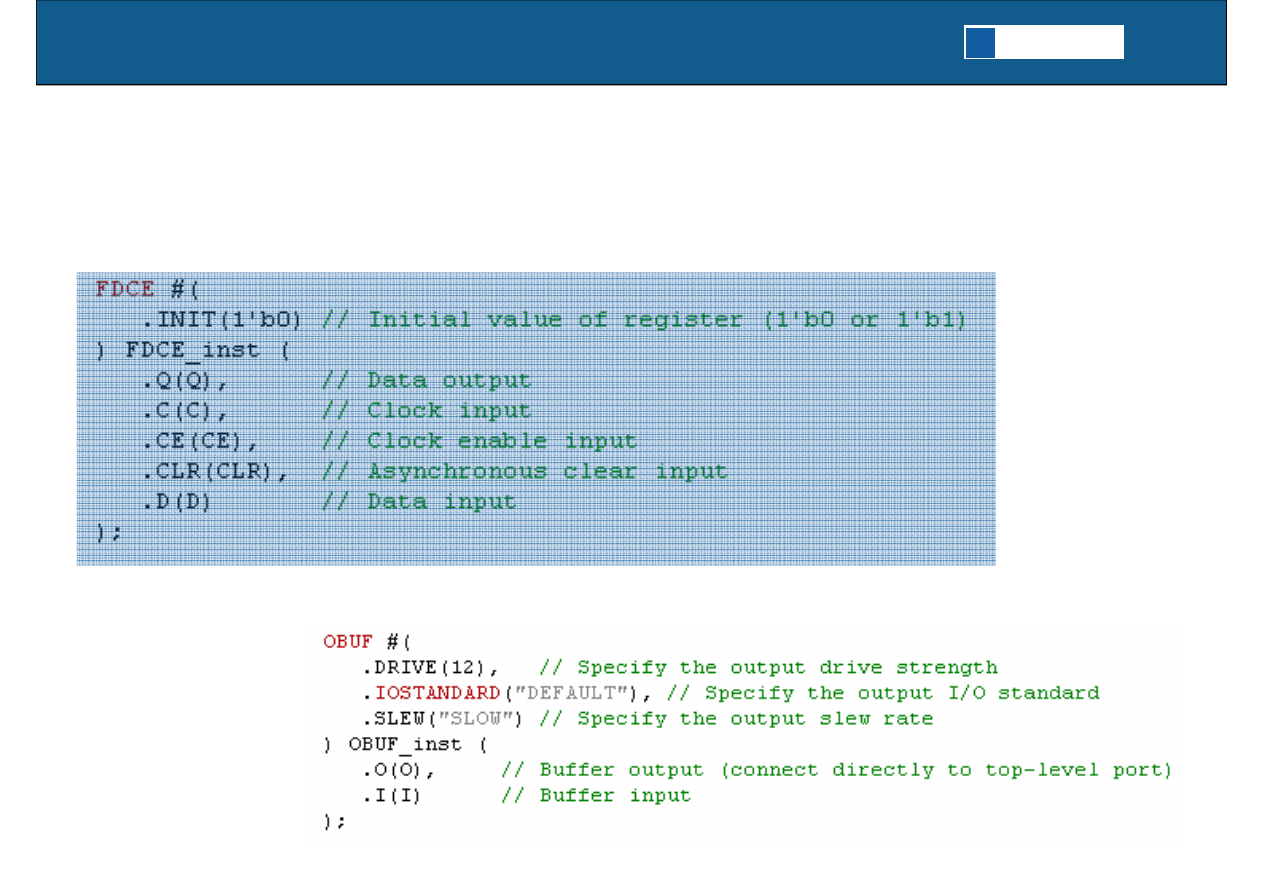

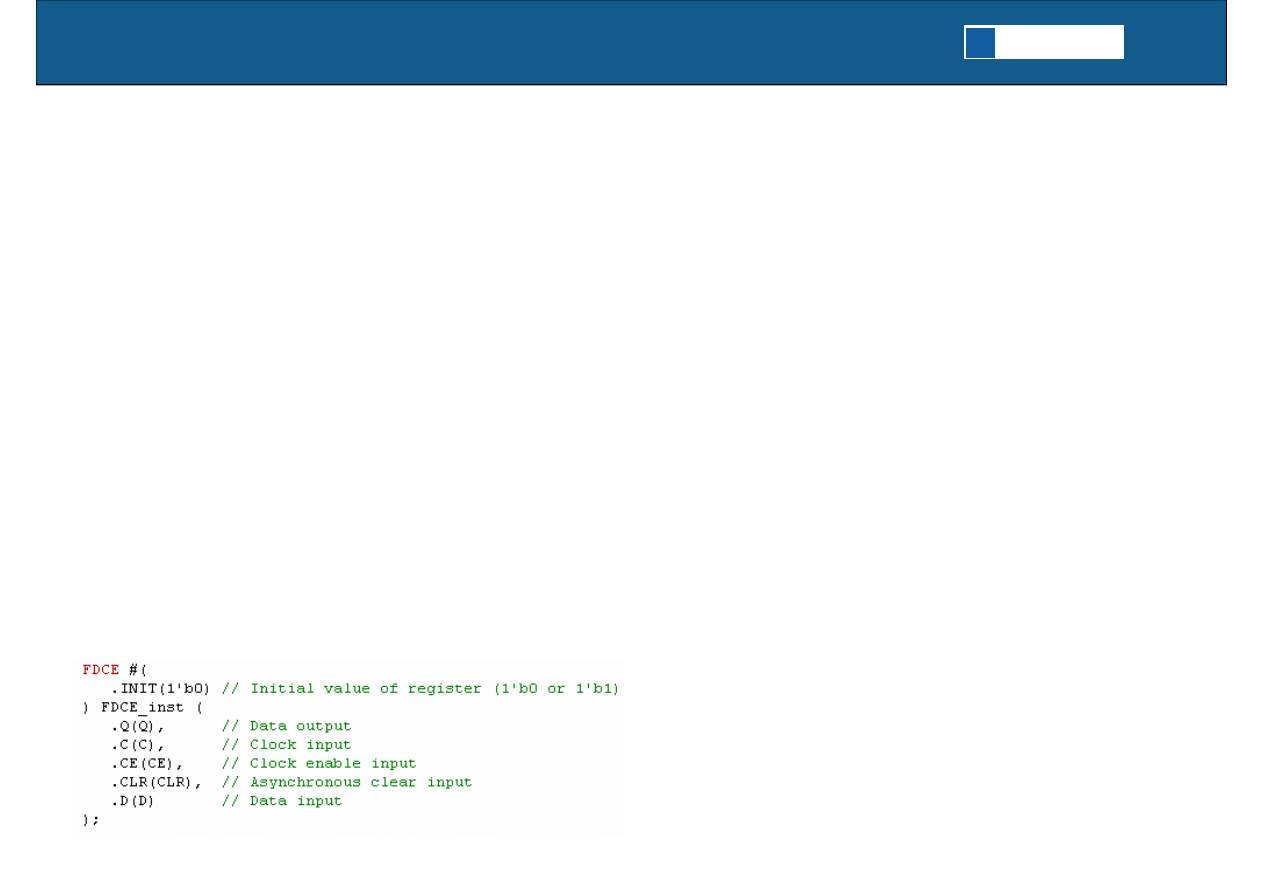

Przykładowe definicje obiektów (rejestr D i bufor 3-st.)

Środowisko Xilinx ISE

1. Modelowanie struktury

18/41

1

2

3

4

5

ZADANIE: dekoder HEX na wyświetlacz 7seg.

Licznik 4 bitowy

?

2. RTL = Register Transfer Level

19/41

1

2

3

4

5

RTL = Register Transfer Level

2. RTL = Register Transfer Level

20/41

1

2

3

4

5

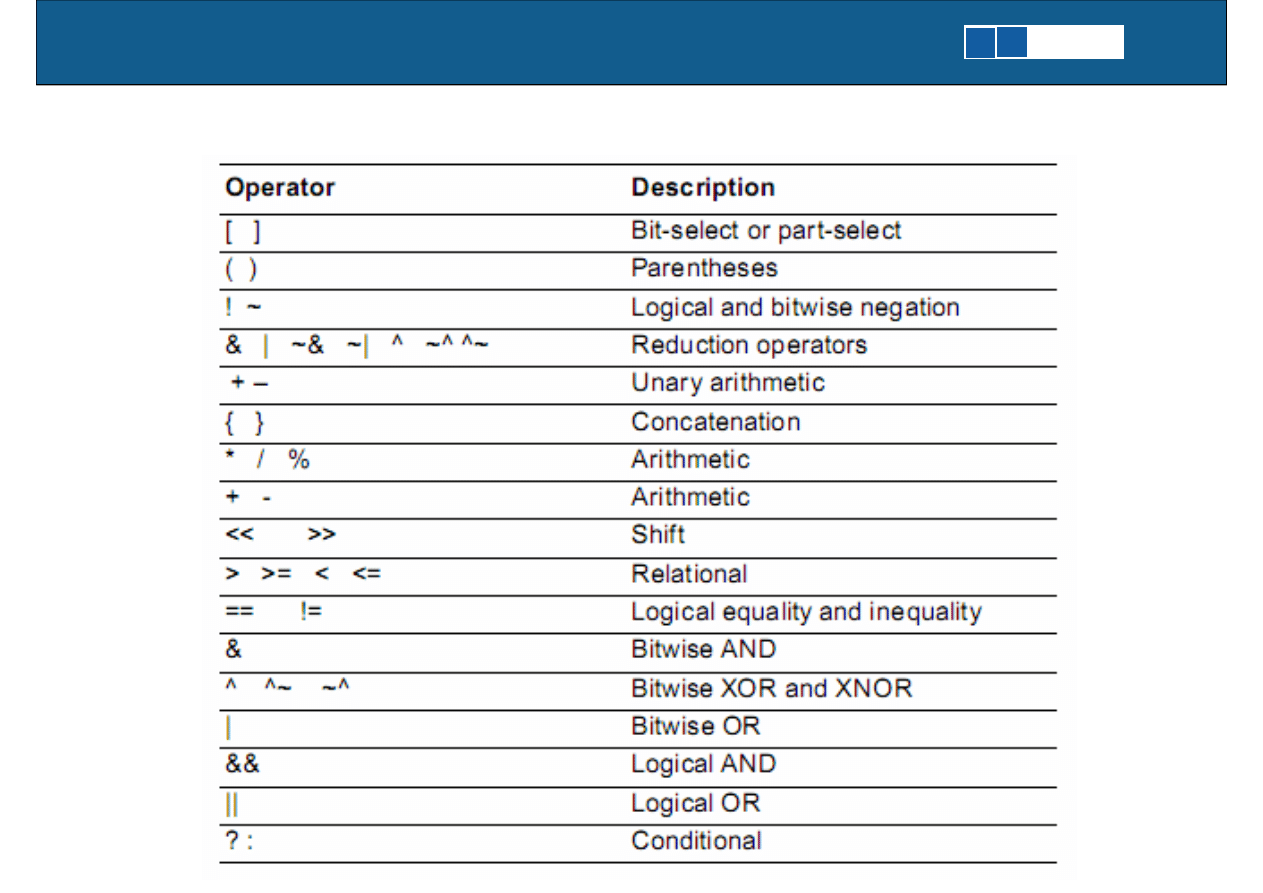

Operatory i ich priorytety

2. RTL = Register Transfer Level

21/41

1

2

3

4

5

PRZYKŁAD: Narysować strukturę

?

3. always, reg : modelowanie sekwencji

22/41

1

2

3

4

5

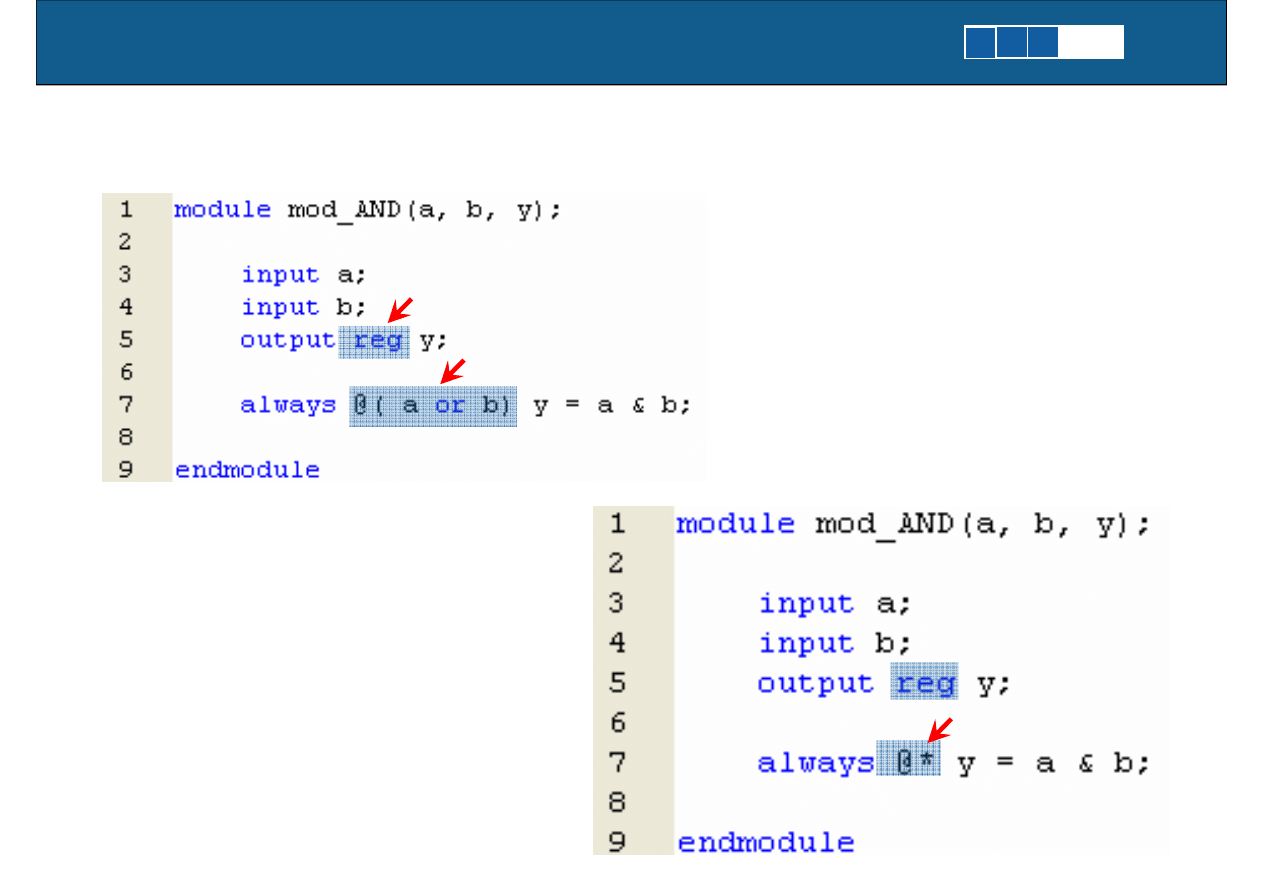

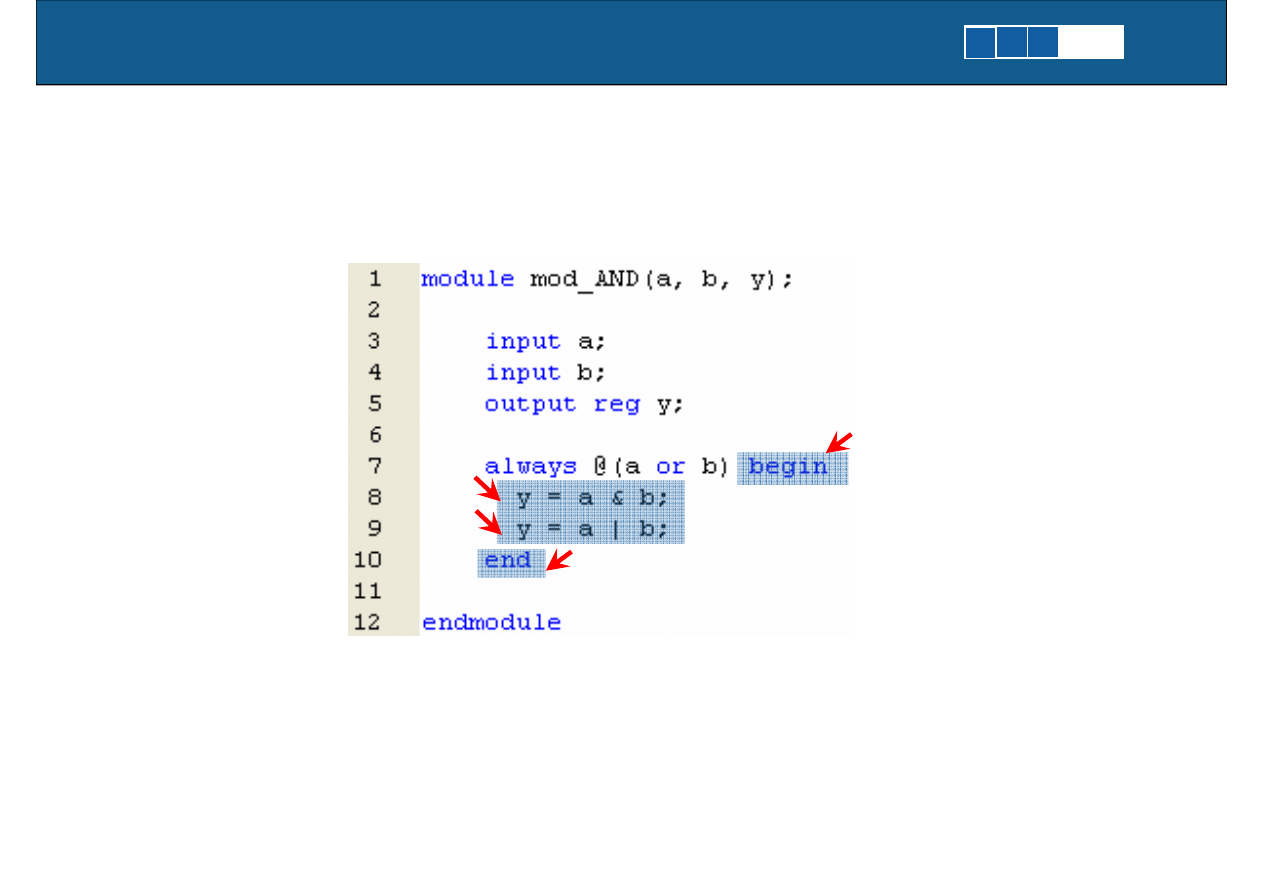

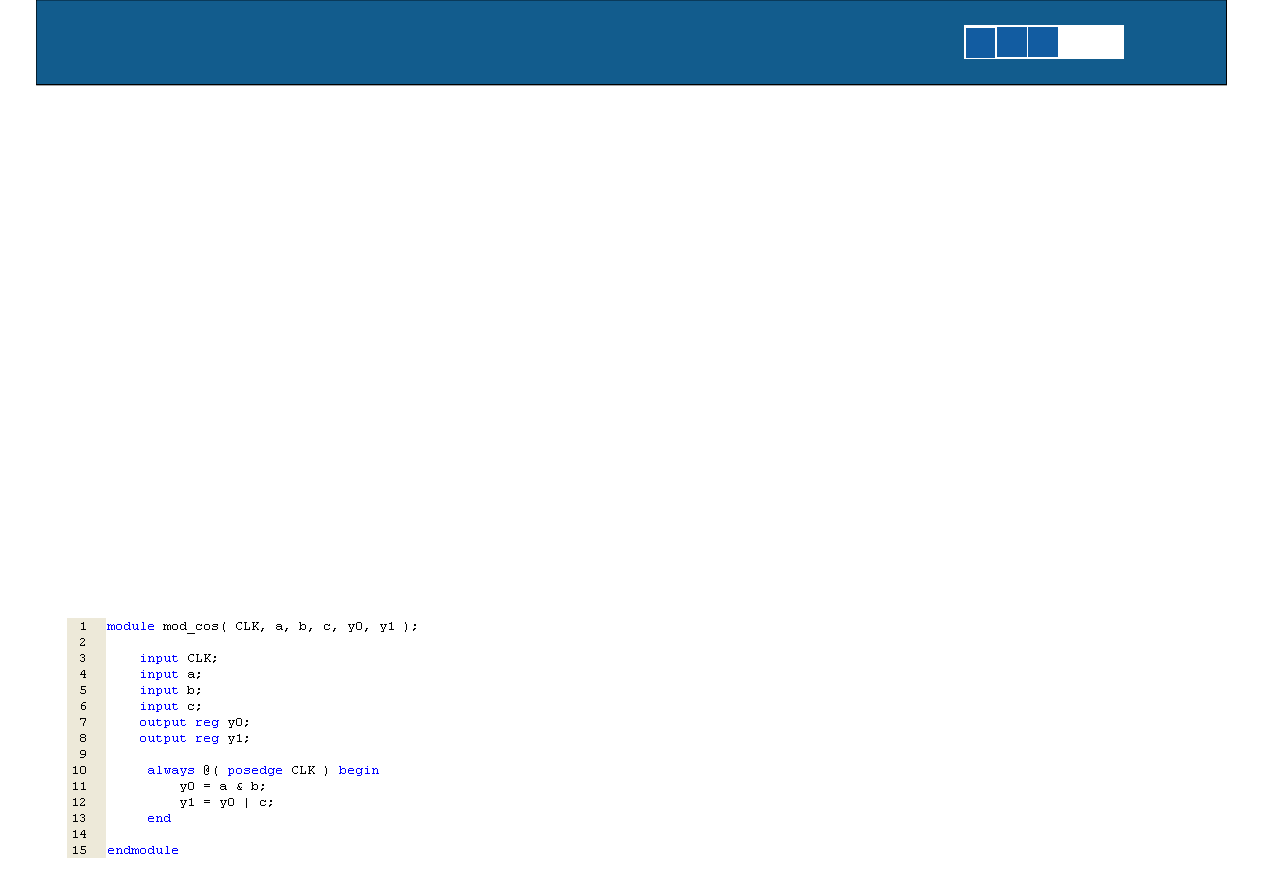

always: reg, liczta czułości

3. always, reg : modelowanie sekwencji

23/41

1

2

3

4

5

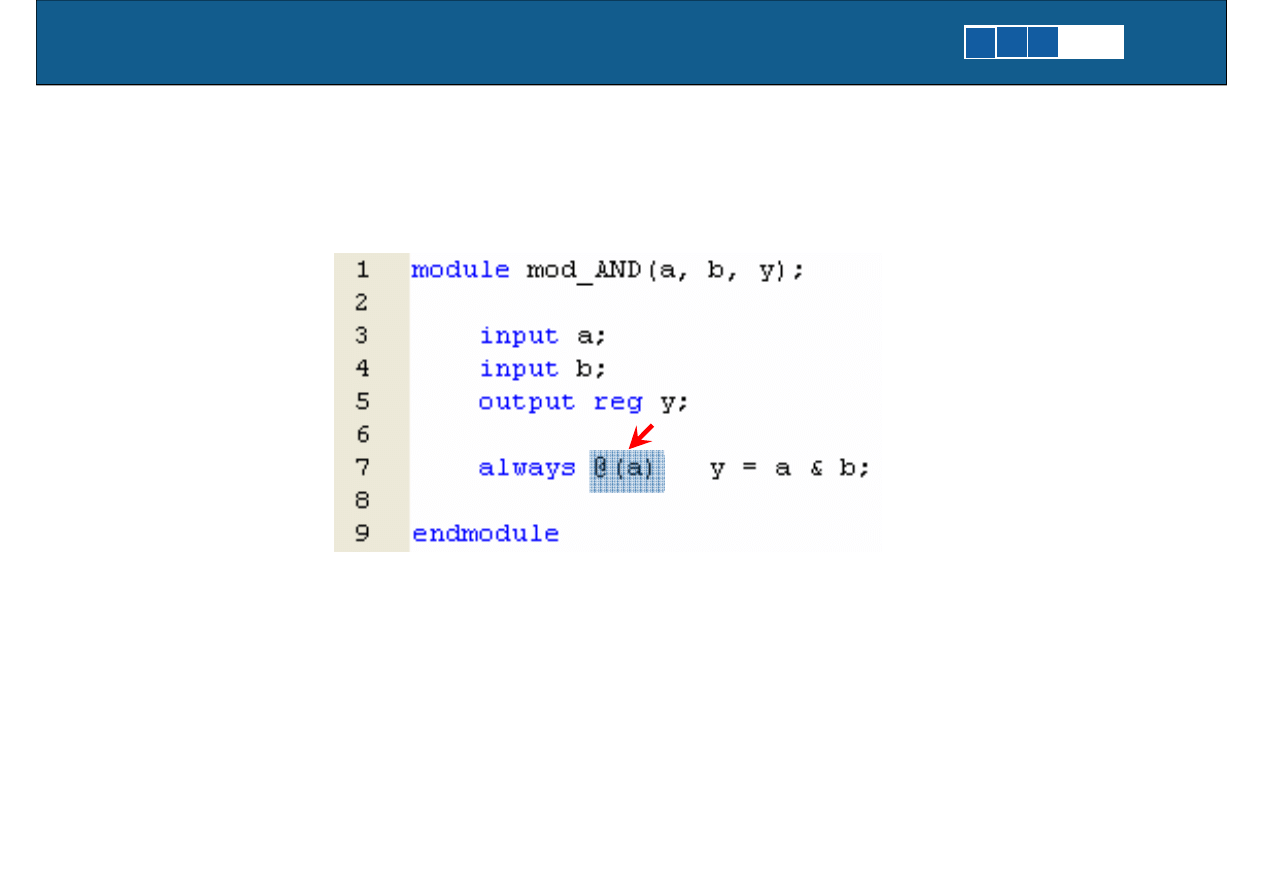

always: ostrożnie z listą czułości

3. always, reg : modelowanie sekwencji

24/41

1

2

3

4

5

always: „sekwencyjność”

3. always, reg : modelowanie sekwencji

25/41

1

2

3

4

5

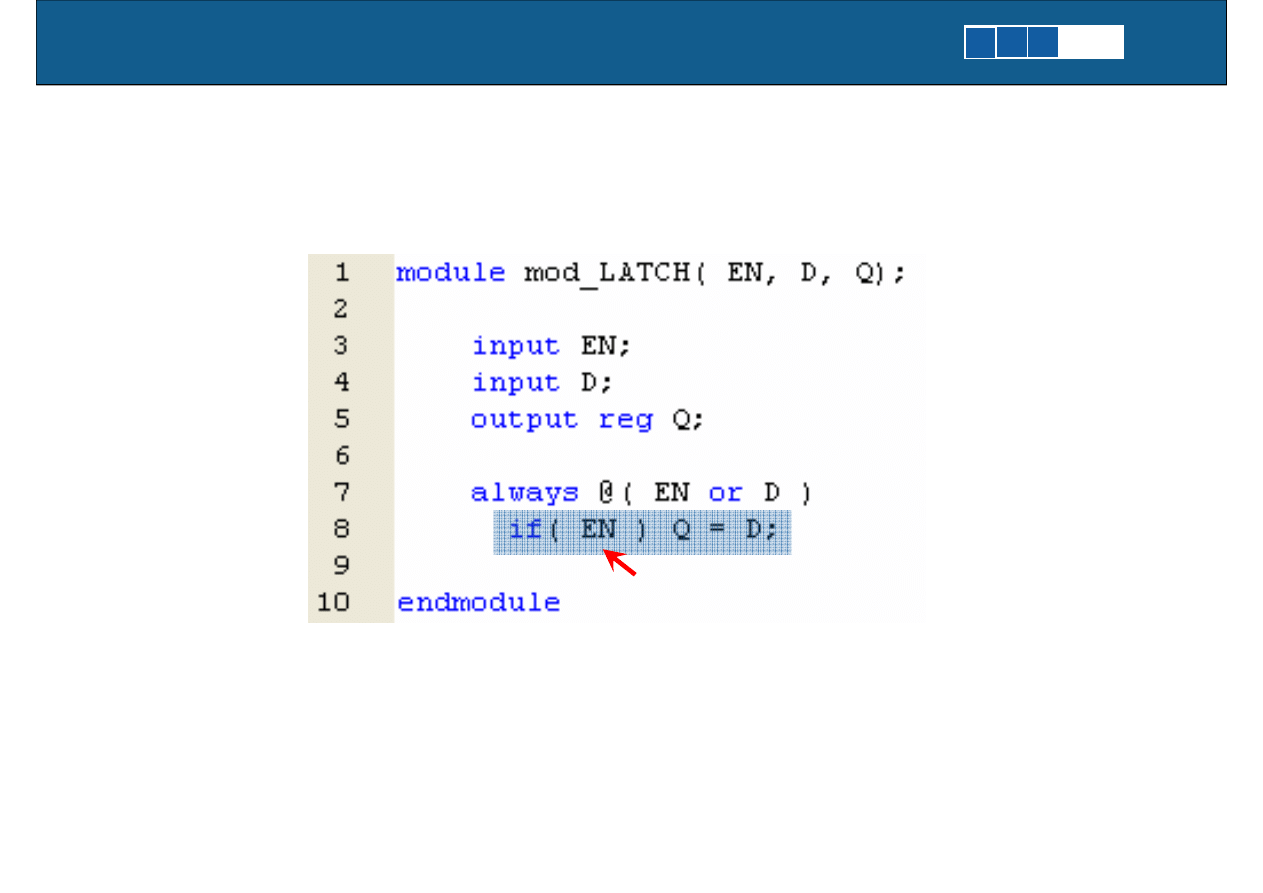

always: LATCH

3. always, reg : modelowanie sekwencji

26/41

1

2

3

4

5

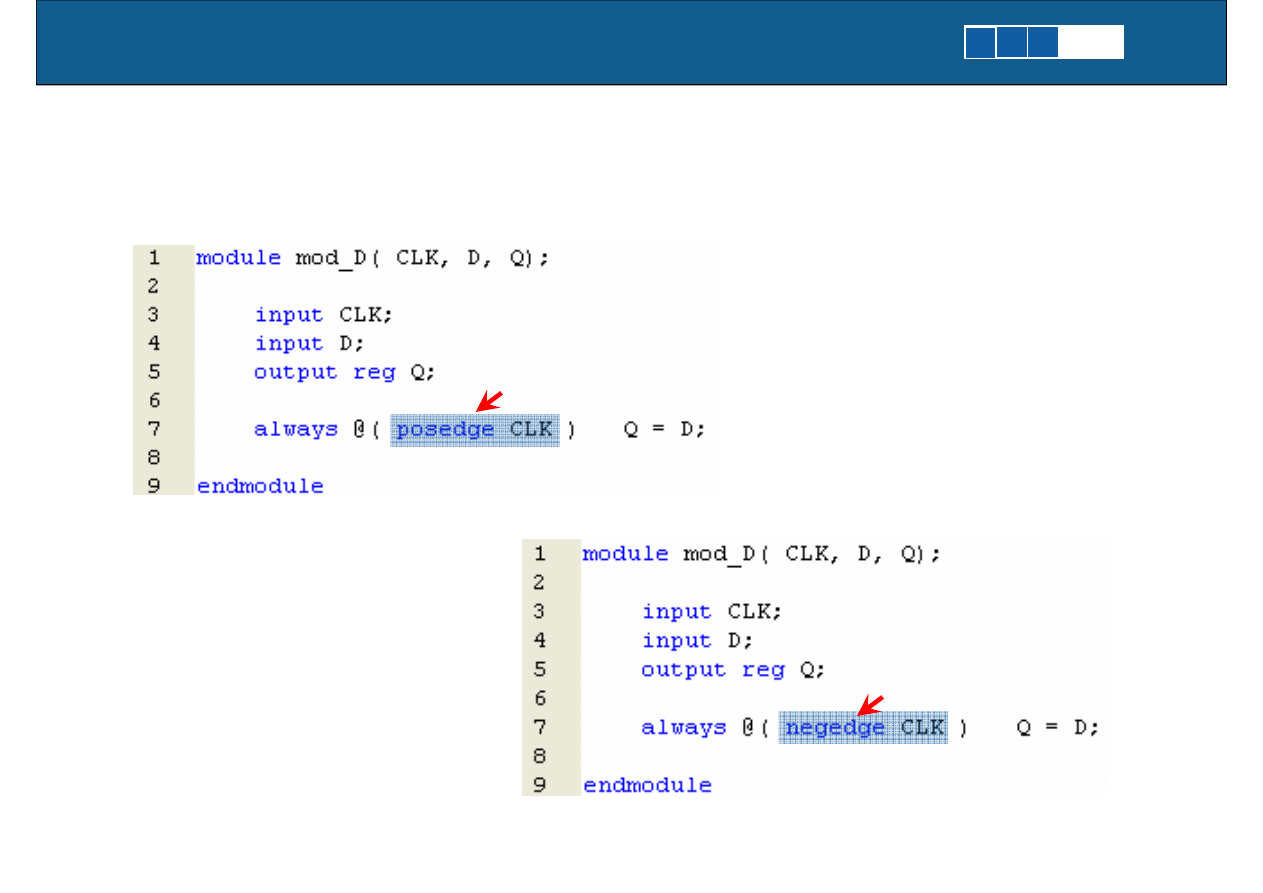

always: zbocze rosnące/malejące

przerzutnik D

3. always, reg : modelowanie sekwencji

27/41

1

2

3

4

5

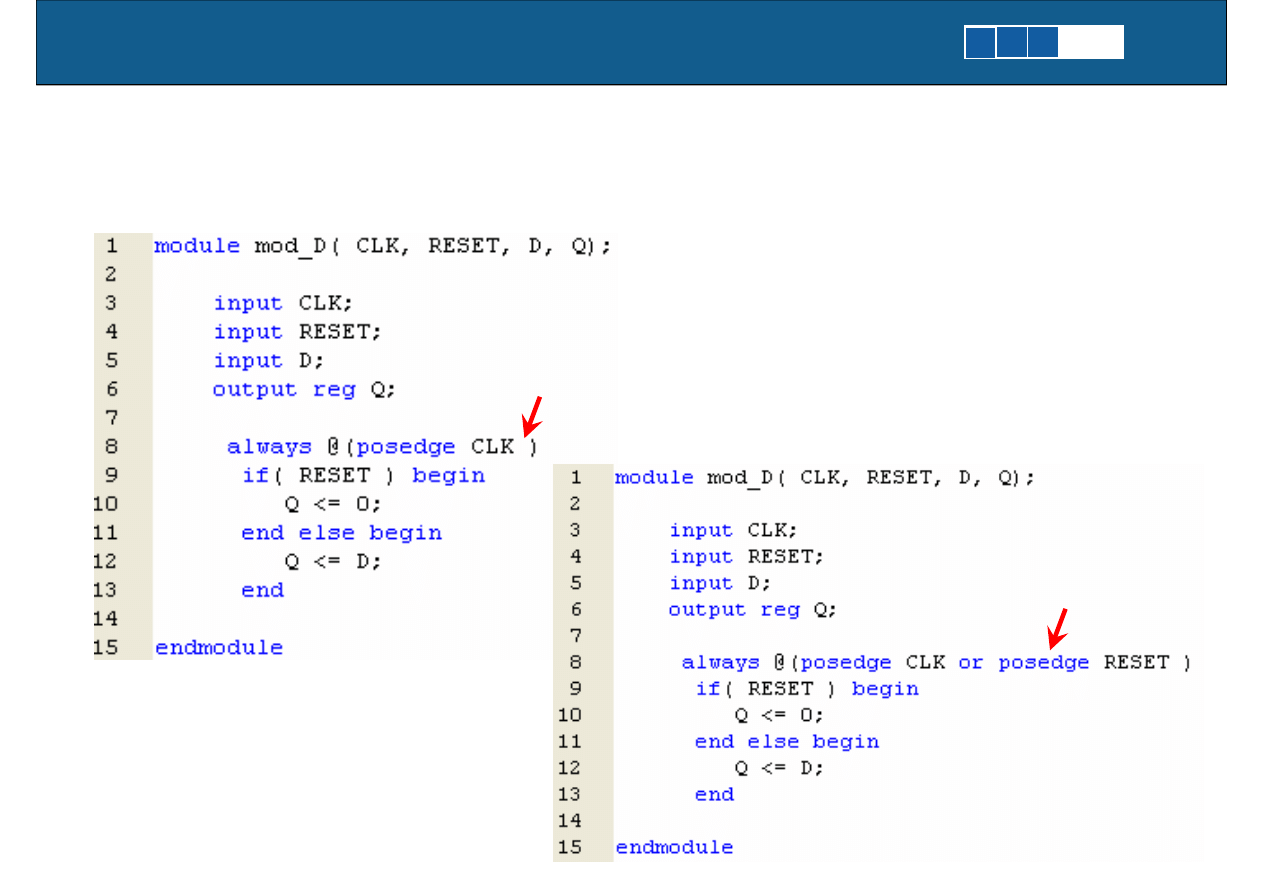

Reset asynchroniczny/synchroniczny

Mieszanie sygnałów synchr./asynchr.

3. always, reg : modelowanie sekwencji

28/41

1

2

3

4

5

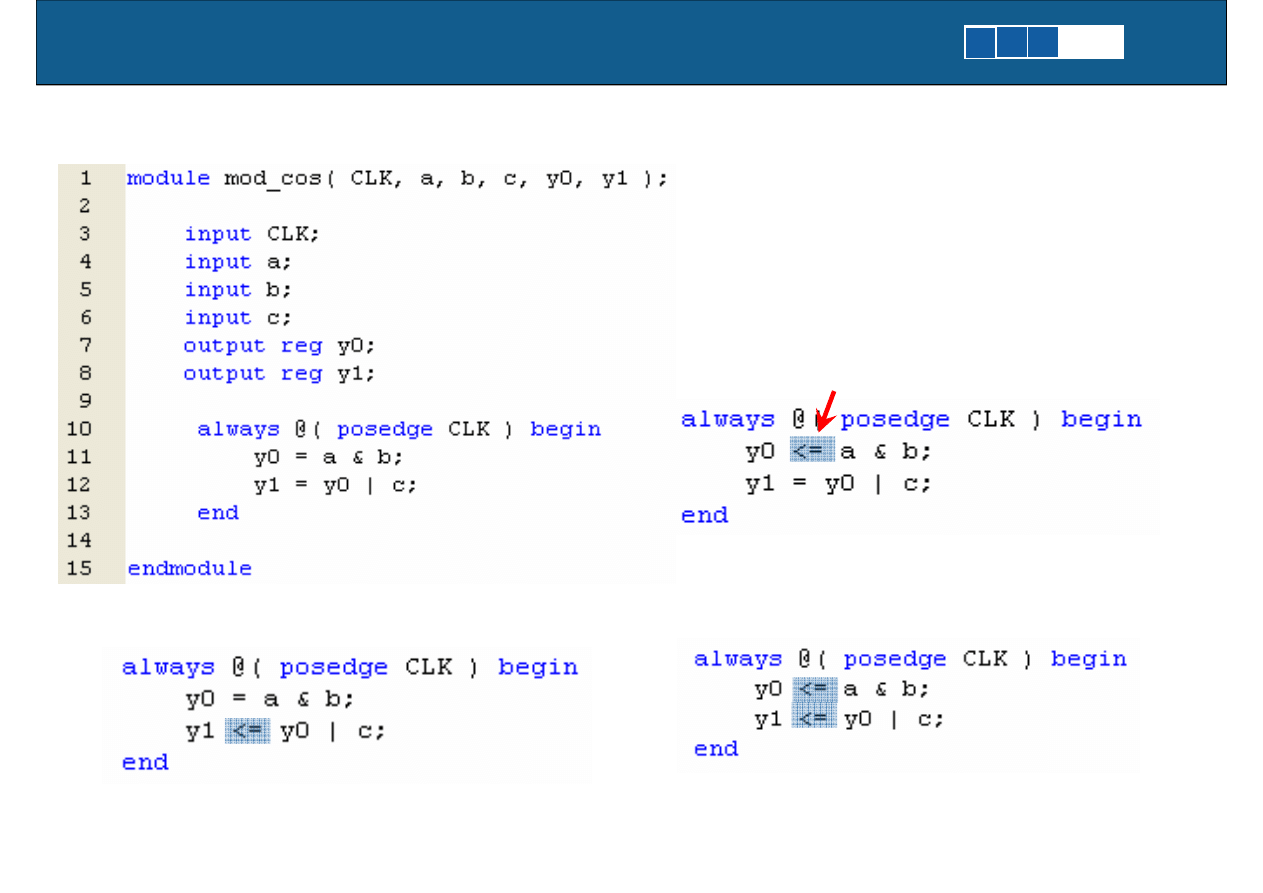

Przypisanie blokujące/nieblokujące

Przypisanie nieblokujące

3. always, reg : modelowanie sekwencji

29/41

1

2

3

4

5

ZADANIE: rejestr przesuwny/licznik

?

30/41

1

2

3

4

5

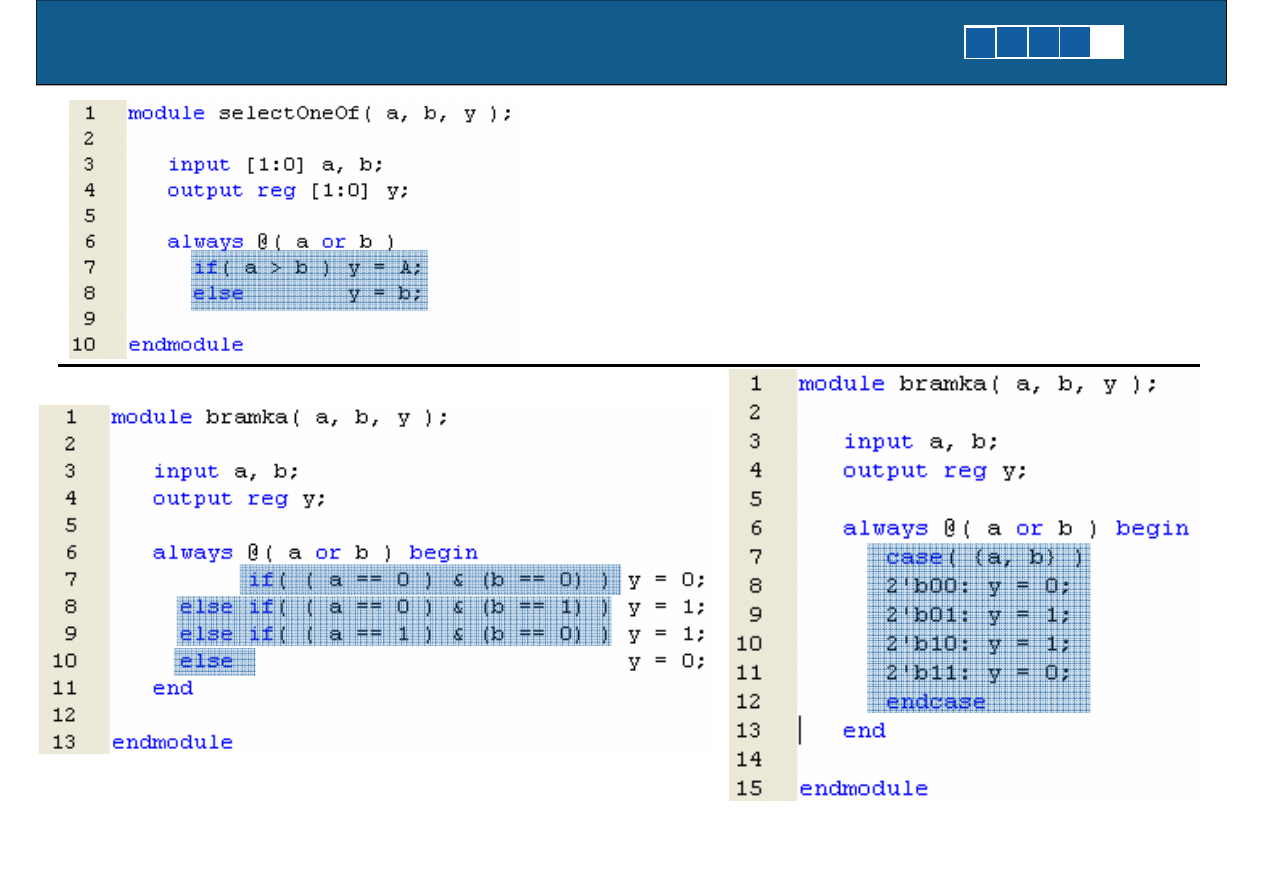

4. Instrukcje sekwencyjne

always: if, case

31/41

1

2

3

4

5

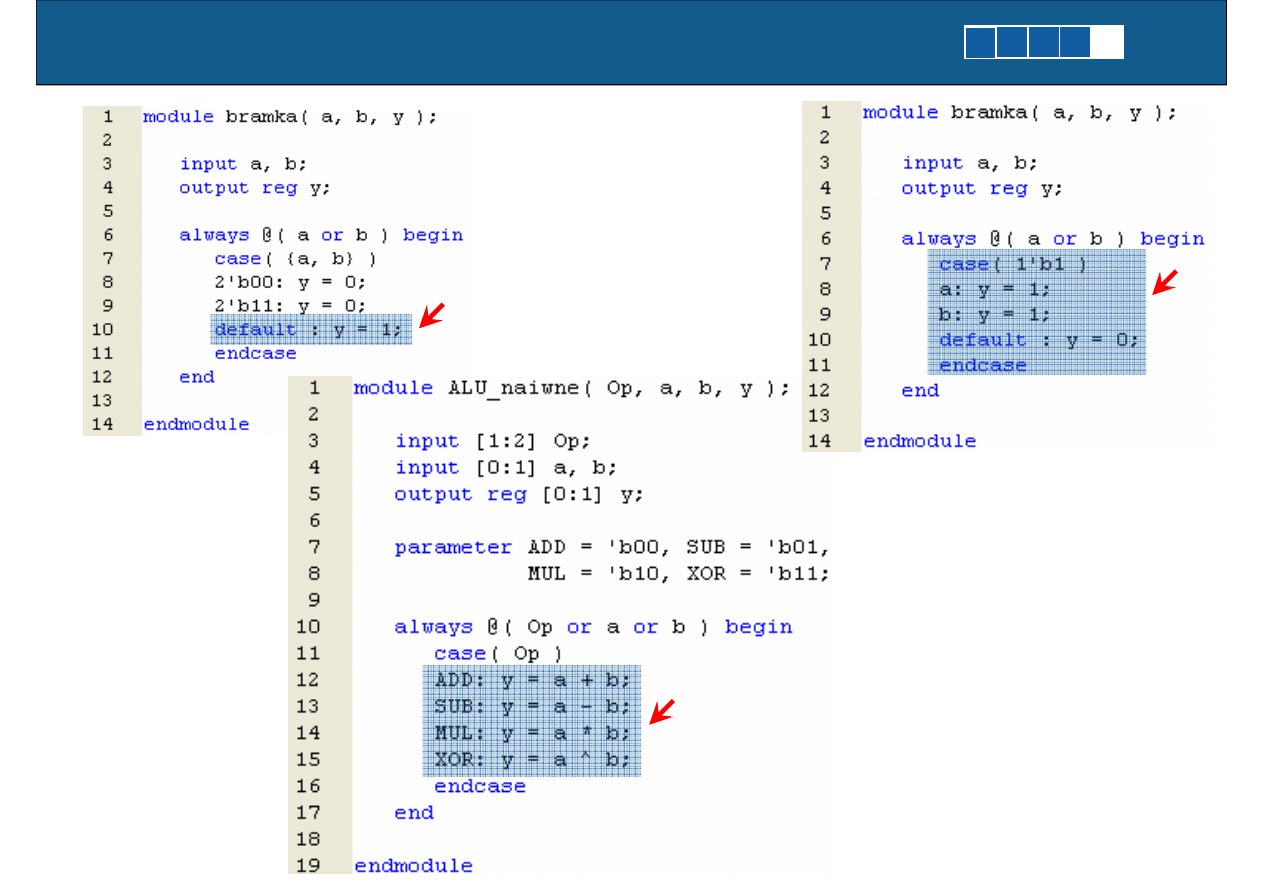

4. Instrukcje sekwencyjne

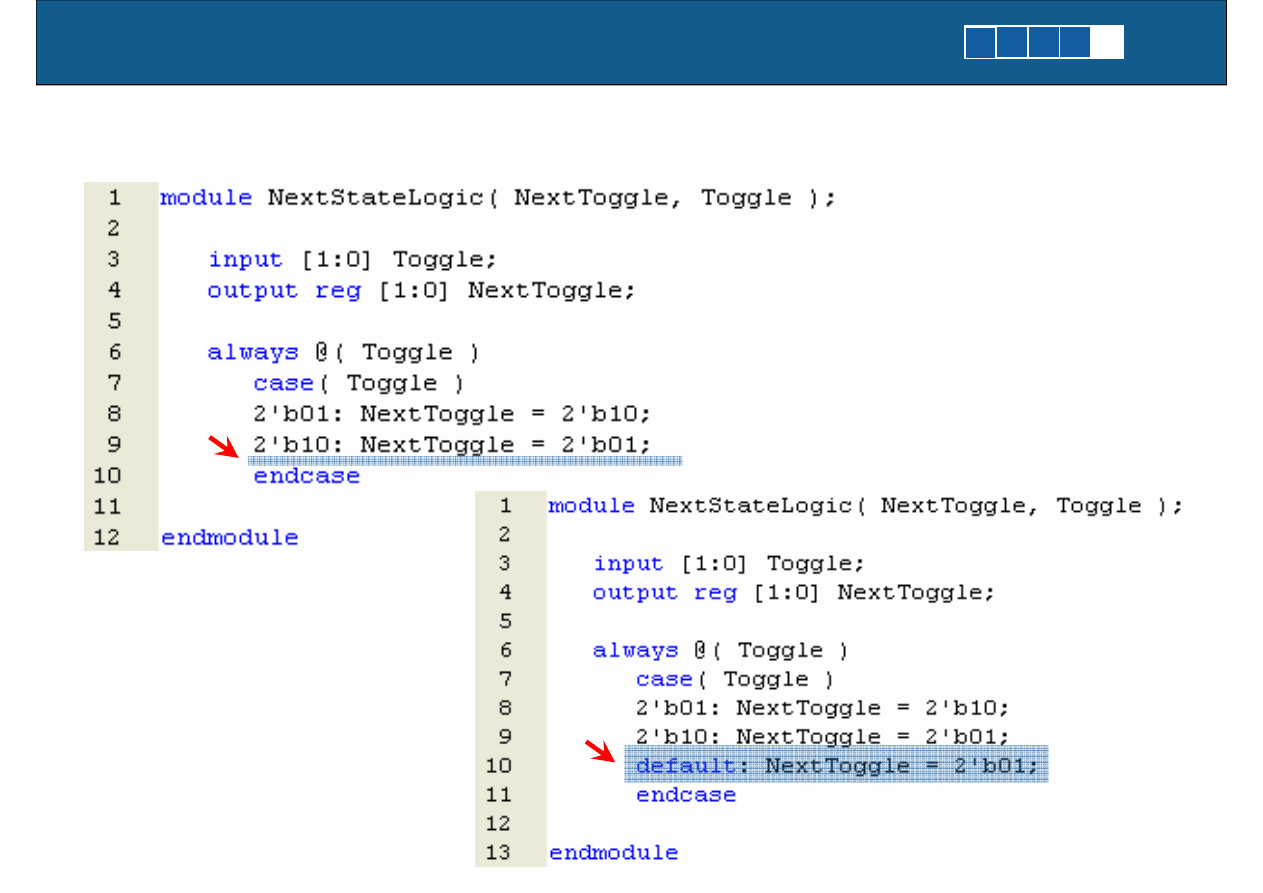

case

32/41

1

2

3

4

5

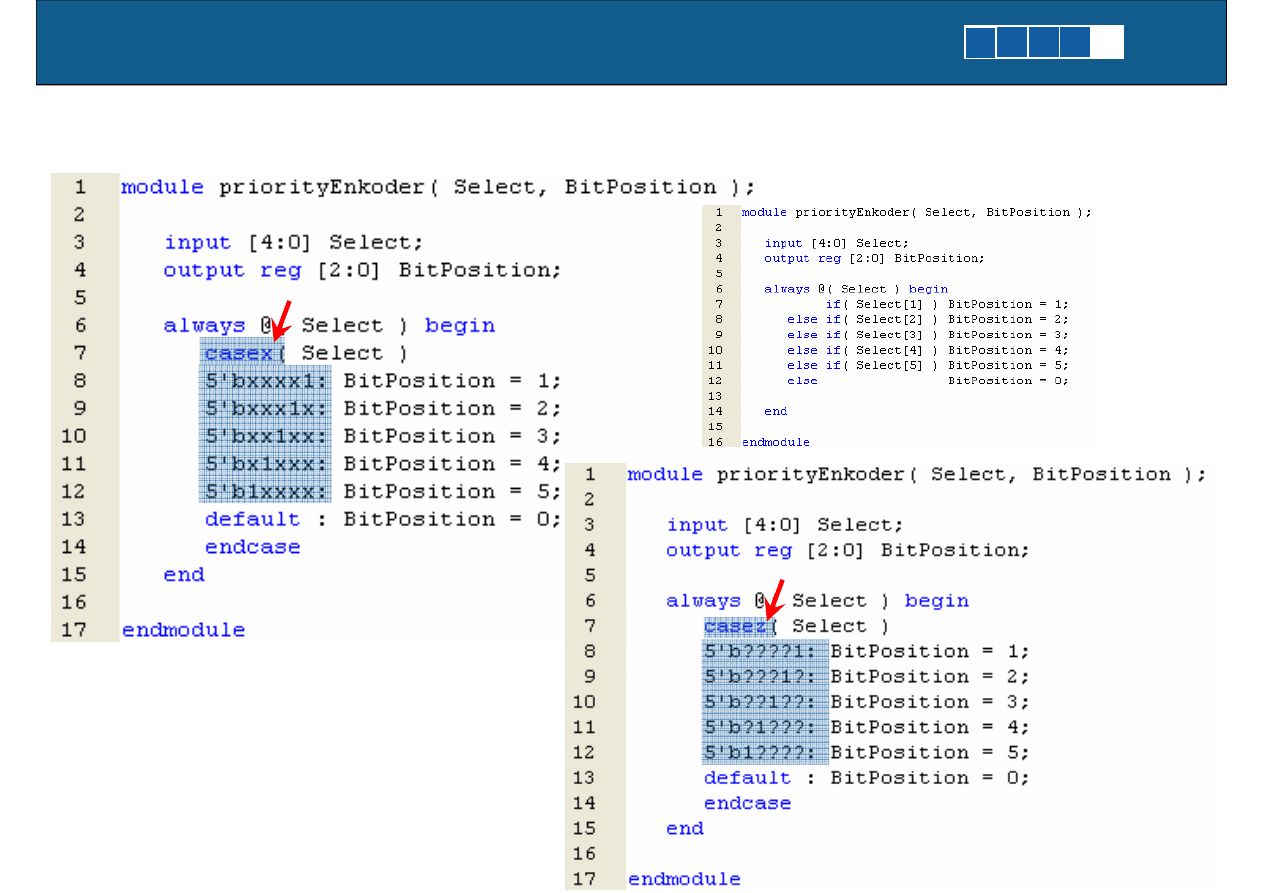

4. Instrukcje sekwencyjne

casex, casez

33/41

1

2

3

4

5

4. Instrukcje sekwencyjne

always: synteza przerzutnika/latch

34/41

1

2

3

4

5

4. Instrukcje sekwencyjne

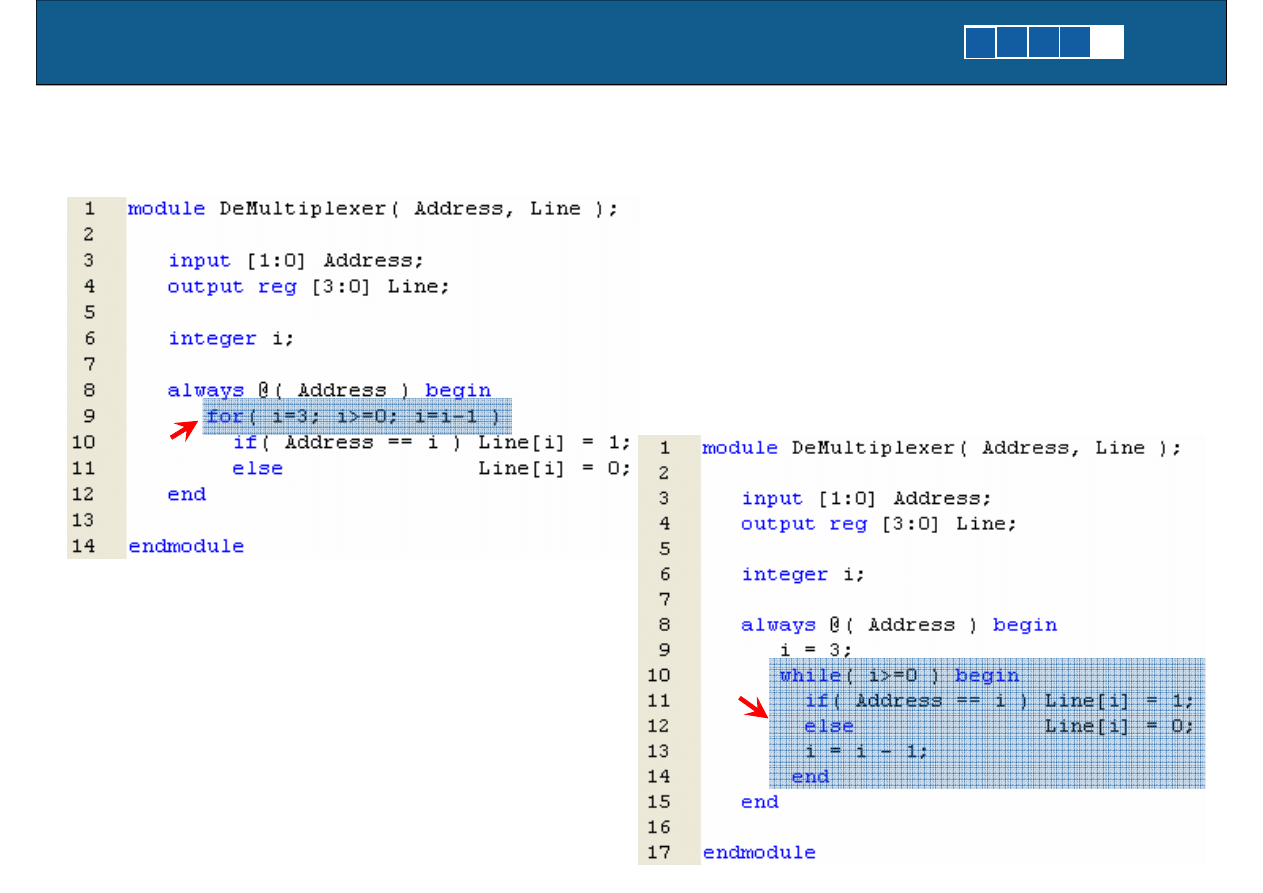

always: for, while

35/41

1

2

3

4

5

4. Instrukcje sekwencyjne

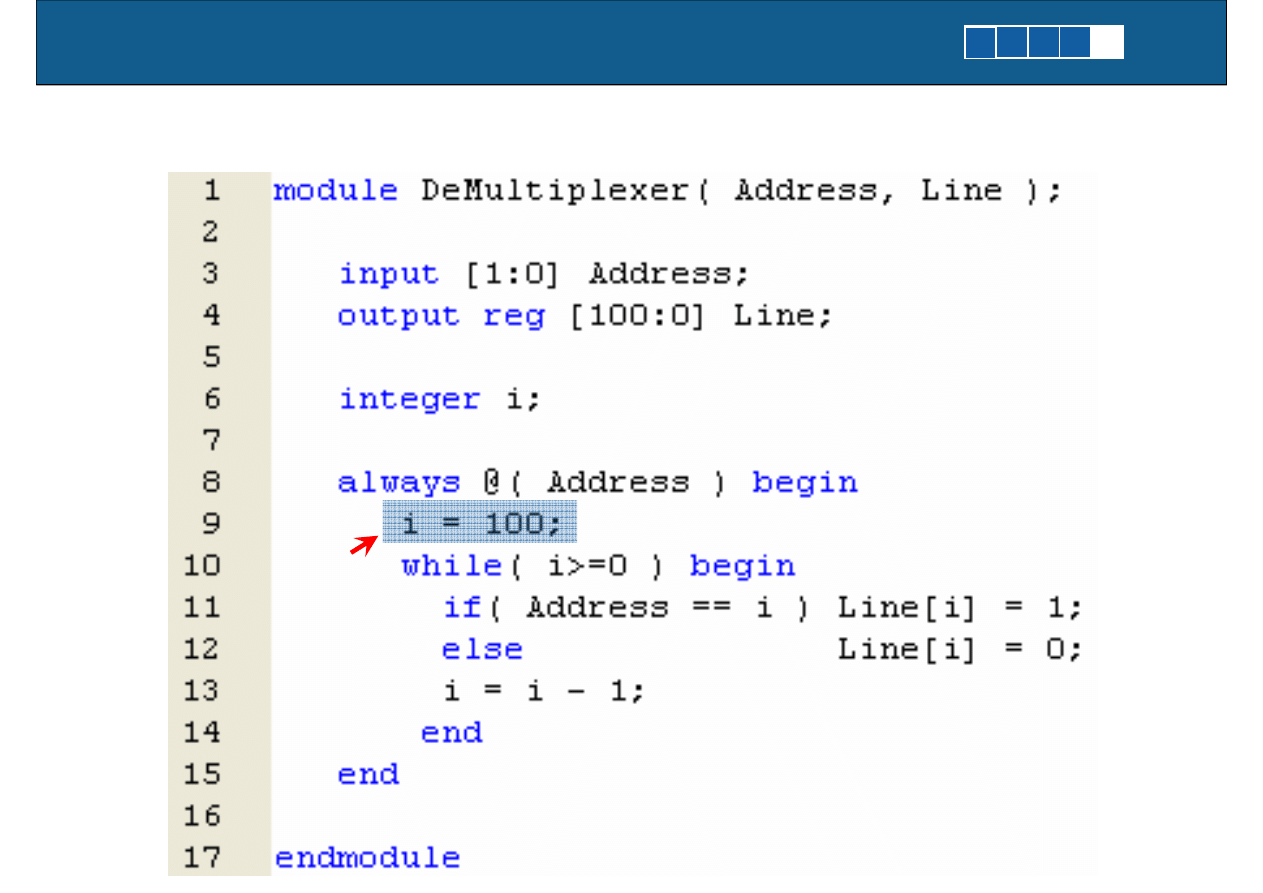

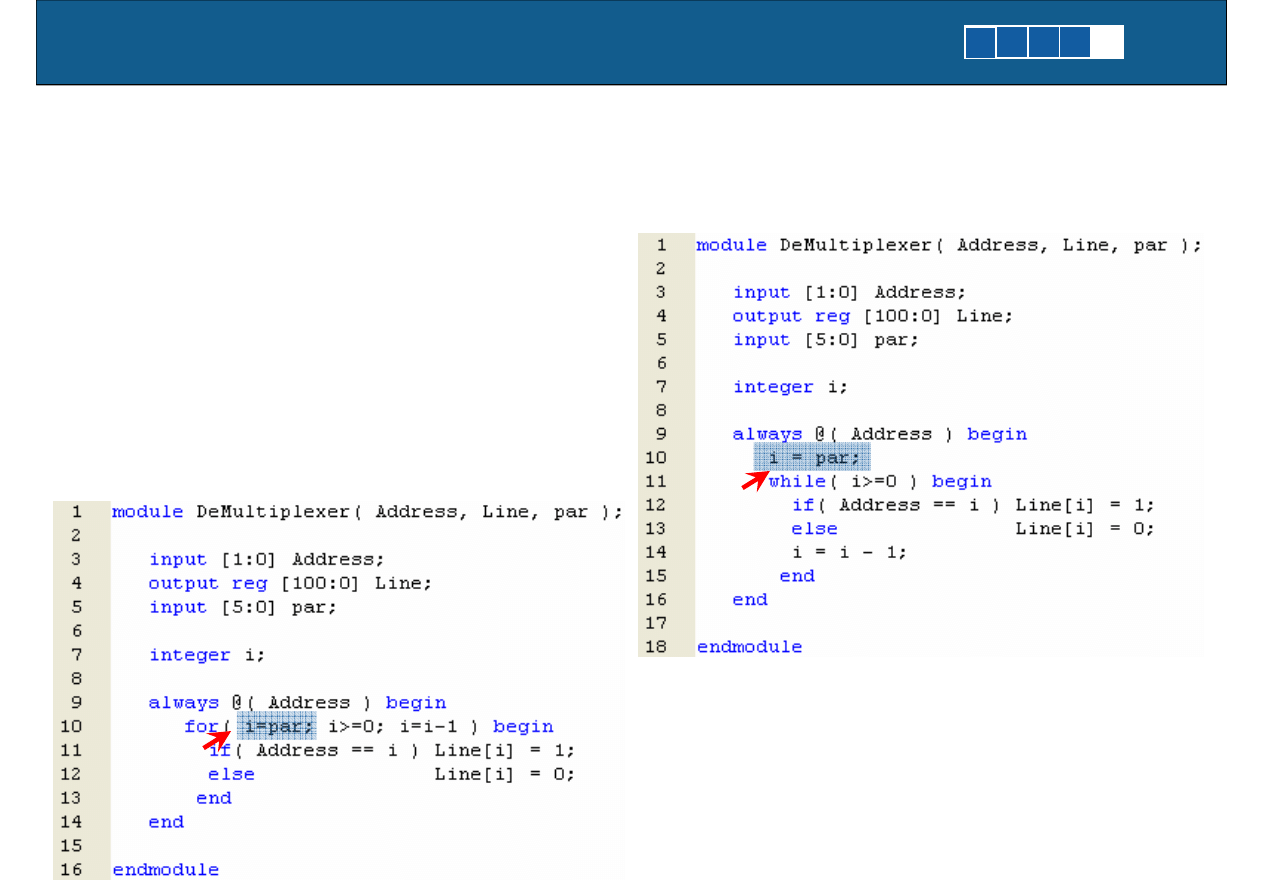

always: for, while - OSTROŻNIE

36/41

1

2

3

4

5

4. Instrukcje sekwencyjne

always: for, while NIE ZAWSZE SYNTEZOWALNE

NA POZIOMIE LOGICZNYM

5. Funkcje i zadania

37/41

1

2

3

4

5

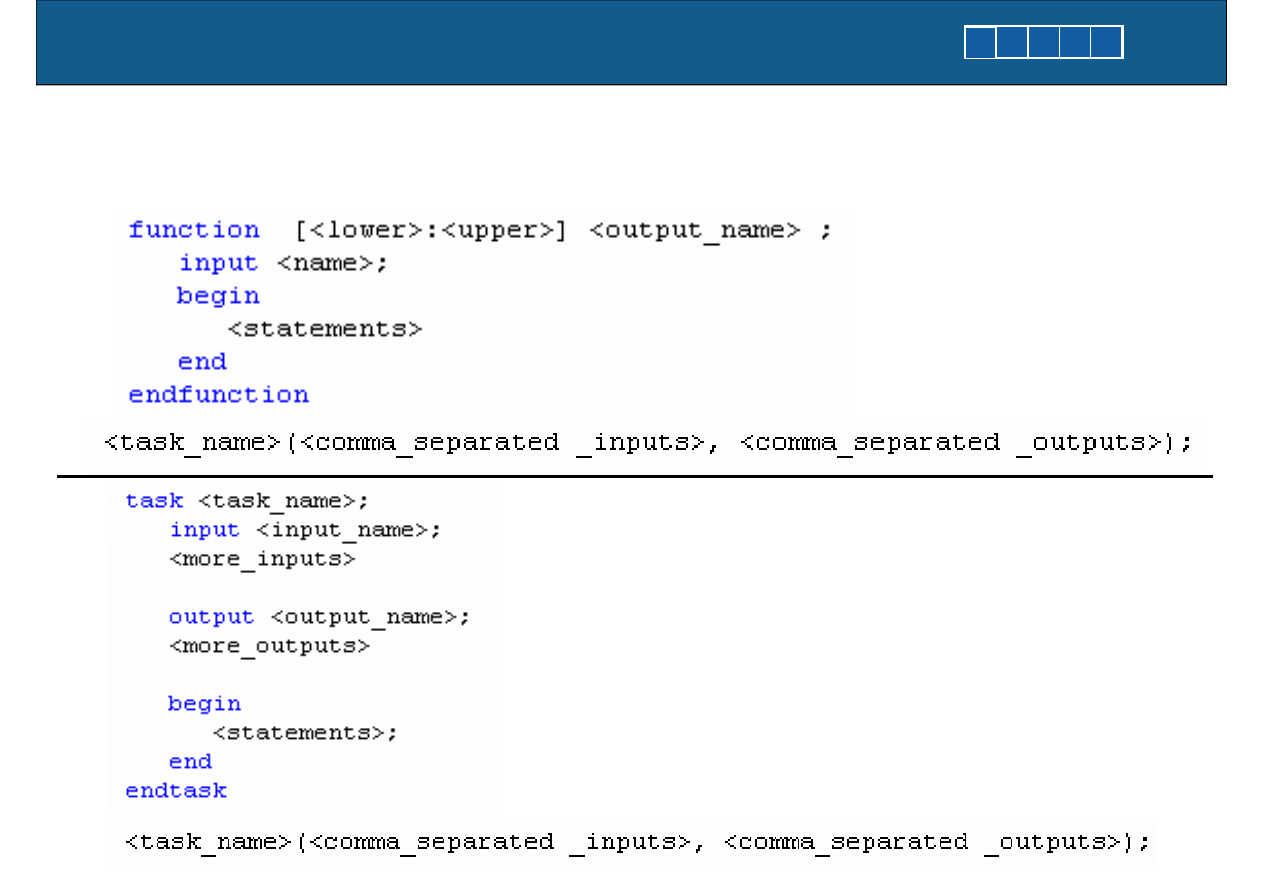

Funkcje, zadania

FUNCTION

TASK

5. Funkcje i zadania

38/41

1

2

3

4

5

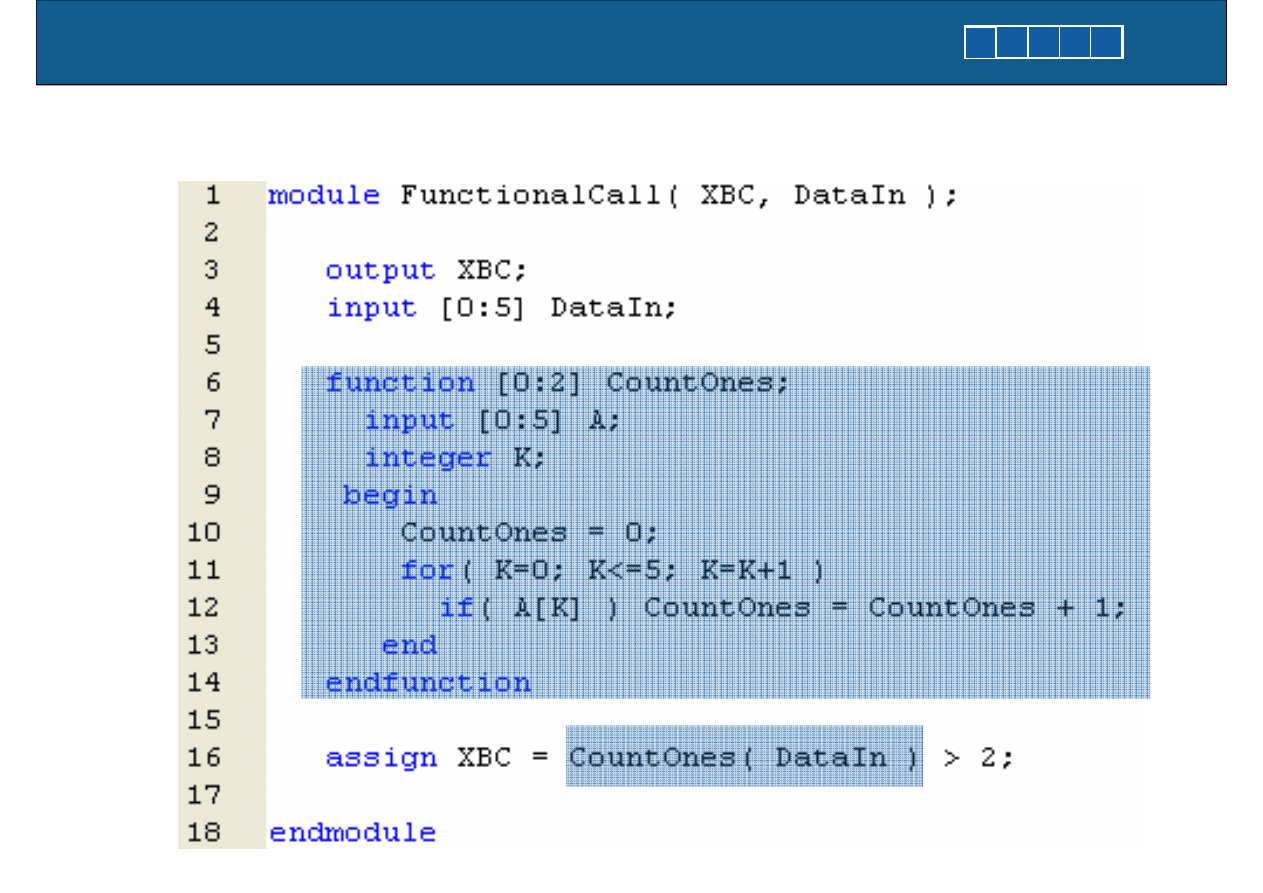

Przykład funkcji

5. Funkcje i zadania

39/41

1

2

3

4

5

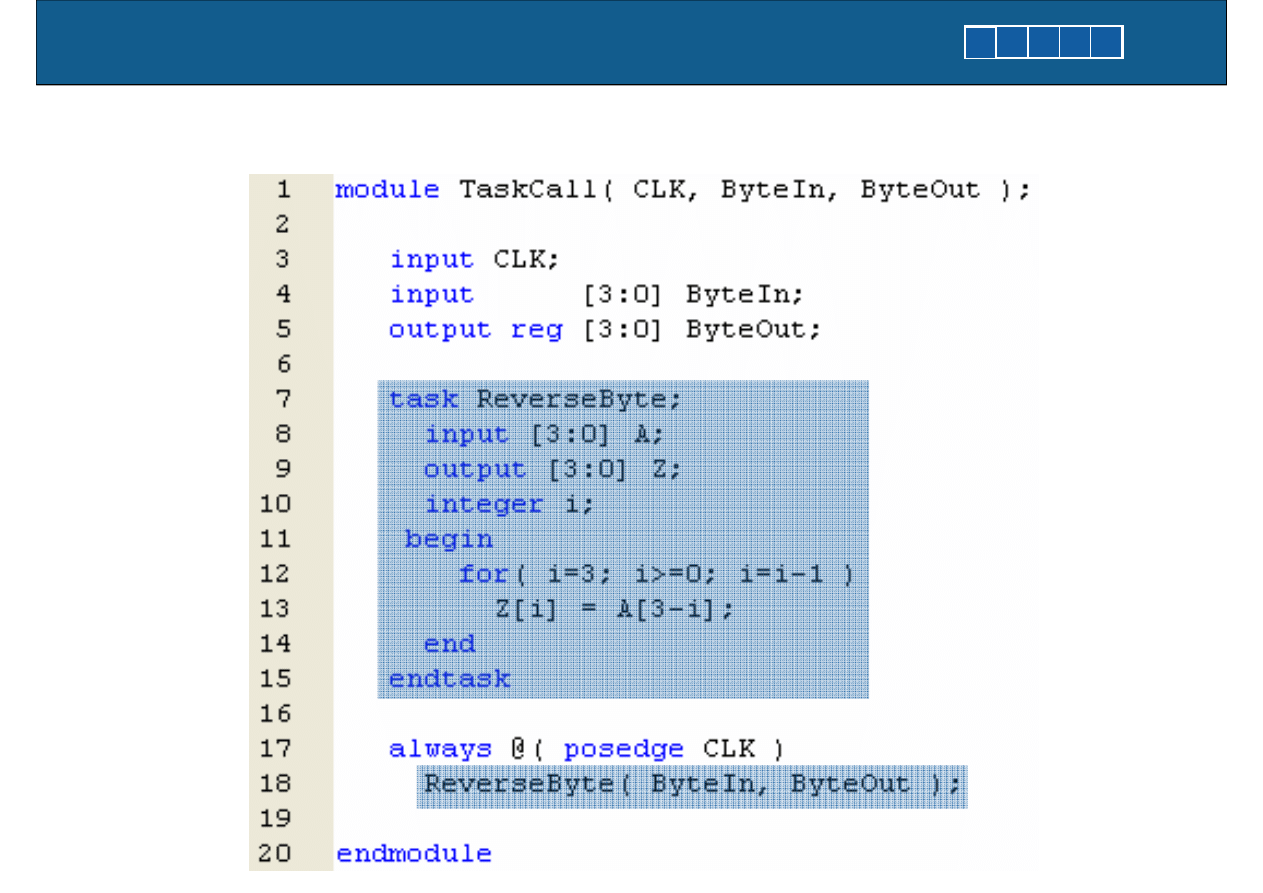

Przykład zadania

Verilog

40/41

Polecana literatura

1) J. Bhasker, Verilog HDL Synthesis, A Practical Primer, Star Galaxy Publishing 1998

3) C.M. Maxfield, The Design Warrior’s Guide to FPGAs, Linacre House 2004

2) Synopsys, FPGA Compiler II/FPGA Express, Verilog HDL Reference Manual,

Synopsys 1999

Verilog

41/41

KONIEC

dr inż. Mariusz Kapruziak

mkapruziak@wi.ps.pl

pok. 107, tel. 449 55 44

Wyszukiwarka

Podobne podstrony:

Kluwer Digital Computer Arithmetic Datapath Design Using Verilog HDL

Computer Architecture Handbook on Verilog HDL

HDL XIX wiek

Arytmetyka resztowa HDL

l5 seql verilog

Active HDL 63SE User Guide

lab3 Verilog

HDL

lab10 Verilog

lab6 Verilog

HDL Wielka Teoria Piekna

HDL

HDL pl PHiMD

Cholesterol całkowity, LDL i HDL normy

instrukcja PTC cw2 hdl wprowadz Nieznany

16 HDL

HDL zagadnienie nr 4

więcej podobnych podstron