UKŁADY I OPERACJE

UKŁADY I OPERACJE

WEJŚCIA/WYJŚCIA

WEJŚCIA/WYJŚCIA

Układy wejścia/wyjścia

Układy wejścia/wyjścia

Operacje z bezpośrednim sterowaniem przez

Operacje z bezpośrednim sterowaniem przez

mikroprocesor

mikroprocesor

Operacje z pośrednim sterowaniem przez

Operacje z pośrednim sterowaniem przez

mikroprocesor (DMA)

mikroprocesor (DMA)

Układem we/wy nazywamy układ elektroniczny pośredniczący w

wymianie informacji pomiędzy mikroprocesorem i pamięcią

systemu z jednej strony a urządzeniem peryferyjnym (zewnętrznym

urządzeniem

współpracującym)

z

drugiej.

Dla systemu mikroprocesorowego układ we/wy widoczny jest jako

rejestr lub zespół rejestrów o określonych adresach oraz pewien

zestaw sygnałów sterujących.

Układem we/wy nazywamy układ elektroniczny pośredniczący w

wymianie informacji pomiędzy mikroprocesorem i pamięcią

systemu z jednej strony a urządzeniem peryferyjnym (zewnętrznym

urządzeniem

współpracującym)

z

drugiej.

Dla systemu mikroprocesorowego układ we/wy widoczny jest jako

rejestr lub zespół rejestrów o określonych adresach oraz pewien

zestaw sygnałów sterujących.

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

Urządzenia

peryferyjne

mogą

służyć

do

Urządzenia

peryferyjne

mogą

służyć

do

wprowadzania,

wyprowadzania

bądź

wprowadzania,

wyprowadzania

bądź

przechowywania informacji lub być układami

przechowywania informacji lub być układami

wykonawczymi.

wykonawczymi.

Dlaczego konieczne jest pośredniczenie?

Dlaczego konieczne jest pośredniczenie?

różnice w szybkości działania (konieczne jest

różnice w szybkości działania (konieczne jest

więc sterowanie przepływem informacji)

więc sterowanie przepływem informacji)

różnice w parametrach elektrycznych (konieczna

różnice w parametrach elektrycznych (konieczna

więc translacja poziomu sygnałów)

więc translacja poziomu sygnałów)

wymagają podania informacji o określonym

wymagają podania informacji o określonym

formacie wraz z pewnymi sygnałami sterującymi

formacie wraz z pewnymi sygnałami sterującymi

(np. Sygnał wideo wraz z synchronizacją)

(np. Sygnał wideo wraz z synchronizacją)

Układy wej/wyj podobnie jak pamięci posiadają

Układy wej/wyj podobnie jak pamięci posiadają

wejścia adresowe i sterujące.

wejścia adresowe i sterujące.

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

00000

00000

0

0

00001

00001

1

1

00002

00002

2

2

00003

00003

3

3

00004

00004

4

4

00005

00005

5

5

00006

00006

6

6

00007

00007

7

7

00008

00008

8

8

00009

00009

9

9

0000A

0000A

10

10

0000B

0000B

11

11

FFFF9

FFFF9

104856

104856

9

9

FFFFA

FFFFA

104857

104857

0

0

FFFFB

FFFFB

104857

104857

1

1

FFFFC

FFFFC

104857

104857

2

2

FFFFD

FFFFD

104857

104857

3

3

FFFFE

FFFFE

104857

104857

4

4

FFFFF

FFFFF

104857

104857

5

5

Adres

szesnastkowo

Adres

dziesiętnie

0000

0000

0

0

0001

0001

1

1

0002

0002

2

2

0003

0003

3

3

0004

0004

4

4

0005

0005

5

5

0006

0006

6

6

0007

0007

7

7

0008

0008

8

8

0009

0009

9

9

000A

000A

10

10

000B

000B

11

11

FFF9

FFF9

65529

FFFA

FFFA

65530

65530

FFFB

FFFB

65531

65531

FFFC

FFFC

65532

65532

FFFD

FFFD

65533

65533

FFFE

FFFE

65534

65534

FFFF

FFFF

65535

65535

Adres

szesnastkowo

Adres

dziesiętnie

Układy wejścia/wyjścia to 65536 "okienek" (o numerach od 0 do 65535)

Układy wejścia/wyjścia to 65536 "okienek" (o numerach od 0 do 65535)

zwanych portami. Są one niezbędne do komunikowania się z

zwanych portami. Są one niezbędne do komunikowania się z

procesorem (8086/88).

procesorem (8086/88).

Przypomnijmy, że komunikacja z tymi portami odbywa się zawsze za

Przypomnijmy, że komunikacja z tymi portami odbywa się zawsze za

pośrednictwem rejestru akumulatora:

pośrednictwem rejestru akumulatora:

•

AL (port - 8 bitowy)

AL (port - 8 bitowy)

•

AX (port 16 - bitowy),

AX (port 16 - bitowy),

a numer portu podawany jest jako dana natychmiastowa lub jako

a numer portu podawany jest jako dana natychmiastowa lub jako

zawartość rejestru DX

zawartość rejestru DX

Do odczytywania danej z portu służy dwuargumentowy rozkaz IN o

Do odczytywania danej z portu służy dwuargumentowy rozkaz IN o

składni:

składni:

IN akumulator, nr_portu

IN akumulator, nr_portu

lub

lub

IN akumulator, rejestr DX

IN akumulator, rejestr DX

Do zapisywania danej do portu służy rozkaz OUT o składni:

Do zapisywania danej do portu służy rozkaz OUT o składni:

OUT nr_portu, akumulator

OUT nr_portu, akumulator

lub

lub

OUT rejestr DX, akumulator

OUT rejestr DX, akumulator

Przykłady

Przykłady

:

:

IN AL,16

IN AL,16

;wpisz do rejestru AL bajt z portu o adresie nr 16

;wpisz do rejestru AL bajt z portu o adresie nr 16

IN AX,DX

IN AX,DX

;

;

wpisz do rejestru AX słowo z portu o numerze w rejestrze

wpisz do rejestru AX słowo z portu o numerze w rejestrze

DX

DX

OUT 6D,AX

OUT 6D,AX

;wyprowadź słowo z rejestru AX do portu o numerze 6D

;wyprowadź słowo z rejestru AX do portu o numerze 6D

OUT DX,AX

OUT DX,AX

;wyprowadź słowo z rejestru AX do portu o numerze w

;wyprowadź słowo z rejestru AX do portu o numerze w

rejestrze DX

rejestrze DX

UKŁDY

UKŁDY

WEJŚCIA/WYJŚCIA

WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

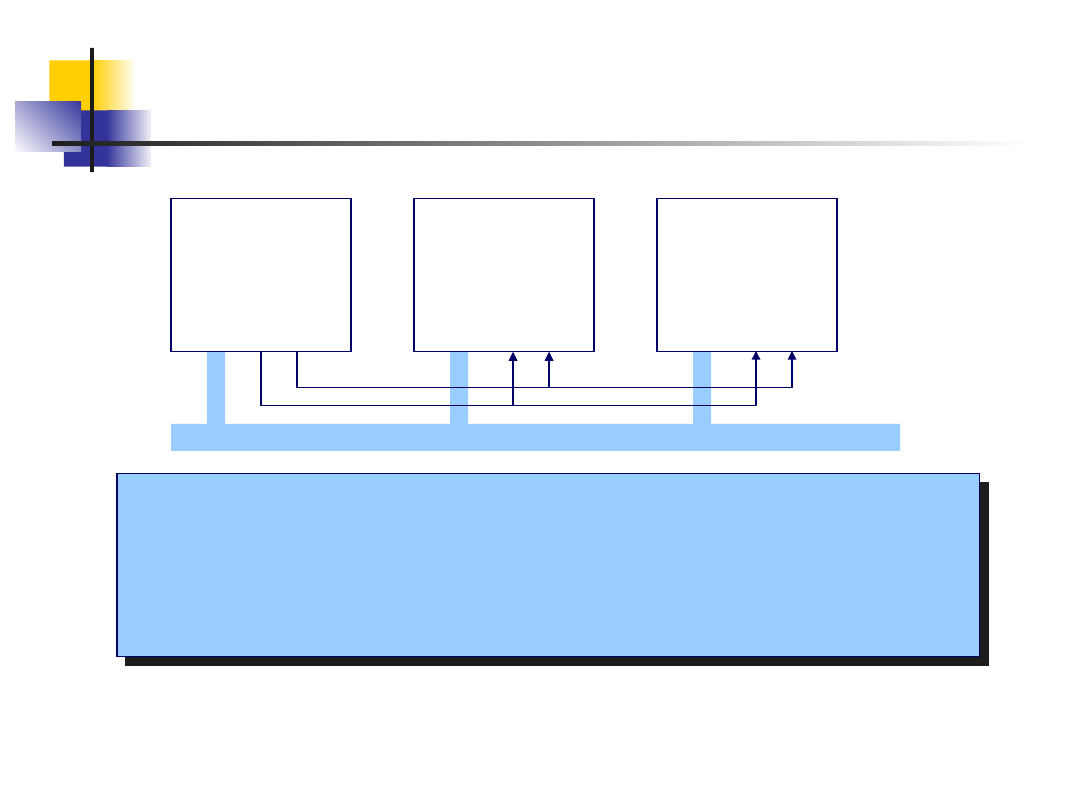

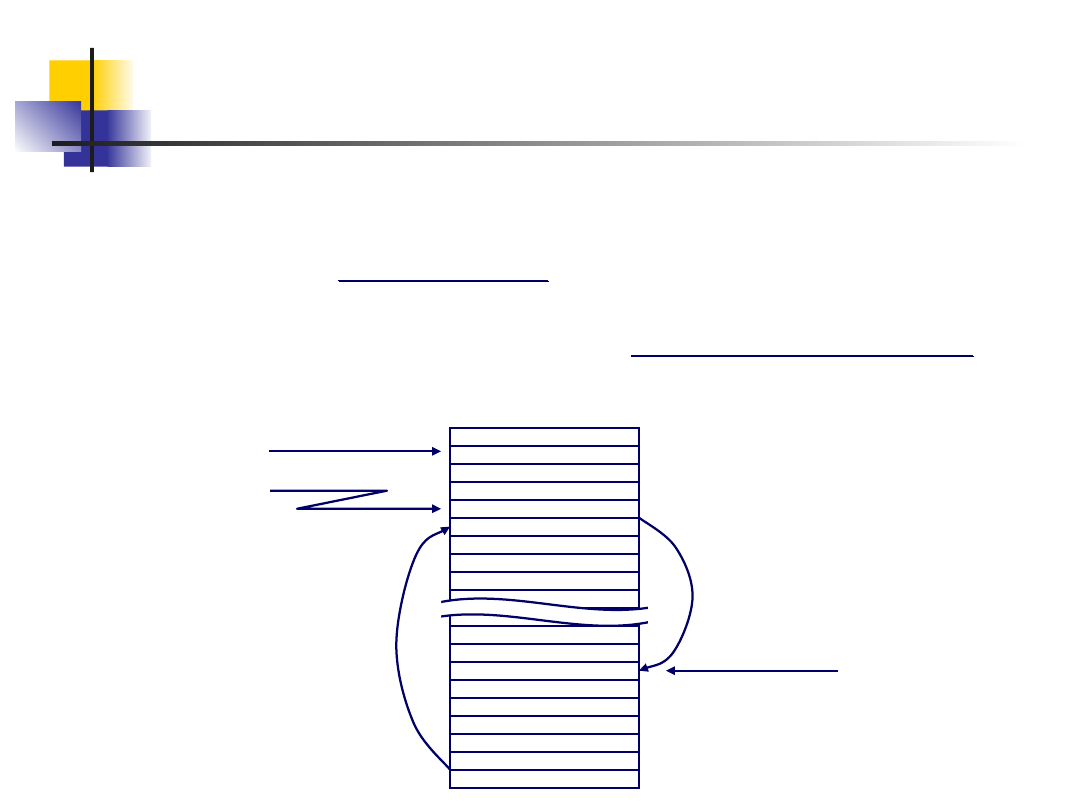

Układy wejścia/wyjścia można podzielić na dwie podstawowe kategorie:

Układy wejścia/wyjścia można podzielić na dwie podstawowe kategorie:

•

układy współadresowalne z pamięcią (np. karta graficzna)

układy współadresowalne z pamięcią (np. karta graficzna)

•

układy izolowane (np. sterownik dysku twardego)

układy izolowane (np. sterownik dysku twardego)

Szyna adresowa

Szyna adresowa

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

CPU

CPU

I/O

I/O

MEMR MEMW

MEMR MEMW

MEMR MEMW

MEMR MEMW

MEMR MEMW

MEMR MEMW

W przypadku układów współadresowalnych z pamięcią

operacyjną wybieramy obiekt, na którym dokonujemy

operacji (komórka pamięci lub rejestr układu we/wy), za

pomocą adresu (istnieje potrzeba wydzielenia w pamięci

przestrzeni dla adresów układów we/wy). Sygnały sterujące

są wspólne dla pamięci i układów we/wy.

W przypadku układów współadresowalnych z pamięcią

operacyjną wybieramy obiekt, na którym dokonujemy

operacji (komórka pamięci lub rejestr układu we/wy), za

pomocą adresu (istnieje potrzeba wydzielenia w pamięci

przestrzeni dla adresów układów we/wy). Sygnały sterujące

są wspólne dla pamięci i układów we/wy.

Np. karta

Np. karta

graficzna

graficzna

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

WSPÓŁADRESOWALNE Z PAMIĘCIĄ

WSPÓŁADRESOWALNE Z PAMIĘCIĄ

Szyna adresowa

Szyna adresowa

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

CPU

CPU

I/O

I/O

MEMR

MEMR

MEMW

MEMW

MEMR MEMW

MEMR MEMW

IOR IOW

IOR IOW

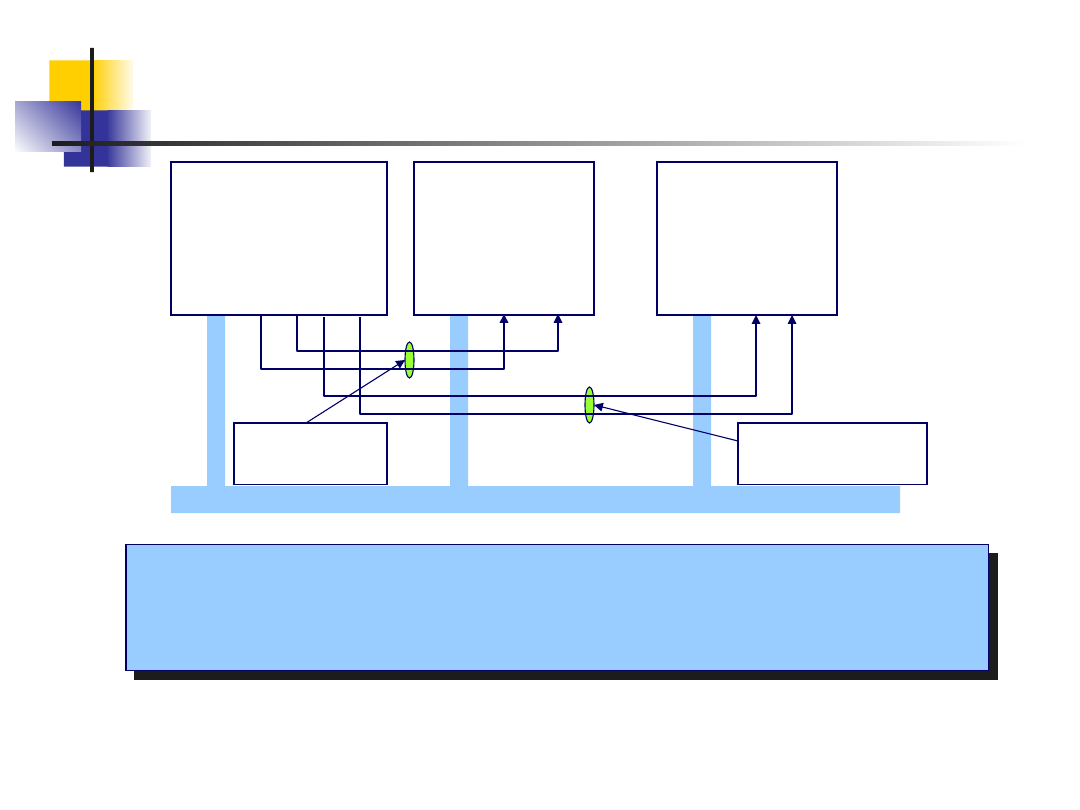

Dla izolowanych układów we/wy wybieramy obiekt, na którym

dokonujemy operacji (komórka pamięci lub rejestr układu

we/wy), za pomocą sygnałów sterujących. Przestrzenie

adresowe pamięci układów we/wy są rozdzielone

Dla izolowanych układów we/wy wybieramy obiekt, na którym

dokonujemy operacji (komórka pamięci lub rejestr układu

we/wy), za pomocą sygnałów sterujących. Przestrzenie

adresowe pamięci układów we/wy są rozdzielone

IOR

IOR

IOW

IOW

Sygnały

Sygnały

sterujące

sterujące

dla pamięci

dla pamięci

Sygnały sterujące

Sygnały sterujące

dla

dla

układów we/wy

układów we/wy

Np. sterownik

Np. sterownik

dysku twardego

dysku twardego

UKŁDY WEJŚCIA/WYJŚCIA IZOLOWANE

UKŁDY WEJŚCIA/WYJŚCIA IZOLOWANE

Operacjami

wejścia/wyjścia

nazywamy

całokształt

działań

potrzebnych

do

realizacji

wymiany

informacji

pomiędzy

mikroprocesorem i pamięcią z jednej strony a układem

wejścia/wyjścia z drugiej.

Operacjami

wejścia/wyjścia

nazywamy

całokształt

działań

potrzebnych

do

realizacji

wymiany

informacji

pomiędzy

mikroprocesorem i pamięcią z jednej strony a układem

wejścia/wyjścia z drugiej.

OPERACJE WEJŚCIA/WYJŚCIA

OPERACJE WEJŚCIA/WYJŚCIA

Operacje wejścia/wyjścia mogą być realizowane:

Operacje wejścia/wyjścia mogą być realizowane:

od początku do końca przy udziale procesora -

od początku do końca przy udziale procesora -

przesyłana informacja przepływa przez rejestry

przesyłana informacja przepływa przez rejestry

procesora, który także steruje każdym krokiem

procesora, który także steruje każdym krokiem

realizacji operacji - są to

realizacji operacji - są to

operacje z bezpośrednim

operacje z bezpośrednim

sterowaniem przez mikroprocesor

sterowaniem przez mikroprocesor

poprzez zainicjowanie operacji przez procesor, który

poprzez zainicjowanie operacji przez procesor, który

następnie przekazuje nadzór nad realizacją operacji

następnie przekazuje nadzór nad realizacją operacji

innemu układowi (zarządcy magistrali) - są to

innemu układowi (zarządcy magistrali) - są to

operacje

operacje

z pośrednim sterowaniem przez mikroprocesor (z

z pośrednim sterowaniem przez mikroprocesor (z

bezpośrednim dostępem do pamięci - DMA)

bezpośrednim dostępem do pamięci - DMA)

.

.

Bezwarunkową operacją wejścia/wyjścia nazywamy taką operację,

przy realizacji której mikroprocesor nie sprawdza gotowości

układu wejścia/wyjścia do tej wymiany. Są to operacje

najprostsze realizowane tylko w niektórych przypadkach np.

przesłanie sygnału do wyświetlania informacji za pomocą

zestawu diod elektroluminescencyjnych.

Bezwarunkową operacją wejścia/wyjścia nazywamy taką operację,

przy realizacji której mikroprocesor nie sprawdza gotowości

układu wejścia/wyjścia do tej wymiany. Są to operacje

najprostsze realizowane tylko w niektórych przypadkach np.

przesłanie sygnału do wyświetlania informacji za pomocą

zestawu diod elektroluminescencyjnych.

Przy realizacji operacji wejścia/wyjścia z testowaniem stanu

układu wejścia/wyjścia, mikroprocesor sprawdza sygnał (np.

określony bit kontrolny) gotowości układu do wymiany. W

przypadku potwierdzenia gotowości do wymiany przez układ jest

ona realizowana. Operacje te są stosowane np. przy współpracy z

przetwornikiem a/c - procesor cyklicznie przepytuje przetwornik

(tzw. pętla przepytywania) do chwili uzyskania zgłoszenia

gotowości.

Przy realizacji operacji wejścia/wyjścia z testowaniem stanu

układu wejścia/wyjścia, mikroprocesor sprawdza sygnał (np.

określony bit kontrolny) gotowości układu do wymiany. W

przypadku potwierdzenia gotowości do wymiany przez układ jest

ona realizowana. Operacje te są stosowane np. przy współpracy z

przetwornikiem a/c - procesor cyklicznie przepytuje przetwornik

(tzw. pętla przepytywania) do chwili uzyskania zgłoszenia

gotowości.

OPERACJE Z BEZPOŚREDNIM

OPERACJE Z BEZPOŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR

MIKROPROCESOR

Operacje wejścia/wyjścia z bezpośrednim sterowaniem

Operacje wejścia/wyjścia z bezpośrednim sterowaniem

przez mikroprocesor :

przez mikroprocesor :

bezwarunkowe operacje wejścia/wyjścia

bezwarunkowe operacje wejścia/wyjścia

operacje z testowaniem stanu układu wejścia/wyjścia

operacje z testowaniem stanu układu wejścia/wyjścia

operacje z przerwaniem programu

operacje z przerwaniem programu

OPERACJE Z PRZERWANIEM PROGRAMU

OPERACJE Z PRZERWANIEM PROGRAMU

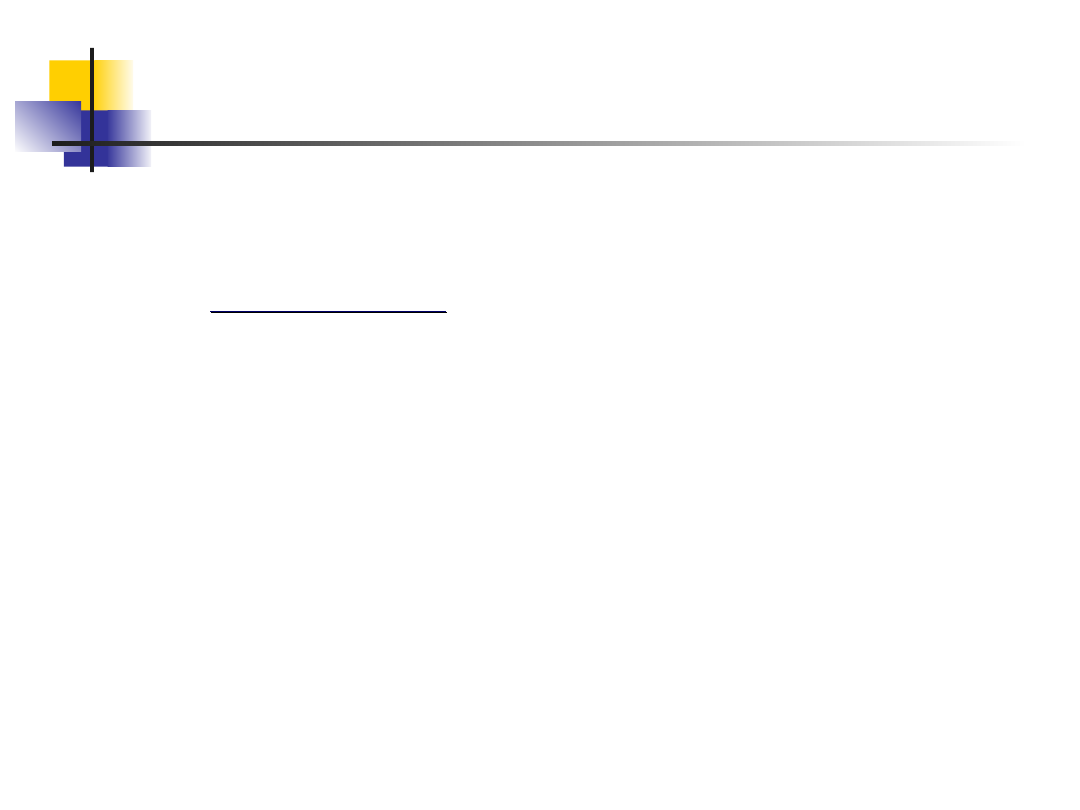

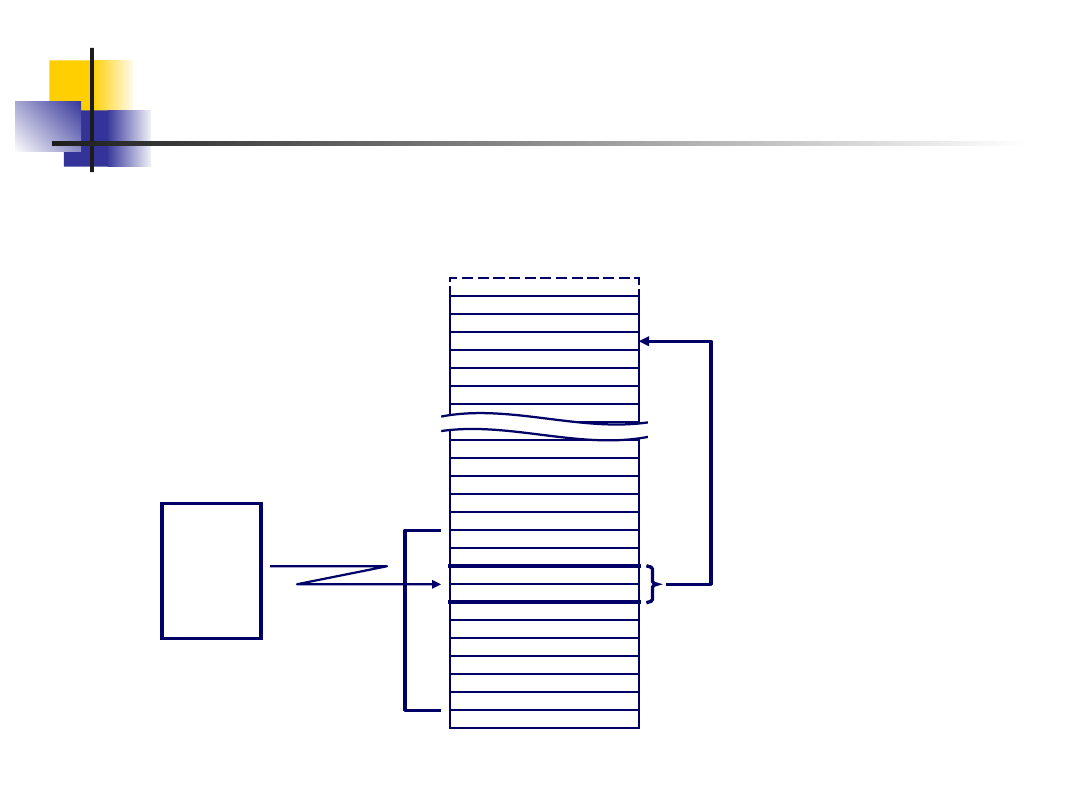

Operacje wejścia/wyjścia z przerwaniem programu eliminują wady operacji z

Operacje wejścia/wyjścia z przerwaniem programu eliminują wady operacji z

testowaniem stanu układu.

testowaniem stanu układu.

Procesor wykonuje

Procesor wykonuje

program główny

program główny

oczekując na zgłoszenie gotowości.

oczekując na zgłoszenie gotowości.

Zgłoszenie

powoduje

przerwanie

wykonywania

programu

głównego

i

Zgłoszenie

powoduje

przerwanie

wykonywania

programu

głównego

i

zapamiętanie informacji potrzebnej do późniejszego powrotu do programu

zapamiętanie informacji potrzebnej do późniejszego powrotu do programu

głównego. Procesor przechodzi do wykonania

głównego. Procesor przechodzi do wykonania

programu obsługi przerwań

programu obsługi przerwań

(

(

ISR -

ISR -

interrupt service routine

interrupt service routine

) - następuje wymiana informacji z układem we/wy. Po

) - następuje wymiana informacji z układem we/wy. Po

zakończeniu wymiany (programu obsługi przerwania) procesor kontynuuje

zakończeniu wymiany (programu obsługi przerwania) procesor kontynuuje

przerwany program główny.

przerwany program główny.

INSTRUKCJA 1

INSTRUKCJA 1

INSTRUKCJA 2

INSTRUKCJA 2

INSTRUKCJA 3

INSTRUKCJA 3

INSTRUKCJA 4

INSTRUKCJA 4

INSTRUKCJA 11

INSTRUKCJA 11

INSTRUKCJA 12

INSTRUKCJA 12

INSTRUKCJA 5

INSTRUKCJA 5

INSTRUKCJA 6

INSTRUKCJA 6

INSTRUKCJA 7

INSTRUKCJA 7

INSTRUKCJA 8

INSTRUKCJA 8

INSTRUKCJA 9

INSTRUKCJA 9

RET 10

RET 10

Program główny

Zgłoszenie

przerwania

Odtworzenie

stanu

rejestrów

procesora

Początek

programu obsługi

przerwania

Zapamiętanie

stanu

rejestrów

procesora

OPERACJE Z BEZPOŚREDNIM

OPERACJE Z BEZPOŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR

MIKROPROCESOR

OPERACJE Z PRZERWANIEM PROGRAMU

OPERACJE Z PRZERWANIEM PROGRAMU

W przypadku pojawienia się jednoczesnego kilku zgłoszeń od

W przypadku pojawienia się jednoczesnego kilku zgłoszeń od

urządzeń we/wy sytuacja może się komplikować. Dlatego stosuje się

urządzeń we/wy sytuacja może się komplikować. Dlatego stosuje się

tzw.

tzw.

sterownik przerwań

sterownik przerwań

.

.

Główne zadania sterownika przerwań:

Główne zadania sterownika przerwań:

•

pośredniczenie w przyjmowaniu zgłoszeń przerwań pomiędzy

pośredniczenie w przyjmowaniu zgłoszeń przerwań pomiędzy

procesorem i układami we/wy

procesorem i układami we/wy

•

przyjmowanie zgłoszeń od wielu układów we/wy (procesor

przyjmowanie zgłoszeń od wielu układów we/wy (procesor

posiada tylko jedno wejście zgłoszenia przerwań)

posiada tylko jedno wejście zgłoszenia przerwań)

•

wybór spośród wielu zgłoszeń tego, które zostanie obsłużone

wybór spośród wielu zgłoszeń tego, które zostanie obsłużone

•

sygnalizowanie wyboru przez podanie adresu układu we/wy, z

sygnalizowanie wyboru przez podanie adresu układu we/wy, z

którym zostanie dokonana wymiana (adresu programu obsługi

którym zostanie dokonana wymiana (adresu programu obsługi

przerwania realizującego tą wymianę, a właściwie numer

przerwania realizującego tą wymianę, a właściwie numer

pozycji w

pozycji w

tablicy wektorów przerwań

tablicy wektorów przerwań

)

)

•

wygenerowanie sygnału zgłoszenia przerwania bezpośrednio

wygenerowanie sygnału zgłoszenia przerwania bezpośrednio

do procesora

do procesora

OPERACJE Z BEZPOŚREDNIM

OPERACJE Z BEZPOŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR

MIKROPROCESOR

OPERACJE Z PRZERWANIEM PROGRAMU - TABLICA WEKTORÓW

OPERACJE Z PRZERWANIEM PROGRAMU - TABLICA WEKTORÓW

PRZERWAŃ

PRZERWAŃ

Początek IRS

Początek IRS

CS

CS

IP

IP

CS

CS

IP

IP

CS

CS

IP

IP

Pamięć

Pamięć

operacyjna

operacyjna

Numer

przerwania

Adres

Adres

początku

początku

programu

programu

obsługi

obsługi

przerwania

przerwania

Tablica

Tablica

wektoró

wektoró

w

w

przerwa

przerwa

ń

ń

CS

CS

IP

IP

CS

CS

IP

IP

Sterowni

Sterowni

k

k

przerwań

przerwań

OPERACJE Z BEZPOŚREDNIM

OPERACJE Z BEZPOŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR

MIKROPROCESOR

Tablica wektorów przerwań

Tablica wektorów przerwań

zajmuje obszar pierwszego kilobajta pamięci

zajmuje obszar pierwszego kilobajta pamięci

operacyjnej:

operacyjnej:

256 wektorów przerwań x 4 bajty dla jednego wektora

256 wektorów przerwań x 4 bajty dla jednego wektora

Adresy programów obsługi przerwań są wpisywane do tablicy wektorów

Adresy programów obsługi przerwań są wpisywane do tablicy wektorów

przerwań podczas ładowania systemu operacyjnego przez BIOS i przez system

przerwań podczas ładowania systemu operacyjnego przez BIOS i przez system

operacyjny.

operacyjny.

Przerwania obsługiwane przez BIOS (32 przerwania) mają numery: od 0 do 1FH.

Przerwania obsługiwane przez BIOS (32 przerwania) mają numery: od 0 do 1FH.

Pozostałe są obsługiwane przez system operacyjny (część jednak przeznaczona

Pozostałe są obsługiwane przez system operacyjny (część jednak przeznaczona

jest na potrzeby użytkownika).

jest na potrzeby użytkownika).

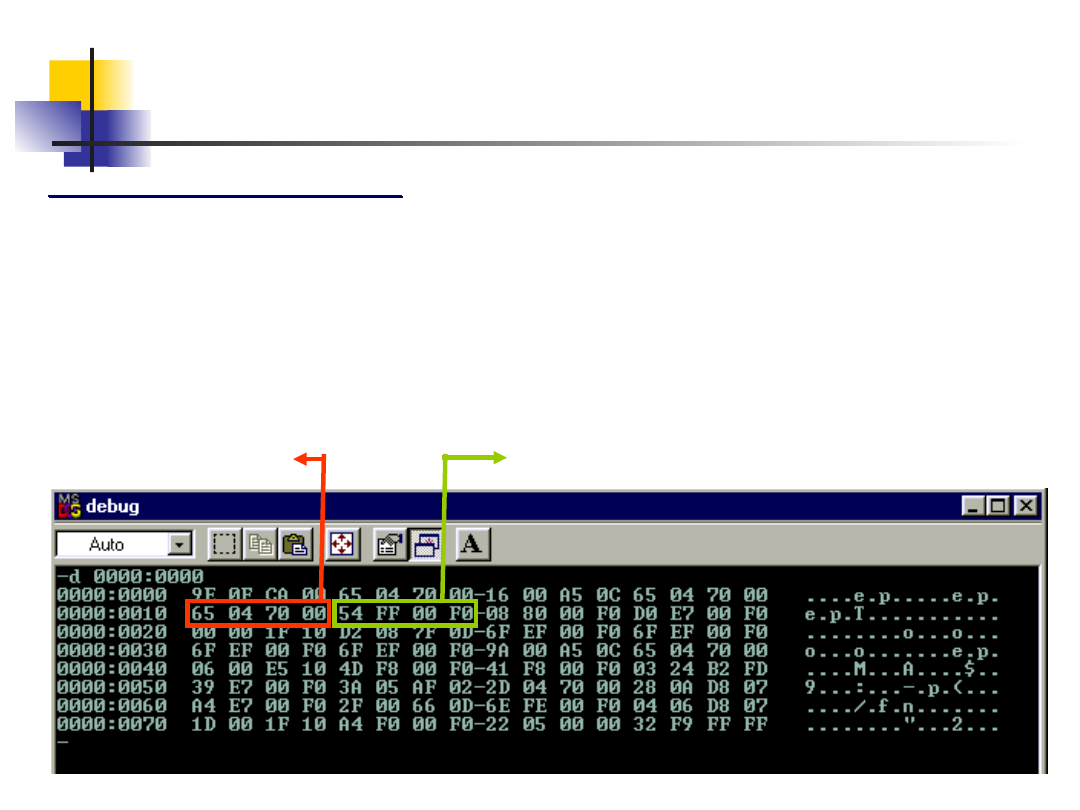

Za pomocą programu DEBUG można obejrzeć tablicę wektorów przerwań.

Za pomocą programu DEBUG można obejrzeć tablicę wektorów przerwań.

Adres piątego wektora

Adres piątego wektora

INT5H

INT5H

CS=F000, IP=FF54

CS=F000, IP=FF54

Adres piątego wektora

Adres piątego wektora

INT5H

INT5H

CS=F000, IP=FF54

CS=F000, IP=FF54

Zobaczmy przykładowo pierwsze 32 wektory (zapis zgodny z przechowywaniem

Zobaczmy przykładowo pierwsze 32 wektory (zapis zgodny z przechowywaniem

odwrotnym)

odwrotnym)

Adres czwartego wektora

Adres czwartego wektora

INT4H

INT4H

CS=0070, IP=0465

CS=0070, IP=0465

OPERACJE Z BEZPOŚREDNIM

OPERACJE Z BEZPOŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR

MIKROPROCESOR

OPERACJE Z PRZERWANIEM PROGRAMU - TABLICA WEKTORÓW

OPERACJE Z PRZERWANIEM PROGRAMU - TABLICA WEKTORÓW

PRZERWAŃ

PRZERWAŃ

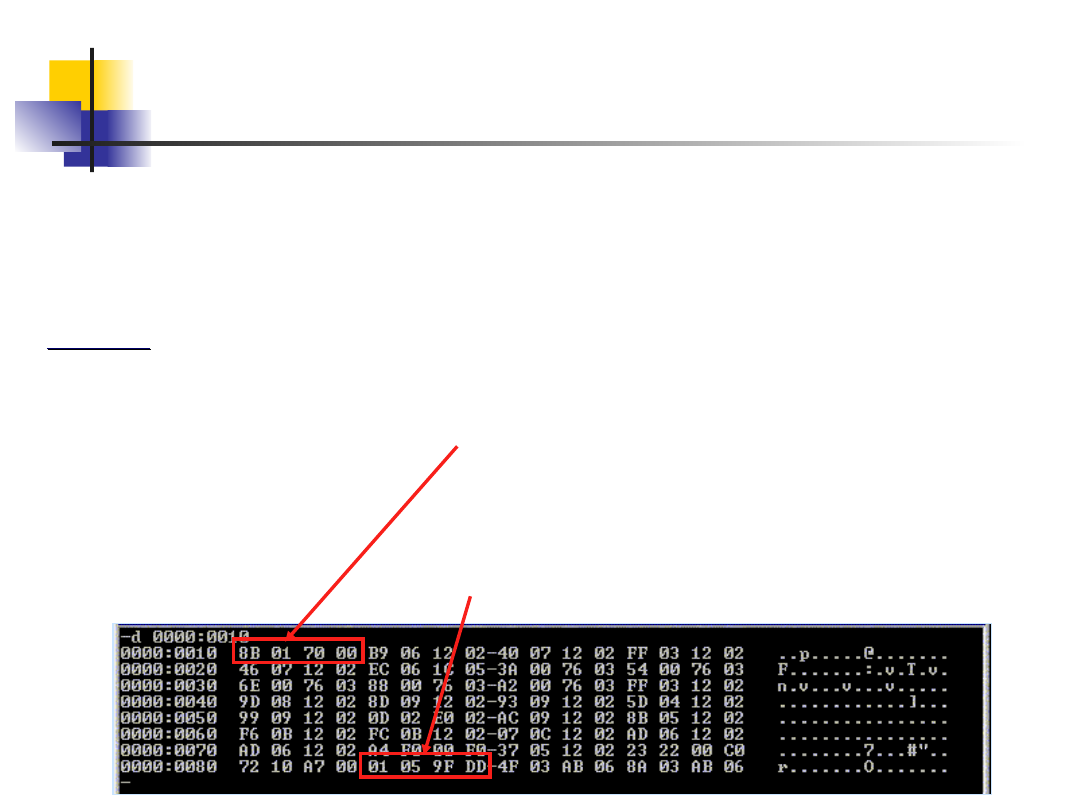

Istnieje pewna reguła obliczania adresów wektora przerwań:

Istnieje pewna reguła obliczania adresów wektora przerwań:

adres_początku

adres_początku

= numer_przerwania x 4

= numer_przerwania x 4

adres_końca

adres_końca

= adres_początku + 3

= adres_początku + 3

Należy pamiętać, że w tablicy wektorów przerwań wektor zajmuje 4 bajty i

Należy pamiętać, że w tablicy wektorów przerwań wektor zajmuje 4 bajty i

wektory liczone są od zera

wektory liczone są od zera

2. Obliczyć adresy dla przerwania INT 21H

2. Obliczyć adresy dla przerwania INT 21H

początek: 21H x 4 = 84H

początek: 21H x 4 = 84H

koniec: 84H + 3 = 87H

koniec: 84H + 3 = 87H

czyli w pamięci operacyjnej obszar 0000:0084 do 0000:0087

czyli w pamięci operacyjnej obszar 0000:0084 do 0000:0087

przeznaczony jest na wektor przerwania 21H

przeznaczony jest na wektor przerwania 21H

Przykład

Przykład

:

:

1. Obliczyć adresy dla przerwania INT 4H

1. Obliczyć adresy dla przerwania INT 4H

początek: 4H x 4 = 10H

początek: 4H x 4 = 10H

koniec: 10H+3 = 13H

koniec: 10H+3 = 13H

czyli w pamięci operacyjnej obszar 0000:0010 do 0000:0013

czyli w pamięci operacyjnej obszar 0000:0010 do 0000:0013

przeznaczony jest na wektor przerwania 4H

przeznaczony jest na wektor przerwania 4H

OPERACJE Z BEZPOŚREDNIM

OPERACJE Z BEZPOŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR

MIKROPROCESOR

OPERACJE Z PRZERWANIEM PROGRAMU - TABLICA WEKTORÓW

OPERACJE Z PRZERWANIEM PROGRAMU - TABLICA WEKTORÓW

PRZERWAŃ

PRZERWAŃ

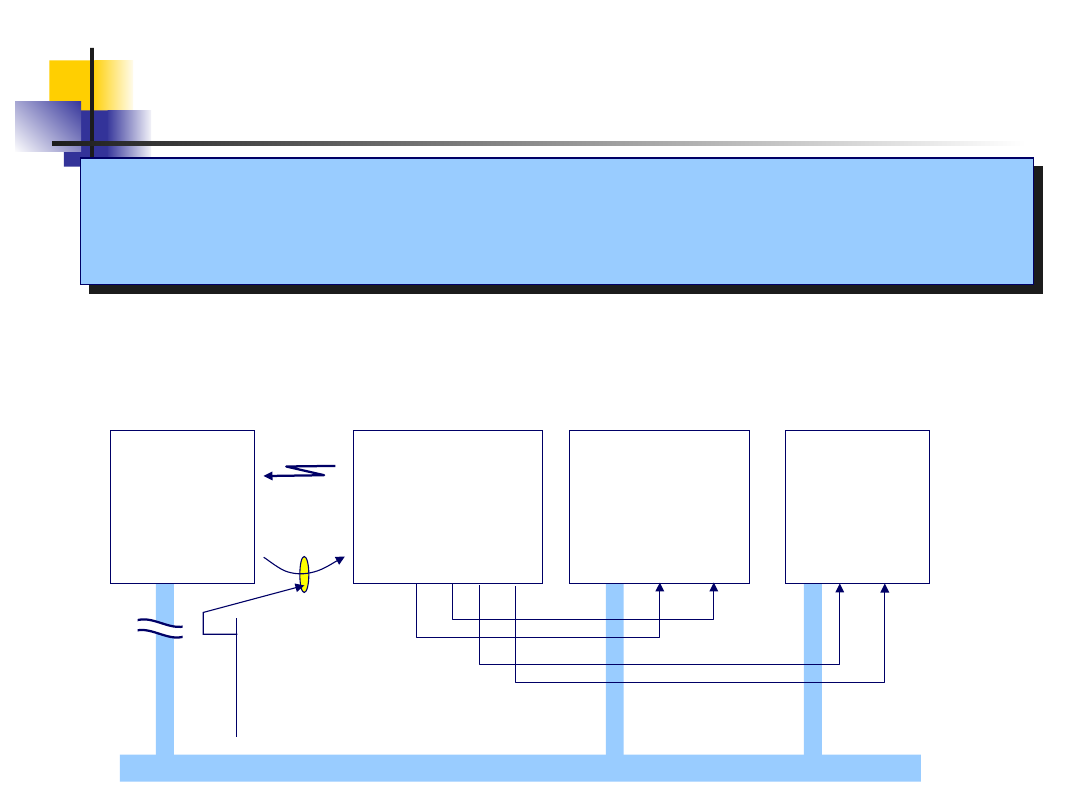

Operacje wejścia/wyjścia polegające na inicjowaniu operacji przez

procesor i przekazaniu sterowania specjalizowanemu układowi

zwanemu sterownikiem DMA (direct memory access) nazywamy

operacją o bezpośrednim dostępie do pamięci.

Operacje wejścia/wyjścia polegające na inicjowaniu operacji przez

procesor i przekazaniu sterowania specjalizowanemu układowi

zwanemu sterownikiem DMA (direct memory access) nazywamy

operacją o bezpośrednim dostępie do pamięci.

W operacji DMA transmisja informacji przebiega pomiędzy układem we/wy a wydzielonym

W operacji DMA transmisja informacji przebiega pomiędzy układem we/wy a wydzielonym

obszarem pamięci pod kontrolą sterownika DMA. Po zgłoszeniu żądania przejęcia kontroli nad

obszarem pamięci pod kontrolą sterownika DMA. Po zgłoszeniu żądania przejęcia kontroli nad

magistralami (za pomocą sygnału HOLD) procesor inicjuje operację i przechodzi w stan

magistralami (za pomocą sygnału HOLD) procesor inicjuje operację i przechodzi w stan

zawieszenia (odseparowanie się od magistral). Po zakończeniu transmisji sterownik DMA

zawieszenia (odseparowanie się od magistral). Po zakończeniu transmisji sterownik DMA

zwraca procesorowi kontrolę nad magistralami.

zwraca procesorowi kontrolę nad magistralami.

Szyna adresowa

Szyna adresowa

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

STEROWNI

STEROWNI

K DMA

K DMA

I/O

I/O

MEMR

MEMR

MEMW

MEMW

MEMR MEMW

MEMR MEMW

IOR IOW

IOR IOW

IOR

IOR

IOW

IOW

CPU

CPU

HOLD

HOLD

Inicjowanie

Inicjowanie

operacji

operacji

Określa:

Określa:

•

wielkość bloku do transmisji

wielkość bloku do transmisji

•

sposób transmisji (blokowa,

sposób transmisji (blokowa,

pojedynczymi słowami, na

pojedynczymi słowami, na

żądanie)

żądanie)

•

adres pierwszej komórki

adres pierwszej komórki

bufora pamięci

bufora pamięci

•

rodzaj operacji (zapis, odczyt)

rodzaj operacji (zapis, odczyt)

zawieszenie

zawieszenie

OPERACJE Z POŚREDNIM

OPERACJE Z POŚREDNIM

STEROWANIEM PRZEZ

STEROWANIEM PRZEZ

MIKROPROCESOR (DMA)

MIKROPROCESOR (DMA)

DZIĘKUJĘ ZA UWAGĘ !

DZIĘKUJĘ ZA UWAGĘ !

Sytuacjami wyjątkowymi w pracy procesora nazywamy zaprzestanie wykonania

Sytuacjami wyjątkowymi w pracy procesora nazywamy zaprzestanie wykonania

aktualnie wykonywanego programu po zakończeniu cyklu instrukcyjnego (lub w

aktualnie wykonywanego programu po zakończeniu cyklu instrukcyjnego (lub w

trakcie cyklu w przypadku niektórych instrukcji operujących na łańcuchach) i

trakcie cyklu w przypadku niektórych instrukcji operujących na łańcuchach) i

przekazanie sterowania do podprogramu obsługi (tzw. handlera) tej sytuacji

przekazanie sterowania do podprogramu obsługi (tzw. handlera) tej sytuacji

znajdującego się pod adresem, który nie wynika z aktualnie wykonywanej

znajdującego się pod adresem, który nie wynika z aktualnie wykonywanej

instrukcji.

instrukcji.

Sytuacje wyjątkowe dzielimy na dwie grupy:

Sytuacje wyjątkowe dzielimy na dwie grupy:

1. powstałe w wyniku działania programu wykonywanego przez procesor

1. powstałe w wyniku działania programu wykonywanego przez procesor

2. pochodzące z układów współpracujących z procesorem

2. pochodzące z układów współpracujących z procesorem

•

zdarzenia niezamierzone (tzw. wyjątki procesora)

zdarzenia niezamierzone (tzw. wyjątki procesora)

–

błąd adresowania

błąd adresowania

–

błąd instrukcji

błąd instrukcji

–

błąd argumentu

błąd argumentu

•

zdarzenia zamierzone

zdarzenia zamierzone

–

praca krokowa

praca krokowa

–

praca w trybie śledzenia

praca w trybie śledzenia

–

przerwania programowe

przerwania programowe

•

błędy wykryte w urządzeniach komputera

błędy wykryte w urządzeniach komputera

–

błąd magistrali

błąd magistrali

–

błąd transmisji

błąd transmisji

–

błąd zasilania

błąd zasilania

•

zdarzenia służące do synchronizacji pracy procesora z urządzeniami

zdarzenia służące do synchronizacji pracy procesora z urządzeniami

znacznie wolniejszymi, które informują procesor o gotowości do pracy (tzw.

znacznie wolniejszymi, które informują procesor o gotowości do pracy (tzw.

przerwania sprzętowe IRQ)

przerwania sprzętowe IRQ)

»

Architektura klasycznego komputera (wg von Neumana) opiera się na założeniach:

Architektura klasycznego komputera (wg von Neumana) opiera się na założeniach:

–

program wykonywany przez procesor wraz z danymi jest umieszczony w pamięci;

program wykonywany przez procesor wraz z danymi jest umieszczony w pamięci;

–

kolejność wykonywanych rozkazów zależy od ich umieszczenia w programie (w

kolejność wykonywanych rozkazów zależy od ich umieszczenia w programie (w

kolejnych komórkach pamięci), a zmiana tej zasady może być wykonana tylko:

kolejnych komórkach pamięci), a zmiana tej zasady może być wykonana tylko:

•

przez program (rozkaz skoku);

przez program (rozkaz skoku);

•

przez system operacyjny np. wykrycie błędu;

przez system operacyjny np. wykrycie błędu;

•

przez operatora np.

przez operatora np.

reset

reset

–

procesor odczytuje kolejne rozkazy z pamięci wysyłając odpowiednie adresy

procesor odczytuje kolejne rozkazy z pamięci wysyłając odpowiednie adresy

OBSŁUGA SYTUACJI WYJĄTKOWYCH

OBSŁUGA SYTUACJI WYJĄTKOWYCH

(PRZERWANIA)

(PRZERWANIA)

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

Wyszukiwarka

Podobne podstrony:

architektura sk 05

architektura sk 01

architektura sk 04

architektura sk 03

architektura sk 08

architektura sk 09

architektura sk 07

architektura sk 13

architektura sk 06

architektura sk 11

architektura sk 02

architektura sk 12

architektura sk 05

Historia architektury i sztuki (10 10 2009)

Historia architektury i sztuki 10 10 09

architektura sk 01

Architektura i Biznes 10 2001 – Katalog Czasopism

9,10 Modele rastrowych i wektorowych danych w SIP,Mozliwosci wykorzystania SIP w architekturze krajo

wykład 10, Ochrona Środowiska, Ekologia i architektura krajobrazu

więcej podobnych podstron