Jaros

ław W. Kłos

Architektura komputer

ó w i programowanie niskopoziomowe

Laboratorium

Pozna

ń 2005

1. Wprowadzenie

2. Budowa mikrokontrolera 8051 i systemu DSM-51

2.1. Mikrokontroler 8051

2.1.1. CPU, podstawowe rejestry

2.1.2. Pamię ć

2.1.3. Cykl rozkazowy

2.1.4. Zintegrowane ukł

ady peryferyjne

2.1.5. Przerwania

2.1.6. Przeglą d instrukcji

2.1.7. Tryby adresowania

2.2. Budowa i obsł

uga systemu DSM-51

2.2.1. Tryby pracy i organizacja pamię ci zewnę trznej w systemie DSM-51

2.2.2. Ukł

ady systemu DSM-51

3. Asembler mikrokontrolera 8051

3.1. Podstawy programowania mikrokontrolera 8051 w systemie DSM-51

3.1.1. Skł

adnia pliku ź ródł

owego

3.1.2. Proces asemblacji

3.1.3. Dyrektywy asemblera i literał

y

3.1.4. Wywoł

ywanie podprogramów EPROMu

3.1.5. Pierwszy program

3.1.6. Pę tle

3.1.7. Rozgał

ę zienia

3.2. Pamię ć

3.2.1. Pamię ć wewnę trzna

•

Rejestry specjalne

•

Banki rejestrów

•

Stos

•

Bity adresowanie bezpośrednio

3.2.2. Pamię ć programu

3.2.1. Obsł

uga tablic w pamię ci programu

3.2.3. Pamię ć zewnę trzna

3.2.4. Obsł

uga urzą dzeń wejścia – wyjścia

3.3. Stos i podprogramy

3.3.1. Modularyzacja programu

•

Interfejs podprogramu

•

Korzystanie z zasobów mikrokontrolera wewną trz podprogramu

3.3.2. Rola stosu przy wywoł

aniu i powrocie z podprogramu

3.3.3. Rekurencja

3.4. Operacje arytmetyczne i logiczne

3.4.1. Reprezentacje liczbowe

•

Liczby NB

•

Liczby U2

•

Reprezentacja BCD

3.4.2. Operacje arytmetyczne

•

Dodawanie i odejmowanie liczb NB i U2 – flagi C i OV

•

Dodawanie i odejmowanie liczb BCD – flaga AV i poprawka dziesię tna

•

Mnożenie i dzielenie

•

Konwersje liczbowe

•

Rotacje

•

Dodawanie i odejmowanie liczb wielobajtowych

•

Operacje na tablicach

3.4.3. Operacje logiczne

•

Suma i iloczyn logiczny

•

Negacja i suma bitowa modulo dwa

•

Stosowanie masek

•

Operacje logiczne na bitach

4. Zintegrowane układy peryferyjne mikrokontrolera 8051

4.1. Porty

4.2. Ukł

ady czasowe

4.3. Sterownik transmisja szeregowej

4.4. Przerwania

5. Układy we-wy w systemie DSM-51

5.1. klawiatura matrycowa

5.2. klawiatura sekwencyjna

5.3. wyświetlacze 7-segmentowe

5.4. wyświetlacz LDC

5.5. port równoległ

y

Dodatki:

A. Lista rozkazów mikrokontrolera 8051

B. Rozkazy zmieniają ce stan flag

C. Dyrektywy asemblera

D. Rejestry specjalne

E. Podprogramy EPROMu w systemie DSM-51

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

1

1.

Wprowadzenie

Skrypt ten powstał

jako materiał

uzupeł

niają cy do zaję ć laboratoryjnych z Architektury

komputeró w i programowania niskopoziomowego prowadzonych na Wydziale Fizyki UAM.

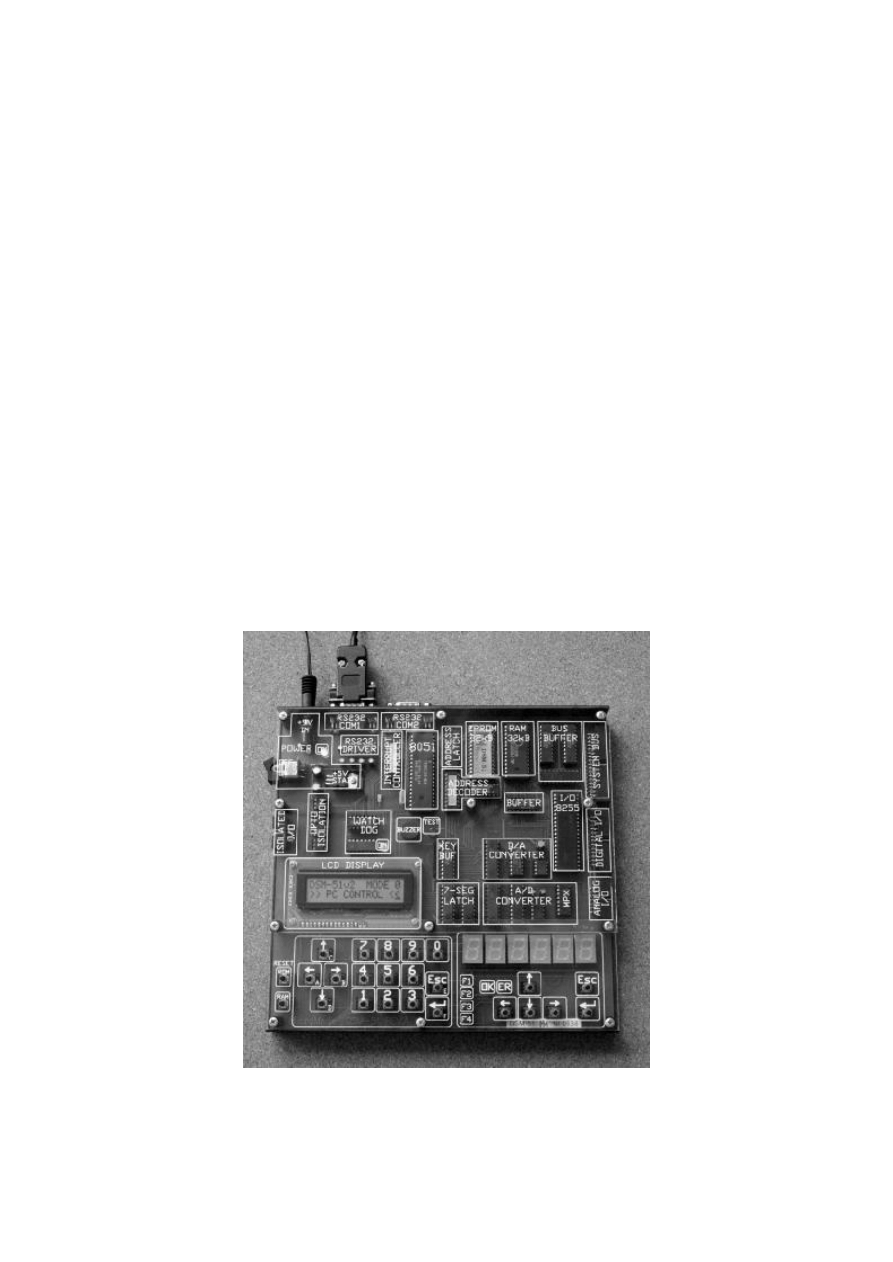

Ć wiczenia prowadzone są z wykorzystaniem Dydaktycznego Systemu Mikroprocesorowego

DSM-51, którego sercem jest mikrokontroler rodziny 8051. Gł

ównym celem tych zaję ć jest

zapoznanie studentów z podstawami programowania niskopoziomowego oraz z budową i

obsł

ugą elementów systemu mikroprocesorowego. Szczególny nacisk poł

ożony jest na

poznanie dział

ania ukł

adów peryferyjnych.

Wybór mikrokontrolera 8051 podyktowany był

prostotą jego budowy i obsł

ugi.

Opanowanie asemblera 8051 i zrozumienie dział

ania prostego systemu mikroprocesorowego

nie przysparza studentom szczególnych trudności. Prostota asemblera 8051 nie jest tu

ograniczeniem, gdyż oddaje najważniejsze i wspólne cechy wię kszości asemblerów bardziej

zł

ożonych procesorów. Ograniczoność zasobów i uboga lista rozkazów wymuszają oszczę dne

korzystanie z pamię ci i rejestrów oraz kształ

tują dobre nawyki programistyczne –

implementacja algorytmów jest tu trudniejsza i wymaga umieję tnego wykorzystania

dostę pnych rozkazów.

W pierwszej czę ści skryptu zarysowano budowę mikrokontrolerów rodziny 8051 oraz

systemu DSM-51. W kolejnym rozdziale przedstawiono podstawy asemblera 8051.

Omówiono: instrukcje i struktury sterują ce przebiegiem programu, tryby adresowania i

rozkazy przesł

ań , pamię ć w systemie mikrokontrolera 8051, obsł

ugę stosu i wykorzystanie

podprogramów; rozdział

zakoń czono opisem instrukcji logicznych i arytmetycznych.

Nastę pnie zamieszczono opis zintegrowanych ukł

adów peryferyjnych mikrokontrolera 8051

oraz przedstawiono system przerwań . Ostatni rozdział

zawiera omówienie wybranych

ukł

adów wejścia-wyjścia systemu DSM-51. W dodatkach zebrano: listę rozkazów

mikrokontrolera 8051, dyrektywy asemblera, mapę pamię ci i wykaz ważniejszych rejestrów

specjalnych oraz spis podprogramów EPROMu w systemie DSM-51.

Materiał

zawarty w skrypcie nie stanowi wyczerpują cej monografii poświę canej

mikrokontrolerowi 8051. Niniejsza praca nie przestawia również wszystkich niuansów

programowania niskopoziomowego. Zainteresowani studenci bę dą zmuszeni się gną ć po

specjalistyczną lekturę . Pomocą może tu posł

użyć zamieszczony w skrypcie spis pozycji

bibliograficznych. Skrypt napisano do ćwiczeń laboratoryjnych prowadzonych na Wydziale

w wymiarze 45 godzin. Stą d też autorzy zmuszeni byli do ograniczenia poruszanej w nim

tematyki i wyboru omawianych zagadnień ; mają jednak nadzieję , iż skrypt ten może być

pomocny w nauce podstaw programowania niskopoziomowego.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

2

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

3

2.

Budowa mikrokontrolera 8051 i systemu DSM-51

W niniejszy rozdział

jest skrótowym omówieniem budowy mikrokontrolera 8051 oraz

systemu DSM-51. Zawiera on podstawowe informacje, z którymi powinien zapoznać się

student przed przystą pieniem do nauki programowania mikrokontrolera i urzą dzeń systemu

DSM-51. W dalszych rozdział

ach, w trakcie nauki programowania, poruszane bę dą

zagadnienia szczegół

owe.

2.1. Mikrokontroler 8051

Przedstawione tu wiadomości, dotyczą ce mikrokontrolera 8051, mają charakter

wprowadzają cy. Ze wzglę du na to że, rozwią zania zastosowane w ukł

adach 8051 są typowe,

stą d poniższy opis można traktować jako ogólną charakterystykę szerokiej klasy

mikrokontrolerów. Mikrokontrolery rodziny 8051 wytarzane są przez wielu producentów w

dużej liczbie wariantów różnią cych się ilością i rodzajem wewnę trznej pamię ci programu

(sposobem jej programowania), ilością wewnę trznej pamię ci danych, typem zintegrowanych

ukł

adów peryferyjnych, liczbą ź ródeł

przerwań , dozwolonymi czę stotliwościami taktowania i

napię ciami zasilania. Przedstawiony niżej opis przedstawia rozwią zania najbardziej typowe,

wspólne dla wię kszości mikrokontrolerów tej rodziny. Zainteresowani szczegół

ami czytelnicy

zmuszeni bę dą się gną ć do pozycji cytowanych w bibliografii.

Termin mikrokontroler oznacza ukł

ad elektroniczny wysokiej skali integracji, który w

swojej strukturze zawiera:

•

mikroprocesor

•

pamię ć

•

urzą dzenia wejścia – wyjścia.

Mikrokontroler stanowi zatem, scalony w jednym ukł

adzie elektronicznym, autonomiczny

system mikroprocesorowy. Podł

ą czają c stosunkowo niewielka liczbę innych elementów

(takich jak czujniki, sygnalizatory, ukł

ady zasilania) można zbudować niewielkim kosztem w

peł

ni funkcjonalne urzą dzenie. Obecnie w wię kszości bardziej zaawansowanych ukł

adów

sterowania i automatyki stosuje się mikrokontrolery. Mikrokontrolery możemy znaleź ć

zarówno w urzą dzeniach gospodarstwa domowego (telewizory, pralki, kuchenki

mikrofalowe), w systemach kontroli czasu i dostę pu (bankomaty, parkomaty, czytniki kart),

jaki i w zastosowaniach przemysł

owych (urzą dzenia pomiarowe, kontrola i sterowanie

procesem technologicznym). Ta zaskakują ca powszechność mikrokontrolerów w różnego

rodzaju aplikacjach wynika z dużej elastyczności urzą dzenia opartego o scalony system

mikroprocesorowy. Dział

anie systemu określa tu program zał

adowany do pamię ci.

Mikrokontroler można zatem potraktować jako „czarną skrzynkę ” o określonej liczbie wejść i

wyjść, której funkcja wyznaczona jest nie tyle przez jej budowę lecz przez wykonywany

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

4

przez nią program. Ł adują c inny program można realizować inne funkcje na tej samej

platformie sprzę towej.

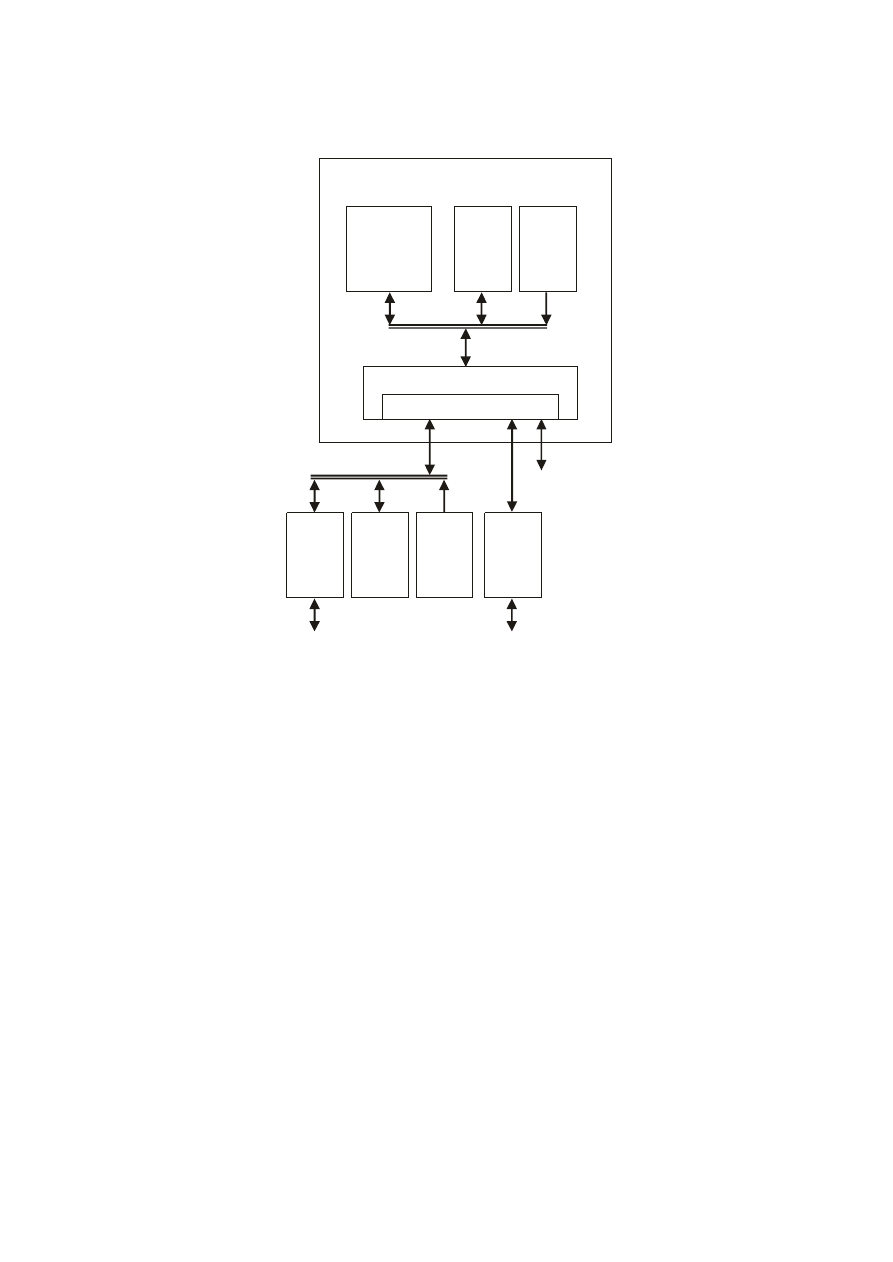

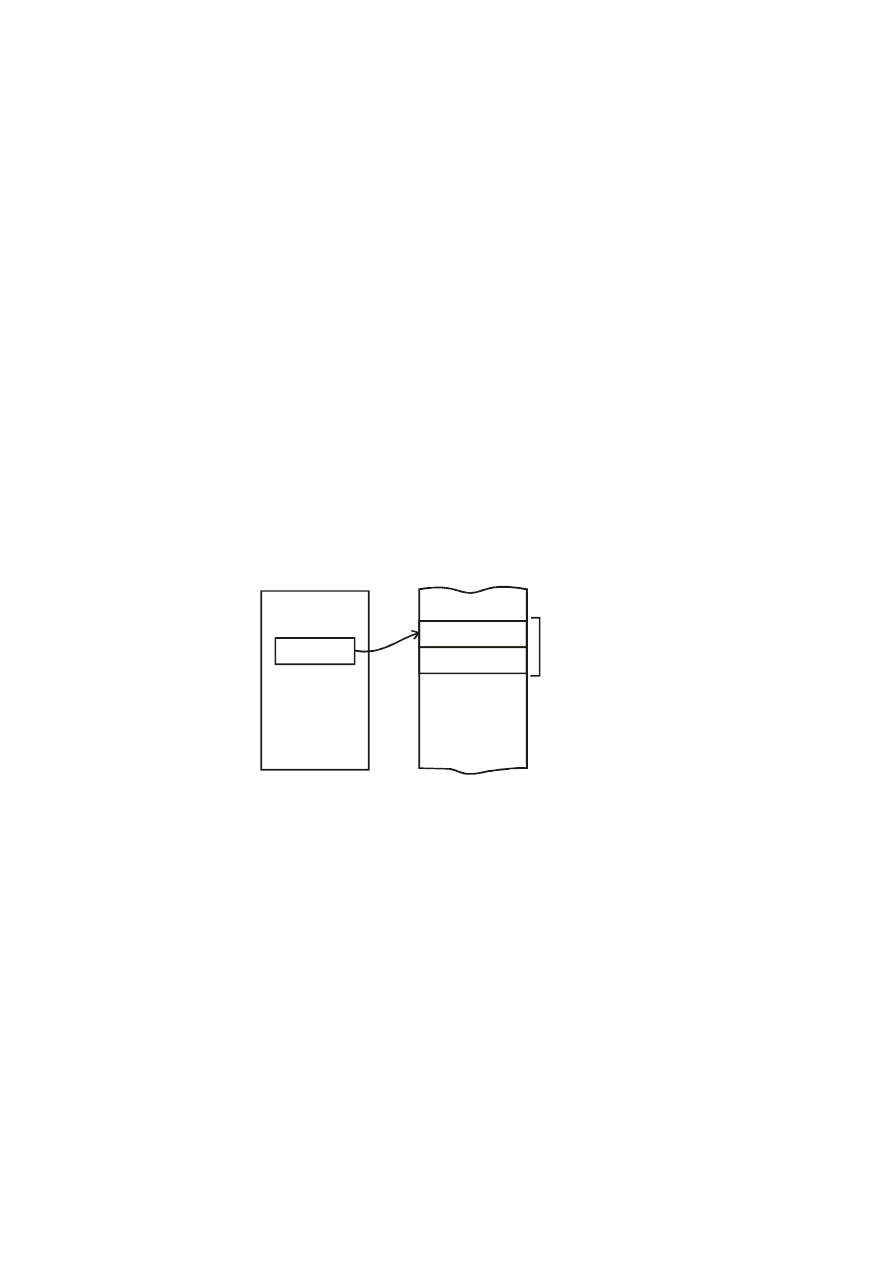

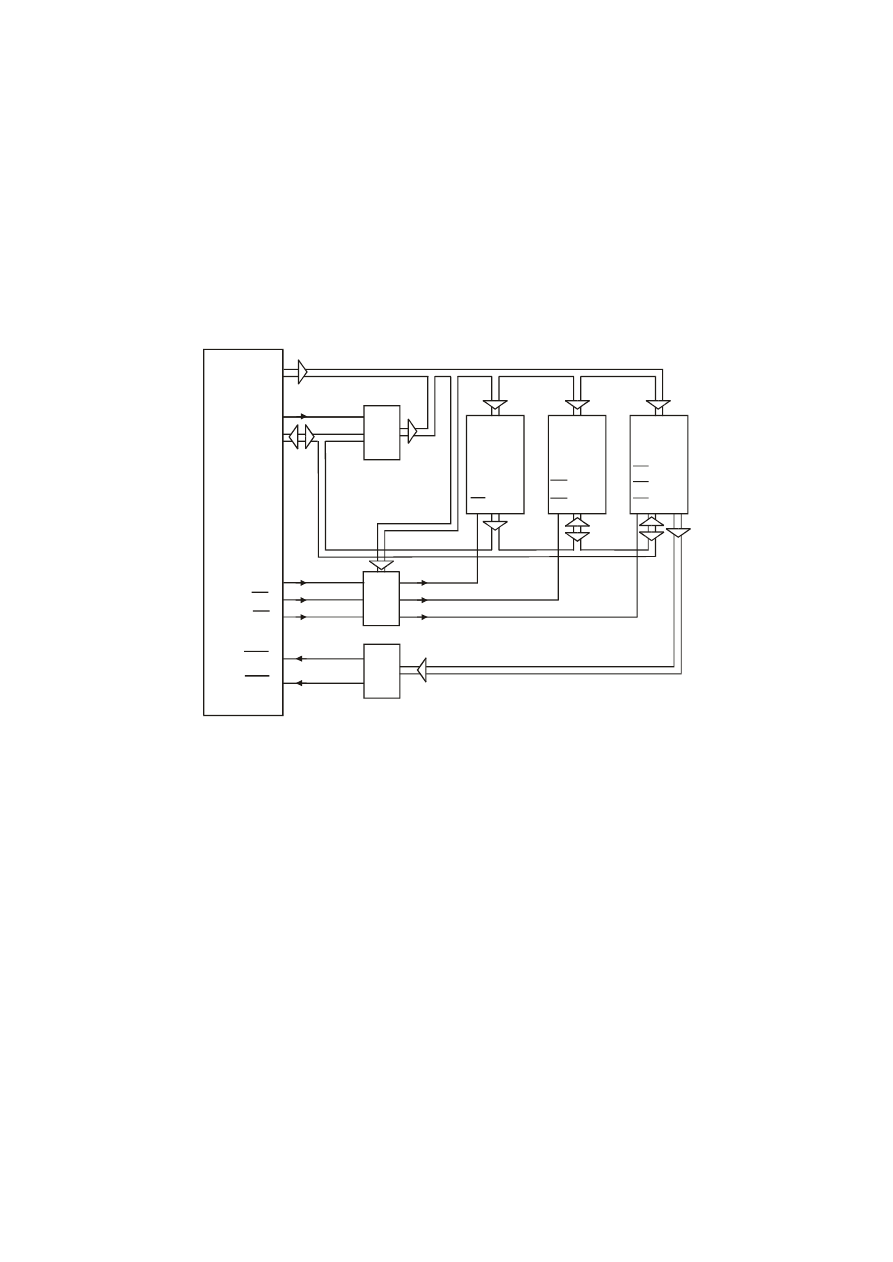

mikrokontroler

mikroprocesor

pami

ę ć

programu

pami

ę ć

danych

zintegrowane uk

łady wejś cia-wyjś cia

porty

pami

ę ć

programu

pami

ę ć

danych

uk

łady

wej

ś cia

wyj

ś cia

uk

łady

wej

ś cia

wyj

ś cia

magistarala wewn

ę trzna

magistarala zewn

ę trzna

Rys.1. Schemat blokowy mikrokontrolera.

Projektowanie urzą dzenia w oparciu o mikrokontrolery jest szczególnie wskazane w

nastę pują cych przypadkach:

•

budowa ukł

adu w oparciu o konwencjonalne ukł

ady logiczne jest nieopł

acalna

(Zaprojektowanie ukł

adu w oparciu o konwencjonalne ukł

ady logiczne może być

nieopł

acalne ze wzglę du na duża liczbę użytych podzespoł

ów i wysokie koszty

projektowania – sprzę towa implementacja pewnych funkcji może być bardzo trudna i

skomplikowana)

•

nie istnieje wyspecjalizowany ukł

ad realizują cy dane zadanie

(Na rynku istnieje wiele wysoko-wyspecjalizowanych ukł

adów elektronicznych. Nie

ma uzasadnienia projektowanie ukł

adu zegarka cyfrowego na bazie mikrokontrolera, o

ile nie jesteśmy zainteresowani jakimiś nietypowymi funkcjami)

•

szybkość dział

ania ukł

adu nie jest najważniejsza

(Dział

anie programu polega na wykonywaniu cią gu standardowych operacji –

instrukcji. Projektują c ukł

ad z konwencjonalnych ukł

adów logicznych, można

zbudować bloki funkcjonalne realizują ce bardziej wyspecjalizowane funkcje. Dzię ki

temu cał

y bę dzie dział

ał

efektywniej)

•

istotna jest ł

atwość wprowadzania zmian i ulepszeń

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

5

(W przypadku mikrokontrolera możliwa jest zmiana sposobu dział

ania urzą dzenia

poprzez zmianie programu zał

adowanego do mikrokontrolera)

•

urzą dzenie wykorzystuje urzą dzenia wejścia-wyjścia, które są zintegrowane w

mikrokontrolerze

(Stosują c mikrokontroler zawierają cy w swej strukturze wszystkie potrzebne w

projektowanym urzą dzeniu ukł

ady wejścia – wyjścia ograniczamy do minimum ilość

podzespoł

ów)

Sercem każdego mikrokontrolera jest mikroprocesor. Zasadniczymi elementami

mikroprocesora są :

•

jednostka arytmetyczno – logiczna

•

ukł

ady sterują ce

•

ukł

ad obsł

ugi przerwań

•

rejestry dostę pne programowo

Zadaniem jednostki arytmetyczno – logicznej (ALU), jak wskazuje nazwa, jest

wykonywanie operacji arytmetycznych takich jak: dodawanie, odejmowanie, mnożenie,

dzielenie oraz logicznych: negacja, suma i iloczyn logiczny. Lista dostę pnych operacji

arytmetyczno-logicznych jest określona dla danego typu mikroprocesora. Szczególną rolę ,

przy wykonywaniu operacji arytmetycznych i logicznych, peł

ni rejestr zwany akumulatorem

(A). Do akumulatora ł

adowany jest zwykle jeden z argumentów operacji. Ponadto najczę ściej

wynik operacji zapisywany jest również w akumulatorze.

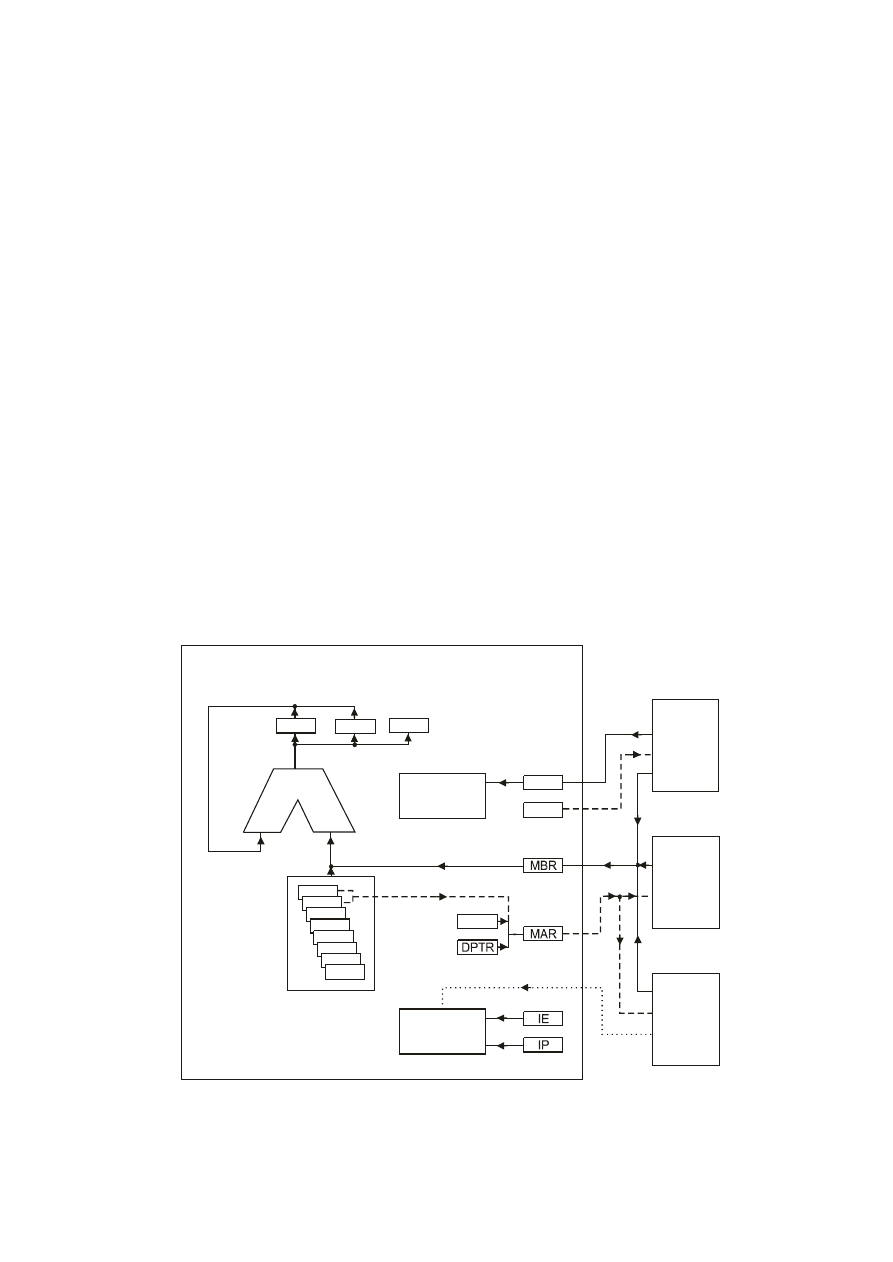

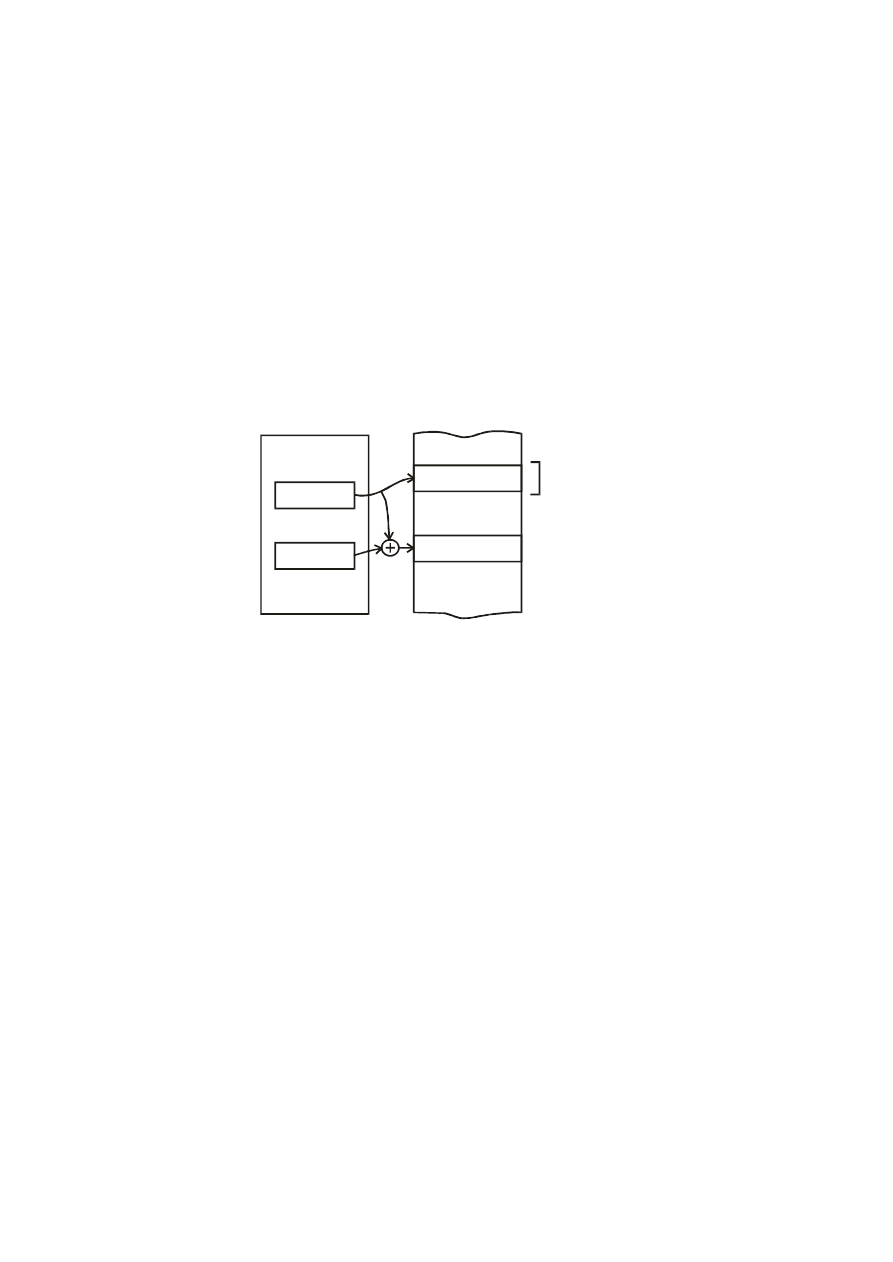

R0

R1

R2

R3

R4

R5

R6

R7

ALU

A

PSW

PC

IR

SP

dekoder

rozkaz

ó w

pami

ę ć

programu

uk

ład obsługi

przerwa

ń

pami

ę ć

danych

uk

łady

wej

ś cia

wyj

ś cia

B

mikroprocesor

Rys.2. Uproszczony schemat mikroprocesora układó w rodziny 8051. Linie ciągłe, kreskowane

i kropkowane oznaczają odpowiednio przesłania: danych, adresó w i sygnałó w sterujących.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

6

Ukł

ady sterują ce odpowiedzialne są za wymianę sygnał

ów sterują cych pomierzy

poszczególnymi elementami mikroprocesora w tzw. cyklu rozkazowym. Wykonywanie

programu polega na pobieraniu kolejnej instrukcji z pamię ci programu, interpretacji pobranej

instrukcji a nastę pnie jej wykonaniu. Adres komórki pamię ci programu pod którym

rozpoczyna się kod kolejnej instrukcji zawarty jest w liczniku rozkazów (PC). Każda

instrukcja ma przypisany unikatowy kod. Kod ten w fazie pobierania instrukcji zapisywany

jest do rejestru rozkazów (IR). Nastę pnie tzw. dekoder rozkazów na podstawie kodu rozkazu

wysył

a sygnał

y sterują ce do odpowiednich ukł

adów mikroprocesora. W odpowiedzi na te

sygnał

y ma miejsce przetwarzanie lub przesył

anie danych. Jeśli przesł

anie danych dotyczy

pamię ci to do mikroprocesor wpisuje bufora adresu (MAR) adres żą danej komórki pamię ci.

Dane przesył

ane mię dzy mikroprocesorem a pamię cią danych wymieniane są za

pośrednictwem rejestru buforowego danych (MBR).

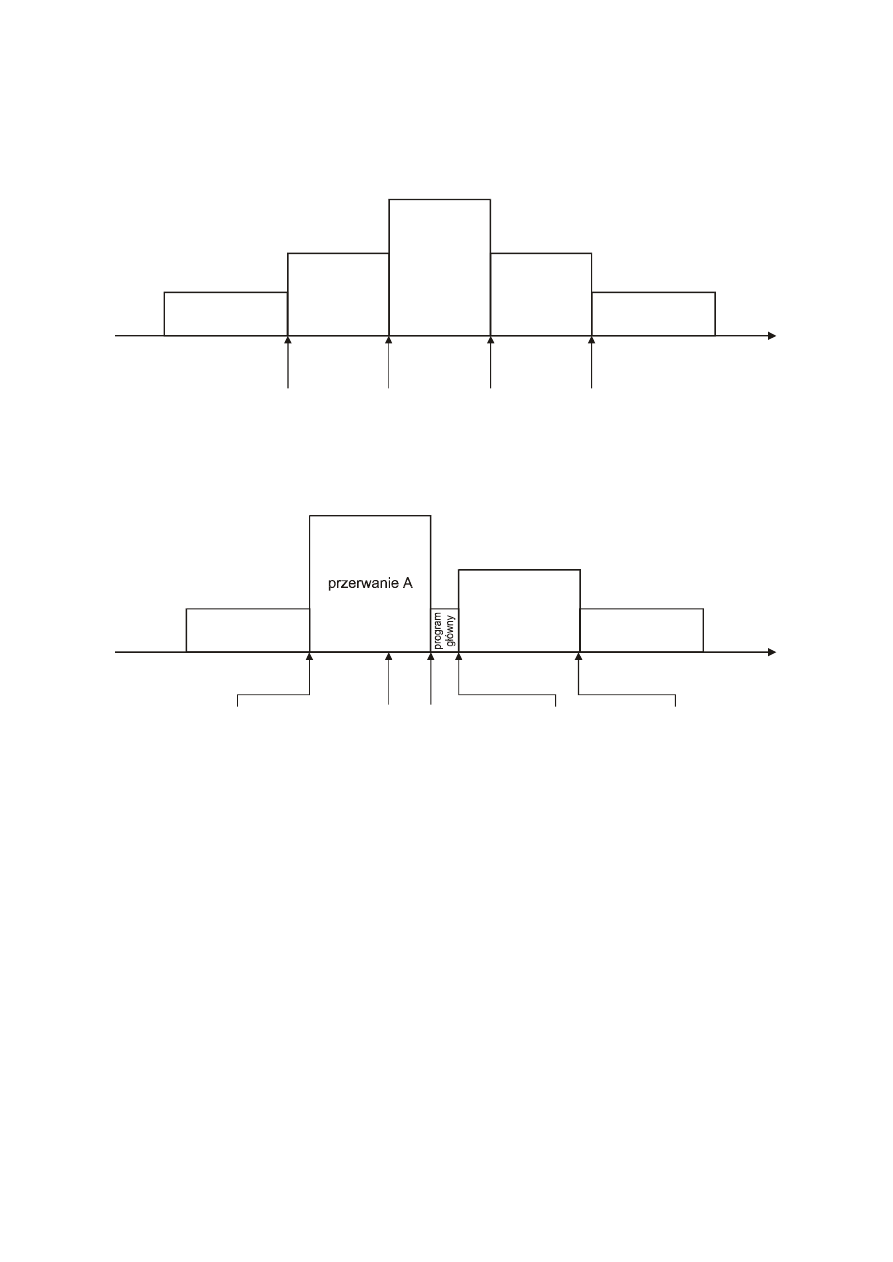

Każdy cykl rozkazowy skł

ada się z jednego lub kilku tzw. cykli maszynowych (patrz

rozdział

cykl rozkazowy). Ukł

ad obsł

ugi przerwań w każdym cyklu maszynowym sprawdza

stan tzw. linii przerwań . Poprzez te linie ukł

ady wejścia/wyjścia przesył

ają sygnał

y żą dania

przerwania. Sygnał

przerwania oznacza, że w urzą dzeniu wystą pił

o pewne zdarzenie, które

wymaga obsł

ugi ze strony mikroprocesora (np.: na wejściu portu pojawił

y się dane, licznik

uległ

przepeł

nieniu). Po odebraniu sygnał

u żą dania przerwania ukł

ad identyfikuje ź ródł

o

przerwania, a nastę pnie na podstawie stanu rejestru maski przerwań (IE) i rejestru priorytetów

przerwań (IP) podejmuje decyzję o rozpoczę ciu lub zaniechaniu obsł

ugi przerwania. Obsł

uga

przerwania polega na zawieszeniu wykonywania programu i rozpoczę ciu wykonywania

specjalnego kodu (procedury) w celu obsł

ugi urzą dzenia zgł

aszają cego przerwanie. Gdy

procedura obsł

ugi przerwania zostanie zakoń czona, ukł

ad obsł

ugi przerwań wznawia

dział

anie zawieszonego programu.

Każdy mikrokontroler zawiera w swojej strukturze pamię ć. Ze wzglę du na peł

nioną

funkcję możemy wyróżnić nastę pują ce rodzaje pamię ci wewnę trznej

•

pamię ć programu

•

pamię ć danych

Pamię ć programu zawiera kody wykonywanych instrukcji oraz bloki danych. Jest to

pamię ć nieulotna (tzn. jej zawartość jest zapisana wzglę dnie trwale i nie ulega zniszczeniu

przy wył

ą czeniu zasilania). Pamię ć ta przeznaczona jest tylko do odczytu. Oznacza to, że

program nie ma możliwości modyfikacji sam siebie oraz, że dane umieszczone w pamię ci

programu są traktowane jak stał

e (tzn. ich wartości nie mogą ulec zmianie). Wśród instrukcji

assemblera nie ma zatem rozkazu, który umożliwiał

by zapis do pamię ci programu.

Zawartość wewnę trznej pamię ć programu mikrokontrolera jest ustalana w trakcie procesu

technologicznego (pamię ć ROM) lub w procesie tzw. programowania pamię ci programu

(pamię ci EPROM, PROM, FLASH). W tym drugim wariancie mikrokontroler podł

ą cza się

tzw. programatora. Urzą dzenie to wysył

a specjalne sygnał

y sterują ce do mikrokontrolera i w

określonych odstę pach czasu ł

aduje dane do pamię ci programu. Dane te programator pobiera

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

7

zwykle poprzez port równoległ

y (bą dź szeregowy) z komputera PC, gdzie program

asemblerowy został

uprzednio napisany i przetł

umaczony na kody bajtowe.

W wewnę trznej pamię ci danych wykonywany program umieszcza tymczasowe dane i

wyniki obliczeń . Pamię ć danych (RAM) jest pamię cią ulotną (tzn. jej zawartość ulega

zniszczeniu przy wył

ą czeniu zasilania). Oprócz tymczasowych danych i wyników obliczeń w

pamię ci wewnę trznej mikrokontrolera zawarte są również wszystkie jego rejestry i struktura

zwana stosem.

Wewnę trzna pamię ć programu i pamię ć danych poł

ą czona jest z pozostałymi

elementami mikrokontrolera (jednostka arytmetyczno logiczna, rejestry, urzą dzenia

wejścia - wyjścia) poprzez wewnę trzną magistralę danych, magistralę adresową i magistralę

sterują ca. Każda magistrala zorganizowana jest w nastę pują cy sposób. Do linii magistrali ma

równoległ

y dostę p kilka ukł

adów (mikroprocesor, pamię ć danych, pamię ć programu, liczne

ukł

ady wejścia wyjścia). Tylko jedno z nich peł

ni rolę nadajnika (wysył

a dane na magistralę ).

Wysł

ane na magistrale dane przeznaczone są tyko dla jednego urzą dzenia, pozostał

e znajdują

się w stanie wysokiej impedancji (tzn. są odł

ą czone od magistrali). Na podstawie

odpowiednich adresów i sygnał

ów sterują cych wystawionych na magistralę określane jest

miejsce ź ródł

owe lub docelowe dla danych.

Wię kszość mikrokontrolerów posiada możliwość podł

ą czenia zewnę trznej pamię ci

programu i zewnę trznej pamię ci danych. W przypadku pamię ci programu aktywny może być

tylko jeden jej rodzaj (pamię ć zewnę trzna albo wewnę trzna). O tym czy wykonywany jest

program z zewnę trznej czy też z wewnę trznej pamię ci programu decyduje specjalny sygnał

doprowadzony z zewną trz do mikrokontrolera. Natomiast wewnę trzna i zewnę trzna pamię ć

danych posiadają odrę bne przestrzenie adresowe. Inne rozkazy przeznaczone są do wymiany

danych z zewnę trzną i wewnę trzną pamię cią danych. Stą d też obia typy pamię ci mogą być

wykorzystywanie równocześnie. Zewnę trzna pamię ć danych i zewnę trzna pamię ć programu

podł

ą czone są do mikrokontrolera poprzez zewnę trzne magistrale: danych, adresową i

sterują cą . Zewnę trzna magistrala danych i zewnę trzna magistrala adresowa są wyprowadzane

na koń cówki portów mikrokontrolera. W przypadku braku zewnę trznej pamię ci danych i

zewnę trznej pamię ci programu porty te peł

ną swą tradycyjna rolę – sł

użą do wymiany

sygnał

ów wejścia/wyjścia.

W zależności od typu mikrokontrolera może on zawierać różne rodzaje urzą dzeń

wejścia/wyję cia. Do wystę pują cych najpowszechniej można zaliczyć:

•

porty równoległ

e

•

porty szeregowe

•

ukł

ady licznikowo – zegarowe

•

przetworniki analogowo – cyfrowe

•

przetworniki cyfrowo – analogowe

Porty równoległ

y posiada szereg koń cówek (zwykle jest to wielokrotność ośmiu), przez które

równocześnie odbywa się wymiana danych. Dzię ki temu przez port równoległ

y można w tym

samym czasie nadać (lub odebrać) wiele bitów danych. Gdy port równoległ

y posiada osiem

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

8

koń cówek można w jednej chwili czasu nadać lub odebrać cał

y bajt. W odróżnieniu od portu

równoległ

ego, port szeregowy wymienia dane za pośrednictwem jednej linii, na której w

kolejnych odstę pach czasu pojawiają się poszczególne bity nadawanego (lub odbieranego)

bajta. Aby nadać (lub odebrać) cał

y bajt należy nadać (lub odebrać) kolejne jego bity.

Rola przetwornika analogowo – cyfrowego polega na zamianie sygnał

u analogowego

podanego na wejście przetwornika na jego reprezantację cyfrową . Sygnał

em analogowym jest

zwykle napię cie elektryczne, które może przybierać dowolne wartości w zadanym zakresie.

Zakres ten podzielony jest na szereg przedział

ów. Każdemu z przedziałów przyporzą dkowany

jest inny kod binarny. Przetwornik pobiera próbkę sygnał

u wejściowego i sprawdza w którym

przedziale zakresu się ona mieści. Nastę pnie przyporzą dkowuje próbce odpowiedni kod

binarny.

Przetwornik cyfrowo – analogowy generuje na swoim wyjściu sygnał

analogowy

odpowiadają cy cyfrowemu kodowi binarnemu podmenu na jego wejście. Ze wzglę du na to

że, liczba kodów binarnych reprezentują cych wartości analogowe jest zawsze skoń czona, na

wyjściu przetwornika cyfrowo-analogowy pojawiają się sygnał

u analogowe o ściśle

określonych poziomach.

Zadaniem ukł

adów licznikowo – zegarowych jest zliczanie impulsów sygnał

ów

pochodzą cych ze ź ródeł

zewnę trznych lub odmierzanie czasu. Sygnał

em zewnę trznym może

np. być napię cie na styczniku podł

ą czonym do odpowiedniego portu mikrokontrolera. Ilość

zliczonych impulsów daje informację o liczbie zał

ą czeń stycznika. Pomiar czasu obywa się

poprzez zliczanie określonej ilości cykli zegara mikrokontrolera. Ukł

ad dział

a wówczas jako

dzielnik czę stotliwości, a przepeł

nienie licznika daje informację o upł

ynię ciu określonego

interwał

u czasu.

2.1.1. CPU – podstawowe rejestry

Rejestry są rodzajem szybkiej i ł

atwo dostę pnej dla mikroprocesora pamię ci. Zasadniczy

proces interpretacji kodu i przetwarzania danych odbywa się za pomocą rejestrów. Nie

wszystkie rejestry mikroprocesora są bezpośrednio dostę pne dla programisty. Czę ść

rejestrów, bardzo istotna dla procesów zachodzą cych wewną trz mikroprocesora, jest

niedostę pna programowo. Wykonywany program nie może bezpośrednio zmienić ich

wartości. Stan tych rejestrów nie może być też wykorzystany do pamię tania wyników dział

ań

bą dź sterowania przebiegiem programu. Do rejestrów niedostę pnych programowo można

zaliczyć wspomniane wcześniej: rejestr rozkazów (IR), bufor adresów (MAR) i bufor danych

(MBR). W bieżą cym rozdziale zostaną omówione wył

ą cznie dostę pne programowo rejestry

mikroprocesora.

Operacje arytmetyczno – logiczne wykonywane są najszybciej gdy ich argumenty

umieszczone są w rejestrach. Wyniki operacji wraz z informacją o możliwych bł

ę dach

zapisywane są w specjalnie przeznaczonych do tego celu rejestrach. Rejestry są stosowane

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

9

przy odwoł

ywaniu się komórek pamię ci, kontrolują przebieg programu – stan pewnych

rejestrów jest istotny przy wykonywaniu skoków, obsł

udze przerwań i podprogramów.

Oprócz rejestrów mikroprocesora (CPU) mikrokontroler zawiera szereg rejestrów

sł

użą cych do obsł

ugi zintegrowanych urzą dzeń wejścia/wyjścia. Rejestry te zostaną

szczegół

owo omówione w dalszej czę ści skryptu poświę conej zintegrowanym ukł

adom

peryferyjnym 8051.

Mikrokontroler 8051 jest mikrokontrolerem 8 – bitowym. Oznacza to, że jego rejestry

(poza pewnymi wyją tkami) są 8 – bitowe. Stą d też jednostka arytmetyczno logiczna w

jednym cyklu rozkazowym może w zasadzie wykonać operacje tylko na pojedynczych

bajtach. Konsekwencją tego jest fakt że, wię kszość operacji arytmetyczno – logicznych

mikroprocesora wykonywana na liczbach jednobajtowych. Aby wykonać dodawanie liczb

dwubajtowych należy napisać wł

asną procedurę , która doda do siebie mł

odsze, a nastę pnie

starsze bajty argumentów z uwzglę dnieniem ewentualnego przeniesienia. Dodawanie

mł

odszych i starszych bajtów są operacjami na liczbach jednobajtowych i mogą być

wykonanie przez mikroprocesor bezpośrednio.

Do najważniejszych rejestrów CPU zalicza się :

•

Akumulator

Akumulator (A) jest rejestrem, który jest zaangażowany przy wykonywaniu operacji

arytmetyczno – logicznych. W akumulatorze przechowywany jest zwykle jeden z

argumentów operacji arytmetycznej lub logicznej. Po wykonaniu operacji wynik najczę ściej

przesył

any jest do akumulatora. Oznacza to, że w wyniku wykonania operacji arytmetyczno –

logicznej zwykle ulega nadpisaniu wartość jednego z jej argumentów – przechowywana

uprzednio w akumulatorze. Z tego wzglę du akumulator ł

aduje się tylko tymczasowymi

danymi, które mają być argumentami operacji arytmetyczno – logicznych. Aby zachować

wynik operacji należy przesł

ać go z akumulatora do pamię ci bą dź innego rejestru.

Akumulator wykorzystywany jest również w operacjach skoków warunkowych. Operacje te

testują zawartość rejestru i w zależności do wyniku testu wykonują skok bą dź pomijają

wykonanie skoku. Operacje skoków warunkowych są używane do budowania podstawowych

struktur sterują cych przebiegiem programu asemblerowego takich jak rozgał

ę zienia i pę tle.

Wynik operacji arytmetycznej operacji arytmetycznej lub logicznej może dzię ki zastosowaniu

skoków warunkowych z testem akumulatora zadecydować o dalszym przebiegu programu.

•

Rejestr pomocniczy B

Rejestr pomocniczy B (zwany również akumulatorem pomocniczym) używany jest przy

operacjach mnożenia i dzielenia. Asembler 8051 pozwala na bezpośrednie mnożenie oraz

dzielenie (cał

kowite) jedynie akumulatora i rejestru B. Przy wykonywaniu dzielenia dzielną

pobierana jest z akumulatora, natomiast dzielnik – z rejestru B. Po wykonaniu operacji

dzielenia iloraz zawarty jest w akumulatorze, a reszta z dzielenia zostaje zapisana w rejestrze

B. Ze wzglę du na to, iż wynikiem mnożenia liczb jednobajtowych jest (w ogólności) liczna

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

10

dwubajtowa, wynik mnożenia nie może być zawarty w cał

ości w akumulatorze. Po

wykonaniu mnożenia w akumulatorze znajduje się tylko mł

odszy bajt iloczynu. Starszy bajt

wyniku przesył

any jest do rejestru B.

•

Rejestr stanu

Wybrane bity rejestru stanu (PSW) peł

nią rolę tzw. flag. Flagi sygnalizują pewne krytyczne,

wymagają ce obsł

ugi, sytuacje wystę pują ce podczas wykonywania operacji arytmetycznych.

Należą do nich: przeniesienie lub pożyczka przy dodawaniu i odejmowaniu liczb naturalnych

(flaga przeniesienia C), przekroczenie zakresu liczb ze znakiem przy dodawaniu i

odejmowaniu (flaga przepeł

nienia OV), pożyczka lub przeniesienie pomię dzy starszą i

mł

odszą czę ścią bajta podczas dodawania i odejmowania (flaga przeniesienia pomocniczego

AC), przekroczenie zakresu jednego bajta przy mnożeniu liczb naturalnych (flaga OV),

wystą pienie dzielenia prze zero (flaga OV). Rejestr stanu zawiera również tzw. flagę

parzystości. Jej ustawienie oznacza, że w akumulatorze liczba bitów równych jeden jest

parzysta. Flaga ta w przeciwień stwie do flag: C, OV i AC które, zmieniają się po wykonaniu

operacji arytmetycznych, modyfikowana przy każdym wpisie do akumulatora (może się

zatem zmienić np. po wykonaniu operacji przesł

ania danych). Dwa bity w rejestrze stanu

oznaczane jako F0 i F1 peł

nią rolę flag (bitów) ogólnego zastosowania i mogą być

wykorzystane przez programistę do innych celów. Bity RS0 i RS1 sł

użą do wyboru obszaru

pamię ci w którym przechowywana jest zawartość ośmiu rejestrów: R0, R1, ... , R7 (obsł

uga

banków rejestrów R0-R7 zostanie omówiona w odrę bnym podpunkcie).

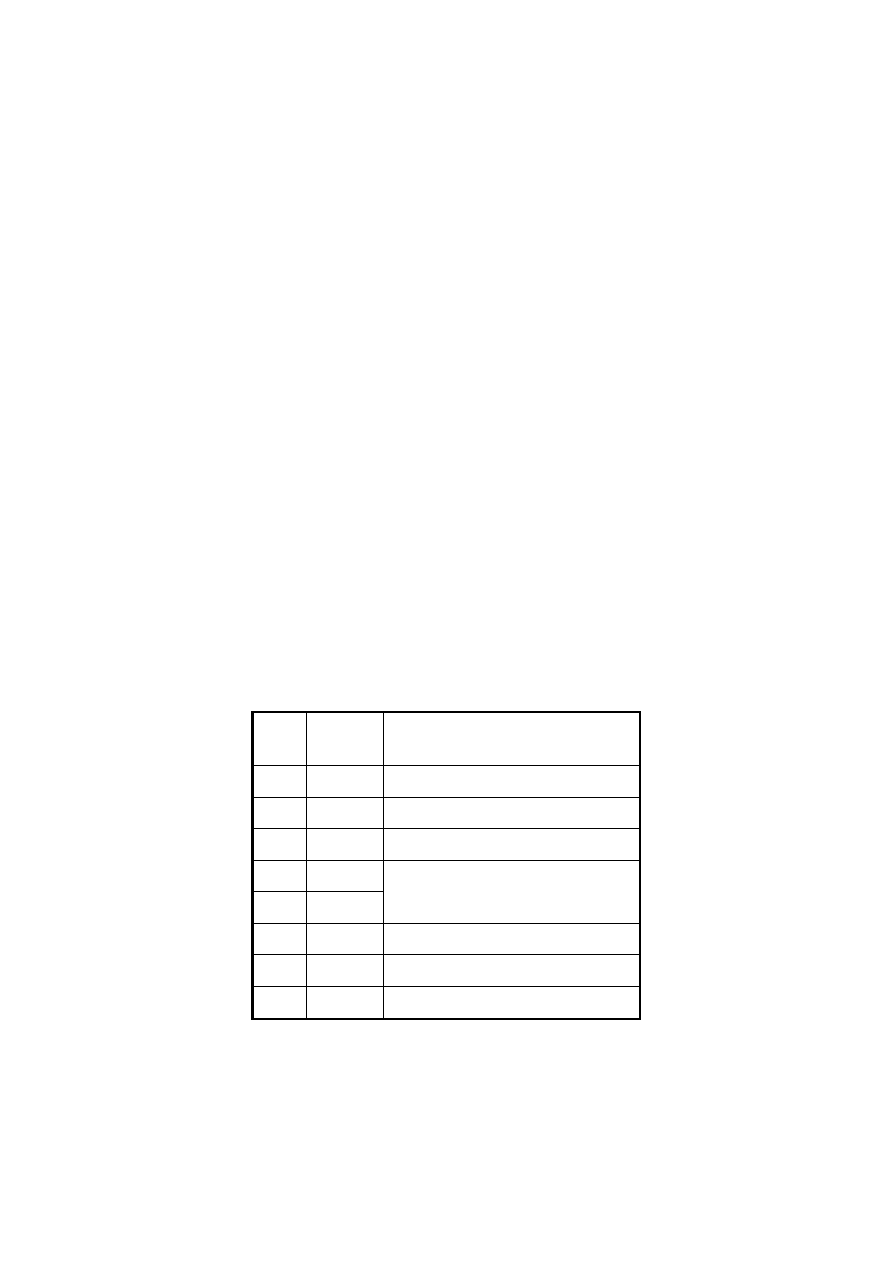

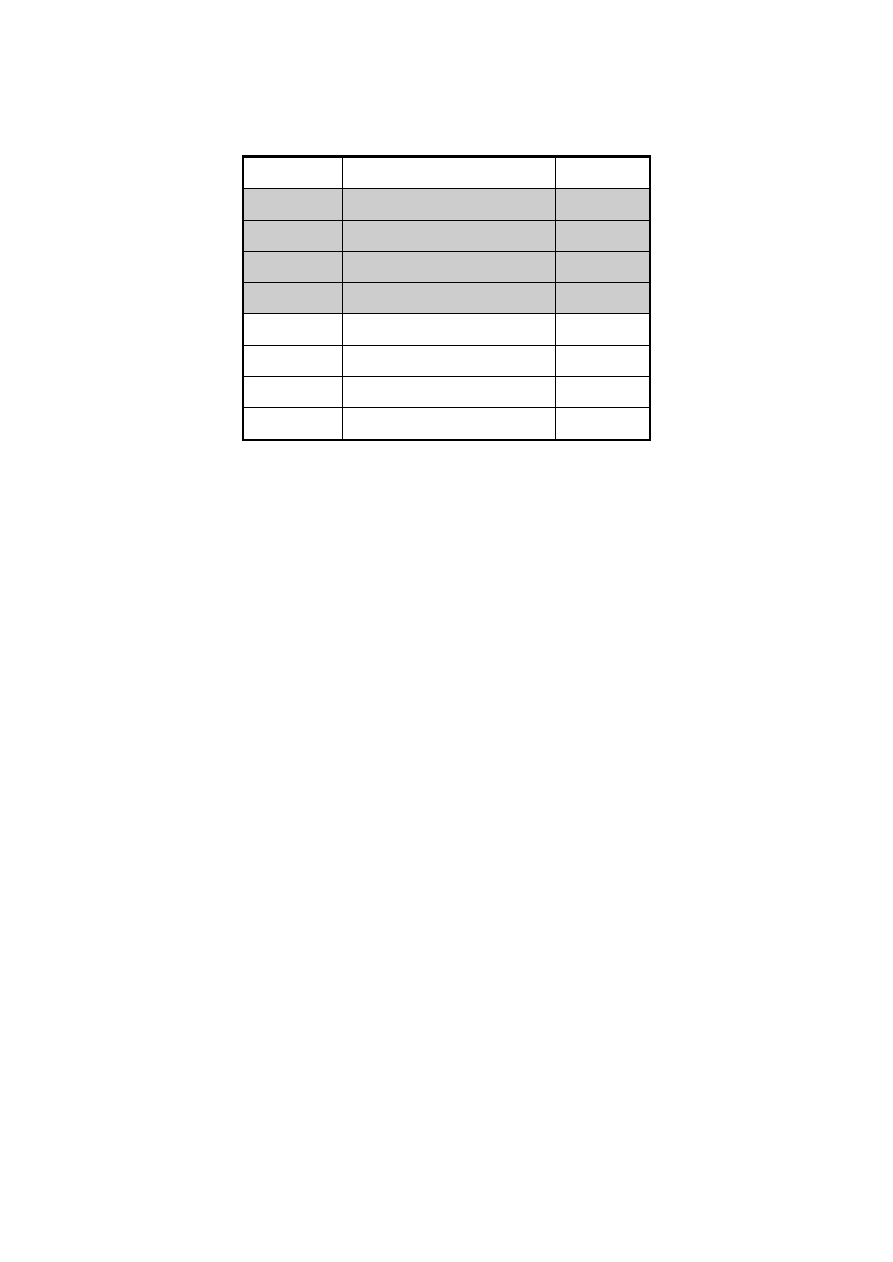

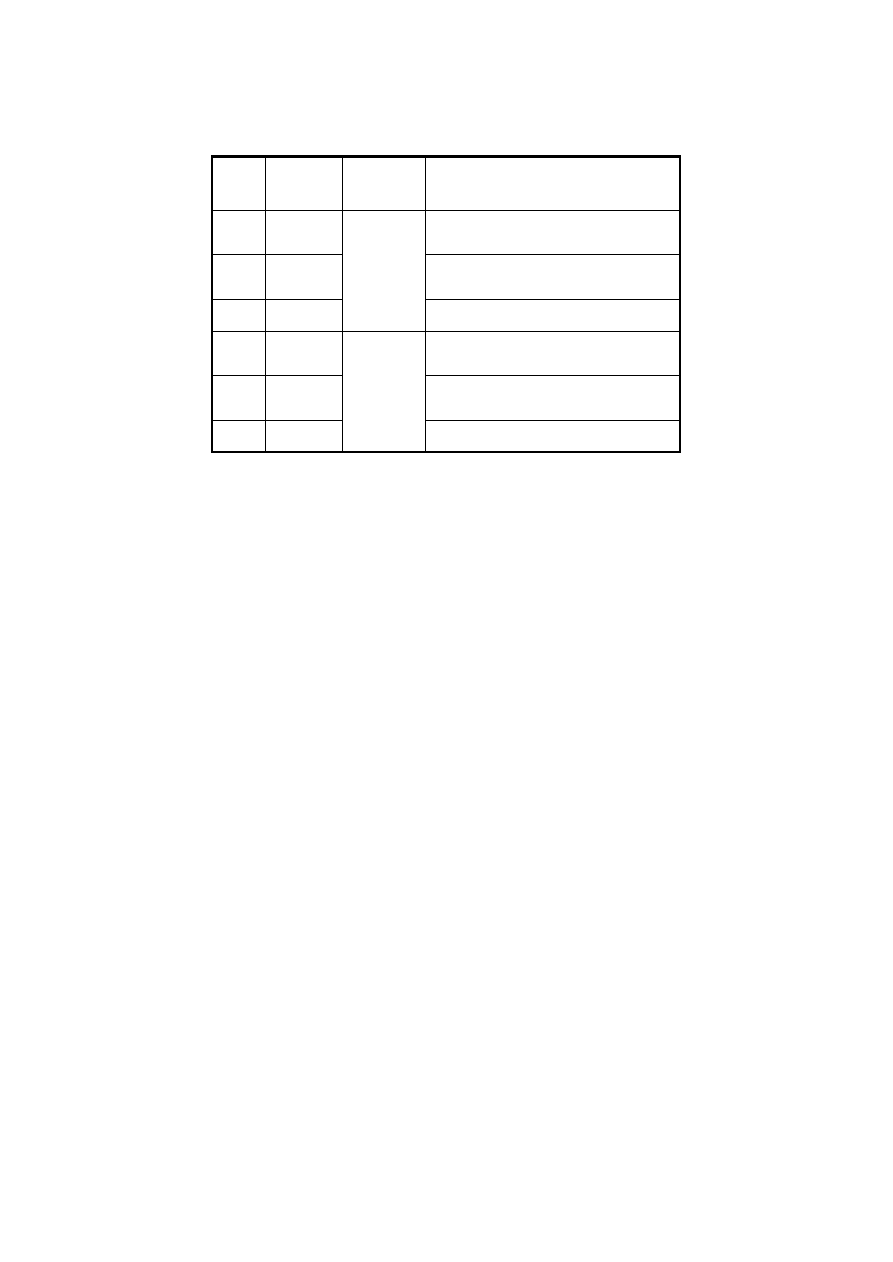

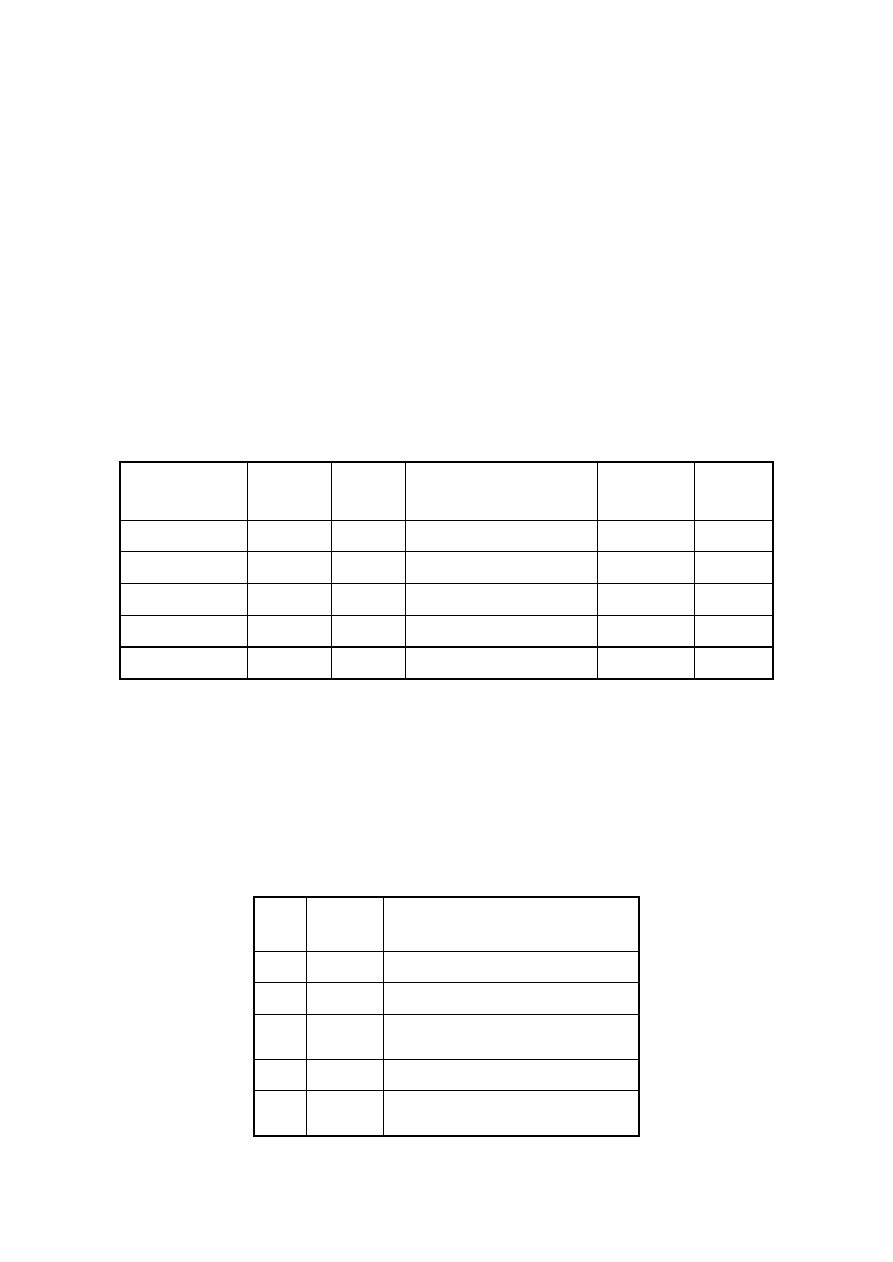

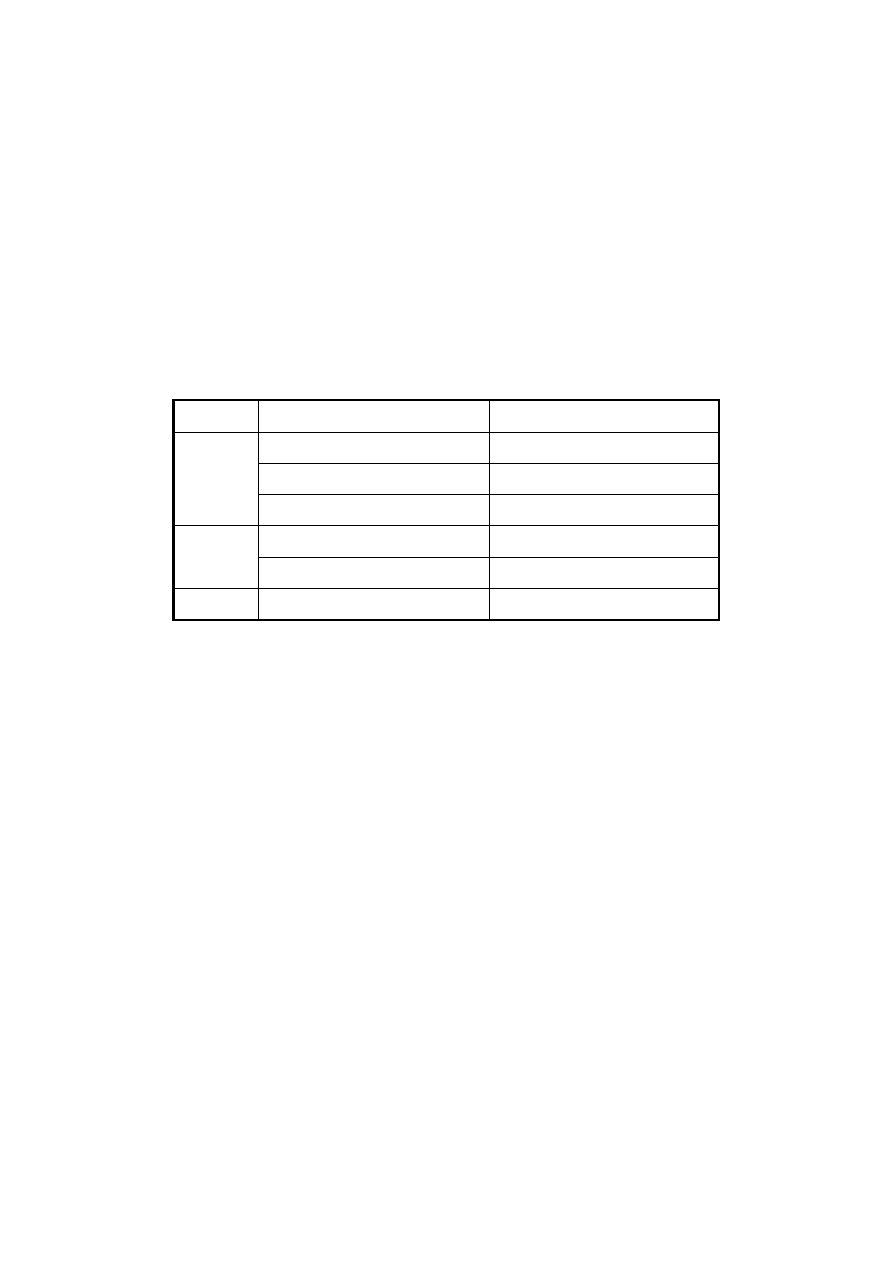

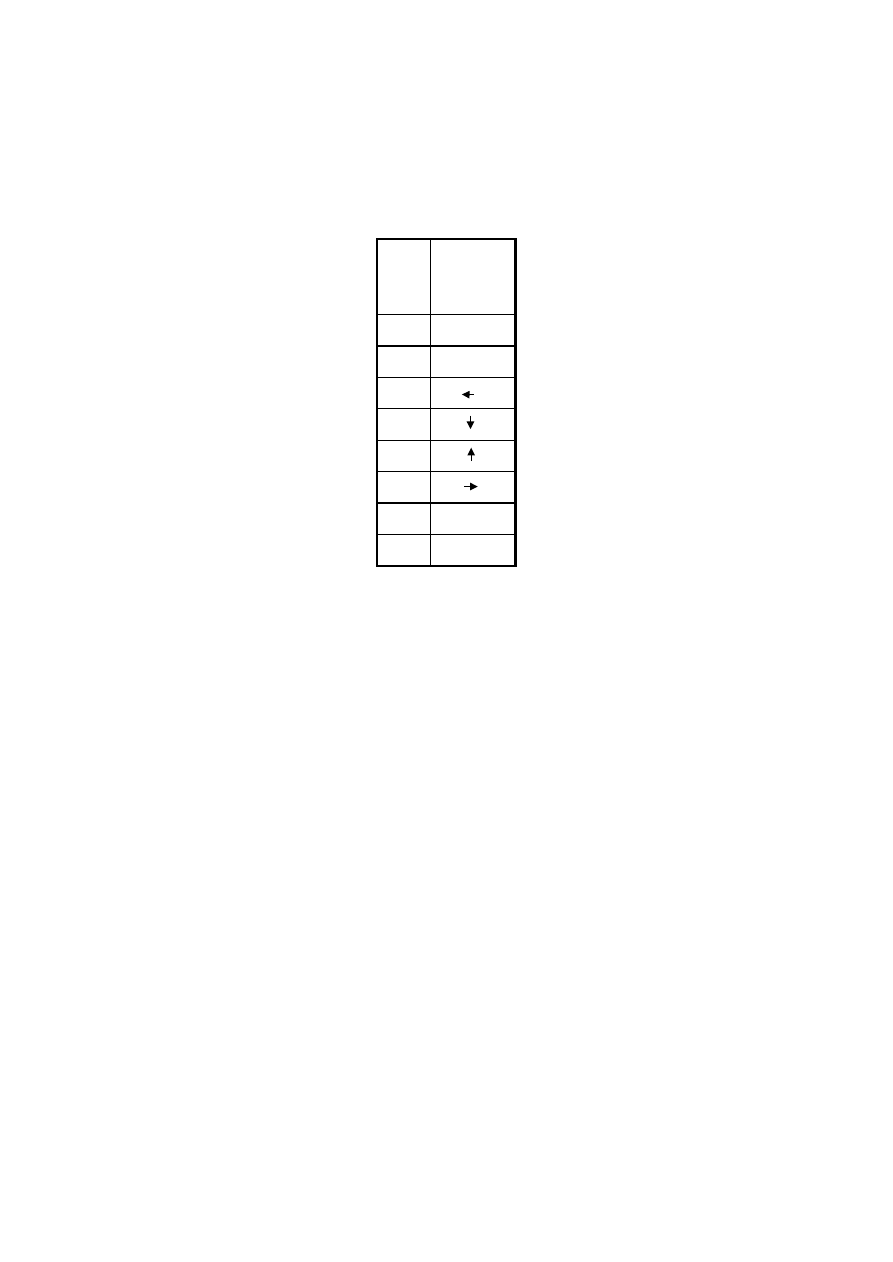

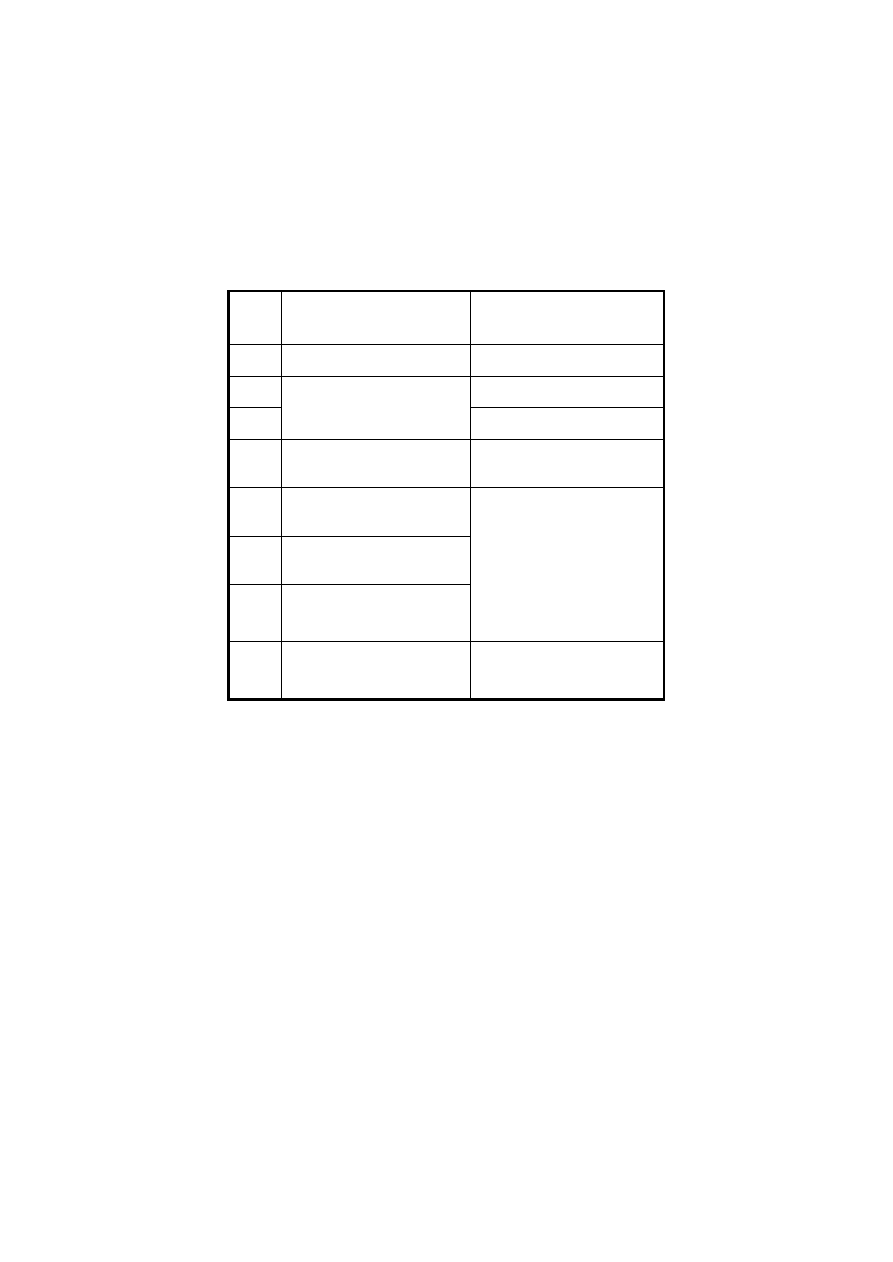

Tabela 1. Oznaczenia i funkcje kolejnych bitó w rejestru stanu (PSW)

numer

bitu

oznaczenie

opis

7

CY

flaga przeniesienia

6

AC

flaga przeniesienia pomocniczego

5

F0

bit ogólnego przeznaczenia

4

RS1

3

RS0

bity wyboru banku rejestrów roboczych

2

OV

flaga przepeł

nienia

1

F1

bit ogólnego przeznaczenia

0

P

flaga parzystości

•

Banki rejestrów R0-R7

Mikrokontroler 8051 dysponuje ośmioma rejestrami ogólnego zastosowania (zwanymi

również rejestrami roboczymi) oznaczonymi: R0, R1, R2, ... , R7. W rejestrach tych

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

11

przechowuje się wszystkie tymczasowe dane na których mikroprocesor wykonuje się bieżą ce

operacje. Mogą to być: dane pobrane z pamię ci, pośrednie wyniki operacji arytmetyczno –

logicznych, iteratory używane w pę tlach, wskaź niki danych, itp.. Podobnie jak w przypadku

akumulatora zawartość rejestrów R0-R7 może być testowana przy pomocy skoków

warunkowych (lista dostę pnych instrukcji jest w tym przypadku uboższa). Zawartość

rejestrów roboczych zapisana jest w wewnę trznej pamię ci mikrokontrolera. Pierwsze 24 bajty

pamię ci wewnę trznej został

y podzielone na 4 ośmiobajtowe banki. W zależności od stanu

bitów RS0 i RS1 (w rejestrze stanu) rejestry robocze przypisane są do jednego z czterech

banków (przedstawia to Tabela 2).

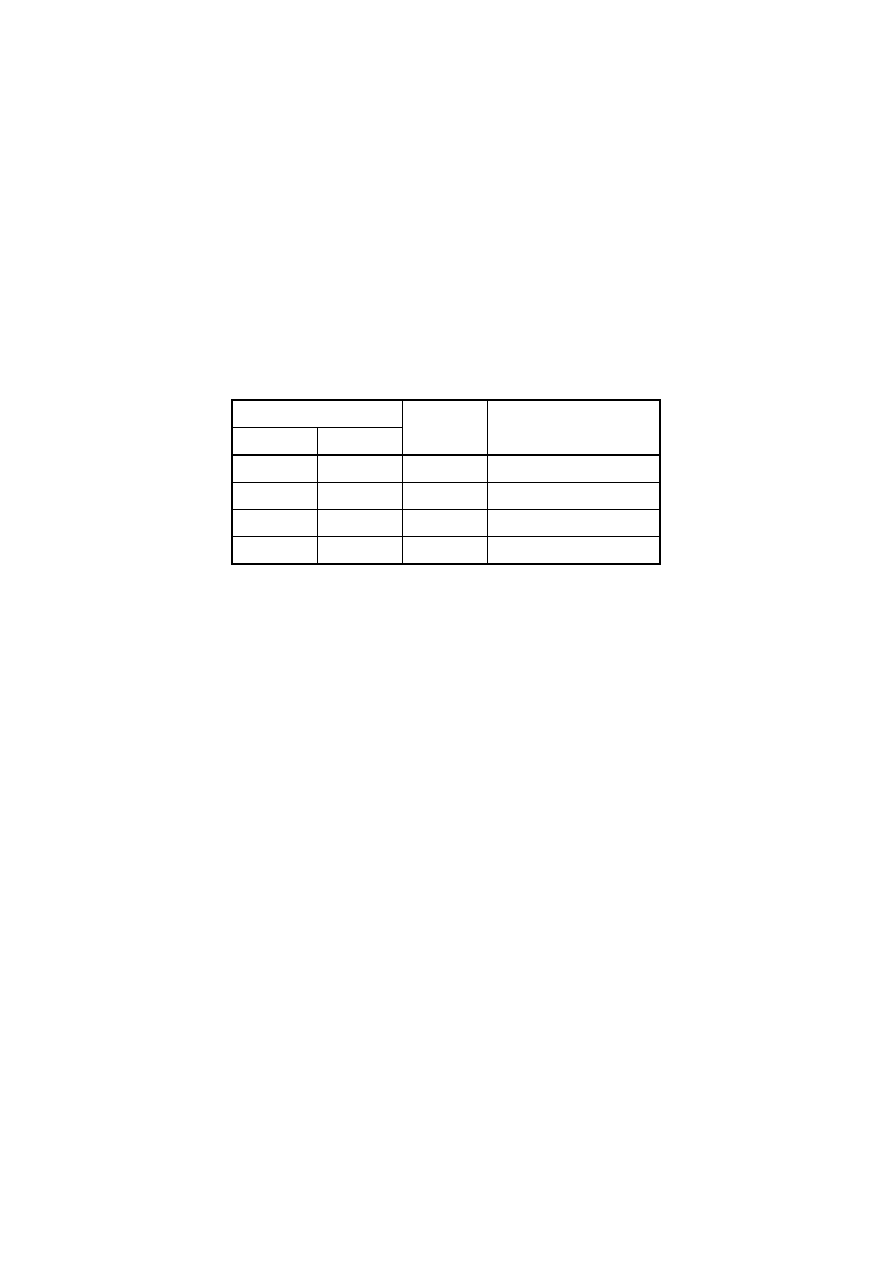

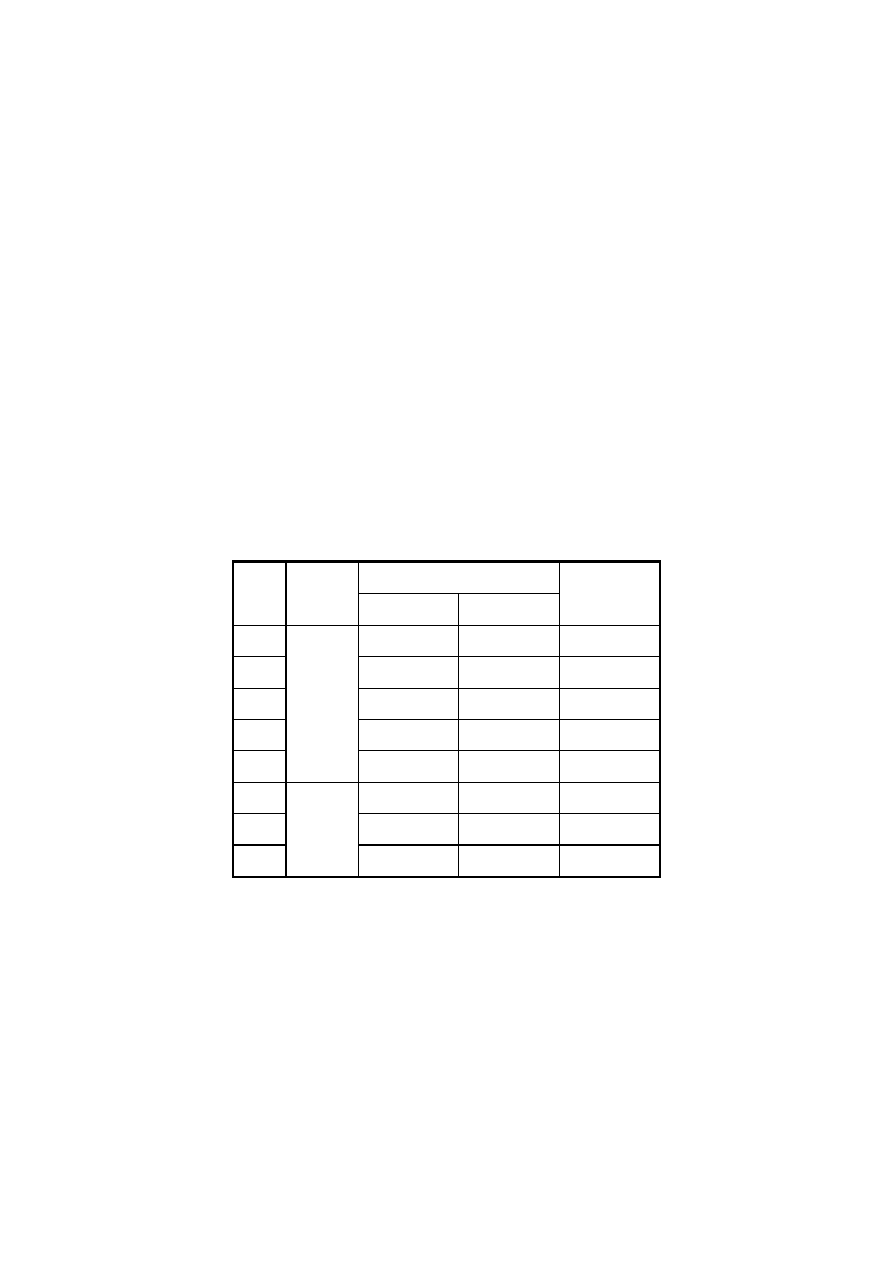

Tabela 2. Adresy wewnę trznego RAM’u przypisane każdemu z bankó w rejestró w roboczych.

bity wyboru banku

RS1

RS0

numer

banku

adresy rejestrów

roboczych

0

0

0

00-07(00-07)

H

0

1

1

08-15(08-0F)

H

1

0

2

16-23(10-17)

H

1

1

3

24-31(18-1F)

H

Po (re)starcie mikrokontrolera rejestr stanu jest wyzerowany. Oznacza to, że rejestry robocze

są domyślnie przypisane do najniższego banku. Mechanizm zmiany banku rejestrów

roboczych może być wykorzystany w dwojaki sposób. (1) W wyją tkowych sytuacjach

programista może potrzebować wię cej niż ośmiu rejestrów roboczych, wówczas uaktywniają c

inny bank nie traci wartości zapisany uprzednio w rejestrach roboczych. Zmiana aktywnego

banku rejestrów uniemożliwia jednak bezpośrednie korzystanie z uprzednio wybranego

banku. Rejestry R0-R7 zwią zane są wówczas z innym obszarem pamię ci. (2) W przypadku

procedury obsł

ugi przerwań i niektórych podprogramów zachodzi konieczność zachowania

wartości rejestrów roboczych tak by procedura obsł

ugi przerwania (lub podprogram) mogł

a

nienależnie korzystać z rejestrów R0-R7, a po jej zakoń czeniu możliwe był

o odtworzenie

poprzednich ich wartości i kontynuowanie dział

ania programu. W procedurze obsł

ugi

przerwania (lub w podprogramie) można wówczas aktywować inny bank rejestrów

roboczych, a tuż przed jej zakoń czeniem aktywować bank używany w programie gł

ównym.

Dwa spośród rejestrów roboczych – rejestry R0 i R1 – wykorzystywane są jako

wskaź niki przy odwoł

ywaniu się do komórek zewnę trznej i wewnę trznej pamię ci danych.

Wspomniany sposób adresowania zostanie szczegół

owo omówiony w rozdziale poświę conym

trybom adresowania.

•

Wskaź nik danych DPTR

Wskaź niki danych (DPTR) jest jednym z dwóch 16-bitowych rejestrów mikrokontrolera

8051. Rejestr ten używany jest jako wskaź nik przy odwoł

ywaniu się do danych zawartych w

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

12

zewnę trznej pamię ci danych i pamię ci programu. Wykorzystanie rejestru DPTR bę dzie

omówione wyczerpują co w rozdziale „Tryby adresowania”.

•

Licznik rozkazów

W liczniku rozkazów (PC) przechowywany jest adres komórki pamię ci programu spod której

ma być pobrany kolejny kod rozkazu. Przed wykonaniem rozkazu licznik rozkazów musi być

zwię kszony liczbę bajtów jaką zajmuje w pamię ci programu bieżą cy kod rozkazu. Dzię ki

temu po wykonaniu rozkazu nowa wartość licznika rozkazów bę dzie wskazywał

a adres pod

którym rozpoczyna się nastę pny rozkaz.

Licznik rozkazów jest rejestrem 16-bitowym. Rejestr ten jest jedynym z dostę pnych

programowo rejestrów mikrokontrolera którego wartości nie można odczytać ani zapisać.

Zmiana wartości licznika rozkazów dokonuje się w toku wykonywania programu. Ma to

miejsce w nastę pują cych sytuacjach. (1) Przed wykonaniem każdego rozkazu (licznik

rozkazów zwię kszany jest o ilość bajtów jaką zajmuje bieżą cy rozkaz). (2) Przy

wykonywaniu skoku (do licznika rozkazów ł

adowany jest adres pamię ci programu pod który

wykonywany jest skok). (3) Przy wywoł

aniu podprogramu lub procedury obsł

ugi przerwanie

oraz w momencie powrotu z podprogramu lub procedury obsł

ugi przerwania. W opisanych

powyżej przypadkach zmiana licznika rozkazów odbywa się automatycznie. Programista nie

ma możliwości ingerencji w te procesy. Nie może bezpośrednio zmienić wartości licznika

rozkazów ponieważ nie ma możliwości zaadresowania tego rejestru.

Gdy stał

e zapisane w pamię ci programu znajdują się w bezpośrednim są siedztwie

kodu programu wówczas istnieje możliwość odwoł

ani się do nich poprzez jeden z trybów

adresowania. W trybie tym adres danych opracowywany jest jako suma licznika rozkazów

oraz przesunię cia. Zawartość licznika rozkazów wskazuje miejsce w kodzie w którym koń czy

bieżą cy rozkaz – czyli rozkaz który odwoł

uje się do danych. Przesunię cie określa ilość bajtów

w kodzie programu jakie dzieli dane od rozkazu odwoł

ują cego się do nich. Wyznaczanie

adresu odbywa się automatycznie. Nie jest wiec w tym przypadku potrzebna programiście

jawna znajomość wartości licznika rozkazów.

•

Wskaź nik stosu

W każdym mikroprocesorze istnieje struktura nazywana stosem. Zgodnie z nazwą dostę p do

danych zgromadzonych na stosie nie jest swobodny. Ze stosu można odczytać (zdją ć) tylko te

dane, które został

y zapisane do (wrzucone na) stosu jako ostatnie. W mikrokontrolerze 8051

stos umieszczony jest w wewnę trznej pamię ci danych. Wrzucanie danych na stos polega na

zapisie kolejnych komórek pamię ci począ wszy od pewnego adresu bazowego (dna stosu).

Przy zrzucaniu danych ze stosu nastę puje odczyt kolejnych, coraz bliższych dnu stosu,

komórek pamię ci. Aby oba procesy mogł

y przebiegać w kontrolowany sposób potrzebny jest

rejestr, zwany wskaź nikiem stosu (SP), w którym przechowuje się adres wierzchoł

ka stosu.

Wskaź nik stosu wskazuje adres komórki pamię ci pod którym zapisano ostatnie dane

wrzucone na stos. W przypadku gdy stos jest pusty wskaź nik stosu zawiera adres mniejszy o

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

13

jeden od adresu bazowego. Do zapisu i odczytu danych ze stosu sł

użą dwa specjalne rozkazy.

Przez wrzuceniem danych na stos mikroprocesor automatycznie zwię ksza o jeden

(inkrementuje) wskaź nik stosu. Przy zrzucaniu danych ze stosu kolejność wskaź nik stosu jest

zmniejszany o jeden (dekrementowany) dopiero po odczycie danych.

W przeciwień stwie do licznika rozkazów programista na możliwość odczytu i zapisu

wskaź nika stosu. Odczyt wskaź nika stosy pozwala kontrolować ilość pamię ci jaką zajmuje

stos. Natomiast zapis do wskaź nika stosu umożliwia, na począ tku programu, gdy stos jest

pusty, wybór innego adresu bazowego dla stosu.

•

Rejestr maski przerwań

Wię kszość mikroprocesorów ma możliwość odbioru sygnał

ów z kilku ź ródeł przerwań . Aby

mieć możliwość sprawnej obsł

ugi przerwań wprowadzono mechanizm za pomocą którego

można blokować sygnał

y przerwań . Jest to użyteczne w trzech przypadkach. (1) W pewnych

sytuacjach programista może w ogóle nie być zainteresowany obsł

ugą przerwań . Ewentualne

sygnał

y żą dania przerwania zakł

ócałyby niepotrzebnie pracę programu. Należy wówczas

zablokować wszystkie sygnał

y przerwań . (2) Jeśli podję to się obsł

ugi przerwań z kilu

wygranych ź ródeł

pozostał

e ź ródł

a przerwań nie powinny w żaden sposób wpł

ywać na bieg

programu – ich sygnał

y przerwań powinny zostać zablokowane. (3) W trakcie obsł

ugi

przerwania należy zablokować sygnał

obsł

ugiwanego przerwania aby mieć możliwość jej

wykonania.

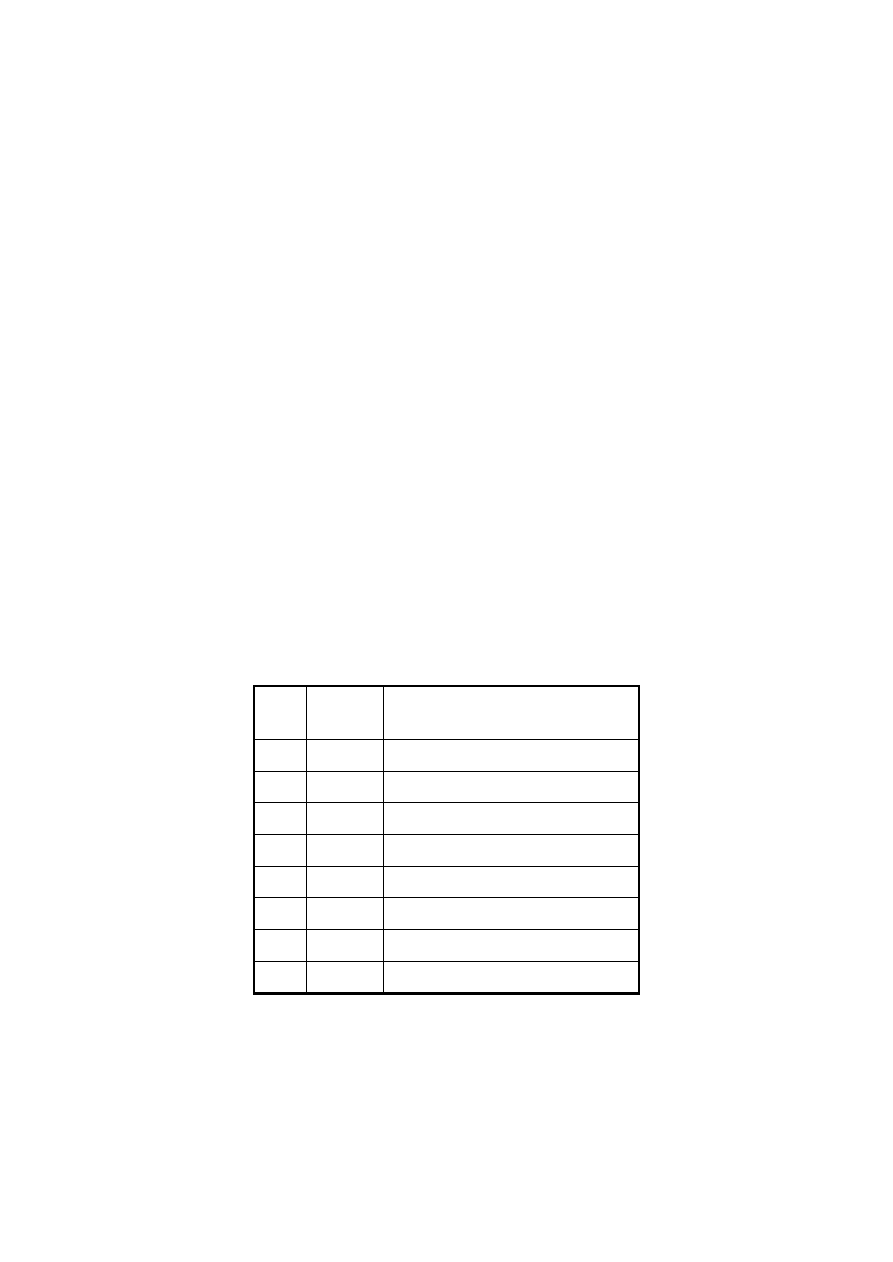

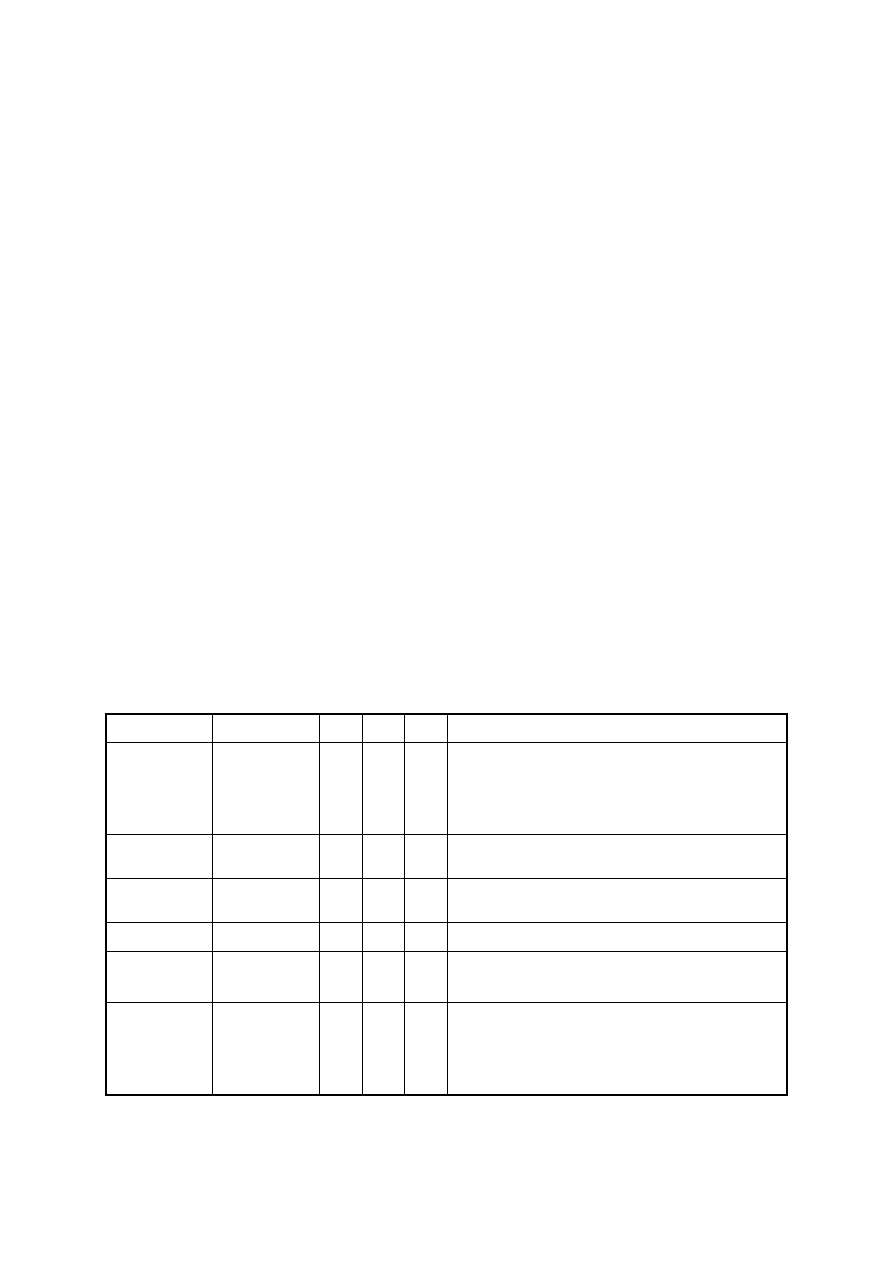

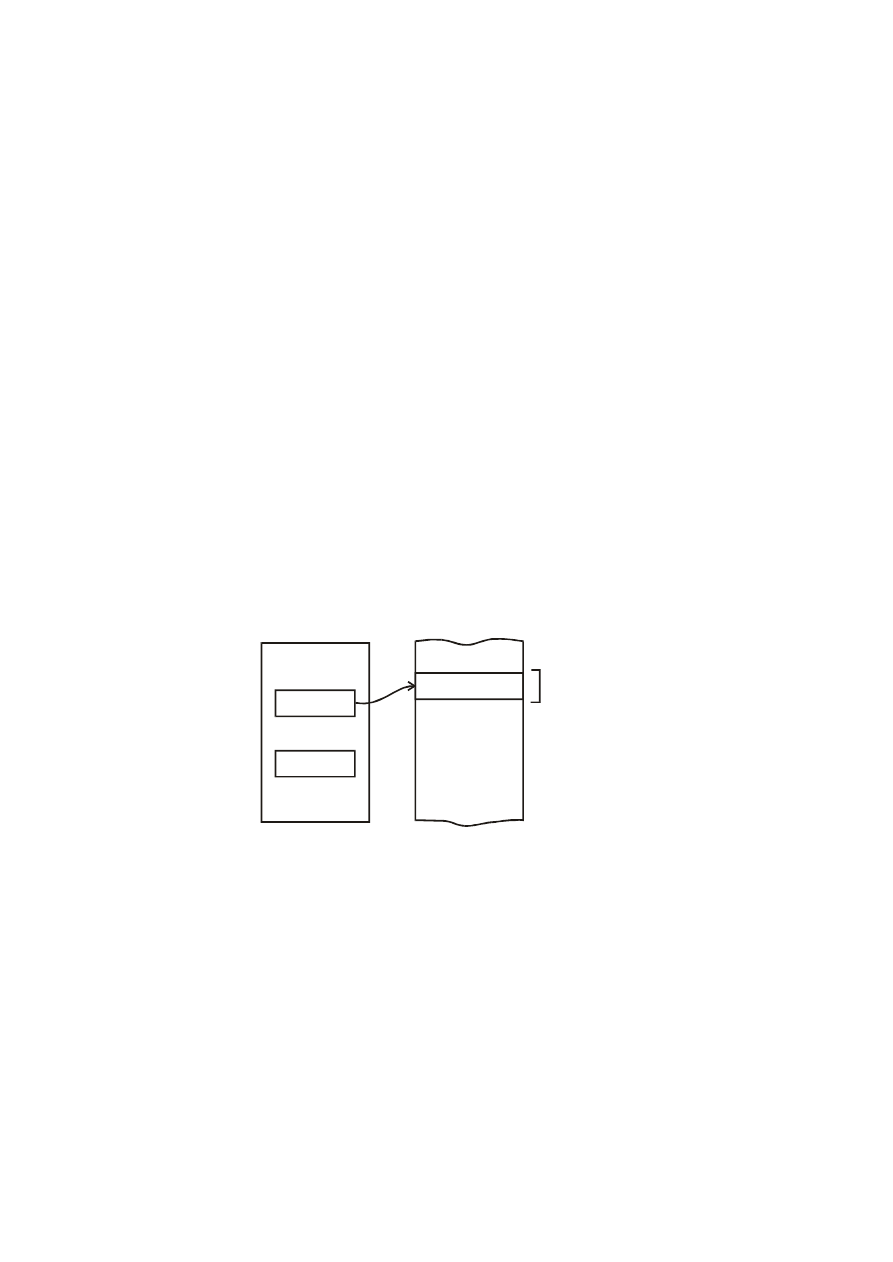

Tabela 3. Oznaczenia kolejnych bitó w rejestru maski przerwań (IE).

numer

bitu

oznaczenie

maskowane ź ródł

o przerwania

7

EA

wszystkie ź ródł

a przerwań

6

-

5

-

4

ES

port szeregowy

3

ET1

ukł

ad licznikowy T1

2

EX1

przerwanie zewnę trzne INT1

1

ET0

ukł

ad licznikowy T0

0

EX0

przerwanie zewnę trzne INT1

Sygnał

przerwania powinien być odblokowany tuż przed opuszczeniem procedury obsł

ugi.

Umożliwia to ponowną reakcję na sygnał

przerwania. Mikrokontroler 8051 jest w stanie

odebrać sygnał

y przerwań pochodzą ce z pię ciu ź ródeł

. Trzy ź ródł

a przerwań stanowią

wewnę trzne ukł

ady peryferyjne mikrokontrolera: dwa ukł

ady licznikowo – zegarowe oraz

port szeregowy. Pozostał

e dwa zwią zanie są ukł

adani zewnę trznymi, które mogą być

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

14

podł

ą czone do mikrokontrolera przez dwie linie przerwań . W rejestrze maski stanu (IE) –

zwanym również rejestrem zezwoleń na przerwania – stan bitu EA określa czy

mikrokontroler w ogóle podejmuje obsł

ugę przerwań . Pię ć innych bitów (por. Tabela 3)

umożliwia zablokowanie (maskowanie) poszczególnych ź ródeł

przerwań .

•

Rejestr priorytetów przerwań

Gdy mikroprocesor jest zaangażowany w obsł

ugę przerwania może pojawić się sygnał

z

innego ź ródł

a przerwania. Musi wówczas zostać podję ta decyzja o zawieszeniu (bą dź

kontynuowaniu) obsł

ugi bieżą cego przerwania i podję ciu (bą dź zaniechaniu) obsł

ugi nowego

przerwania. W mikrokontrolerze 8051 każdemu z pię ciu ź ródeł

przerwań można przypisać

wysoki lub niski poziom priorytetu. Na podstawie poziomów priorytetów bieżą cego i nowego

przerwania podejmowana jest decyzja o kontynuowaniu lub zaniechaniu wykonywania

procedury obsł

ugi bieżą cego przerwania. Poziomy priorytetów ź ródeł

przerwań określa stan

poszczególnych bitów rejestru priorytetów przerwań (IP). W Tabeli 4 opisano znaczenie

kolejnych bitów tego rejestru.

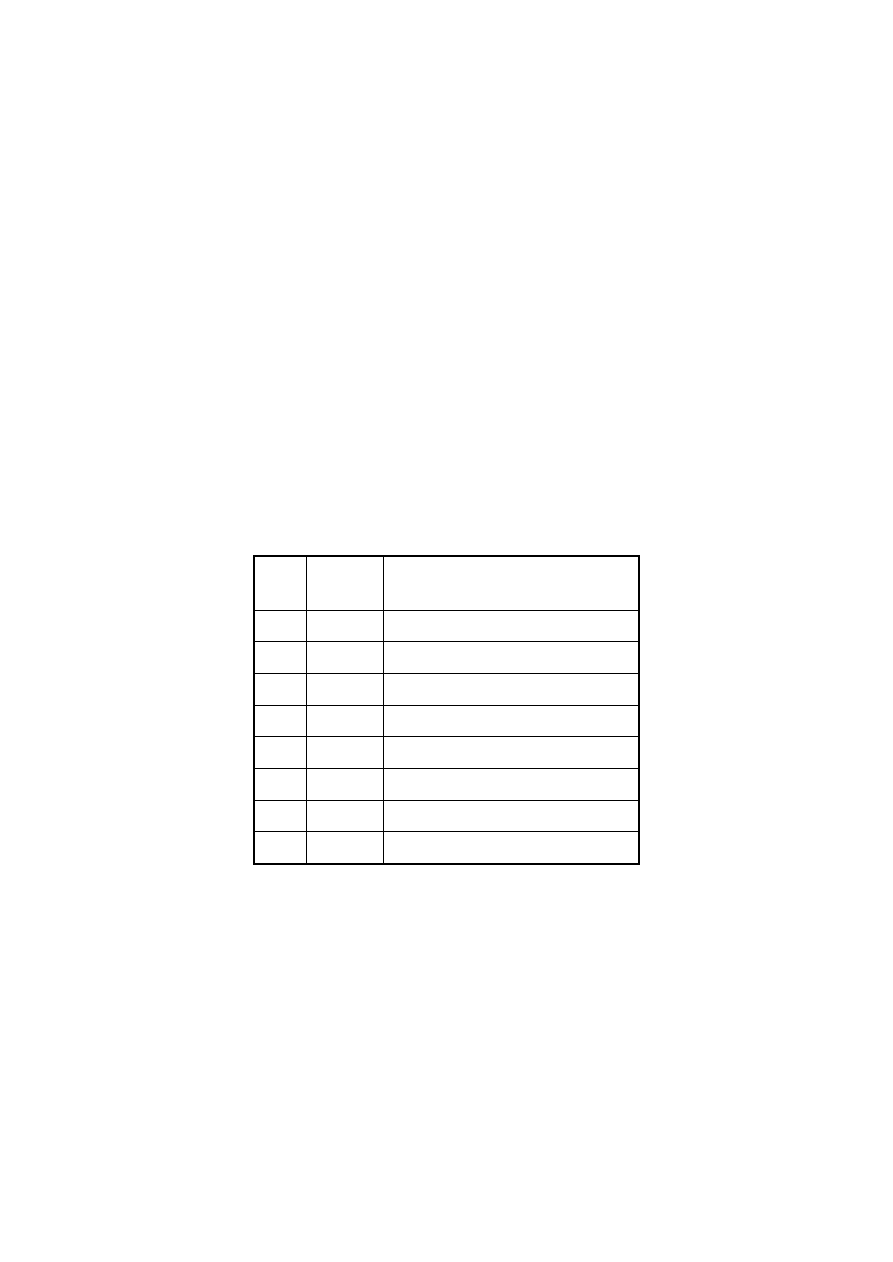

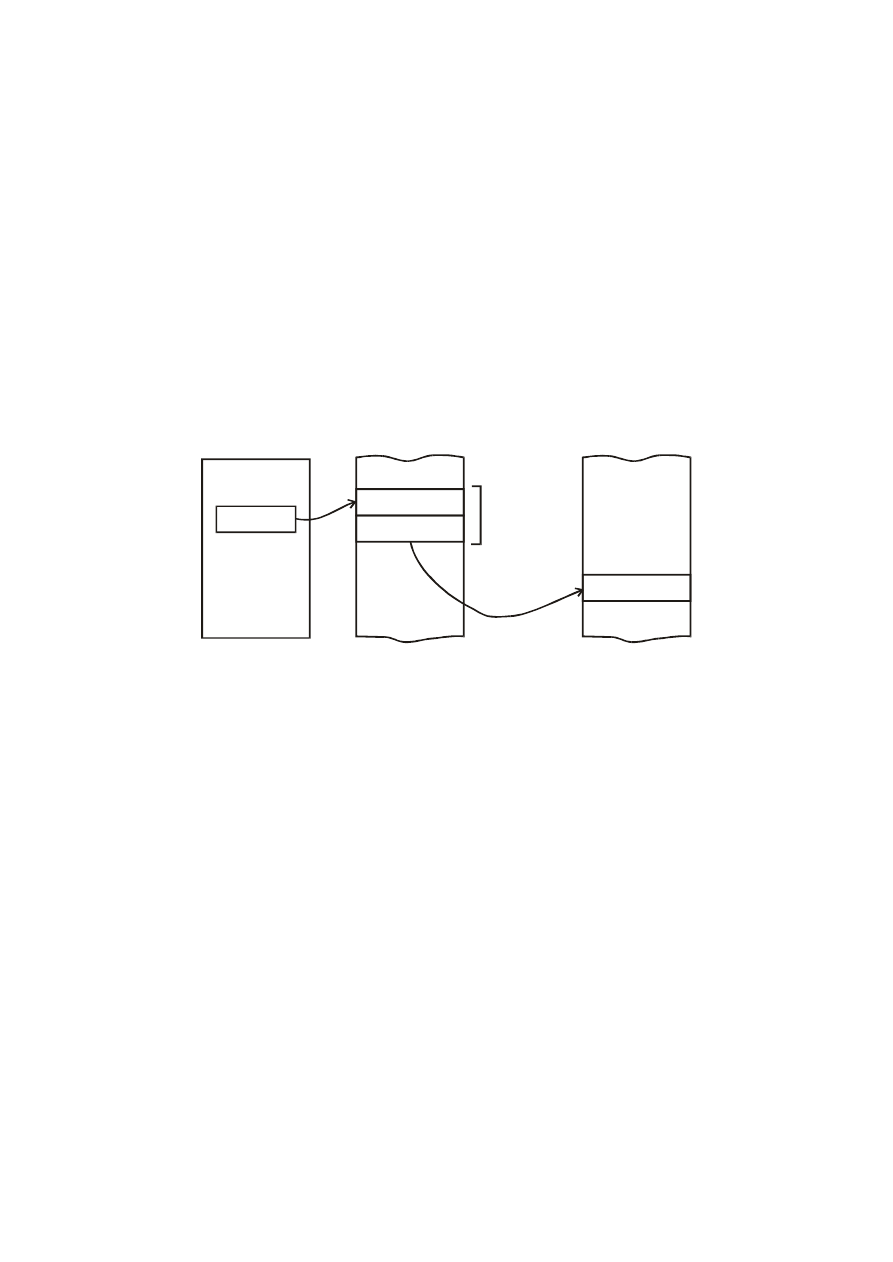

Tabela 4. Oznaczenia kolejnych bitó w rejestru maski przerwań (IP).

numer

bitu

oznaczenie

poziom priorytet ź ródł

o przerwania

7

-

6

-

5

-

4

PS

port szeregowy

3

PT1

ukł

ad licznikowy T1

2

PX1

przerwanie zewnę trzne INT1

1

PT0

ukł

ad licznikowy T0

0

PX0

przerwanie zewnę trzne INT1

Szczegół

owy opis obsł

ugi przerwań wraz z przedstawieniem reguł

określają cych

podejmowanie obsł

ugi na podstawie ich priorytetów zostanie przedstawiony w rozdziale

„Przerwania”.

2.1.2. Pamięć

Ze wzglę du na to że, mikrokontrolery rodziny 8051 są mikrokontrolerami ośmiobitowymi,

komórki obsł

ugiwanej przez nie pamię ci są jednobajtowe. Uwaga ta dotyczy zarówno

pamię ci programu jak i pamię ci danych.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

15

Mikrokontrolery 8051 posiadają odrę bne przestrzenie adresowe dla wewnę trznej i

zewnę trznej pamię ci danych. Przestrzeń adresowa pamię ci wewnę trznej ma 256 bajtów

oznacza to, że adresy komórek wewnę trznej pamię ci danych są jednobajtowe. Natomiast

zewnę trzna pamię ć danych adresowana jest dwubajtowo. Wynika stą d, że maksymalny

rozmiar tego rodzaju pamię ci wynosi 64 kilobajty. Do wymiany danych z oboma typami

pamię ci danych sł

użą różne rozkazy przesł

ań . Wewnę trzna pamię ć danych jest bardziej

elastyczna pod wzglę dem możliwości odwoł

ywania się do jej komórek. Mikrokontroler

pozwala stosować kilka trybów adresowania danych pamię ci wewnę trznej, natomiast w

przypadku zewnę trznej pamię ci danych dostę pny jest tylko jeden tryb adresowania (patrz

rozdział

tryby adresowania).

•

Wewnę trzna pamię ć danych

W wewnę trznej pamię ci danych można wyróżnić trzy obszary. (1) W pierwszych 128 bajtach

pamię ci (adresy 0-127) możliwe jest stosowanie dwóch trybów adresowania. (2) Górnemu

obszarowi pamię ci i (3) obszarowi rejestrów specjalnych odpowiada ten sam przedział

adresów (adresy 128-255), lecz oba obszary dostę pne są w innych trybach adresowania.

Przesył

ają c dane do komórki pamię ci o adresie z przedział

u 0-127, w jednym z dwóch

dostę pnych trybów, zapiszemy je w tej samej strukturze fizycznej. Zapis danych pod adresem

z przedział

u 128-255 zostanie dokonany jednym z rejestrów specjalnych lub górnym obszarze

wewnę trznej pamię ci danych w zależności od zastosowanego trybu adresowania.

W obszarze niskich adresów wewnę trznej pamię ci danych (adresy 0-127) znajdują się

4 banki rejestrów roboczych R0-R7. Umieszczono je pod adresami: 0-7, 8-15, 16-23, 24-31.

Obszar niskich adresów przeznaczony jest domyślnie do użytku przez stos. Po restarcie

mikrokontrolera wskaź nik stosu przyjmuje wartość 7. O ile programista nie zmieni wartości

wskaź nika stosu, pierwsze wrzucenie danych na stos spowoduje zapis danych do komórki

pamię ci o adresie 8. Z tego powodu, w mikrokontrolerze 8051 stos zaczyna się wypeł

niać w

miejscu, w którym istnieją trzy wyższe banki rejestrów roboczych. Aby móc jednoczenie

korzystać ze stosu i wyższych banków rejestrów R0-R7 należy przesuną ć wskaź nik stosu do

obszaru wyższych adresów. Adresy (48-127) w dolnym obszarze wewnę trznego RAM’u oraz

cał

y obszar górnej wewnę trznej pamię ci RAM (128-255) przeznaczone są do swobodnego

wykorzystania przez programistę .

W obszarze rejestrów specjalnych przechowywane są wszystkie (z wyją tkiem licznika

rozkazów) dostę pne programowo rejestry mikroprocesora oraz rejestry sł

użą ce do obsł

ugi

zintegrowanych

ukł

adów

peryferyjnych.

W

Tabeli 5

zebrano

adresy

rejestrów

mikrokontrolera omówionych poprzednim rozdziale. Watro zwrócić uwagę , iż 16 bitowy

wskaź nik danych DPTR przechowywany jest w pamię ci w dwóch kolejnych komórkach

oznaczonych DPL i DPH. Pod niższym adresem przechowywany jest mł

odszy bajt wskaź nika

danych (DPH), wyższy adres odnosi się do starszego bajta (DPH). Adresy i znaczenie bitów

rejestrów obsł

ugi ukł

adów peryferyjnych zostaną omówione w dalszej czę ści skryptu.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

16

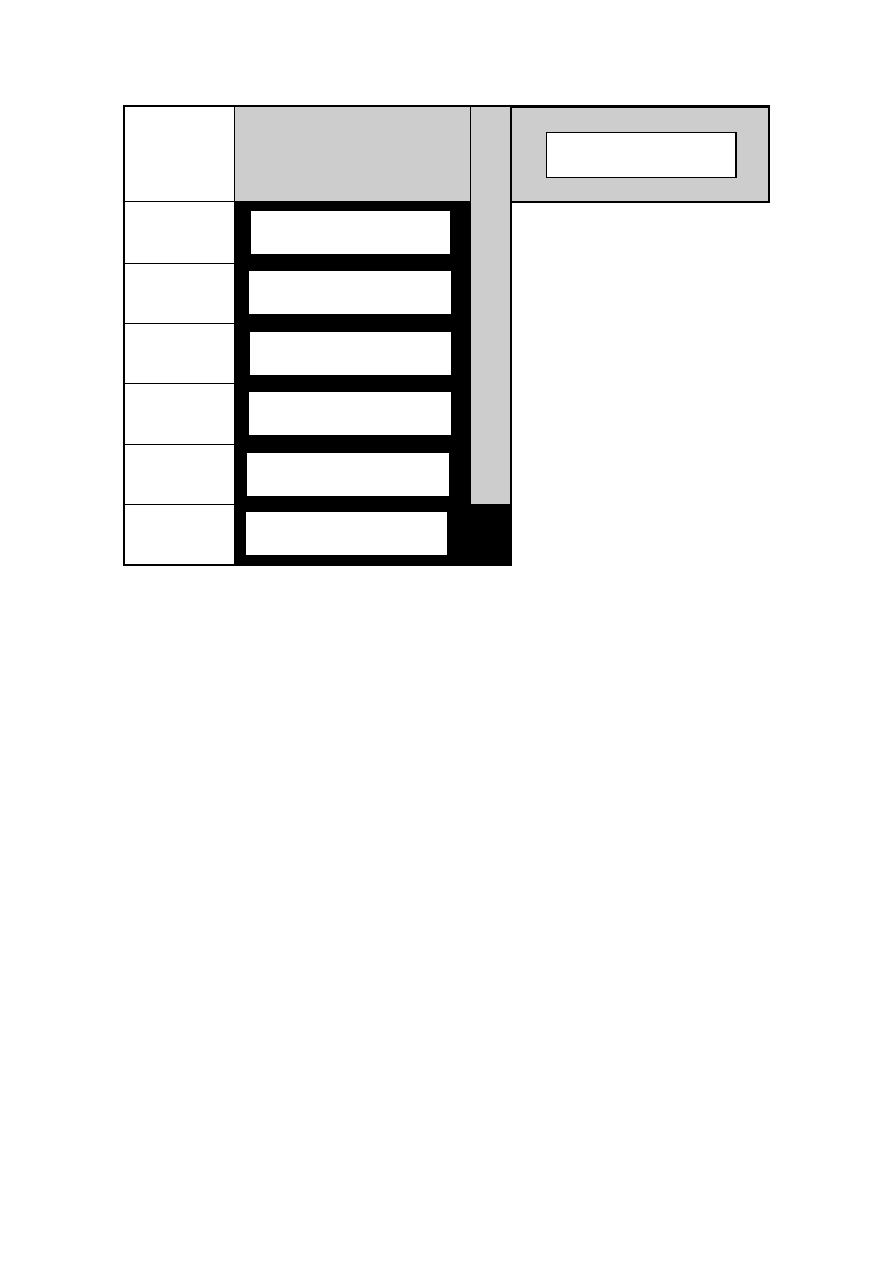

Tabela 5. Adresy podstawowych rejestró w mikrokontrolera 8051. Pocieniowane komó rki

wskazują rejestry o adresowanych bitach.

rejestr

opis

adres

B

akumulator pomocniczy

240 (F0

H

)

A

akumulator

224 (E0

H

)

PSW

rejestr stanu

208 (D0

H

)

IP

rejestr priorytetów przerwań

184 (B8

H

)

IE

rejestr maski przerwań

168 (A8

H

)

DHP

starszy bajt wskaź nika danych

131 (83

H

)

DPL

mł

odszy bajt wskaź nika danych

130 (82

H

)

SP

wskaź nik stosu

129 (81

H

)

Mikrokontroler 8051 pozwala odwoł

ywać się do poszczególnych bitów w wybranych

komórkach wewnę trznej pamię ci danych. Adresowane bity posiada 16 komórek pamię ci w

niskim obszarze pamię ci oraz 16 rejestrów specjalnych. W niskim obszarze pamię ci bajty z

adresowanymi bitami zajmują cią gł

y obszar (adresy 32-47), natomiast adresowane bity

posiada co ósmy rejestr specjalny (128, 136, 144, ... ,248). Wśród adresowalnych rejestrów

mikroprocesora tylko wskaź nik stosu (SP) oraz wskaź nik danych (DPTR) nie posiadają

adresowalnych bitów. Adresy rejestrów: A, B, PSW, IP, IE dzielą się przez osiem, co

wskazuje iż do bitów tych rejestrów można odwoł

ywać się bezpośrednio. Ł atwo się wykazać,

że mikrokontroler 8051 dysponuje 256-ma adresowanymi bitami (dwie 16 bajtowe grupy

komórek pamię ci). Adres bitu należą cego do jednej z szesnastu komórek niskiego RAM’u

(32-47) adresy można wyznaczyć zgodnie z poniższym wzorem:

adres_bitu = (adres_bajtu-32)*8 + numer_bitu_w_bajcie

gdzie adres_bajtu oznacza adres jednej z szesnastu komórek pamieci (adresy 32-47), a

numer_bitu_w_bajcie określa numer bitu w komórce pamię ci (0 – najmł

odszy bit, 7-

najstarszy bit). Np. trzeci bit w komórce o adresie 39 ma przyporzą dkowany adres równy: 59.

Adresy bitów rejestrów specjalnych można wyrazić wzorem:

adres_bitu = adres_bajtu + numer_bitu_w_bajcie

Wynika stą d, że najmł

odszy bit rejestru specjalnego ma taki sam adres jak komórka pamię ci

w której znajduje się rejestr.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

17

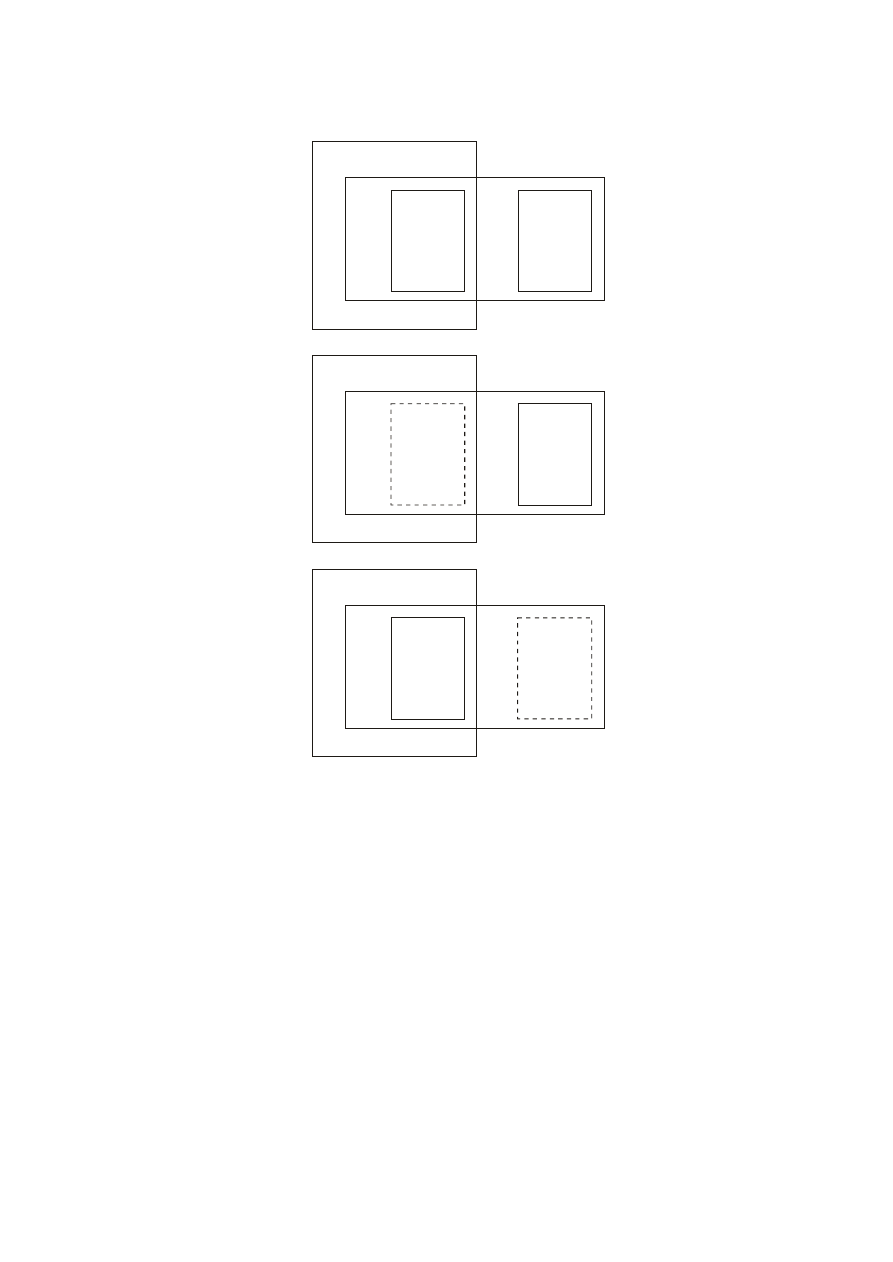

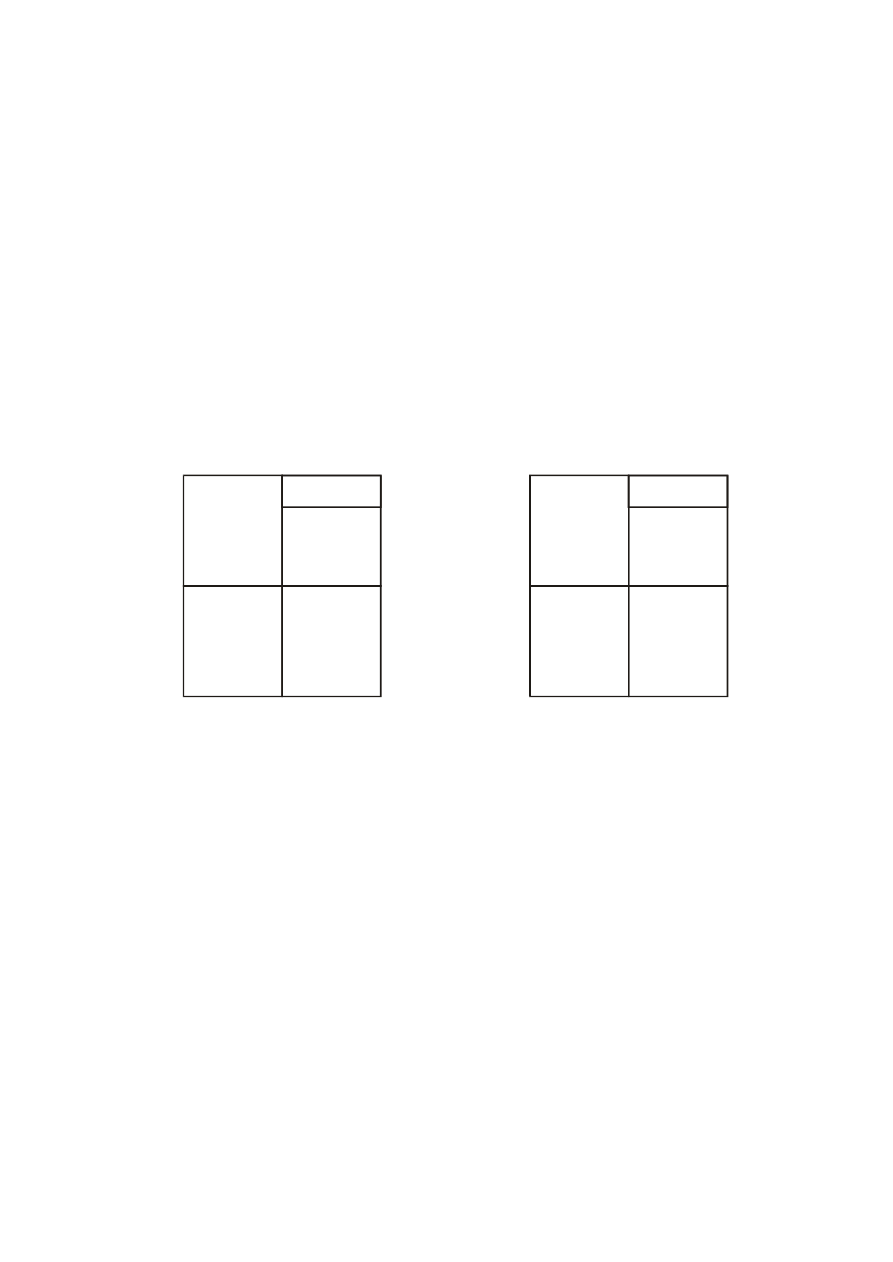

128-255

(80-FF)

H

pami

ęć ogólnego

przeznaczenia

048-127

(30-7F)

H

032-047

(20-2F)

H

024-031

(18-1F)

H

016-023

(10-17)

H

008-015

(08-0F)

H

S

t

o

s

000-007

(00-07)

H

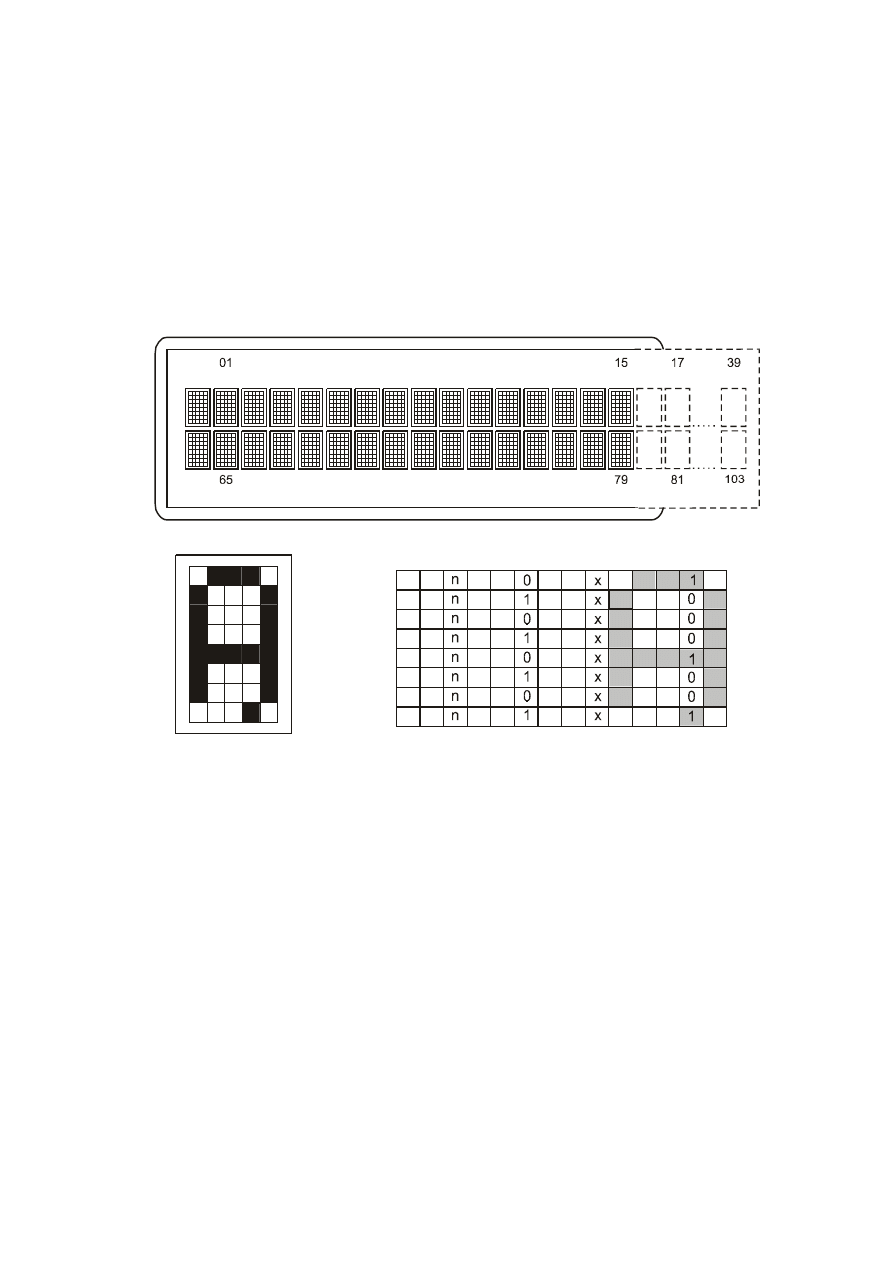

Rys.3. Organizacja wewnę trznej pamię ci danych mikrokontrolera 8051. Obszary

zakreskowane oznaczają pamię ć adresowaną bezpośrednio (poprzez podanie adresu

komó rki), obszary cieniowane – pamię ć adresowaną pośrednio (za pomocą rejestru

wskaźnikowego).

•

Zewnę trzna pamię ć danych

Zewnę trzna pamię ć danych na przestrzeń adresową wynoszą cą 64 kilobajty. Adresy komórek

tej pamię ci są zatem liczbami dwubajtowymi. Do adresowania tego rodzaju pamię ci używa

się dwubajtowego wskaź nika danych DPTR oraz rejestrów roboczych R0 albo R1. W drugim

przypadku w rejestrze R0 lub R1 zapisuje się mł

odszy bajt adresu. Starszy bajt adresu

wystawiany jest na wyjście portu P2. Adresowanie pośrednie zewnę trznej pamię ci danych

przy pomocy rejestrów DPTR, R0 i R1 zostanie omówione w detalach w rozdziale

poświę conym trybom adresowania.

Dostę p do zewnę trznej pamię ci danych na ogół

trwa dł

użej niż w przypadku

wewnę trznego RAM’u (każdy z rozkazów przesł

ania trwa dwa cykle maszynowe). Pamię ć ta

jest też mniej elastyczna niż wewnę trzna pamię ć danych. Zewnę trzny RAM można adresować

tylko w jednym trybie, ponadto wymiana danych odbywa się tutaj zawsze za pośrednictwem

akumulatora. Aby przesł

ać z jednej komórki zewnę trznej pamię ci danych do drugiej należy

najpierw przesł

ać dane do akumulatora, a nastę pnie innym rozkazem wysł

ać zawartość

akumulatora pod docelowy adres.

Programista może wykorzystywać zewnę trzną pamię ć danych w zasadzie bez

wię kszych ograniczeń . Mikrokontroler 8051 nie posiada odrę bnej przestrzeni adresowej dla

zewnę trznych urzą dzeń wejścia/wyjścia, wię c komunikacja mikroprocesora z zewnę trznymi

obszar rejestr

ów

specjalnych

pami

ęć ogólnego

przeznaczenia

kom

órki o

adresowanych bitach

bank 3

rejestr

ów roboczych

bank 2

rejestr

ów roboczych

bank 1

rejestr

ów roboczych

bank 0

rejestr

ów roboczych

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

18

ukł

adami peryferyjnymi odbywa się identycznie jak wymiana danych z zewnę trznym

RAM’em. W przestrzeni adresowej zewnę trznej pamię ci danych wydziela się (kosztem

zmniejszenia ilości zainstalowanej pamię ci RAM) pewien obszar, który zarezerwowany jest

dla ukł

adów wejścia/wyjścia. Organizacja przestrzeni adresowej zewnę trznej pamię ci danych

zostanie omówiona niżej na przykł

adzie systemu DSM-51. W rozdziale „Ukł

ady systemu

DSM-51” zostanie przedstawiony sposób adresowania zewnę trznych ukł

adów peryferyjnych

(umieszczonych na pł

ycie DSM-51) oraz organizacja magistrali systemu DSM-51.

•

Pamię ć programu

Wię kszość mikrokontrolerów 8051 umożliwia korzystanie z wewnę trznej i zewnę trznej

pamię ci programu. Tylko nieliczne modele rodziny 8051 pozbawione są wewnę trznej pamię ci

programu (w systemie DSM-51 zastosowano ukł

ad 80C31 który może korzystać wył

ą cznie z

pamię ci zewnę trznej). Pamię ć programu zintegrowana w ukł

adzie 8051 może zostać

wykonana w wielu technologiach. (1) W przypadku pamię ci typu ROM program wpisany jest

trwale w procesie technologicznym (za pomocą naświetlania maską ). (2) Pamię ci typu

EPROM i (3) EEPROM (flash) mogą być zapisywane w warunkach warsztatowych za

pomocą tzw. programatorów. Urzą dzenia te poprzez porty P1 i P2 przesył

ają się adresy

komórek pamię ci; port P0 wykorzystują natomiast do wysył

ania danych. W trakcie

zapisywania pamię ci programu programator taktuje mikrokontroler sygnał

em zegarowym.

Kasowanie pamię ci EPROM jest możliwe tylko wówczas, gdy w obudowie mikrokontrolera

znajduje się krzemowe okienko pozwalają ce naświetlić strukturę ukł

adu promieniami

ultrafioletowymi. Tań sze ukł

ady w plastykowej obudowie (pozbawione okienka

krzemowego) umożliwiają jedynie jednokrotne zapisanie pamię ci programu. W przypadku

ukł

adów EEPROM kasowanie wewnę trznej pamię ci programu odbywa się poprzez wysł

anie

odpowiednich sygnał

ów sterują cych.

W pewnych sytuacjach zapisany w pamię ci wewnę trznej program musi być chroniony

przez możliwością jego odczytania, dopisania dalszych fragmentów kodu, czy też podł

ą czenia

zewnę trznej pamię ci programu. Zabezpieczenia te można uaktywnić w ukł

adzie wysył

ają c

odpowiednie sygnał

y sterują ce w procesie zapisywania wewnę trznej pamię ci programu.

Ponadto programowalne wersja mikrokontrolera 8051 posiadają w swojej strukturze tzw.

tabelę szyfrują ca. W zależności od wersji mikrokontrolera liczy ona 16, 32 lub 64 bajty. Po

ustawieniu odpowiednich sygnał

ów sterują cych ładowanie tabeli szyfrują cej przebiega

podobnie jak zapisywanie pamię ci programu. Odczyt (weryfikacja) pamię ci programu przez

programator daje wówczas nastę pują cy rezultat:

dane_odczytane = not ( dane_zapisane exor dane_tablicy_szyfrującej[i] )

gdzie

i = adres_danych mod długość _tablicy_szyfrującej

Nieznajomość tablicy szyfrują cej praktycznie uniemożliwia poprawne odczytanie pamię ci

programu.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

19

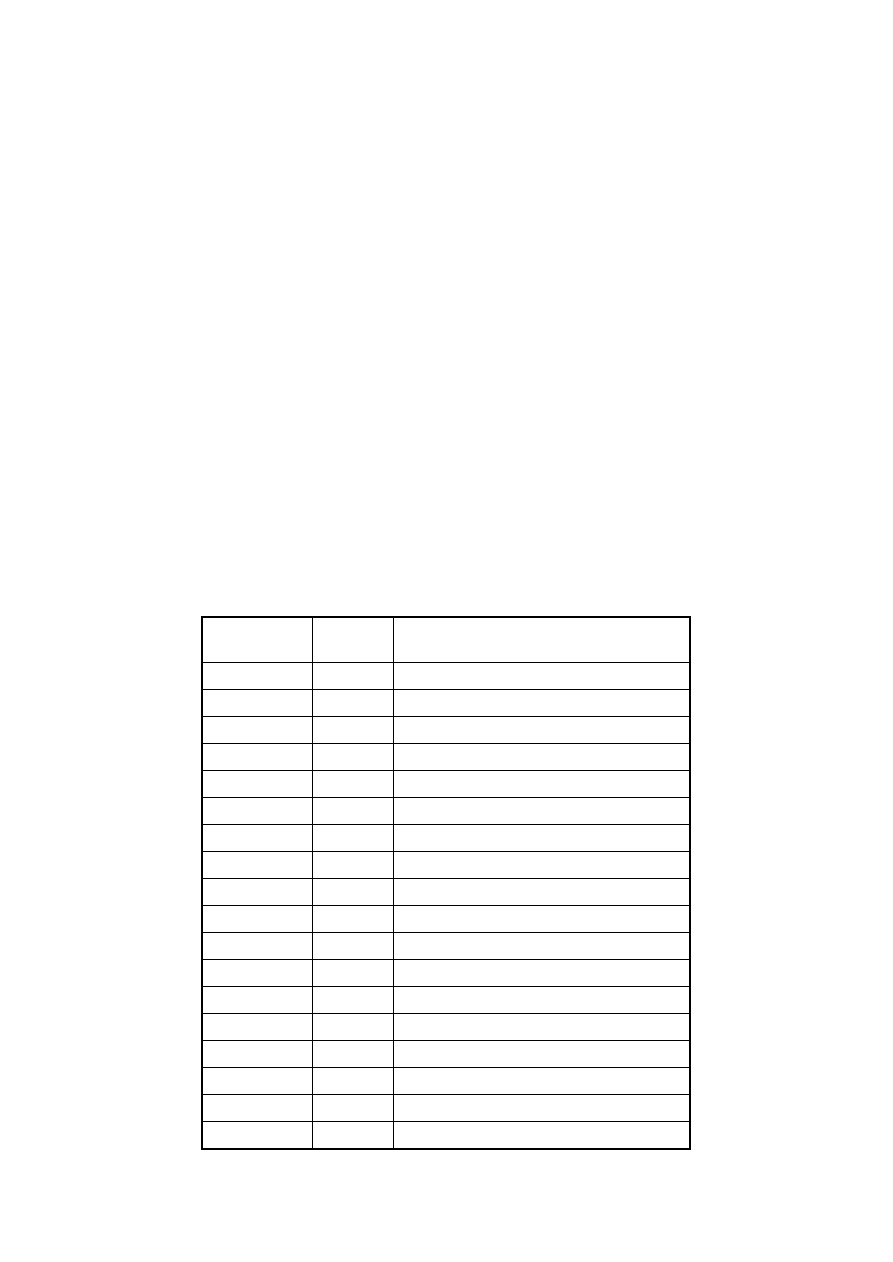

zewn trzna

pami

ę

ę ć

programu

mikrokontroler

b)

32767

7FFF

(

H

)

0000

0000

H

(

)

w

pami

ewn

ę trzna

ę ć

programu

mikrokontroler

c)

32767

7FFF

(

H

)

0000

0000

H

(

)

w

pami

ewn

ę trzna

ę ć

programu

zewn trzna

pami

ę

ę ć

programu

mikrokontroler

a)

32767

7FFF

(

H

)

0000

0000

H

(

)

65534

FFFF )

H

((

32768

8000

H

(

)

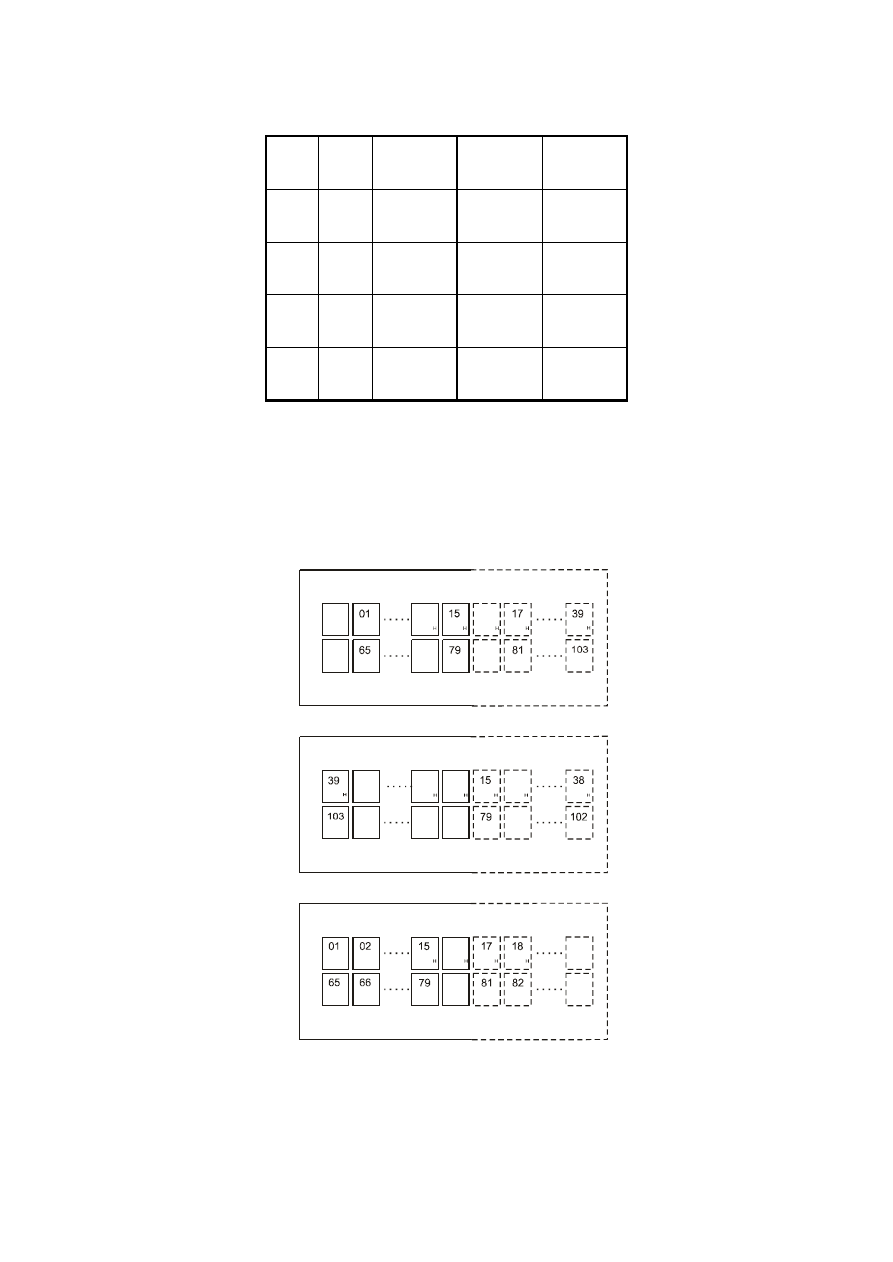

Rys.4. Organizacja pamię ci programu w mikrokontrolerze 8051. (a) Mikrokontroler

wykorzystuje zaró wno wewnę trzną jak i wewnę trzną pamię ć programu. (b) Mikrokontroler

nie posiada, bądź ma wyłączoną (koń có wka EA w stanie niskim) wewnę trzną pamię ć

programu. (c) W systemie istnie tylko aktywna pamię ć wewnę trzna.

Gdy w systemie istnieje zewnę trzna pamię ć programu wówczas należy ustalić z

którego rodzaju pamię ci mikrokontroler rozpocznie pobieranie kodu. Określa to stan jednego

z wyprowadzeń mikroprocesora oznaczonego jako EA. Gdy wyprowadzenie EA jest w stanie

wysokim to pierwsza wykonana instrukcja bę dzie pochodzić z pamię ci wewnę trznej. Po

wykonaniu cał

ego kodu zawartego w wewnę trznej pamię ci programu kolejny bajt kodu

bę dzie poprany z pierwszej komórki pamię ci zewnę trznej. Jeśli wyprowadzenie EA jest w

stanie niskim, to wykonywany jest wył

ą cznie kod zawarty w zewnę trznej pamię ci programu.

Wewnę trzna i zewnę trzna pamię ć programu traktowana jest w sposób jednolity. Z punktu

widzenia mikrokontrolera obie pamię ci tworzą spójna, cią gł

a, 64 kilobajtową przestrzeń

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

20

adresową pamię ci programu. Zgodnie z powyższym możliwe są zatem dwa warianty. (1) Gdy

wyprowadzenie EA znajduje się w stanie niskim to pierwsza komórka pamię ci zewnę trznej

ma wówczas adres równy 0 w przestrzeni adresowej pamię ci programu nie zależnie od tego

czy mikrokontroler posiada bą dź nie wewnę trzną pamię ć programu. Jeśli w mikrokontrolerze

istnie wewnę trzna pamię ć programu to jest ona niewidoczna dla systemu. (2) Jeśli

wyprowadzenie EA jest w stanie wysokim to adres 0 w przestrzeni adresowej odpowiada

począ tkowi wewnę trznej pamię ci programu, a pamię ć zewnę trzna stanowi kontynuacji

pamię ci wewnę trznej – pierwsza komórka zewnę trznej pamię ci danych ma adres równy

pojemności (wyrażonej w bajtach) pamię ci wewnę trznej.

Po (re)starcie mikrokontrolera licznik rozkazów przyjmuje wartość 0. Stą d też

pierwszy bajt kodu jest pobierany spod adresu 0. Pierwszy kod rozkazu asemblerowego musi

zatem być umieszczony pod tymże adresem. Jednakże obszar niskich adresów pamię ci

programu (począ wszy od adresu 3) jest zarezerwowany na procedury obsł

ugi przerwań . Z

tego też wzglę du pierwszy rozkaz kodu asemblerowego jest skokiem, który omija procedury

obsł

ugi przerwań i umożliwia rozpoczę cie wykonywania kodu w obszarze wyższych adresów.

2.1.3. Cykl rozkazowy

Wszystkie procesy zachodzą ce w systemie mikroprocesorowym synchronizowane są

periodycznym sygnał

em generatora określanego zwyczajowo jako sygnał

zegarowy. Kolejne

okresy sygnał

u zegarowego wyznaczają rytm i sekwencję wszystkich procesów

rozgrywają cych się w ukł

adzie. Mikroprocesor (mikrokontroler) jest zatem cyfrowym

ukł

adem sekwencyjnym. Stan ukł

adu sekwencyjnego jest funkcją dyskretnego czasu oraz

historii ukł

adu. Kwanty czasu wyznaczone są tu przez kolejne okresy sygnał

u zegarowego.

Mikrokontrolery

rodziny

8051

mają

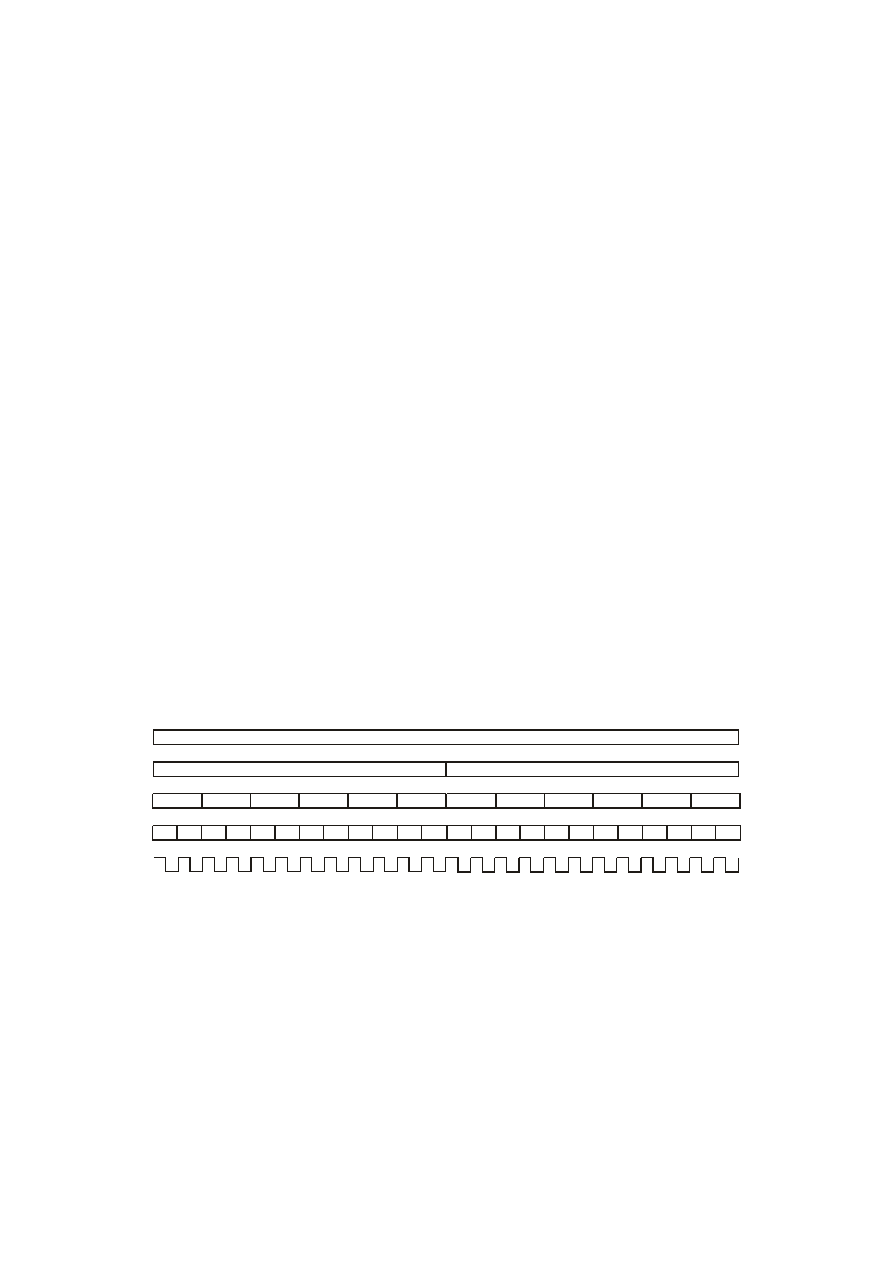

możliwość

wykorzystania

zarówno

wewnę trznego generatora sygnał

u zegarowego jak i podł

ą czenia generatora zewnę trznego. W

przypadku stosowania generatora wewnę trznego należy podł

ą czyć do wyprowadzeń

mikrokontrolera jedynie rezonator kwarcowy, który określi czę stotliwość sygnał

u

zegarowego. Niektóre wersje mikrokontrolerów 8051 pozwalają na taktowanie sygnał

em o

czę stotliwości 33 MHz. W systemie DSM-51 zastosowano zegar o czę stotliwości

11.0592 MHz.

Instrukcje (rozkazy) mikrokontrolera wykonywane są w tzw. cyklach rozkazowych. W

czasie trwania cyklu rozkazowego mikroprocesor podejmuje nastę pują ce akcje:

•

pobiera kodu operacji,

•

dekoduje kod operacji,

•

pobiera argumenty (operandy) rozkazu,

•

zwię ksza wartość licznika rozkazów,

•

wykonuje rozkaz,

•

zapisuje wynik.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

21

Pierwsze cztery etapy cyklu rozkazowego nazywa się fazą pobrania; dwa ostatnie są

określane jako faza wykonania.

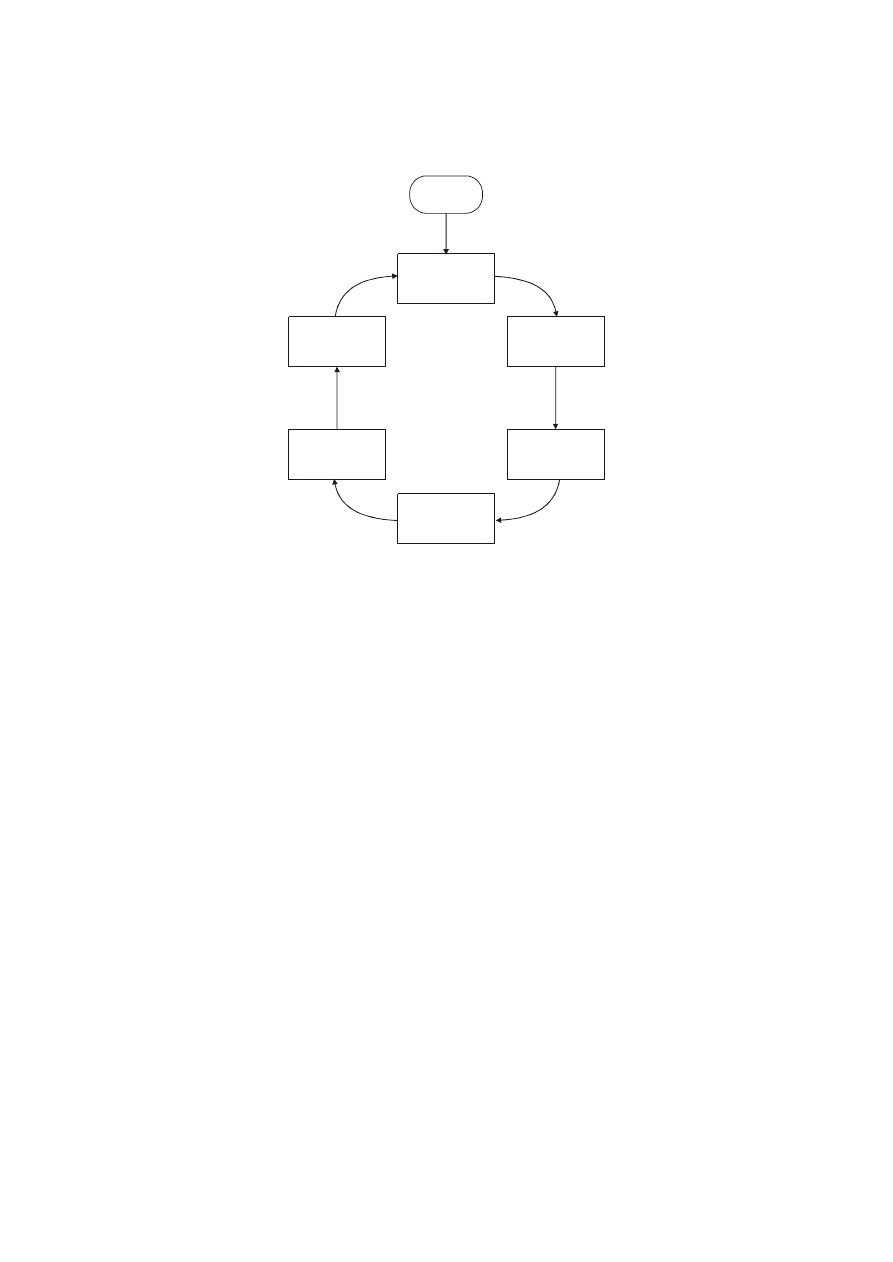

pobranie

kodu operacji

PC=0

pobranie

argument

ów

dekodowanie

kodu operacji

zwi

ę kszenie

PC

wykonanie

rozkazu

zapisanie

wynik

ów

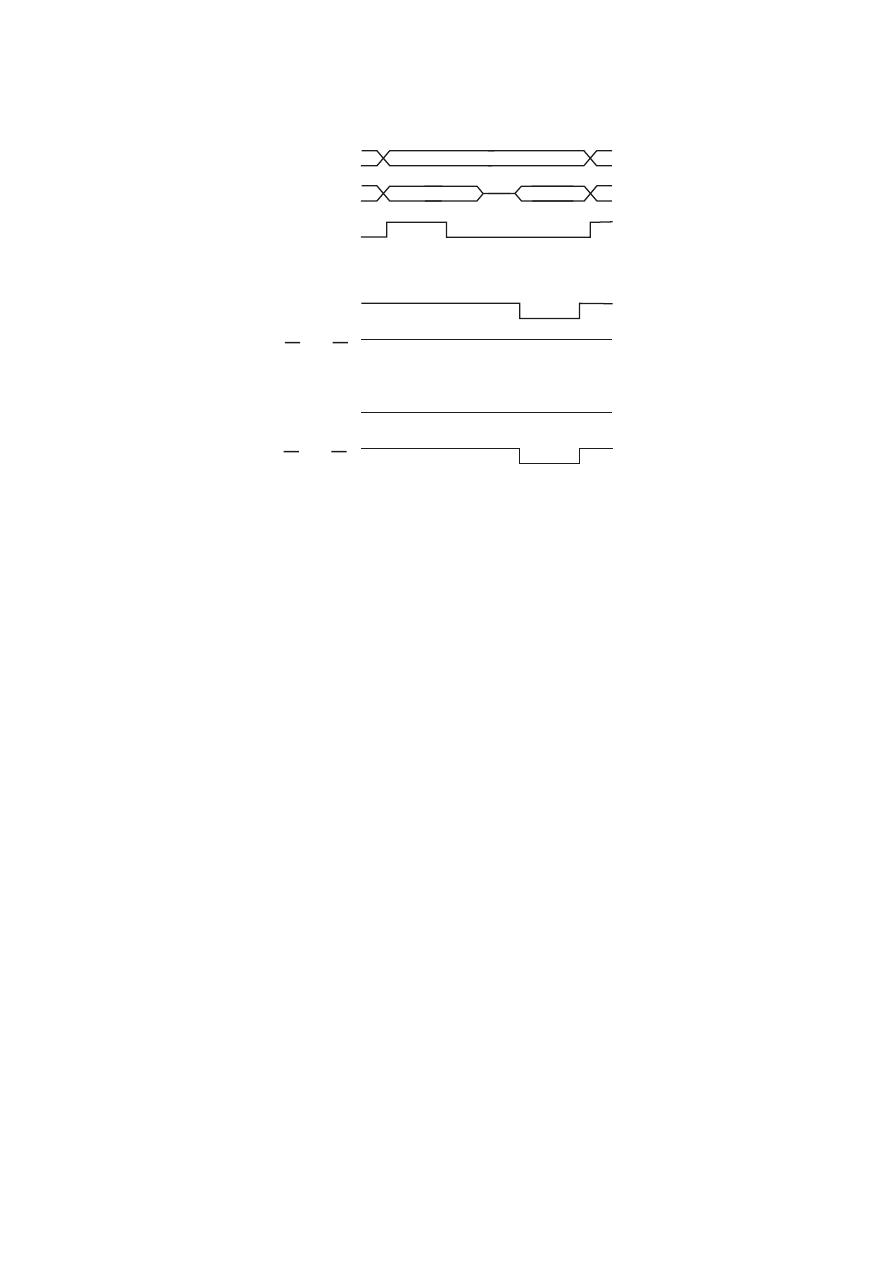

Rys.5. Cykl rozkazowy.

Pierwszy bajt w kodzie rozkazu jest tzw. kodem operacji. Unikalny, jednobajtowy kod

operacji określa rozkaz jaki ma wykonać mikroprocesor. W pierwszym etapie cyklu

rozkazowego kod ten przesył

any jest do rejestru rozkazów. Nastę pnie ma miejsce proces

dekodowania kodu operacji w ukł

adzie zwanym dekoderem rozkazów. Po zdekodowaniu

kodu operacji mikroprocesor uzyskuje informację o tym jak dł

ugi jest kod rozkazu, gdzie

znajdują się jego argumenty, jaka operację na wykonać i gdzie wysł

ać wynik operacji. W

dalszej kolejności zmieniana jest wartość licznika rozkazów. Licznik rozkazów zwię kszany

jest o dł

ugość kodu rozkazu wyrażoną w bajtach. Powyższa akcja koń czy fazę pobierania. W

fazie wykonania ma miejsce egzekucja rozkazu, oraz zapisanie ewentualnych wyników

dział

ania rozkazu.

Zilustrujmy powyższe rozważania nastę pują cym przykł

adzem. Zał

óżmy, że

mikroprocesor ma wykonać rozkaz polegają cy na zwię kszeniu o jeden komórki pamię ci

wewnę trznego RAM’u o adresie 50. Lina kodu asemblerowego przedstawiają ca taki rozkaz

ma postać.

INC 20

Przyjmijmy, iż w pamię ci programu kod tego rozkazu rozpoczyna się począ wszy od adresu

300. Powyższa linia kodu ź ródł

owego bę dzie reprezentowana w kodzie programu w

nastę pują cy sposób.

300 7

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

22

301 20

W pierwszej kolumnie umieszczono adresy komórek pamię ci programu; kolumna druga

zawiera wartości przechowywane komórkach pamię ci. Cał

y kod rozkazu zajmuje zatem dwa

bajty pamię ci programu. Wartość 7 (umieszczona pod adresem 300) oznacza kod operacji:

„zwię ksz o jeden zawartość komórki wewnę trznego RAM’u o adresie podanym w kodzie

rozkazu”. Liczba 20 znajdują ca się pod adresem 301 jest jedynym operandem rozkazu i

określa adres komórki pamię ci wewnę trznego RAM’u, której wartość ma zostać zwię kszona.

W fazie pobrania do rejestru rozkazów zostanie zał

adowana wartość 7. Dekoder rozkazów na

taj podstawie uzna, iż w kolejnej komórce pamię ci programu zawarty jest adres komórki

wewnę trznej pamię ci danych, której zawartość powinna być zwię kszona o jeden. Ze wzglę du

na to, że rozkaz o kodzie operacji równym 7 ma dł

ugość dwóch bajtów, licznik rozkazów

zostanie zwię kszony o 2. Po zakoń czeniu cyklu rozkazowego pozwoli to pobrać kod operacji

kolejnego rozkazu znajdują cy się pod adresem 302. W fazie wykonywania nastą pi

zwię kszenie o jeden wartości jaka został

a pobrana z komórki wewnę trznego RAM’u o adresie

20 i zapisanie wyniku pod tym samym adresem.

Czas trwania cyklu rozkazowego jest różny w zależności od rodzaju operacji oraz od

liczby, dł

ugości i trybu odwoł

ywania się do argumentów. Jest on jednak zawsze

wielokrotnością czasu trwania tzw. cyklu maszynowego. Wię kszość instrukcji wykonywana

jest w jednym lub w dwóch cyklach maszynowych. Jedynie dwie instrukcje: rozkaz mnożenia

i dzielenia wymagają czterech cykli maszynowych. Cykl maszynowy skł

ada się z sześciu

stanów oznaczonych: S1, S2, S3, ... , S6. Każdy ze stanów trwa dwa okresy sygnał

u

zegarowego (dwa cykle zegarowe). Wynika stą d że na cykl maszynowy przypada 12 cykli

zegarowych.

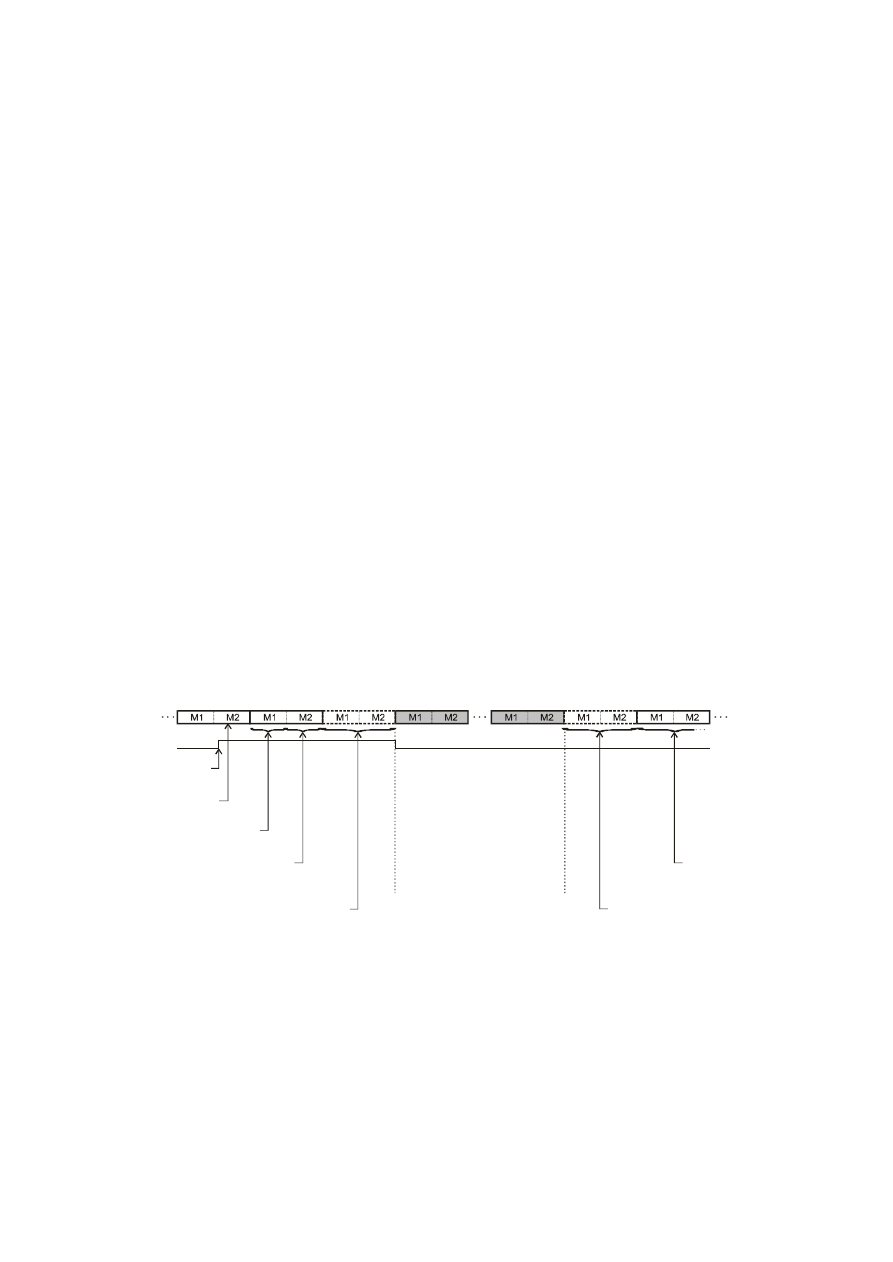

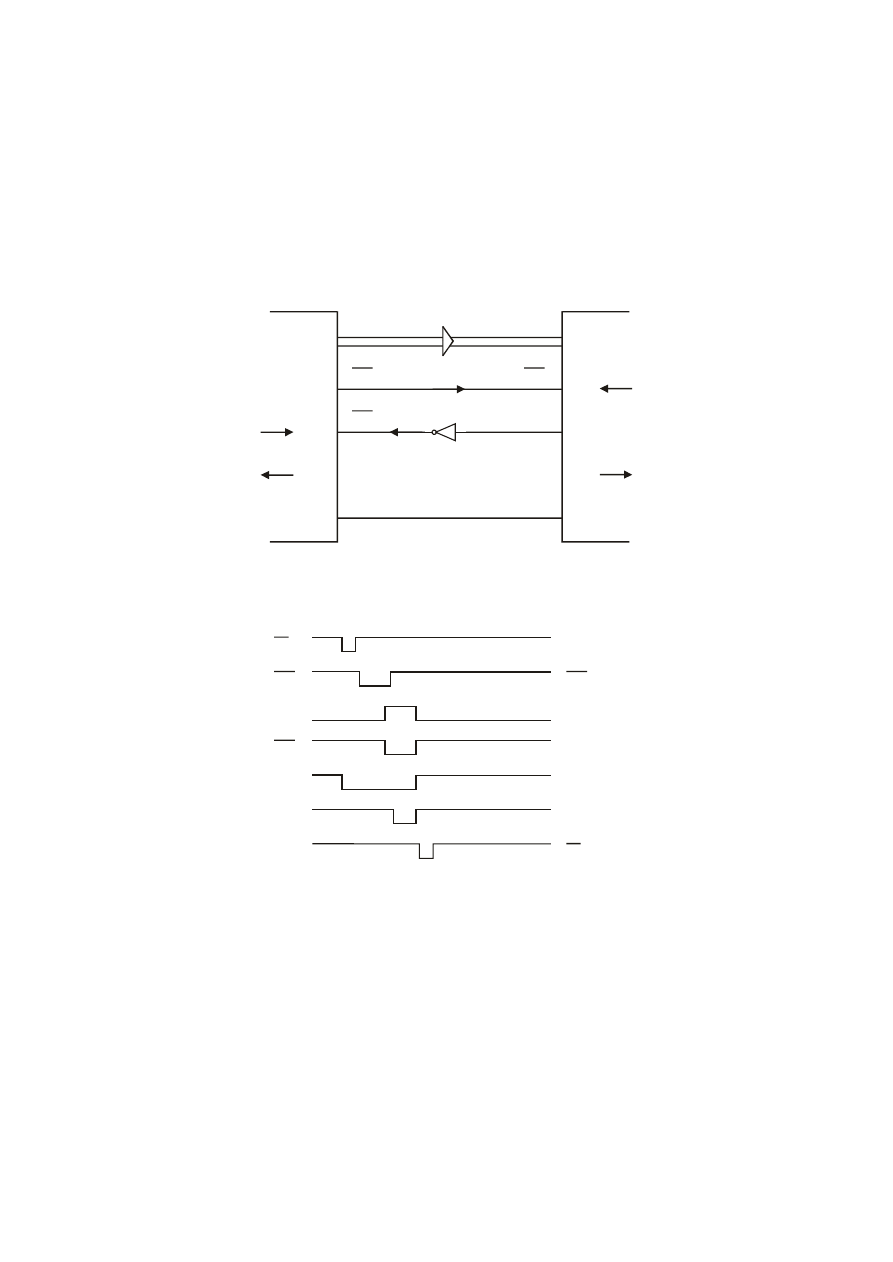

R

M1

M2

S1

S2

S3

S4

S5

S6

S1

S2

S3

S4

S5

S6

P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2

Rys.6. Podział cyklu rozkazowego na cykle maszynowe i zegarowe. Przedstawiono rozkaz

wykonywany w dwó ch cyklach maszynowych.

Czas cyklu rozkazowego można zatem wyznaczyć ze wzoru:

cykl_rozkazowy=12*ilość _cykli_maszynowych/czę stoliwość _zegara

Przykł

adowo, czas wykonywania instrukcji mnożenia w systemie DSM-51 wynosi

12*4/(11.0592 MHz)=4,3403

µ

s.

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

23

W niektórych z najnowszych wersji mikrokontrolerów rodziny 8051 cykl maszynowy

trawa 6, 4, czy nawet jeden cykl zegarowy. W ukł

adach tych przy niskiej czę stotliwości

zegara można czas wykonywania instrukcji jest stosunkowo krótki.

•

Zerowanie mikrokontrolera

Każdy mikroprocesor wyposażony jest ukł

ad zerowania, który zapewnia rozpoczę cie pracy

ukł

adu w ściele określonym stanie. Po wł

ą czeniu zasilania stan rejestrów i pamię ci

wewnę trznej mikrokontrolera jest nieokreślony. Z tego też wzglę du, każde rozpoczę cie lub

wznowienie pracy mikrokontrolera musi być poprzedzone specjalną procedurą zerowania. Po

jej zakoń czeniu wszystkie rejestry specjalne uzyskują ściśle określone wartości. Do

wię kszości rejestrów specjalnych zostaje wpisano wartość zero. Reguł

a ta dotyczy również

licznika rozkazów. Dzię ki temu po zakoń czeniu procedury zerowania mikrokontroler w

pierwszym cyklu rozkazowym pobiera kod począ wszy od adresu zero w pamię ci programu –

wznawia zatem wykonywanie programu do począ tku. Odmienne traktowane są jedynie:

wskaź nik stosu i porty mikrokontrolera. Do wskaź nika stosu zostaje wpisany adres 7

(pierwszy wpis na stos odbywa się pod adres 8), a do wszystkich czterech portów wysł

ana

wartość 255 (wszystkie linie portów zostają ustawione w stan wysoki). Zerowanie

mikrokontrolera nie zmienia stanu jego pamię ci wewnę trznej. Z tego też wzglę du

przechowywane w wewnę trznym RAM’ie rejestry robocze nie są zerowane.

Sygnał

reset wprowadzany jest poprzez jedną z koń cówek mikrokontrolera oznaczoną

RST. Koń cówka RST zwykle podł

ą czona jest do masy (lub dodatniego bieguna zasilana przy

przeciwnej polaryzacji sygnał

u reset) poprzez kondensator. Dzię ki temu krótko po wł

ą czeniu

zasilania na wejściu RST generowany jest impuls sygnał

u reset. Zerowanie mikrokontrolera

może być również przeprowadzone w trakcie wykonywania programu w przypadku

stwierdzenia jego nieprawidł

owego dział

ania. Zerowanie może być przeprowadzone

automatycznie przez specjalny ukł

ad (określany jako tzw. watchdog) lub wywoł

ane na

żą danie użytkownika (np. przez wciśnię cie odpowiedniego przycisku).

2.1.4. Zintegrowane układy peryferyjne

Do

wystę pują cych

najpowszechniej

zintegrowanych

ukł

adów

peryferyjnych

mikrokontrolerów rodziny 8051 można zaliczyć: porty równoległ

e, ukł

ady licznikowo –

zegarowe oraz port szeregowy. W bieżą cym rozdziale zostanie przedstawiona krótka

charakterystyka każdego z wymienionych ukł

adów. Zamieszczony opis nie bę dzie jednak

wyczerpują cy – zostanie ograniczony do podstawowych informacji dotyczą cych budowy i

obsł

ugi ww. urzą dzeń .

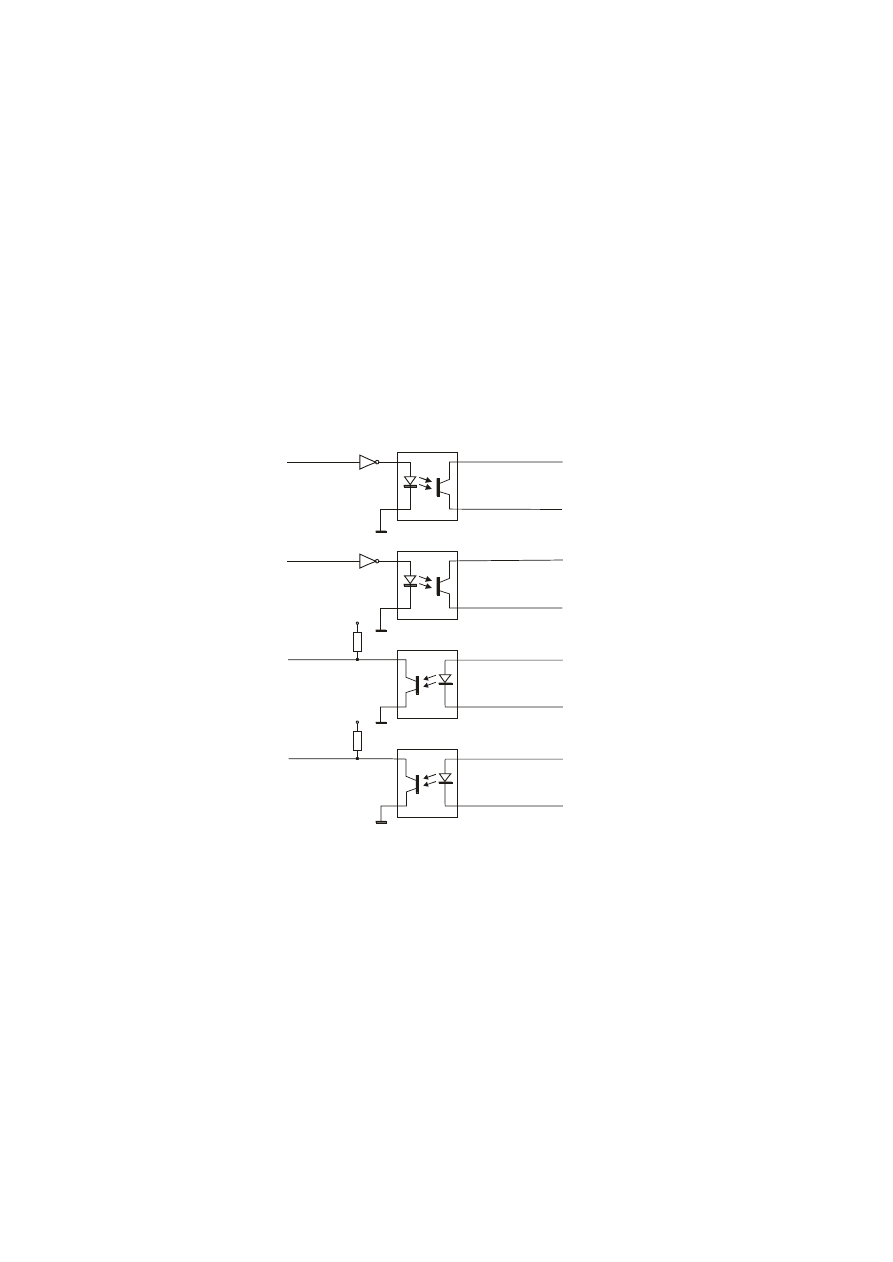

•

Porty równoległ

e

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

24

Wię kszość mikrokontrolerów rodziny 8051 zawiera trzy ośmiobitowe porty. Do obsł

ugi

portów sł

użą trzy rejestry specjalne oznaczone P0, P1, P2, P3. Odczyt danych z któregoś z

wymienionych rejestrów jest równoważny pobraniu danych z odpowiedniego porty. Wysł

anie

danych na jeden z portów odbywa się poprzez wpisanie zadanej wartości do wł

aściwego

rejestru.

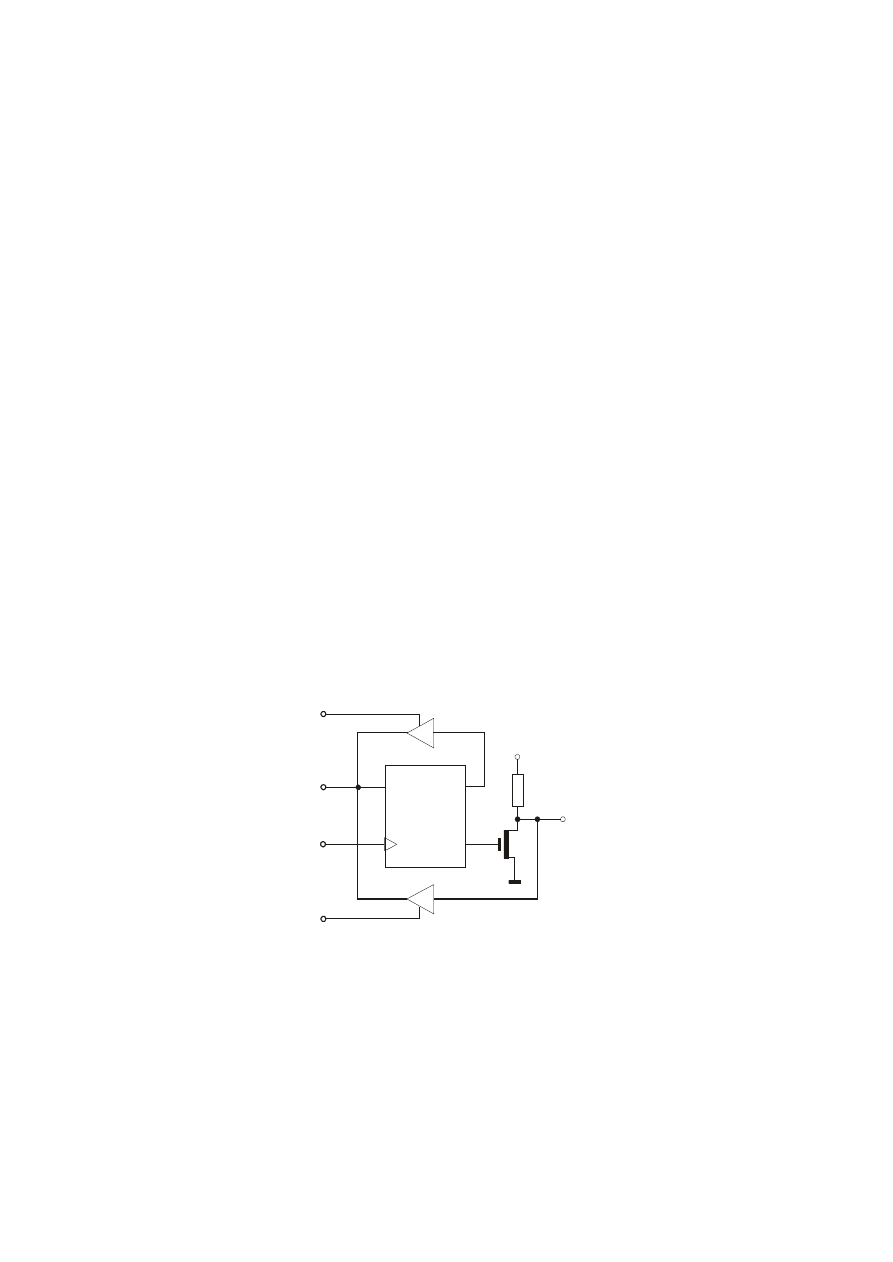

Na koń cówkach dowolnego z portów znajdują się przerzutniki, które pamię tają

ostatnio zapisane dane. Odczyt danych z portu może zatem przebiegać w dwojaki sposób. (1)

Można odczytać bezpośrednio stan koń cówek portu, lub (2) dokonać odczytu stanów

zatrzaśnię tych w przerzutnikach. W pierwszym przypadku uzyskamy informację o stanie

zewnę trznych linii podł

ą czonych do portu – w tej sytuacji odczytujemy sygnały zewnę trzne.

W przypadku drugim, dowiadujemy się jakie dane zapisano ostatnio na port – w tych

okolicznościach pobieramy sygnał

wewnę trzny. Z tego wzglę du, dla portów równoległ

ych

ukł

adu 8051 przewidziano dwa sygnał

y odczytu danych sterują ce trójstanowymi buforami,

które podł

ą czają linie wewnę trznej magistrali danych do wyjść przerzutników lub koń cówek

portów.

Na koń cówkach portów umieszczono tranzystory sterowane (zanegowanymi)

wyjściami przerzutników. Jeśli do przerzutnika wpiszemy logiczną jedynkę wówczas kanał

tranzystora bę dzie zablokowany i koń cówka portu uzyska poprzez rezystor pocią gają cy

wysoki potencjał

. Wpisanie zera do przerzutnika udrażnia kanał

tranzystora i powoduje

zwarcie koń cówki portu do masy. Ł atwo zauważyć, że aby prawidł

owo odczytać stan

koń cówek portu należy uprzednio wpisać do portu (przerzutników) jedynki.

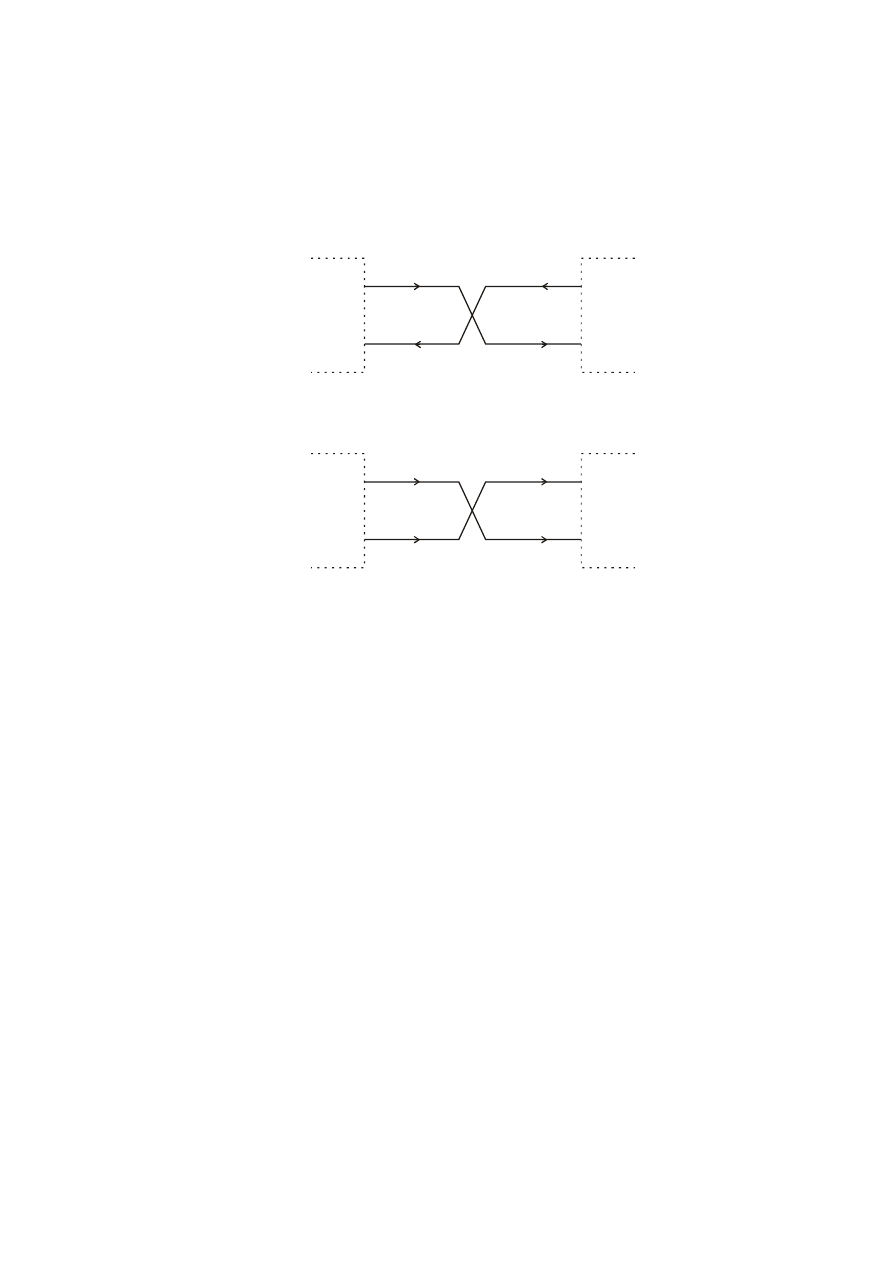

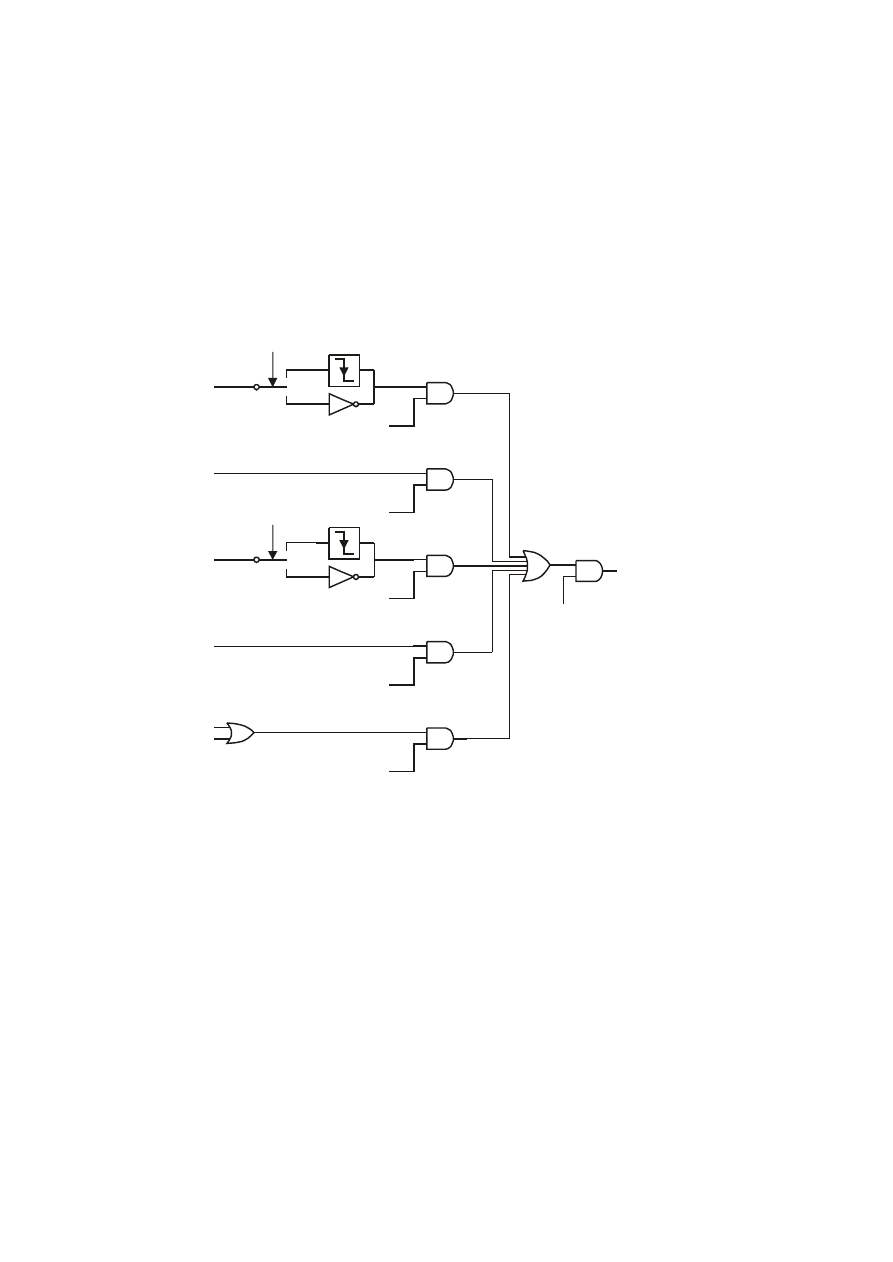

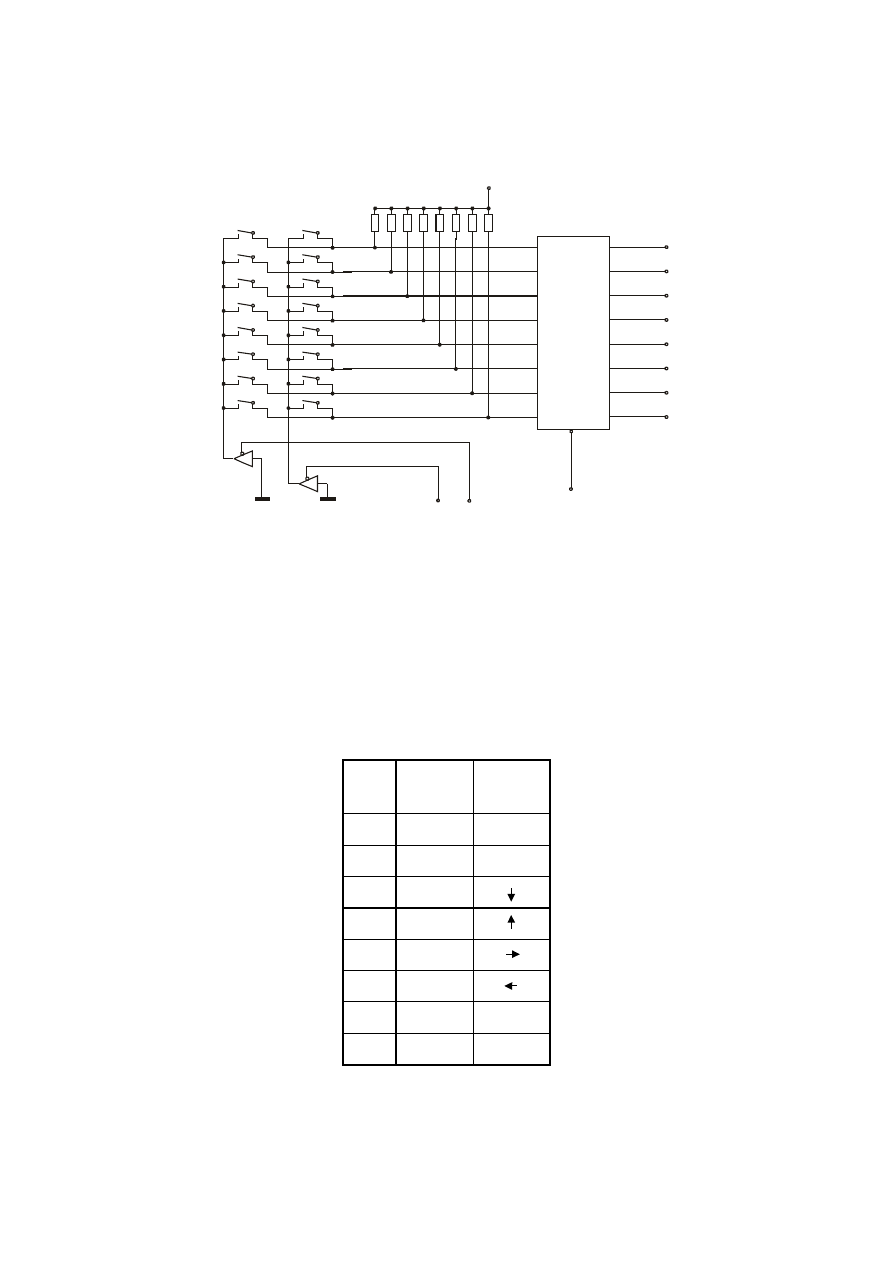

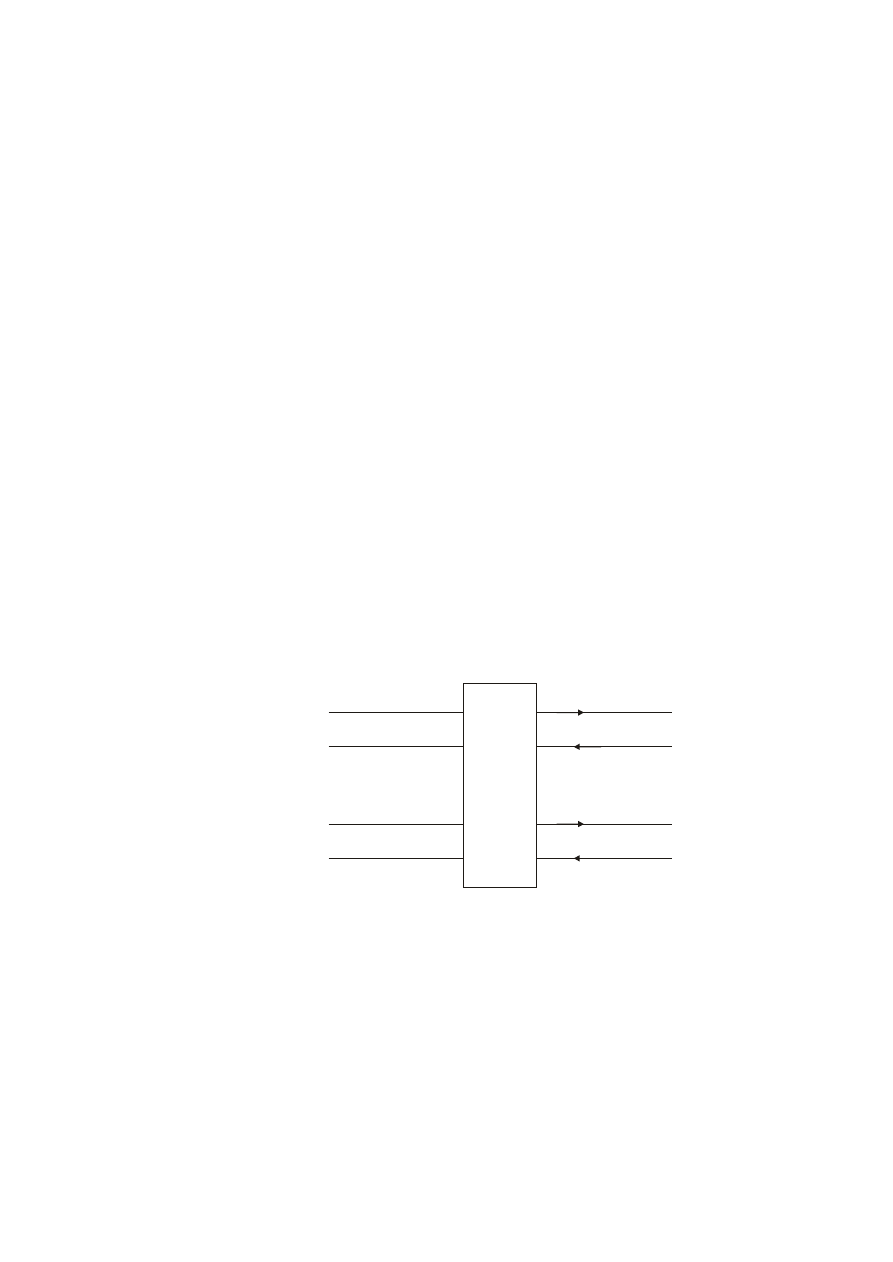

CLK

Q

Q

_

D

V

cc

zapis

dane

odczyt

ko

ó wki

ń c

odczyt

przerzutnika

ko

ń cowka

Rys.7. Budowa koń có wki portu.

Kilka instrukcji mikrokontrolera pobiera argument spod komórki pamię ci o podanym

w kodzie rozkazu adresie, a nastę pnie, co charakterystyczne, zapisuje wynik operacji adresem

tego operandu. (Pozostał

e instrukcje umieszczają wynik operacji w akumulatorze.)

Wspomniane instrukcje określa się jako tzw. instrukcje odczyt-modyfikacja-zapis. Jeśli adres

jest adresem portu to instrukcja typu odczty-modyfikacja-zapis odczytuje stany zatrzaśnię te w

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

25

przerzutnikach portu. Inne instrukcje odwoł

ują ce się do portów mikrokontrolera odczytują

natomiast stan koń cówek portów. Ich wykonanie musi być wię c poprzedzone wysł

aniem na

port ‘jedynek’. Po (re)starcie w przerzutnikach portów zapisane są jedynki. Oznacza to, że

pierwszy odczyt portu przez instrukcje typu odczyt-modyfikacja zapis da wartość 255.

W obszarze rejestrów specjalnych portom P0, ... ,P3 został

y przyporzą dkowane

odpowiednio adresy: 128, 144, 160, 176. Jak ł

atwo zauważyć wszystkie porty

mikrokontrolera mają adresowalne bity. Daje to programiście możliwość odczytu i zmiany

stanu pojedynczych bitów w porcie. Jednakże instrukcje które adresują pojedyncze bity

portów są instrukcjami typu odczty-modyfikacja-zapis. Instrukcje te odczytują stany zapisane

w przerzutnikach portów a nie stany wystę pują ce na koń cówkach portów. Watro mieć

świadomość faktu, że wspomniane instrukcje odczytują wewnę trzny stan wszystkich ośmiu

linii portu, a nastę pnie wykonują operację tylko na wskazanym bicie, po czym dokonują

zapisu cał

ego, zmodyfikowanego w ten sposób bajta na port. Powyższe uwagi są bardzo

istotne dla prawidł

owego zrozumienia zasad obsł

ugi portów. Niuanse dotyczą ce

programowania zostaną omówione szerzej w rozdziale 4.1. Porty.

Na portach P0 i P2 zbudowana jest zewnę trzna magistrala danych i zewnę trzna

magistrala adresowa mikrokontrolera. Obie magistrale wymieniają ł

ą cznie 24 sygnały (16

linii magistrali adresowej i 8 linii magistrali danych). Aby skoncentrować obie magistrale na

16 koń cówkach portów prowadzono multipleksowanie sygnał

ów wymienianych przez port

P0. Na port P2 wystawiany jest starszy bajt adresu. Mł

odszy bajt adresy pojawia się na porcie

P0 chwilę póź niej, gdy wystawione uprzednio na koń cówki portu P0 dane zostaną zapisane w

zewnę trznym buforze zatrzaskowym. Port P3 wykorzystywany jest do wymiany kilku

sygnał

ów sterują cych pracą zewnę trznych magistrali oraz sygnałów przerwań . Pozostałe

koń cówki portu P3 używane są przez ukł

ady licznikowe oraz port szeregowy. Jeśli porty P0,

P2 i P3 nie są wykorzystywane do wyżej wymienionych celów mogą sł

użyć do bezpośredniej

wymiany danych tak jak port P1.

Współ

praca mikrokontrolera 8051 z ukł

adami zewnę trznymi (takimi jak pamię ć

danych, pamię ć programu oraz ukł

ady wejścia/wyjścia) w oparciu o zewnę trzne magistrale

zostanie omówiona w kolejnym rozdziale na przykł

adzie systemu DSM-51.

•

Ukł

ady licznikowo – czasowe

Typowy przedstawiciel rodziny ukł

adów 8051 zawiera w swojej strukturze dwa

szesnastobitowe ukł

ady licznikowo – czasowe oznaczane T0 i T1. Ukł

ady te dział

ają jako

dzielniki czę stotliwości i mają możliwość zliczania cykli maszynowych mikrokontrolera lub

impulsów pochodzą cych ze ź ródeł

zewnę trznych. Zliczanie impulsów zewnę trznych odbywa

się przez czwartą i pią tą koń cówkę portu P3. Impulsy z linii P3.4 i P3.5 inkrementują

odpowiednio licznik T0 i T1. Mikrokontroler sprawdza stan czwartej i pią tej koń cówki portu

P3 w pierwszym cyklu zegarowym stanu S3 każdego cyklu maszynowego. Inkrementacja

odpowiedniego licznika ma miejsce wówczas, gdy stan linii P3.4 lub P3.5 ulegnie zmianie w

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

26

kolejnym cyklu maszynowym. Ogranicza to maksymalną czę stotliwość do 1/24

czę stotliwości cyklu zegarowego. Istnieje możliwość zablokowania liczników sygnał

em

zewnę trznej linii przerwań . Sygnał

przerwania z linii INT0 lub INT1 daje możliwość

wstrzymania pracy odpowiedniego licznika – T0 lub T1.

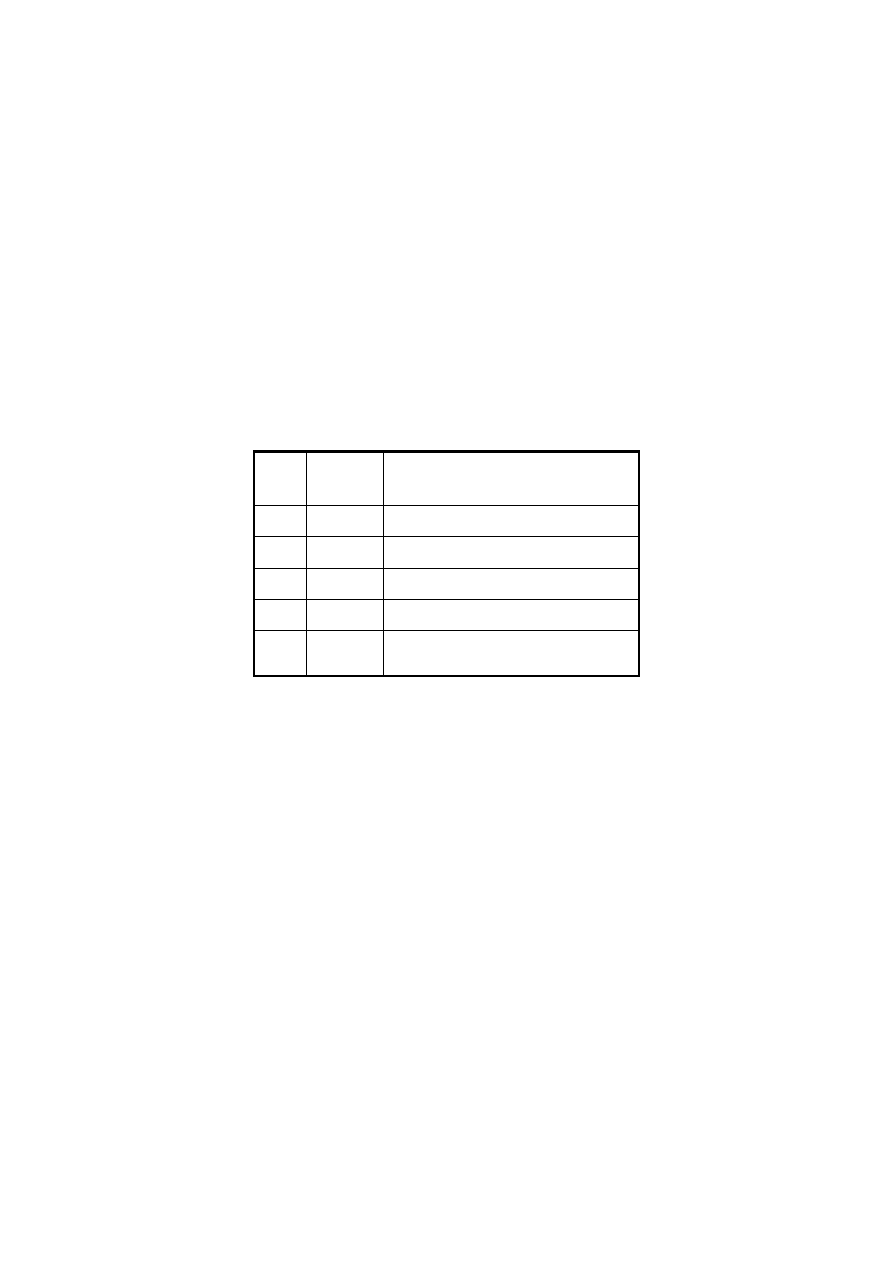

Zawartość liczników przechowywana jest w czterech rejestrach specjalnych. Pod

adresami 138, 139 umieszczono odpowiednio mł

odsze bajty liczników T0 i T1 – oznaczone

jako TL0 i TL1. Natomiast adresy 140 i 141 zawierają ich starsze czę ści – TH0 i TH1.

Ładują c powyższe rejestry można określić począ tkową wartość od której każdy z układów

rozpocznie zliczanie.

Do kontroli pracy i sterowania ukł

adami licznikowo – zegarowymi sł

uży adresowalny

bitowo rejestr specjalny TCON (o adresie 136).

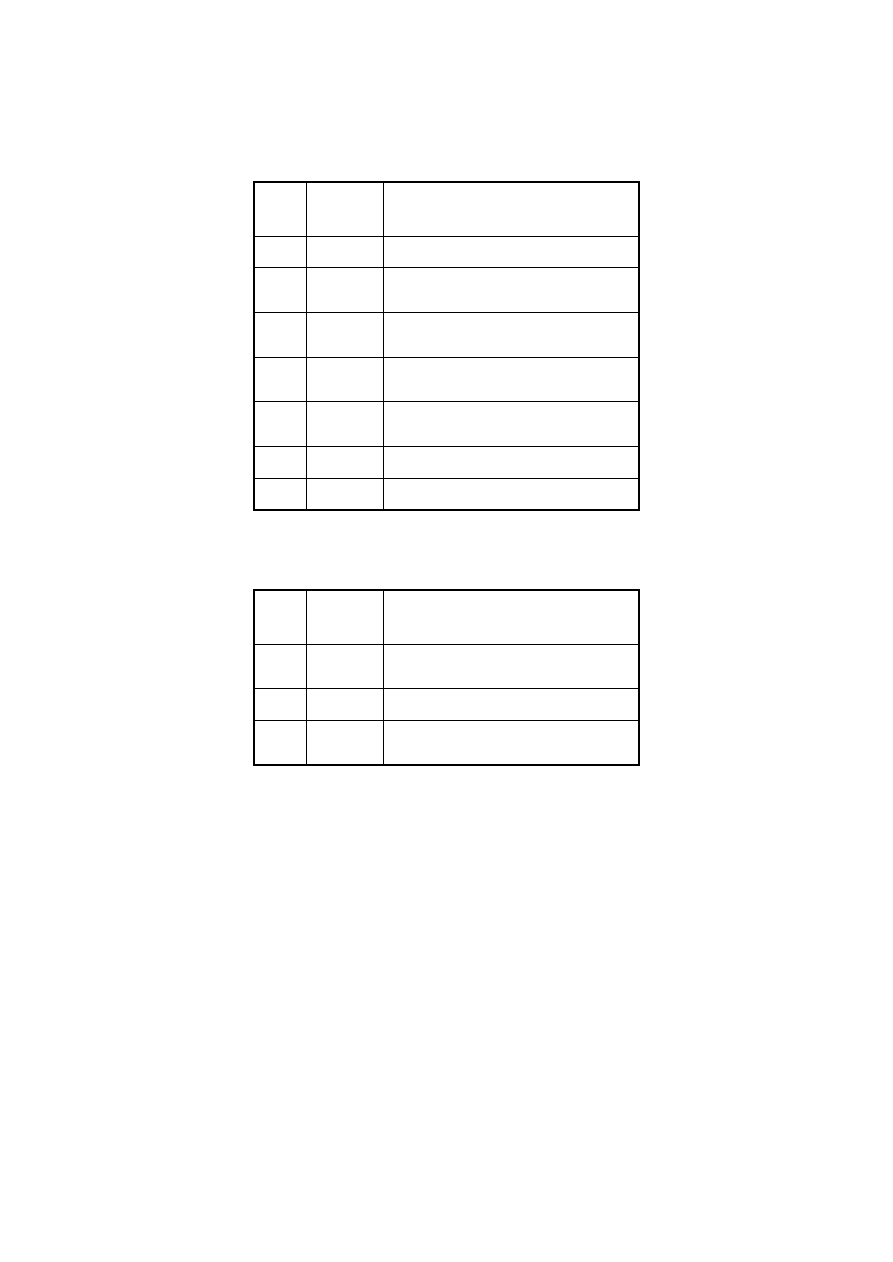

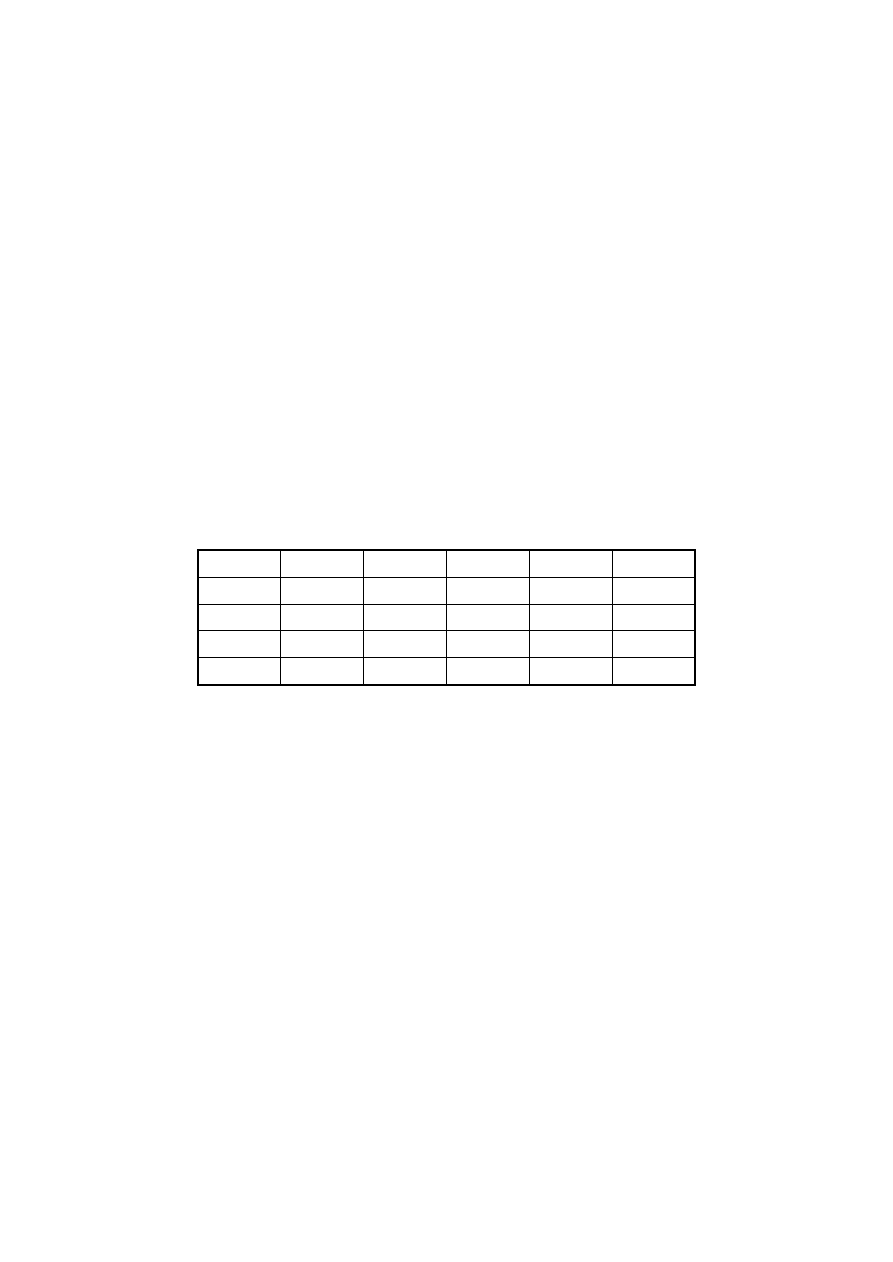

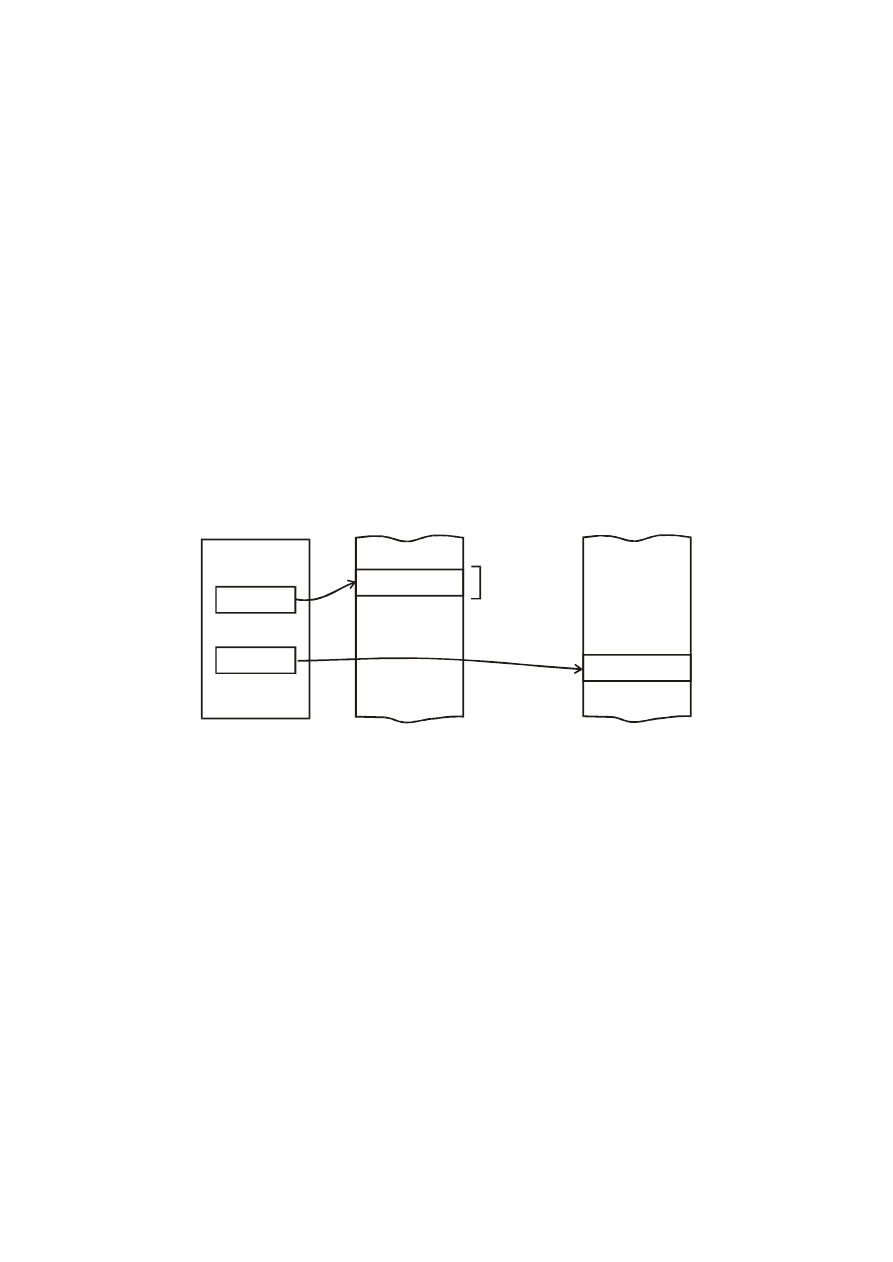

Tabela 6. Oznaczenia kolejnych bitó w rejestru kontrolnego układó w licznikowych (PCON).

numer

bitu

oznaczenie

poziom priorytet ź ródł

o przerwania

7

TF1

flaga przepeł

nienia licznika T1

6

TR1

bit startu/stopu licznika T1

5

TF0

flaga przepeł

nienia licznika T0

4

TR0

bit startu/stopu licznika T0

0-3

-

bity sterują ce zewnę trznymi liniami

przerwań

Każdy z liczników podejmuje prace tylko wówczas, gdy odpowiednia flaga TR0 lub TR1

rejestru zostanie ustawiona. Rejestr TCON zawiera dwie flagi TF0 i TF1, które są sprzę towo

ustawione przez w momencie przepeł

nienia odpowiedniego licznika. Po zał

adowaniu i

uruchomieniu liczników kontrola stanu flag TF0 i TF1 pozwala określić moment w którym

licznik zliczył

zadaną przez nas liczbę impulsów. Licznik zliczają cy cykle maszynowe może

być wykorzystywany do wyznaczania interwał

ów czasowych. Ładują c do licznika inną

wartość począ tkową można odmierzać zadany interwał

wyznaczony czasem, który upł

ywa do

startu do przepeł

nienia licznika.

czas_przepełnienia=czas_cyklu_maszynowego*(pojemność -wartość _początkowa)

Czę stotliwość zegara w systemie DSM-51 został

a tak dobrana, aby można był

o za pomocą

liczników dokł

adnie odmierzać interwał

y 25 milisekundowe. Posł

ugują c się powyższym

wzorem ł

atwo jest sprawdzić, że po zał

adowaniu wartości 90*256 do licznika o pojemności

2

16

jego przepeł

nienie nastę puje po 25ms.

Każdy z ukł

adów licznikowo – zegarowych generuje sygnał

przerwania w chwili jego

przepeł

nienia. W przypadku, gdy ukł

ad pracuje jako zegar tzn. zlicza cykle maszynowe

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

27

mikrokontrolera może być wykorzystany do okresowego wymuszania jakieś akcji. Kod który

ma być wykonywany okresowo umieszczany jest procedurze obsł

ugi przerwania. W

momencie podję cia obsł

ugi przerwania zostanie automatycznie (na drodze sprzę towej)

wyzerowana flaga TF0 (TF1). Po przeł

adowaniu rejestrów TL0 (TL1) i TH0 (TH1) ukł

ad

licznikowo – zegarowy jest gotowy do wygenerowania kolejnego przerwania i powtórnego

wykonanie kodu umieszczonego w procedurze obsł

ugi przerwania. Zostanie ono zgł

oszone po

upł

ywie czasu potrzebnego do nastę pnego przepeł

nienia się licznika. Obsł

uga przerwań

liczników zostanie mówiona szczegół

owo i zilustrowana przykł

adami w dalszej czę ści

skryptu, w rozdziale 4.4 „Przerwania”.

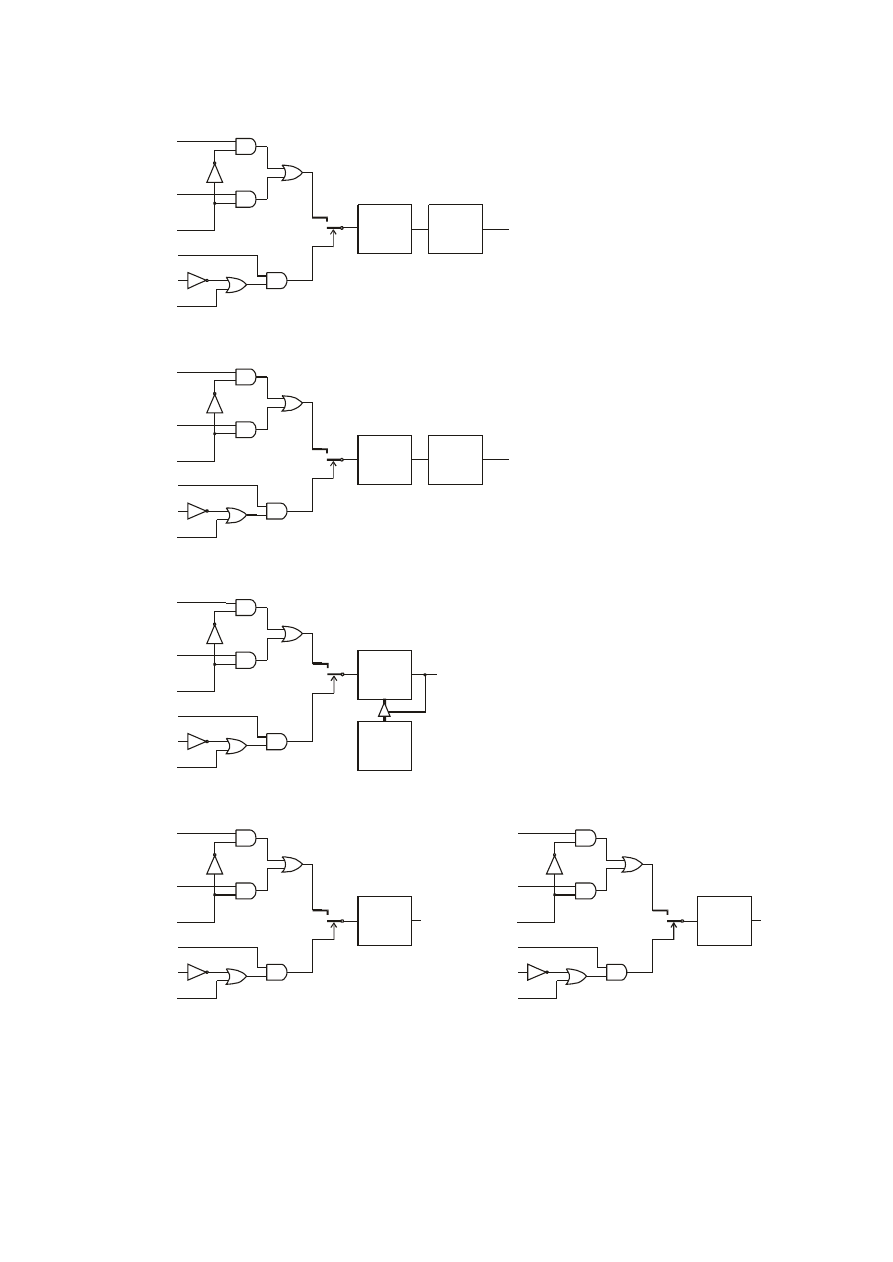

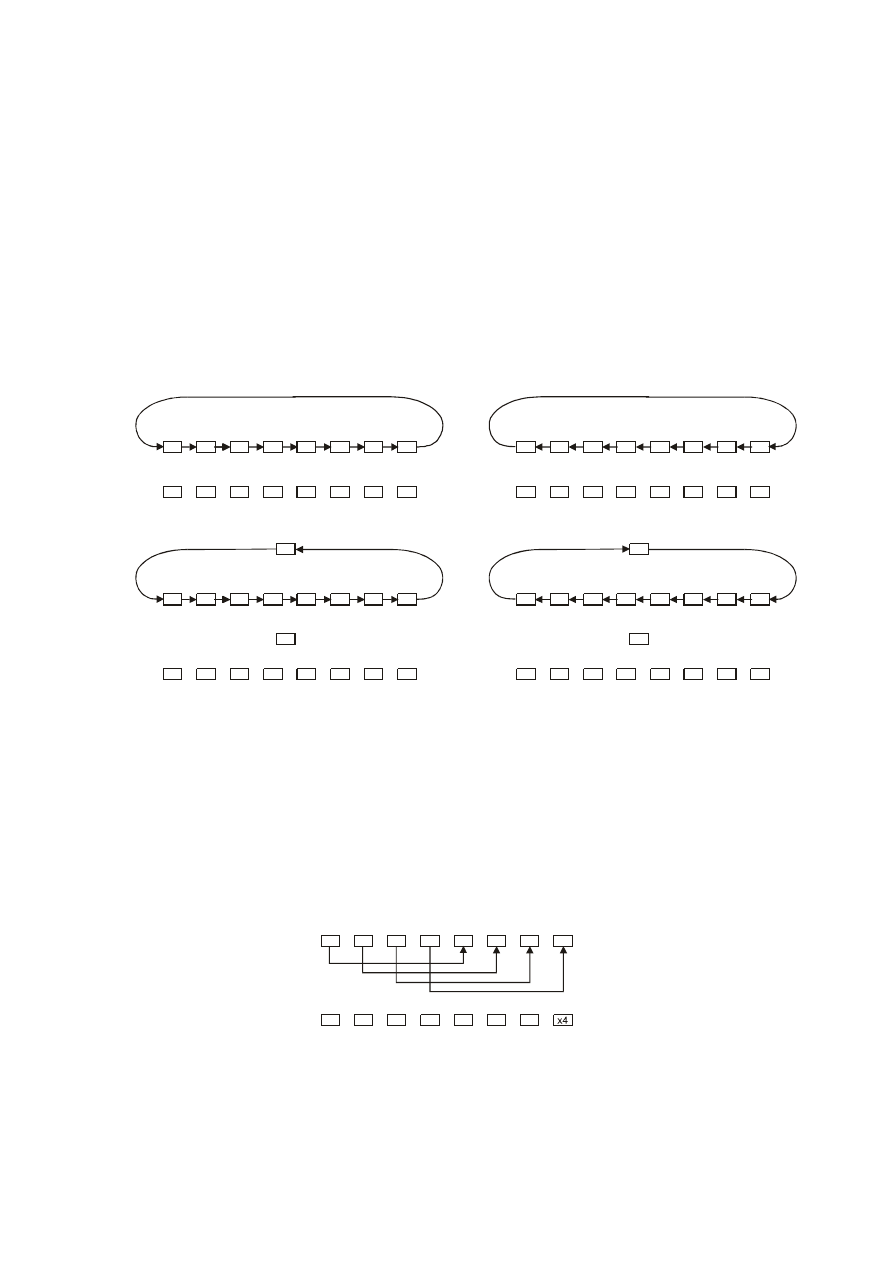

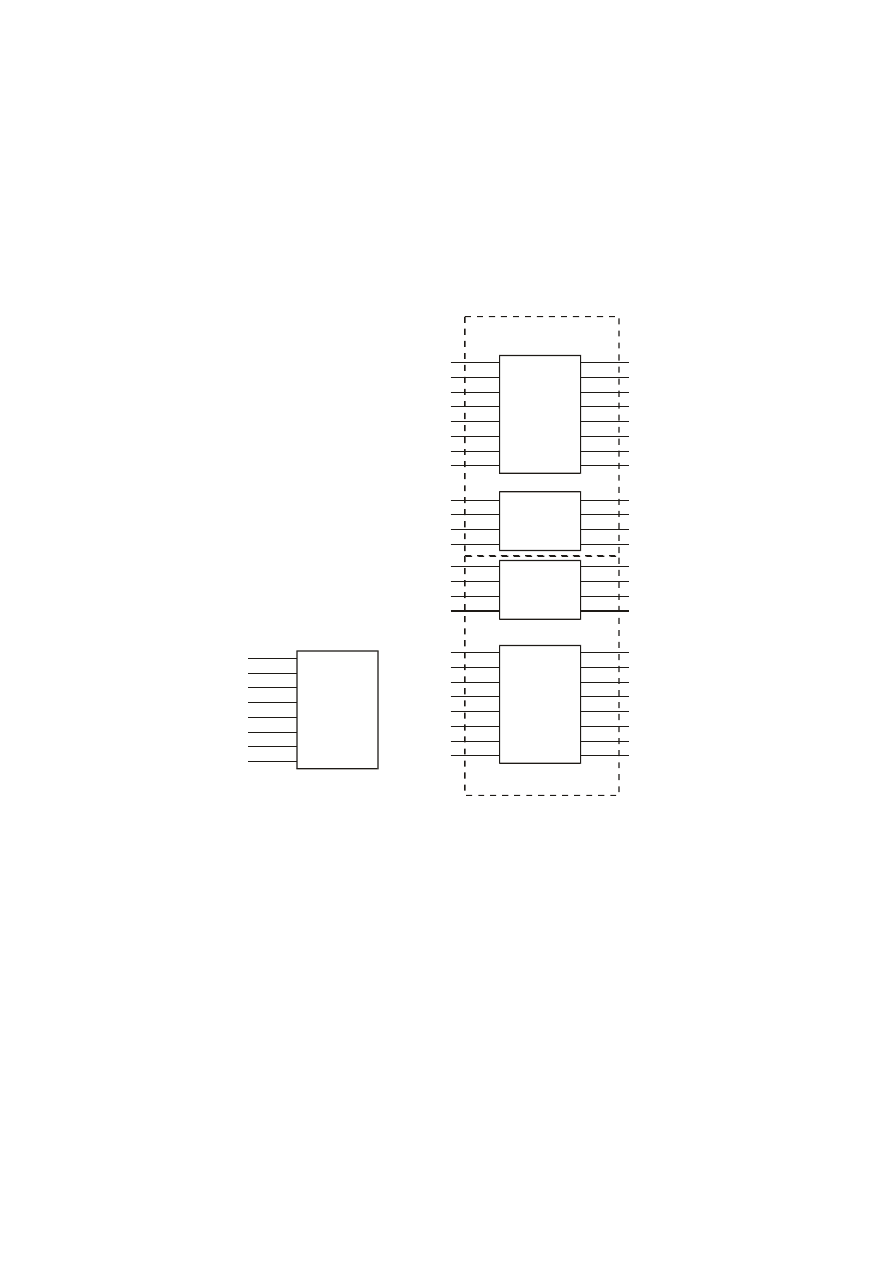

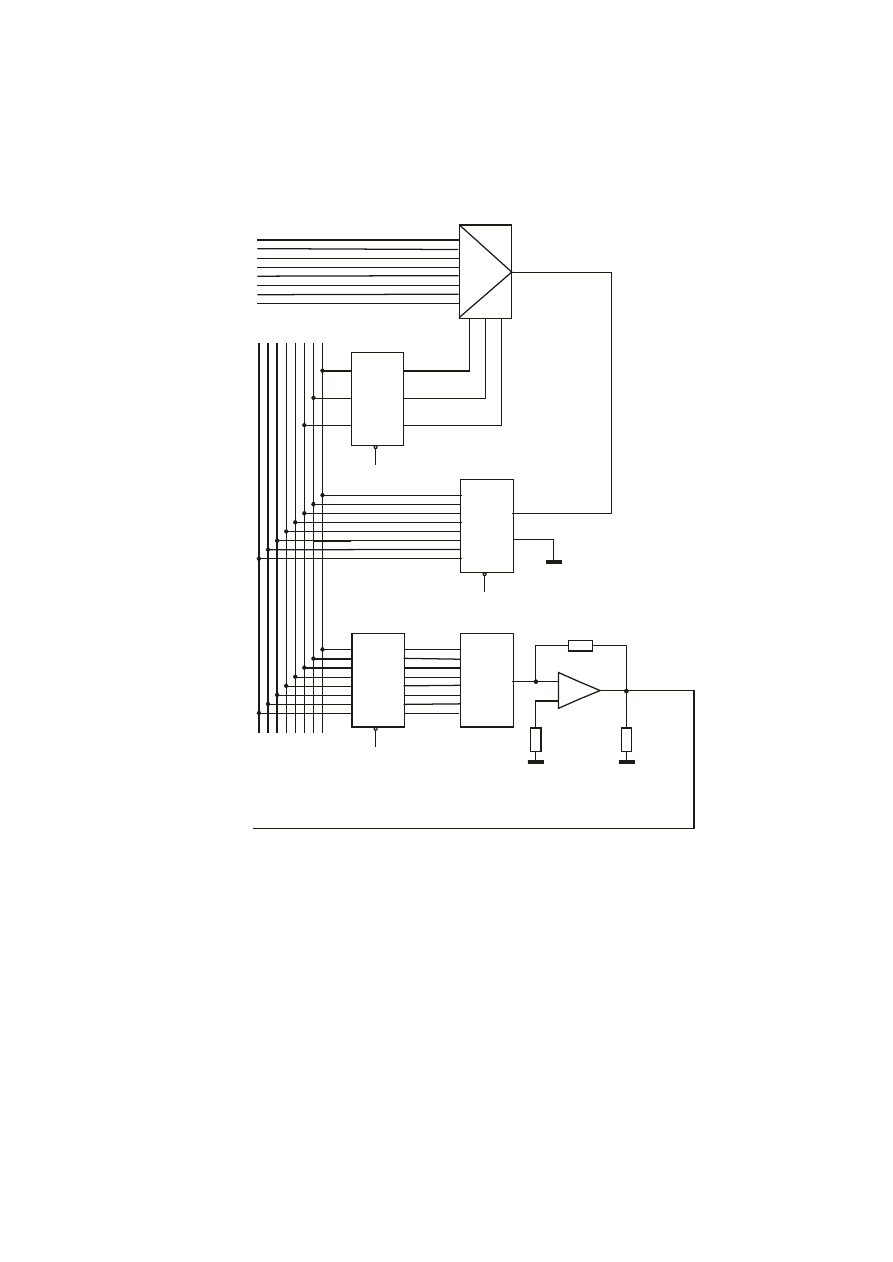

Ukł

ady licznikowe T0, T1 mogą pracować w czterech opisanych niżej trybach. Przy

czym tylko trzy z nich dostę pne są dla licznika T1. Wprowadzenie licznika T1 w zabroniony

tryb 3. skutkuje jego zatrzymaniem.

(1) W trybie 0 ukł

ad pracuje jako licznik 13-bitowy. Starsza czę ść licznika jest

inkrementowana, gdy nastę puje przeniesienie z czwartego bitu mł

odszej czę ści.

Licznik wykorzystuje wię c tylko 5 bitów rejestru TL0 (TL1) i cał

y rejestr TH0

(TH1). Stan trzech najstarszych bitów rejestru TL0 (TL1) jest w tym trybie pracy

nieokreślony. Pojemność licznika wynosi: 2

5

*2

8

=8192.

(2) W trybie 1 licznik wykorzystuje cał

ą dostę pną pojemność rejestrów TL0 (TL1) i

TH0 (TH1). Ukł

ad jest licznikiem 16-bitowym o pojemność równej: 2

8

*2

8

=65536

(3) W trybie 2 pracuje tylko mł

odsza czę ść licznika. Zawartość starszej czę ści licznika

nie ulega zmianie i jest używana do automatycznego przeł

adowania mł

odszej czę ści

licznika po jej przepeł

nieniu. Ukł

ad pracuje jako licznik 8-bitowy z przeł

adowaniem.

Pojemność licznika wynosi zatem: 2

8

=256.

(4) Tryb 3 zarezerwowany jest wył

ą cznie dla licznika T0. W trybie tym licznik pracuje

jako dwa niezależne liczniki 8-bitowe. Licznik pracują cy na rejestrze TL0

wykorzystuje bity sterują ce TR0 i TF0 oraz ma możliwość zliczania impulsów z

koń cówki P3.4 – tak jak cał

y licznik T0 pracują cy w trybach 0-3. Drugi licznik

dział

ają cy na bazie rejestru TH0 korzysta z bitów sterują cych ukł

adu T1 oraz

koń cówki P3.5 jako ź ródł

a impulsów zewnę trznych. Uniemożliwia to kontrole i

sterowanie licznika T1. Ukł

ad licznikowy T1 może być wówczas wykorzystany

jedynie jako generator sygnał

u taktują cego dla portu szeregowego.

Do ustalenia trybu pracy oraz ź ródł

a zliczanych impulsów sł

uży rejestr specjalny TMOD o

adresie 137. Mł

odsza czę ść rejestru odnosi się do licznika T0, starsza wyznacza sposób pracy

licznika T1. Bity 0 i 1 (4 i 5) określają jeden z czterech trybów pracy dla licznika T0 (T1). Za

pomocą bitu 2 (6) wskazuje się ź ródł

o zliczanych impulsów. Ustawienie tego bitu oznacza

taktowanie licznika kolejnymi cyklami maszynowymi, wyzerowanie – wymusza zliczanie

impulsów zewnę trznych. Ustawienie bitu 3 (7) umożliwia blokowanie licznika T0 (T1) przez

sygnał

na linii przerwań INT0 (INT1).

Architektura komputerów i programowanie niskopoziomowe– laboratorium.

28

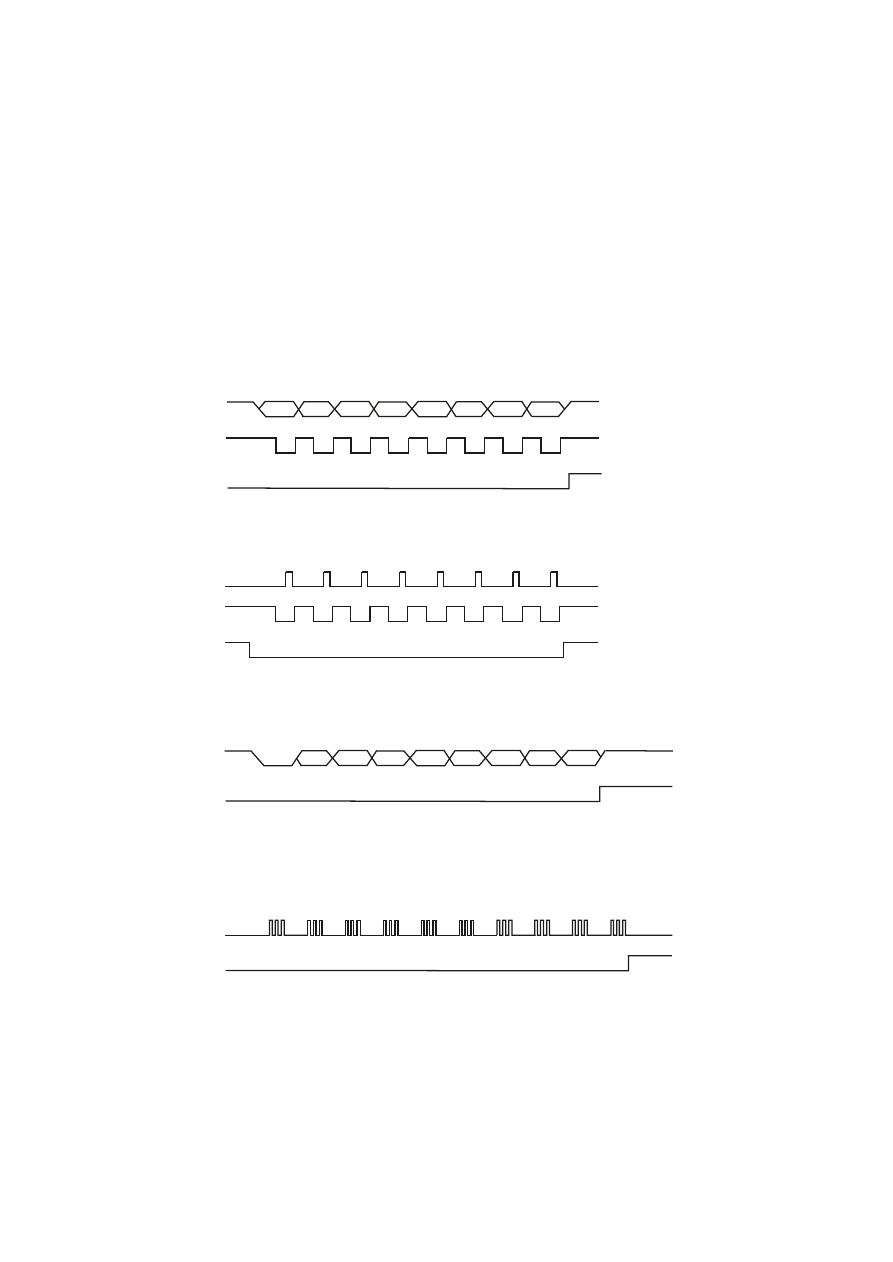

TL x

TH x

TF x

f

masz.

TR x

GATE x

C/T x

(impulsy zew.)

(5 bit

ów)

T x

/INT x

(8 bit

ów)

a)

1

0

TF x

TL x

TH x

f

masz.

TR x

GATE x

C/T x

(impulsy zew.)

(8 bit

ów)

T x

/INT x

(8 bit

ów)

b)

1

0

TF x

TL x

f

masz.

TR x

GATE x

C/T x

(impulsy zew.)

(8 bit

ów)

prze

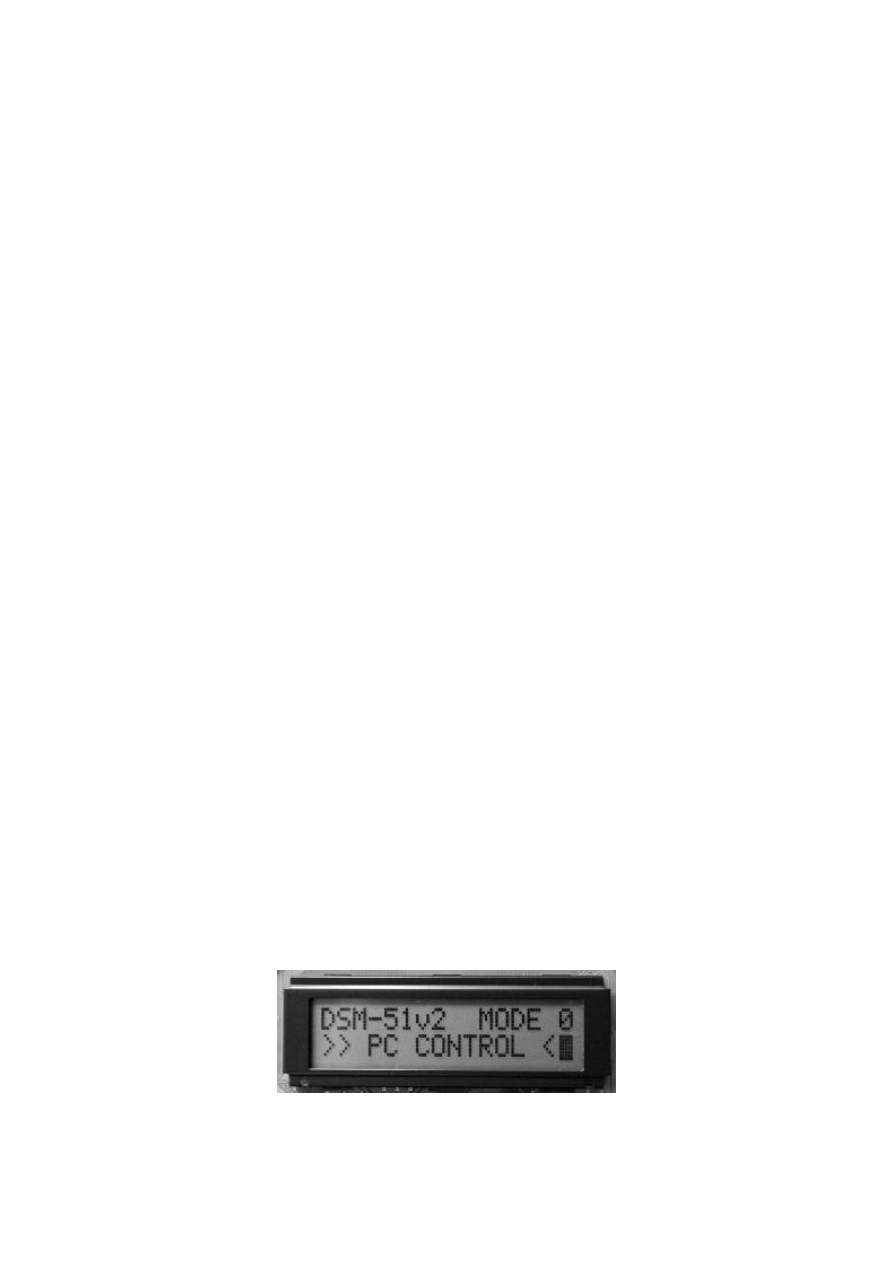

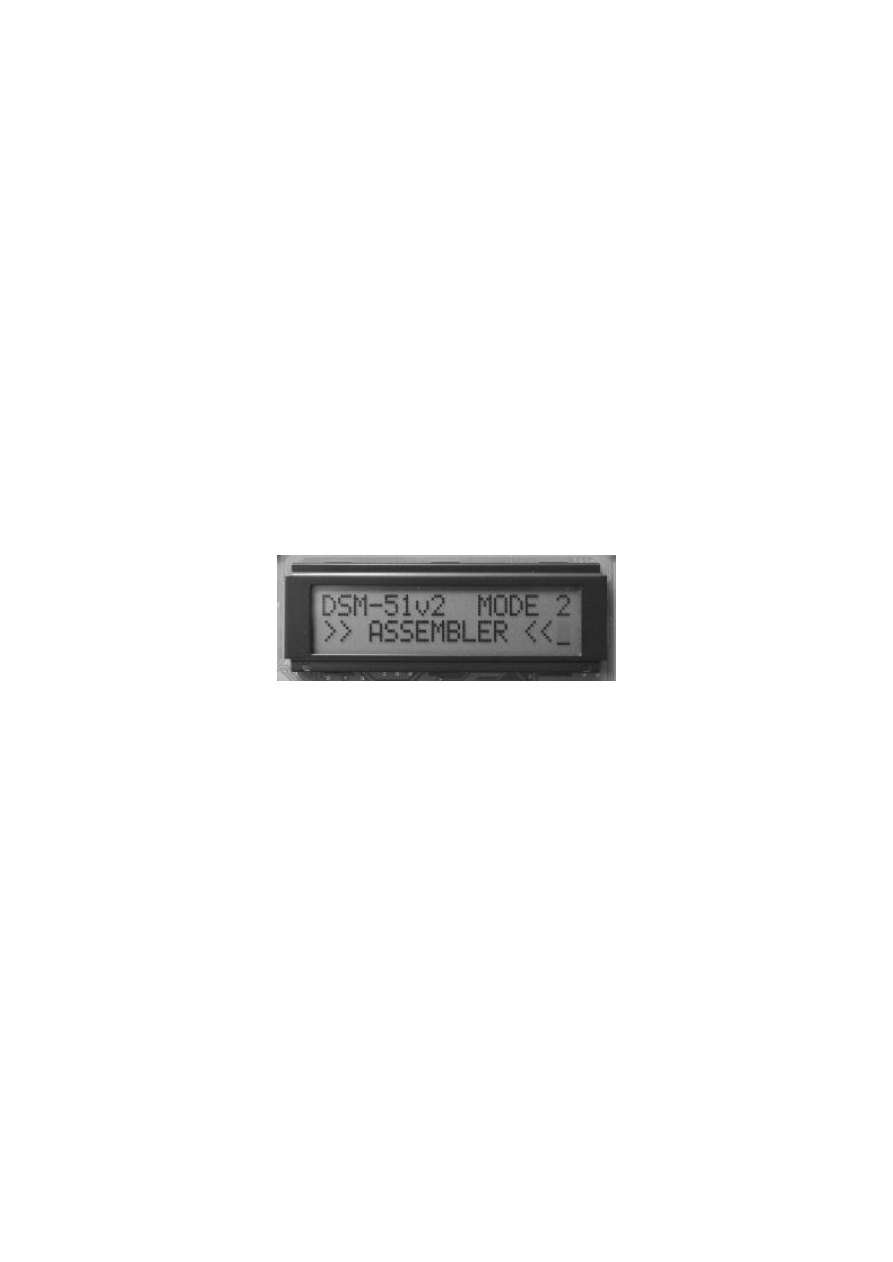

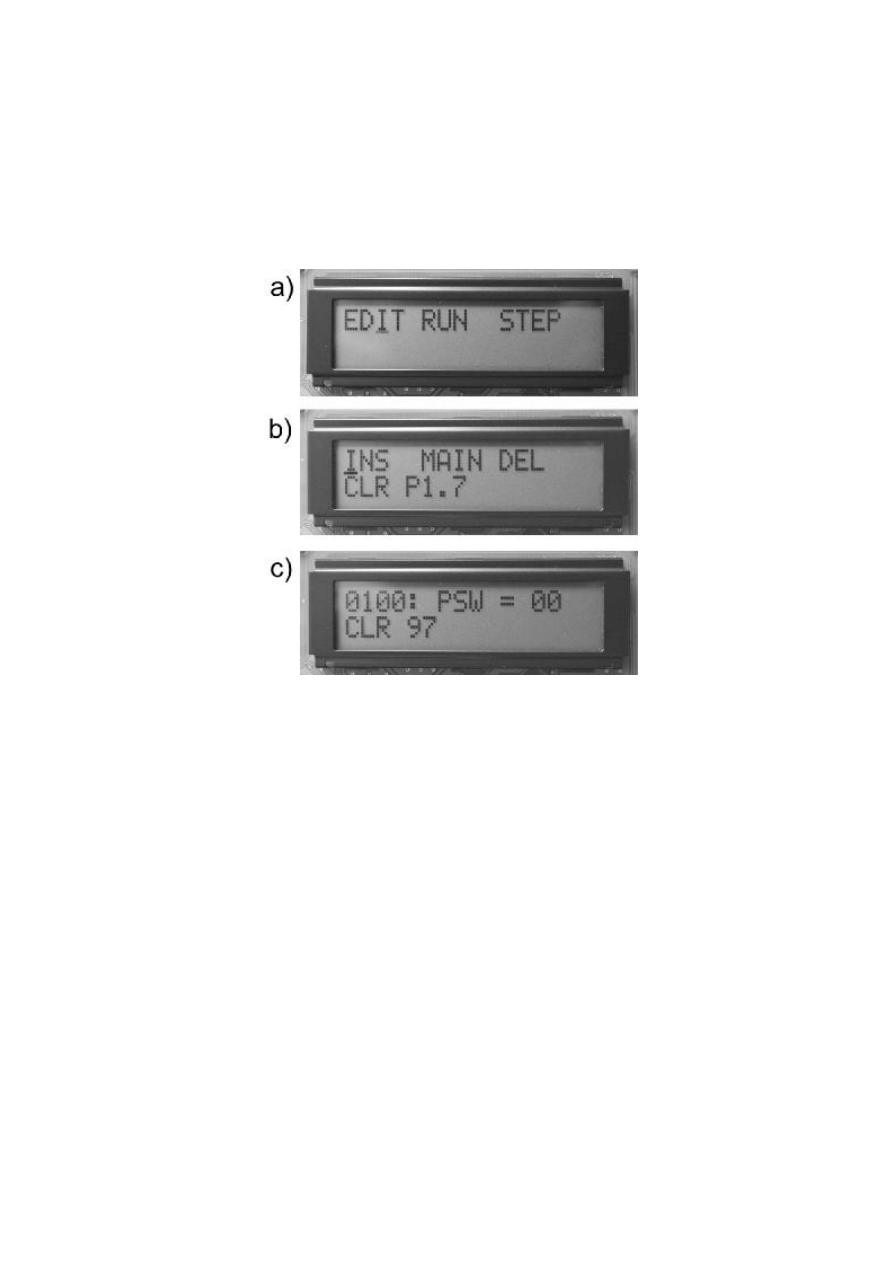

ładowanie