INTERFEJS I2C

1.Wstęp

Interfejs Inter IC BUS (I2C BUS) opracowany został przez firmę Philips w celu

synchronicznej komunikacji szeregowej pomiędzy urządzeniami tworzącymi

pewien zestaw modułami w ramach urządzenia jak również układami

scalonymi na płytce drukowanej. Firma opracowała układy kontrolerów

interfejsu szeregowego (SIO) w które wyposaża układy scalone umożliwiając

w ten sposób wykorzystanie interfejsu w układach mikroprocesorowych

sterownikach jednoukładowych sterownikach wyświetlaczy do sterowania

pamięci i układów I/O w cyfrowej syntezie częstotliwości i przetwarzaniu

sygnałów w telekomunikacji sprzęcie elektroakustycznym i video.

Magistrala tegoż interfejsu składa się z dwóch dwukierunkowych linii:

· pierwszej dla sygnału danych (ang. Serial Data - SDA)

· drugiej dla sygnału zegarowego (ang. Serial Clock - SCL).

Magistrala umożliwia przesyłanie danych pomiędzy dwoma dowolnymi

urządzeniami zgodnie ze zdefiniowanym protokołem :

· inicjalizacja transmisji danych może nastąpić tylko gdy magistrala nie jest

zajęta

· podczas transmisji danych sygnał na linii SDA musi być stabilny gdy stan

linii SCL jest wysoki zmiany na SDA podczas wysokiego stanu na SCL są

interpretowane jako sygnały sterujące (start transmisji danych stop transmisji

danych dane ważne).

Każda transmisja inicjowana jest poprzez wystąpienie warunku start i

kończona poprzez wystąpienie warunku stop. Ilość bitów transmitowanych

pomiędzy warunkami nie jest limitowana. Każde z urządzeń rozpoznawane

jest przez unikalny adres przesyłany na początku transmisji. Osiem bitów

reprezentuje adres urządzenia slave natomiast najmniej znaczący bit (LSB)

określa kierunek transmisji. Wszystkie urządzenia po wykryciu warunku 'start'

porównują odebrany adres ze swoim adresem sprzętowym i jeżeli jest on

zgodny adresują się jako odbiornik lub nadajnik. Występują również adresy

własne programowalne oraz adresy rozgłoszeniowe (ang. general call)

przeznaczone dla wszystkich urządzeń w systemie poprzedzające bajty

określające polecenie. Urządzenia mają oprócz funkcji nadajników i

odbiorników przypisane statusy typu master i slave. MASTER to urządzenie

które inicjuje i prowadzi transmisję danych generując sygnały zegarowe.

SLAVE to dowolne poprawnie zaadresowane urządzenie.

Możliwe są trzy formaty transmisji :

· master - nadawca slave - odbiorca

· master - odbiorca slave - nadawca

· ze zmianą kierunku transmisji.

W trzecim formacie przed każdą zmianą kierunku transmisji musi być

generowany sygnał start adres urządzenia slave oraz nowa wartość bitu

kierunku. Interfejs dopuszcza możliwość przyłączenia do magistrali kilku

urządzeń o statusie master. Aby uniknąć kolizji (obecność kilku urządzeń

sterujących sygnałami na magistrali) w systemie I2C problem ten rozwiązano

stosując arbitraż. Arbitraż oparto na zasadzie kontroli zgodności stanu linii

SDA z wartością logiczną bitu wyprowadzonego przez dane urządzenie.

Odczyty stanu linii SDA odbywają się w ściśle określonych momentach

wyznaczonych sygnałem zegarowym. Jeżeli dwa lub więcej urządzeń stara

się wysłać jednocześnie dane na magistralę to wykorzystując metodę

iloczynu na drucie" pierwsze które wyśle jedynkę utraci kontrolę nad łączem.

Przedstawione rozwiązanie preferuje urządzenie które w trakcie arbitrażu

wysyła najniższą wartość binarną.

Sygnał zegarowy na magistrali generowany jest zawsze przez urządzenie

master nawet gdy urządzenie to odbiera dane. Jedynym przypadkiem gdy

inne urządzenia ingerują w przebieg sygnału zegarowego jest proces

arbitrażu oraz przypadek gdy wolne urządzenie odbiorcze chce obniżyć

szybkość transmisji wymuszając niski poziom na linii SCL.

Obie linie SDA i SCL są liniami dwukierunkowymi połączonymi przez

rezystory podciągające (ang. Pull-up Resistor) do napięcia zasilania 5[V]+-

10[%]. Kiedy szyna jest wolna obie linie są w stanie wysokim. By móc

realizować funkcję wired-AND" stopnie wyjściowe urządzeń dołączonych do

magistrali muszą posiadać wyjścia typu otwarty kolektor lub otwarty dren.

Standardowa szybkość transmisji wynosi 100[kbitów/s] adresując do128

urządzeń. Możliwa jest również praca w trybie szybkim z szybkością

400[kbitów/s] i zaadresowanie 1024 urządzeń. Liczba układów dołączonych

do magistrali zależy jedynie od dopuszczalnej pojemności magistrali -

400[pikoF]. Dopuszcza się przyłączenie do magistrali układów wykonanych w

różnych technologiach (NMOS CMOS bipolarna). Każdy układ posiadający

określone na stałe poziomy napięć wejściowych (maksymalnie 1 5 dla L 3 dla

H) może mieć swoje odrębne źródło zasilania.

W produkcji znajduje się szereg sterowników interfejsu I2CBUS. Przykładem

może być kontroler interfejsu szeregowego (SIO) w mikrokomputerach

rodziny PCF84CXX. Układ SIO pozwala na współpracę wielu urządzeń

realizowaną poprzez wspólną magistralę złożoną z dwóch linii przy czym

komunikacja dwóch dowolnych urządzeń odbywa się bez zakłócania

pozostałych. Komunikacja pomiędzy procesorem mikrokomputera a

sterownikiem interfejsu odbywa się poprzez wewnętrzną magistralę

mikrokomputera oraz przerwanie SIR które pojawia się po skompletowaniu

bajtu. Przesłanie bajtu do/z SIO wykonuje tylko jedna instrukcja. Do

przechowywania danych oraz informacji sterujących działaniem interfejsu

wykorzystuje się cztery rejestry:

· rejestr przesuwający dane

· rejestr statusu

· rejestr sterujący sygnałem CLK

· rejestr adresowy.

Pod względem praktycznym można powiedzieć że magistrala I2C jest

integralną częścią przyrządów sterowanych przez komputer , procesor czy

sterownik i daje możliwość wyświetlenia pełniejszej informacji niż tylko cyfr .

Już od pewnego czasu można zaobserwować ewolucję w kierunku coraz

liczniejszej aparatury, profesjonalnej i nie tylko. To było powodem pojawienia

się na rynku wyświetlaczy alfanumerycznych lecz nie wyposażonych w

interfejs I2C. W niniejszy interfejs można wyposażyć zwykły alfanumeryczny

wyświetlacz LCD.

2.

Wyświetlacz alfanumeryczny

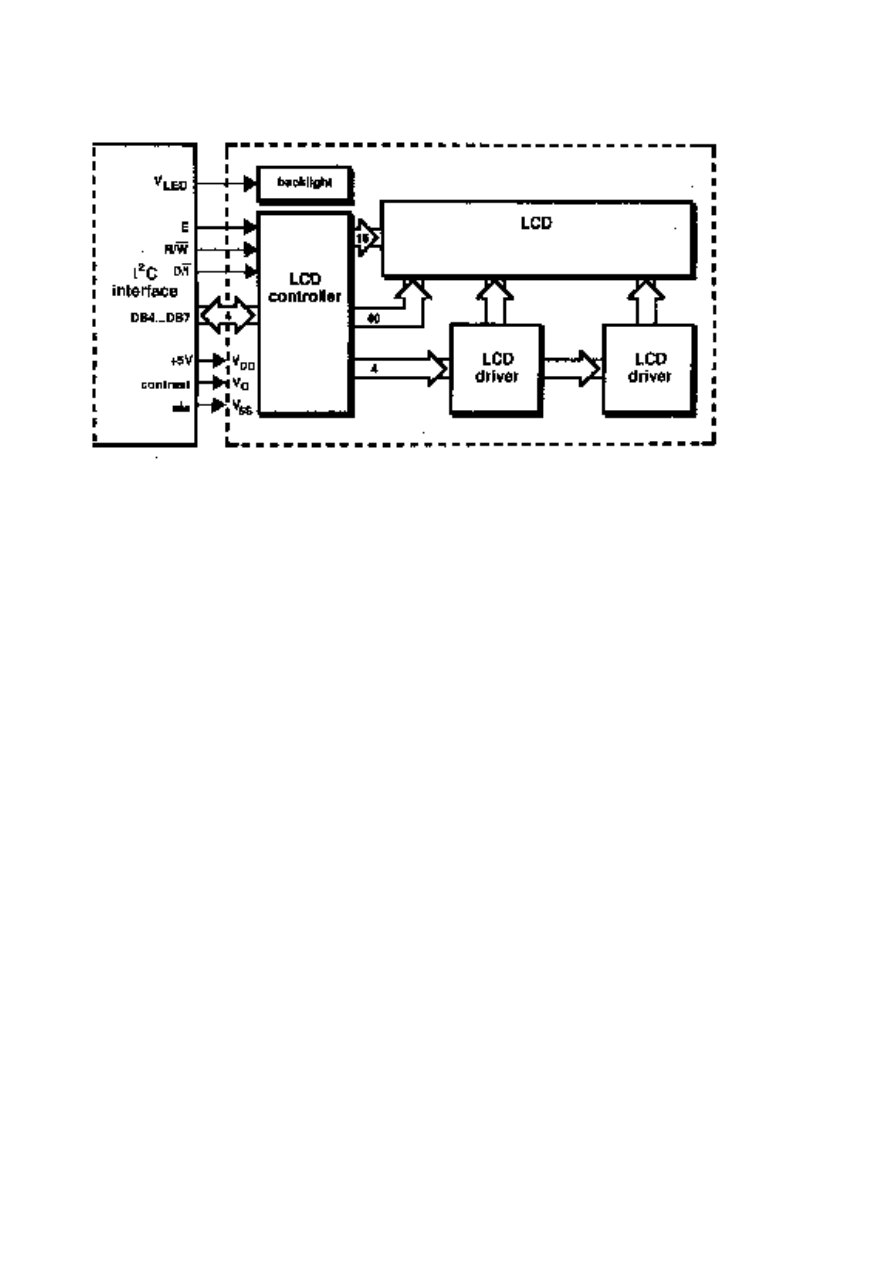

Na rys.1 przedstawiony jest schemat blokowy, to co nazywamy

wyświetlaczem LCD , w rzeczywistości zawiera, oprócz samego

wyświetlacza, również zespolone z nim obwody mikrokontrolera. Właściwiej

byłoby zatem mówić o module LCD. Można zastosować wyświetlacz Hitachi

o dwóch wierszach po 40 znaków. Każdy znak mieści się w matrycy o

szerokości 5 i wysokości 8 punktów, z których tylko 7 jest wykorzystywanych

przez większość znaków zawartych w znakowej pamięci ROM. Punkty 8-go

dolnego rzędu, zostały zarezerwowane dla kursora, mogą jednak zostać

wykorzystane w znakach specjalnych jak też w znakach zdefiniowanych

przez odważnego użytkownika. Do sterowania modułem służy specjalny

układ sterujący układ scalony – kontroler LCD. Sterownik ten wypełnia

podwójną funkcję sterowania wyświetlaczem i komunikacji z komputerem, w

tym przypadku przez interfejs I2C . Wymiana danych pomiędzy interfejsem i

sterownikiem odbywa się za pośrednictwem tylko 4 bitów, DB4 do DB7.

Wprawdzie sam sterownik może posługiwać się słowami jednobajtowymi( 8

bitów), ale w tym przypadku spowodowało by to niepotrzebną komplikację

interfejsu I2C.

Rys. 1 schemat blokowy ilustrujący koncepcje interfejsu I2C do sterowania

modułem LCD

Poza 4 bitami danych są jeszcze 4 linie poleceń. Znaczenie linii E (enable –

umożliwienie ) i R/W ( read/write – odczyt/zapis) wydaje się oczywiste.

Sygnał D/I (data/instruction – dane/instrukcje) mówi o tym , czy dane obecne

na liniach danych są poleceniem przeznaczonym dla sterownika LCD czy

danymi do wyświetlacza. Czwarta z tych linii, VLED , pozwala wyłączać

podświetlanie (backlight) wyświetlacza, czyli LEDy, które, umieszczone za

ekranem modułu, pobierają 170 mA (maksimum 250 mA) z zasilacza 5V.

Proste porównanie z prądem pobieranym przez właściwy wyświetlacz ( 1mA

– max 3mA), wskazuje , że podświetlanie jest energetyczne dość rozrzutne.

3.

Interfejs I2C

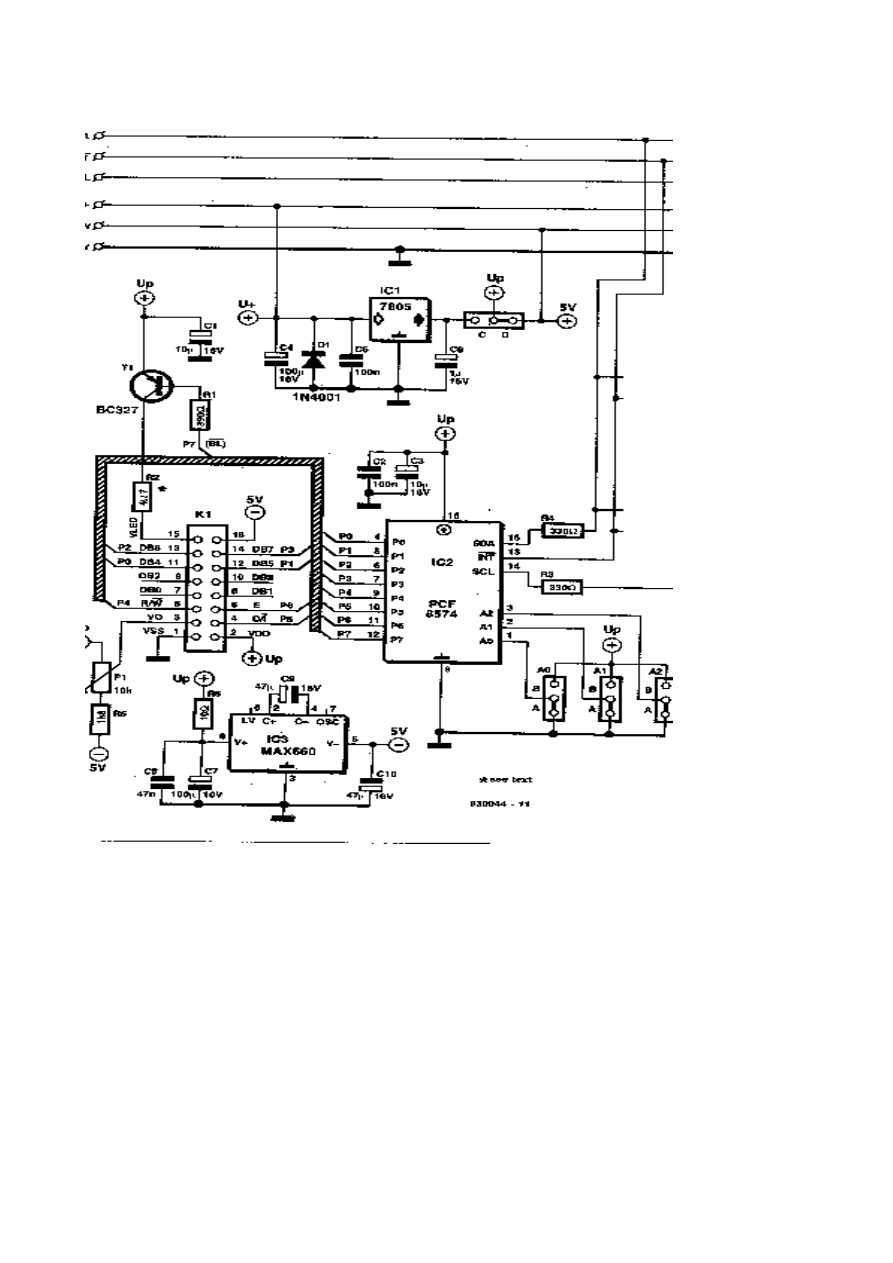

Rysunek 2 przedstawia schemat elektryczny układu sterującego

wyświetlaczem, na którym można zauważyć linie magistrali i 8 bitowy układ

wejść/wyjść (E/S) (IC2 – PCF8574). Układ ten jest właściwym interfejsem

magistrali I2C i równocześnie sterownikiem wyświetlacza. Ponieważ pełne 8

bitów PCF8574 nie jest potrzebne dla danych, pozostałe 4 bity zostały

przeznaczone dla poleceń. Zworki A0 do A2 pozwalają zdefiniować adres

zajmujący przez IC2 w magistrali I2C .

Ma to następującą strukturę: 0100 A2 A1 A0 R/W

Można także

uznać, że obok IC2, również tranzystor T1 jest częścią interfejsu pomiędzy

magistralą I2C a wyświetlaczem LCD. Tranzystor ten, za pośrednictwem

programu, steruje podświetlaniem ekranu. Rezystor R2 ogranicza prąd LED

podświetlania wyświetlacza LM092LN. Za pośrednictwem zwornika C/D

można wybrać sposób zasilania układu albo z linii +5V, albo z linii +U,

poprzez stabilizator IC1 /należy wsiąść pod uwagę , że pobór prądu przez

układ może osiągnąć około 250mA. Układ IC3 typu MAX660 służy do

wytworzenia napięcia –5V, potrzebnego do regulacji kontrastu wyświetlacza.

Napięcie to jest niezbędne, ponieważ kontrast daje się regulować napięciem

dodatnim. W praktyce okazuje się że przy bardzo ostrych kątach obserwacji

kontrast daje się ustawić dysponując napięciem ujemnym. Optymalne

napięcie doprowadzone do wyprowadzenia V0 może mieć wartość

dochodzącą do 6,5V poniżej napięcia zasilania, co odpowiada –1,5V w

stosunku do masy . Rezystor R5 ogranicza dolne napięcie regulacji kontrastu

P1 do tej wartości.

4.Program

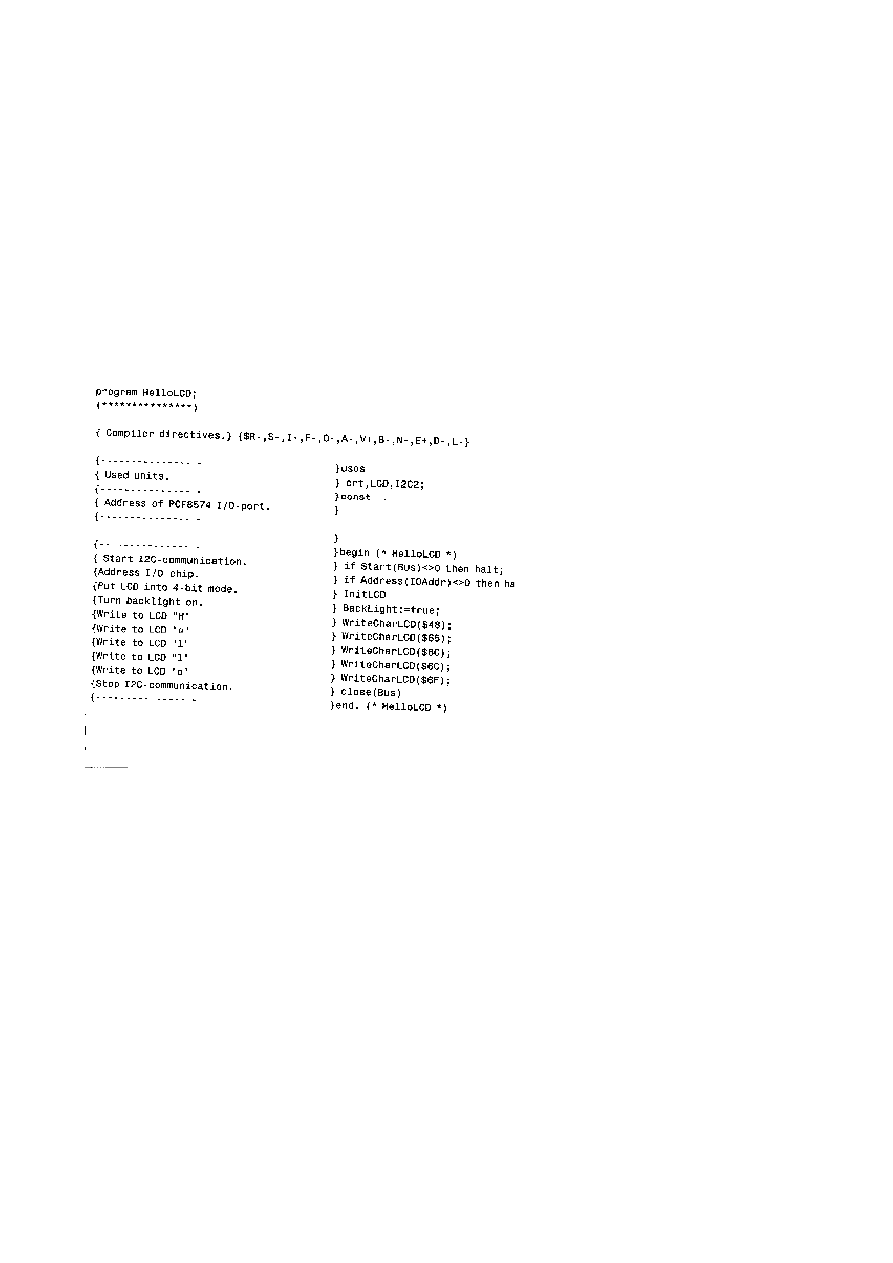

Dla posiadaczy komputera PC, znających np. Turbo-Pascal, oprogramowanie

tego układu jest bardzo proste. Wystarczy użyć specjalnej w tym celu

napisanej procedury LCD (LCD unit), nie wgłębiając się w techniczne aspekty

wyświetlacza.

Aby pokazać, w jaki sposób procedura LCD może być użyta w programie na

rysunku powyżej zamieszczony został listing prostego programu, który

powoduje napisanie na wyświetlaczu słowo “Hello”.

Podstawowym zadaniem

programu jest formułowanie poprawnych (z punktu widzenia kolejności,

poziomów) poleceń i danych do wyświetlania. Interfejs I2C nie robi nic poza

przetwarzaniem strumienia danych szeregowych z magistrali na zrozumiałe

dla wyświetlacza dane równoległe. Program odpowiada za porządek

przekazywanych danych i za kolejność. Na rysunku 4 pokazane są

zależności czasowe związane z procesem odczytu i zapisu danych.

Przekazywanie instrukcji i danych odbywa się zawsze półbajtami (nibble),

poczynając od starszego półbajtu. Na wykresie widać, że zaczyna się od

przesłania instrukcji do wyświetlacza, operacji rozpoczynanej przejściem linii

E (enable) z poziomu wysokiego na niski. W środku przebiegu widać, jak

program może odczytać wskaźnik zajętości BF (bus flag), do której to

informacji dodaje się stan licznika adresu sterownika wyświetlacza. Program

koniecznie musi sprawdzać ten bit przed każdą operacją odczytu lub zapisu.

Przez czas od 40 m s do 16ms, zależnie od przeznaczenia danych, sterownik

jest głuchy na nadchodzące sygnały. Może tylko nastąpić odczyt bajtu ze

wskaźnikiem zajętości. Trzecia część wykresu ilustruje proces odczytu

danych, operacje mogą się odbywać tylko wówczas, gdy linia E jest w stanie

wysokim.

Tabela 2 zawiera wszystkie potrzebne informacje (wraz z binarnymi)

dotyczące liter, cyfr oraz innych znaków( w tym alfabetu japońskiego), które

można otrzymać na wyświetlaczu. Trzeba podkreślić, że najważniejsze litery i

cyfry mają kody odpowiadające kodom ASCII, co znacznie upraszcza pisanie

tekstów na ekranie. W pierwszej kolumnie tabeli, dla czterech starszych bitów

oznaczonych 0000, widać 8 cyfr w nawiasach. Oznaczają one 8 znaków (jest

ich tylko 8) definiowanych przez użytkownika. W tym celu zarezerwowano

trochę miejsca w RAM sterownika LCD, zwanej CGRAM (Character

Generator RAM). Jeżeli ten obszar Ramu nie jest używany do

przechowywania własnych znaków, to może on zostać użyty do

przechowywania danych. Potrzebne informacje do, odpowiadające

poszczególnym pozycjom wyświetlacza, dotyczące umiejscowienia w pamięci

RAM wyświetlanych danych (DDRAM, Display Data RAM), są zebrane w

tabeli 3.

Wyszukiwarka

Podobne podstrony:

programator pamięci I2C

Mikrokontrolery STM32 Użycie interfejsu I2C, USART, SPI

AVT 5321 Szukacz i tester układów na magistrali I2C

i2c

AKiSO SS wykład 8 I2C SPI 1W CAN

Zegar czasu rzeczywistego sterowany szyną I2C

Miagistrala i2c

6 magistrala I2C

i2c to keyboard interface

I2C Multiplexer

I2C bus specificaion 2000 id 20 Nieznany

I2C Bus Implementierung

I2C

Magistrala I2C 10 id 276712 Nieznany

I2C Interface fuer Druckerschnittstelle

I2C BUS SPECIFICATION 2

i2c slave mode

Copieur I2C 24C01 24C16

więcej podobnych podstron