Wstęp

Sygnały elektryczne, takie jak napięcie, istnieją w systemach cyfrowych w jednej z dwóch rozróżnialnych wartości: poziom niski L (ang. Low) oraz poziom wysoki H (ang. High). Przypisanie wartości dwójkowych 0 i 1 tym poziomom jest dowolne. W praktyce zamiast poziomów określa się dwa pola tolerancji, wewnątrz których powinien znajdować się poziom sygnału reprezentującego logiczne 0 i 1 (rys. 1).

Rys. 1. Pola tolerancji napięcia w logice pozytywnej (poziom niższy reprezentuje 0, zaś poziom wyższy 1).

Bramki logiczne

Bramkami logicznymi nazywamy układy elektroniczne realizujące funkcje logiczne jednej lub wielu zmiennych. Sygnały wejściowe i wyjściowe bramek przyjmują wartość 0 lub 1.

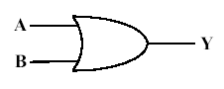

Podstawowe bramki logiczne to: AND, OR, NOT (inwerter), NAND, NOR, XOR. Wszystkie bramki logiczne, z wyjątkiem NOT mogą mieć większą liczbę wejść. Bramki logiczne należą do grupy cyfrowych układów kombinacyjnych, tzn. układów w których stan wyjść jednoznacznie zależy od aktualnego stanu wejść. Bramka scharakteryzowana jest poprzez nazwę, symbol graficzny, funkcje logiczne oraz tablicę prawdy (tabela 1).

Bramka OR czyli funkcja logiczna „lub” - jest to układ sumy logicznej, który daje na wyjściu sygnał jeden, jeżeli tę wartość ma conajmniej jeden z sygnałów. Oznacza to, że zero pojawia się wtedy i tylko wtedy, kiedy oba sygnały są wartości zero.

Bramka AND czyli funkcja logiczna „i”, jest to układ logiczny, który spełnia następujące funkcje: na wyjściu pojawia się sygnał 1 wtedy i tylko wtedy, kiedy oba sygnały wejściowe posiadają wartość logiczną jeden.

Nazwa bramki |

Symbol graficzny |

Funkcja logiczna |

Tablica prawdy |

NOT |

|

|

|

AND |

|

|

|

OR |

|

|

|

NAND |

|

|

|

NOR |

|

|

|

XOR |

|

|

|

Tabela. 1. Bramki logiczne.

Bramka NOT (inwerter ) realizuje funkcje logiczną „nie”. Jest to układ zmieniający wartość logiczną sygnału na przeciwną tzn. daje na wyjściu sygnał jeden, gdy na wejściu pojawia się zero i odwrotnie.

Złożone funkcje logiczne realizują bramki NOR, NAND oraz XOR.

Bramka NOR (funkcja logiczna „nie-lub”, układ sumy zanegowanej) jest to układ na którego wyjściu pojawia się sygnał jeden wtedy i tylko wtedy, gdy na wszystkich wejściach istnieje sygnał zero.

Bramka NAND (funkcja logiczna „nie-i”) jest to układ logiczny iloczynu zanegowanego, dający na wyjściu wartość zero wtedy i tylko wtedy, gdy na wejściu wszystkie sygnały mają wartość jeden.

Bramki logiczne są realizowane w układach scalonych. Układ scalony jest półprzewodnikowym kryształem krzemu, inaczej zwanym modułem (ang. chip), zawierającym elektroniczne części, takie jak: tranzystory, diody, rezystory i kondensatory. Elementy te są połączone wewnątrz modułu, realizując żądany układ elektroniczny. Moduł jest zamontowany w ceramicznej lub plastykowej obudowie z przymocowanymi zewnętrznymi końcówkami. Złożoność układów scalonych określa tzw. skala integracji. Przyjęto, że układem scalonym o małej skali integracji SSI (ang. Small Scale Integration) jest układ zawierający do 10 bramek. Układ scalony o średniej skali integracji MSI (ang. Medium Scale Intergration) zawiera od 10 do 100 bramek. Układ scalony o dużej skali integracji LSI (ang. Large Scale Integration) zawiera od 100 do kilku tysięcy bramek. Układy scalone zawierające więcej niż kilka tysięcy bramek są układami o bardzo dużej skali integracji VLSI (ang. Very Large Scale Integration). Superduży stopień scalenia, wielki stopień scalenia, olbrzymi stopień scalenia, SLSI, ULSI (ang. Super Large Scale of Integration, Ultra Large Scale of Integration) oznacza największy stopień scalenia układu elektronicznego w obiegowej klasyfikacji. Układy ULSI zawierają w jednej strukturze krzemowej miliony tranzystorów. Tyle elementów zawierają np. architektury procesorów 32 i 64 bitowych.

Układy scalone klasyfikuje się również ze względu na technologie, w jakich zostały wykonane. Do najbardziej popularnych należą następujące technologie:

TTL (ang. Transistor Transistor Logic),

ECL (ang. Emiter Coupled Logic),

MOS (ang. Metal Oxide Semiconductor),

CMOS (ang. Complementary Metal Oxide Semiconductor).

Osiągnęły one wysoki poziom technologiczny i znaczne upowszechnienie rynkowe oraz w dalszym ciągu są ulepszane jakościowo i rozszerzane asortymentowo.

Układy kombinacyjne

Układem kombinacyjnym nazywamy układ, w którym każda kombinacja sygnałów wejściowych jednoznacznie określa kombinację sygnałów wyjściowych. Kombinacja sygnałów wejściowych nazywana jest stanem wejść, natomiast kombinacja sygnałów wyjściowych - stanem wyjść.

Oznaczymy przez X zbiór wszystkich możliwych stanów wejść, zaś przez Y zbiór wszystkich możliwych stanów wyjść. Rozważmy układ kombinacyjny o m wejściach i n wyjściach. Działanie układu kombinacyjnego opisuje funkcja logiczna:

![]()

,

równoważna układowi następujących funkcji logicznych:

![]()

![]()

![]()

Układ kombinacyjny można opisać również za pomocą tablicy prawdy.

Analiza układów kombinacyjnych

Analiza układu kombinacyjnego polega na określeniu relacji pomiędzy wartościami jego wejść i wyjść. Śledząc sygnały na wejściach i wyjściach każdej bramki otrzymujemy funkcje logiczne. Poniższe akapity omawiają przykładowe, proste układy kombinacyjne.

Bramy, multipleksery i demultipleksery

Przyglądając się tabeli stanów bramki AND można stwierdzić, że jeżeli na wejściu S jest stan 0, wówczas na wyjściu jest także stan 0. Natomiast, gdy na wejściu S jest stan 1, na wyjściu bramki jest taki sam sygnał jak na drugim wejściu A. Tę właściwość bramki AND wykorzystuje się do budowy układów przepuszczających lub zatrzymujących informację zwanych bramami (rys. 2).

Gdy na wejściu sterującym S jest sygnał 0 („brama zamknięta”), wtedy wszystkie wyjścia Bi mają stan 0. Gdy S = 1 wówczas Bi = Ai („brama otwarta”).

Rys.2. Brama: A0, A1, A2 - wejścia informacyjne; S - wejście sterujące; B0, B1, B2 - wyjścia.

Bramy znajdują zastosowanie przy sterowaniu przesyłaniem informacji. Do tych samych celów mogą zostać zastosowane multipleksery i demultipleksery. Multiplekserem nazywamy układ kombinacyjny wybierający informację dwójkową na jednej z linii wejściowych i kierujący ją na jedną linię wyjściową. Wybór linii wejściowej jest określany przez linie sterujące. Sieć realizującą układ multipleksera o 22 liniach wejściowych i 2 liniach sterujących jest pokazana na rysunku 3.

Rys. 3. Multiplekser o czterech wejściach i dwóch liniach adresowych (sterujących).

Demultiplekser kieruje informację z wejścia X na jedno z wyjść Yi, w zależności od kombinacji bitów na wejściu adresowym (rys. 4).

Rys. 4.Demultiplekser dwóch liniach adresowych i czterech liniach wyjściowych.

Układy arytmetyczne

Układ kombinacyjny dodający dwie cyfry dwójkowe jest nazywany półsumatorem (ang. Half Adder). Wynik dodawania dwóch liczb jednobitowych w ogólnym przypadku jest liczbą dwubitową (np. 1 B+1 B = 10 B). Zmiennymi wejściowymi półsumatora są bity składników (A, B). Zmiennymi wyjściowymi są bity sumy S i przeniesienia C (bardziej znaczący bit wyniku). Sieć (rys. 5) i tablica prawdy (tab. 2) dla półsumatora są przedstawione poniżej.

Wejścia |

Wyjścia |

||

pulsem |

B |

C |

S |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

Tabela 2. Tablica prawdy dla półsumatora.

Z tablicy prawdy półsumatora otrzymujemy następujące funkcje logiczne:

![]()

![]()

.

Na tej podstawie możemy narysować schemat logiczny półsumatora (rys. 5).

(a)

|

(b)

|

Rys. 5. Półsumator: (a) układ bramek, (b) symbol.

Korzystając z praw de Morgana można przedstawić funkcje S(A, B) oraz C(A, B) w postaci:

![]()

![]()

i na ich podstawie narysować schemat logiczny półsumatora zrealizowanego za pomocą bramek NAND.

Układ kombinacyjny dodający trzy cyfry dwójkowe jest nazywany sumatorem pełnym (ang. Full Adder). Ma trzy wejścia. Dwie ze zmiennych wejściowych (A, B) reprezentują bity składników sumy. Trzecie wejście (C1) reprezentuje przeniesienie z poprzedniej, mniej znaczącej pozycji. Zmiennymi wyjściowymi są bity sumy S i przeniesienia C. Tablica prawdy dla sumatora pełnego jest przedstawiona w tabeli 3.

Wejścia |

Wyjścia |

|||

A |

B |

C1 |

C |

S |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Tabela 3. Tablica prawdy dla sumatora.

Z tablicy prawdy sumatora pełnego otrzymujemy następujące funkcje logiczne:

![]()

,

![]()

.

Funkcji s(x,y,z) nie można zminimalizować. Zatem

![]()

.

Minimalizując funkcję c(x,y,z) otrzymujemy:

![]()

.

Na podstawie otrzymanych funkcji S(A, B, C1) oraz C(A, B, C1) rysujemy schemat logiczny sumatora. Używając symbolu półsumatora układ można narysować w postaci zaprezentowanej na rys. 6.

(a)

|

(b)

|

Rys. 6. Sumator pełny: (a) - układ bramek, (b) symbol.

Sumę dwóch n-bitowych liczb dwójkowych można uzyskać w układzie n-bitowego sumatora równoległego.

Dekodery

Dekoderem (konwerterem kodu) nazywamy układ kombinacyjny realizujący funkcję logiczną zmieniającą informację dwójkową z jednej postaci na drugą (z jednego kodu na inny). Sieć realizującą przykładowy układ dekodera 3 - bitowego przedstawiono na rysunku 7.

Rys. 7. Konwerter naturalnego kodu binarnego na kod Graya.

Zaprezentowany na rys. 7 układ realizuje konwersję według tablicy prawdy, zamieszczonej w tabeli 4.

Naturalny kod binarny |

Kod Graya |

||||

X2 |

X1 |

X0 |

Y2 |

Y1 |

Y0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

Tabela 4. Tablica prawdy dla konwertera kodu naturalnego na kod Graya.

Układy sekwencyjne

Do dalszych rozważań wprowadzimy dyskretną skalę czasu. Kolejne punkty na tej skali będziemy oznaczać liczbami naturalnymi 1, 2, ..., t-1, t, t+1, .... Zbiór wszystkich możliwych stanów wejść układu w chwili t będziemy oznaczać przez Xt, natomiast zbiór wszystkich możliwych stanów wyjść układu w chwili t przez Yt.

W układach kombinacyjnych stan wejść Xt wyznacza jednoznacznie stan wyjść Yt.

W układach sekwencyjnych stan wyjść Yt zależy nie tylko od stanu wejść Xt, lecz także od stanu wejść Xt-1, Xt-2, .... Układ sekwencyjny jest zatem układem z pamięcią.

Kolejne punkty na dyskretnej skali czasu układu sekwencyjnego odpowiadają kolejnym zboczom jednakowego typu (dodatnim, ujemnym) impulsów zegarowych (ang. Clock pulses). Diagram czasowy impulsów zegarowych jest przedstawiony na rysunku 8.

Rys. 8. Diagram czasowy impulsów zegarowych o częstotliwości ![]()

.

1

2

zbocze dodatnie (narastające)

poziom

zbocze ujemne (opadające)

t

okres T

t+1

czas

Wyszukiwarka