Sprawozdanie 6

Układy cyfrowe i systemy wbudowane

Prow.: dr inż. Dariusz Caban

Założenia

Celem laboratorium była obsługa wyświetlacza LED w taki sposób, by w pierwszym wierszu wyświetlacza wyświetlono liczbę liter każdego z tworzących układ, a w drugim wierszu wyświetlono licznik odliczający od zera do sumy liczby liter tworzących układ.

Wykonanie

Wykonano językiem VHDL, korzystając ze schematu.

Uznaliśmy, że do wykonania tego zadania potrzebujemy dwóch sygnałów licznika. Jednego, tego właściwego i drugiego opóźniającego. Licznik opóźniający został stworzony jako wektor 25-cio bitowy, powodujący opóźnienie równe około 1 sekundy. Drugi, właściwy licznik miał za zadanie liczyć od zera do dziewięciu, dlatego został zaprojektowany jako wektor trój bitowy. Dla ładniejszego wyświetlania uznaliśmy, że w pierwszej linii na pierwszym miejscu od prawej zostanie wyświetlona liczba liter jednego wykonawcy, a na pierwszym miejscu od lewej drugiego. W naszym przypadku (3 i 6). Miejsca pomiędzy cyframi zostały wygaszone. Licznik w drugiej linii wyświetlacza natomiast znajdował się po środku wyświetlacza, reszta miejsc wygaszona.

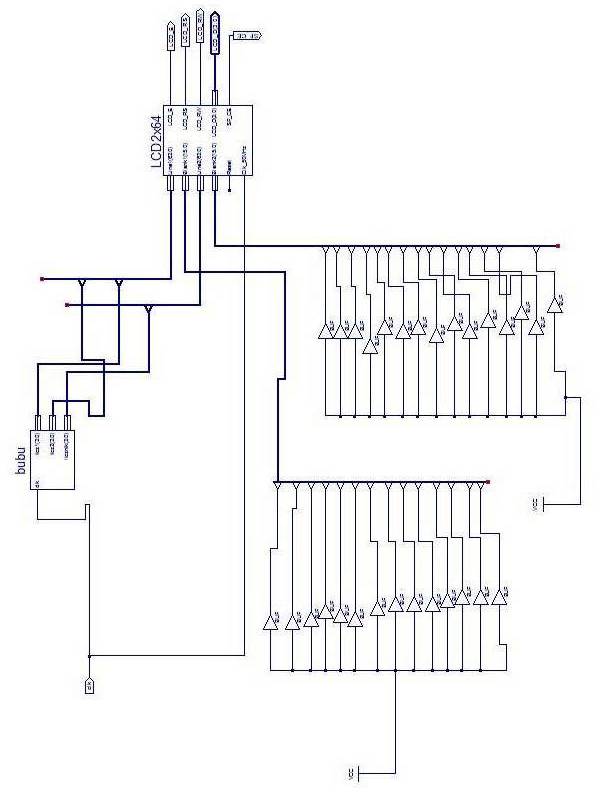

Schemat układu:

Objaśnienia:

Wykorzystano gotowy już moduł dwuwierszowej obsługi wyświetlacza o nazwie LCD2x64. Moduł posiada pięć wyjść, do których podpięto wyjścia z układu o tych samych nazwach co w pliku ucf obsługi wyświetlacza LCD. Moduł posiada cztery wejścia plus wejście na zegar. Pierwsze wejście Line1 obsługuje wyświetlanie znaków w pierwszym wierszu, Blink1 gaszenie pozycji w pierwszym wierszu. Analogicznie pozostałe dwa wejścia obsługują drugi wiersz wyświetlacza.

Do magistrali dla wejścia Blink1(0:15) podpięto vcc na pozycjach (1:14), gdyż na pozycji 0 i 15 będą wyświetlana ilość liter w imionach wykonujących ćwiczenie. Do magistrali dla wejścia Blink2 podpięto vcc na pozycjach (0:6) i (8:15), by licznik wyświetlał się w połowie drugiego wiersza.

Do wejścia Line1 podpięto na magistrali(0) i (15) sygnały wyjścia licz1 i licz2 z modułu „bubu”. Do Line2 sygnał licznik na pozycji (7).

Opis modułu „bubu” poniżej.

Kod VHDL:

Powyższy moduł posiada tylko jedno wejście zewnętrzne na moduł. Z początku ustawiono zmienne licz1 i licz2 na 3 i 6 i od razu wysłano do wyjścia modułu.

Następnym krokiem było stworzenie licznika. Licznikiem nadrzędnym jest licznik o nazwie „licznik2” liczący do ~ 2^25. Wewnątrz licznika2 umiejscowiono drugi o nazwie „temp”, który miał dodać 1 tylko wtedy, gdy nadrzędny licznik dobił do maksymalnej wartości.

Gdy temp osiągnie wartość „1001” czyli 9, co jest sumą liter wykonawców układu, miał wrócić do zera i zacząć liczenie od początku.

Po całym zabiegu sygnał temp wysłano na wyjście licznik.

Wyniki końcowe:

Należy wspomnieć, że żeby dało się wykorzystać takie działanie liczników, oparte na funkcjach arytmetycznych, należy przed właściwym kodem programu umieścić odpowiedniego include'a: use IEEE.STD_LOGIC_UNSIGNED.ALL;

Układ działał poprawnie.

str. 2

Elżbieta Tchorowska 19-01-2011

Konrad Kukulski

str. 1

entity bubu is

Port ( clk : in STD_LOGIC;

licz1 : out STD_LOGIC_VECTOR (3 downto 0);

licz2 : out STD_LOGIC_VECTOR (3 downto 0);

licznik : out STD_LOGIC_VECTOR (3 downto 0));

end bubu;

architecture Behavioral of bubu is

signal temp: std_logic_vector (3 downto 0);

signal licznik2: std_logic_vector (25 downto 0);

begin

licz1<="0011";

licz2<="0110";

process (clk)

begin

if rising_edge (clk) and (clk='1') then

if (licznik2="11111111111111111111111111") then

licznik2<="00000000000000000000000000"; if (temp="1001") then

temp<="0000";

else temp<=temp+"0001";

end if;

end if;

licznik2<=licznik2+"00000001";

end if;

end process;

licznik<=temp;

end Behavioral;

Wyszukiwarka