Projektowanie systemów napięcia

odniesienia dla ADC o sukcesywnej

aproksymacji

Autor: Alan Welsh

Tłumaczenie: Nikodem Czechowski

Efektywna precyzja wysoko rozdzielczych

przetworników Analogowo - Cyfrowych (ADC)

o sukcesywnej aproksymacji (SAR) zależy od

jakości

napięcia

odniesienia

-

jego

dokładności, stabilności czasowej a także

wydajności

prądowej

źródła

napięcia

odniesienia.

Przełączany

kondensator,

znajdujący się na wejściu napięcia odniesienia

przetwornika ADC SAR jest obciążeniem

dynamicznym,

co

oznacza

że

układ

stabilizujący napięcie odniesienia musi być

zdolny do obsłużenia takiego obciążenia pod

względem stabilności czasowej i prądowej.

Niektóre układy ADC integrują w swojej

strukturze źródło napięcia odniesienia oraz

bufor dla tego napięcia, jednakże w wielu

aplikacjach jest to rozwiązanie dalekie od

optymalnego, a dużo lepsze efekty można

osiągnąć stosując zewnętrzne stabilizatory

napięcia odniesienia wraz z stosownymi

buforami. W poniższym artykule opisano jakie

wyzwania

czekają

na

projektantów

pragnących stworzyć taki układ w swoim

systemie.

Anatomia wejścia napięcia odniesienia

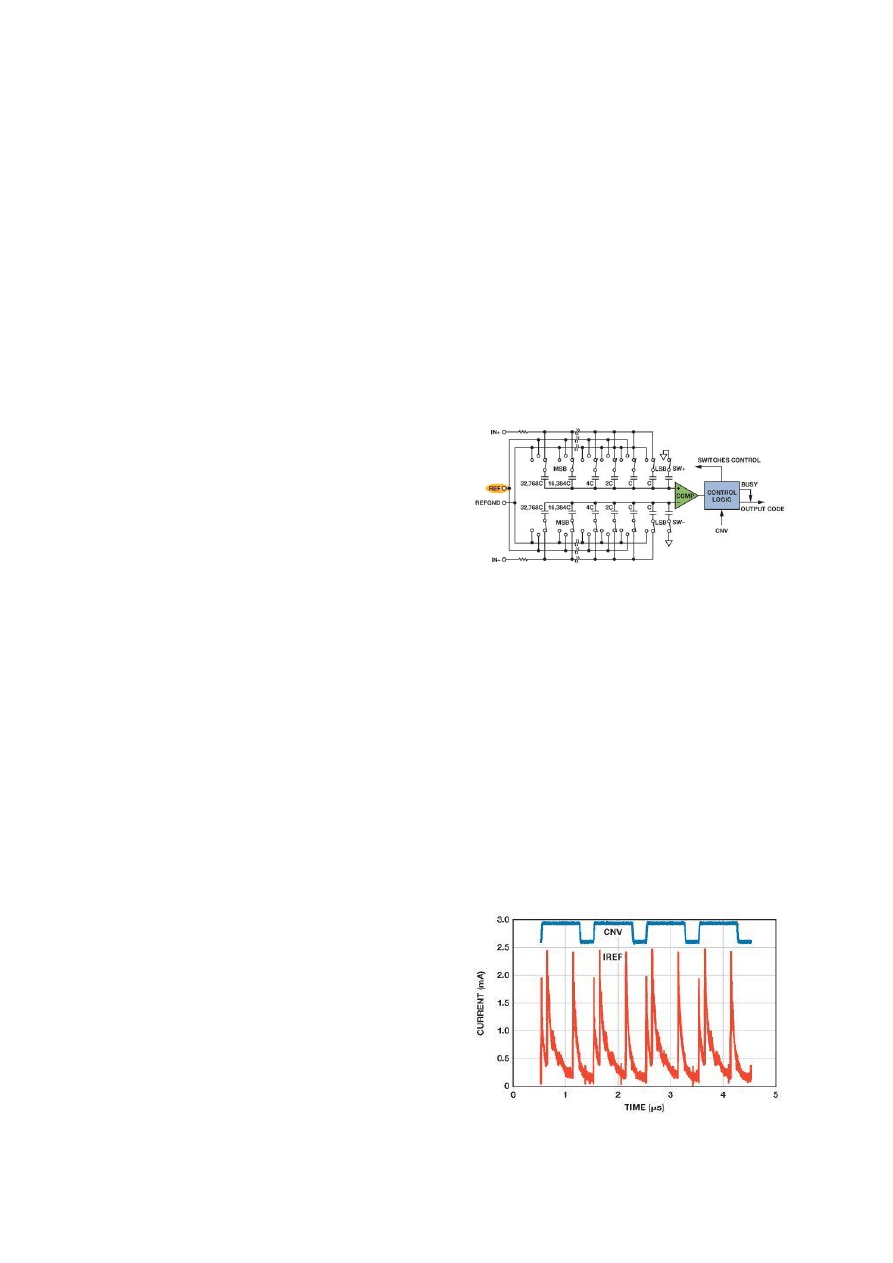

Uproszczony

schemat

przetwornika

analogowo-cyfrowych

pokazany

jest

na

poniższej ilustracji. Podczas próbkowania,

kondensatory tworzące układ przetwornika

cyfrowo-analogowego (DAC) podłączone są do

wejścia układu ADC i są ładowane ładunkiem,

który jest proporcjonalny do napięcia na

wejściu przetwornika. Gdy układ przechodzi w

stan konwersji pojemności te są odłączane od

wejść przetwornika, algorytm konwersji

sukcesywnie przełącza każdy do referencji lub

do masy. Zmiana rozkładu ładunku powoduje

w tym momencie zwiększenie poboru prądu z

układu

stabilizacji

napięcia

odniesienia.

Dynamika poboru prądu zależna jest od

szybkości przetwarzania układu ADC oraz od

częstotliwości

wewnętrznego

zegara,

kontrolującego przełączanie poszczególnych

pojemności odpowiadających kolejnym bitom.

Kondensator

odpowiadający

najbardziej

znaczącemu

bitowi

(MSB)

gromadzi

największy

ładunek

i

w

konsekwencji

powoduje największy pobór prądu.

Wykres, pokazany poniżej, obrazuje

dynamiczny pobór prądu na wejściu

układu AD7980. Jest to przetwornik ADC o

sukcesywnej aproksymacji, firmy Analog

Devices. Układ ten jest częścią rodziny

PulSAR®, charakteryzuje się 16 bitową

rozdzielczością i prędkością przetwarzania

1

MSPS.

Prąd

mierzono

poprzez

wstawienie 500 Ω opornika w tor napięcia

odniesienia i monitorowanie spadku

napięcia na nim. Wykres pokazuje szpilki

poboru prądu sięgające aż do 2,5 mA oraz

mniejsze, które pojawiają się podczas

procesu konwersji.

Aby dostarczyć taki prąd w sposób wolny

od szumu kondensator o dużej pojemności

charakteryzujący

się

niskim

ESR

(efektywna

rezystancja

szeregowa).

Typowo stosuje się tutaj wartości

pojemności 10 µF lub więcej, umieszczone

możliwie

blisko

wejścia

napięcia

odniesienia do układu ADC. Większy

kondensator wygładzi to napięcie lepiej,

jednakże im większa pojemność tym

większą rolę gra stabilność układu. Co

więcej konieczne jest zaprojektowanie

układu stabilizacji napięcia odniesienia w

taki sposób aby był on w stanie naładować

ten kondensator dostatecznie szybko i bez

powodowania

znacznych

spadków

napięcia na linii odniesienia. W kartach

katalogowych przetworników ADC podaje

się jedynie średni prąd pobierany przez

układ z napięcia odniesienia przy zadanej

szybkości przetwarzania. Na przykład dla

opisywanego układu AD7980 w karcie

katalogowej prąd ten, przy przetwarzaniu

z prędkością 1 miliona próbek na sekundę

i napięciem odniesienia 5 V wynosi 330

µA. Pomiędzy konwersjami nie jest

pobierany prąd, zatem skaluje się on z

prędkością przetwarzania, spadając do na

przykład 33 µA przy 100 kSPS. Stabilizator

napięcia odniesienia, lub jego bufor, musi

posiadać możliwie niską impedancję

wyjściową przy częstotliwości zadanej

prędkością próbkowania, tak aby napięcie

odniesienia mogło być dostarczane do

układu przetwornika ADC bez spadków

wywołanych

dynamicznym

poborem

prądu przez ten układ.

Driver napięcia odniesienia

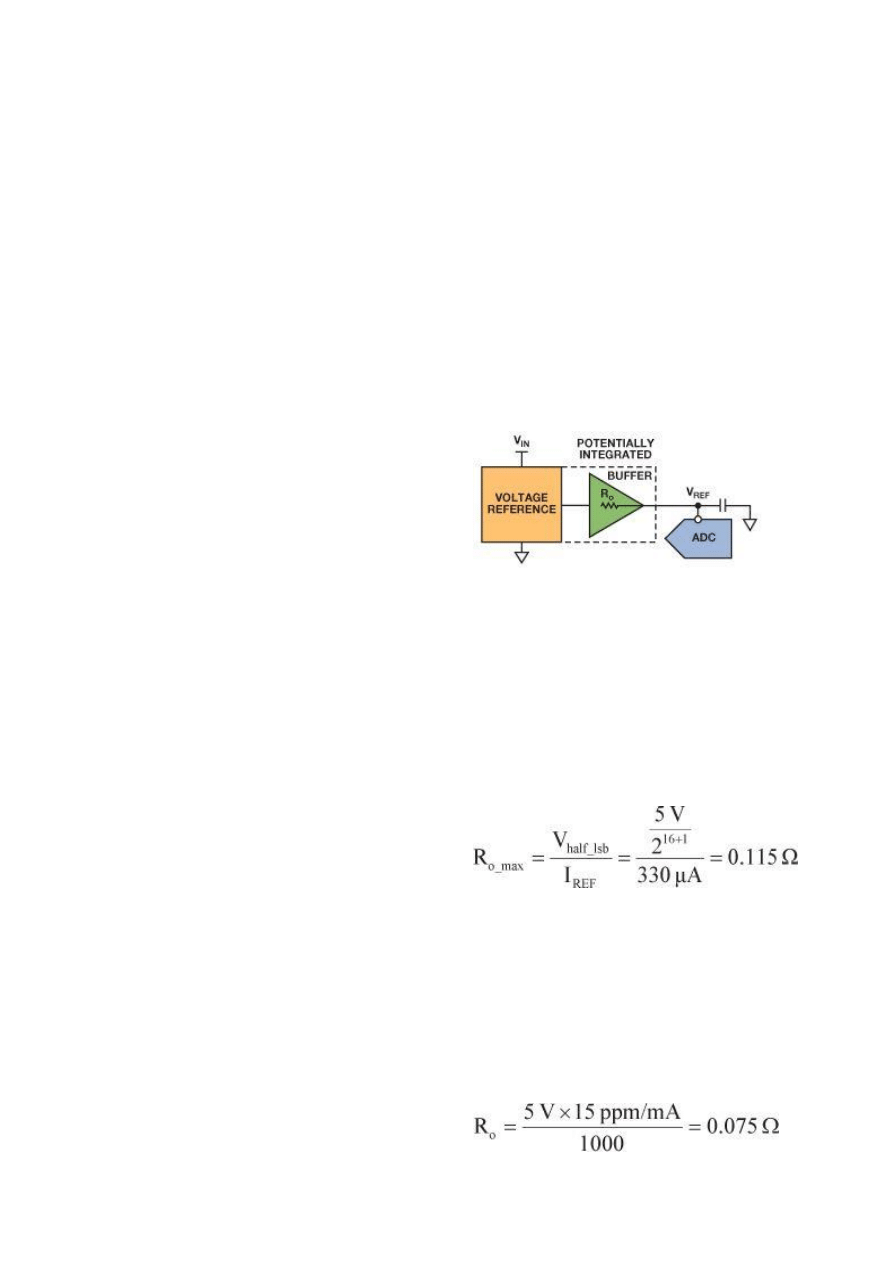

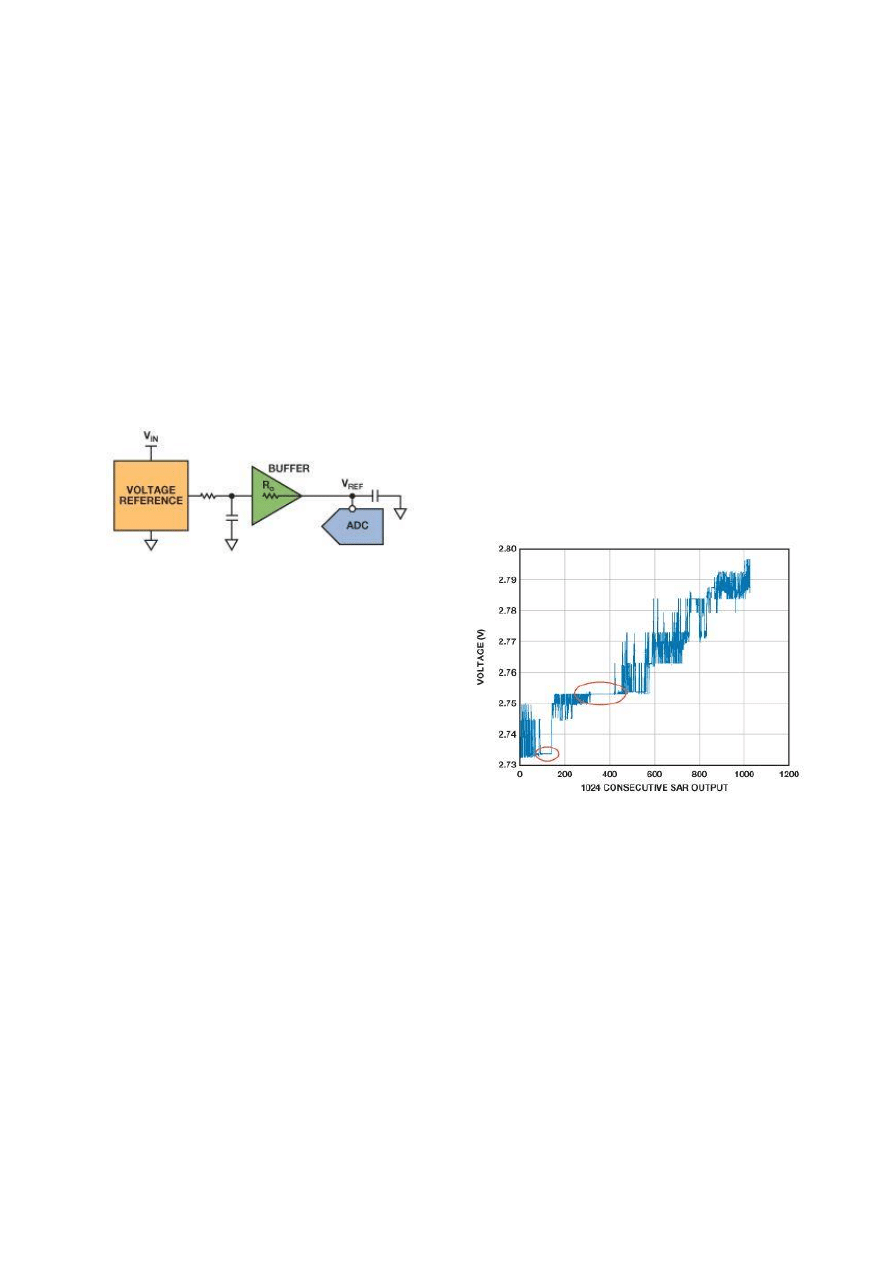

Poniższy schemat pokazuje typowy układ

napięcia odniesienia. Stabilizator tego

napięcia może być wbudowany w bufor

lub też jako bufor może służyć zewnętrzny

wzmacniacz operacyjny. Aby uniknąć

błędów w konwersji analogowo-cyfrowej

średni prąd pobierany przez przetwornik

nie może spowodować spadku napięcia

odniesienia większego niż ½ LSB. Błąd

spowodowany zmianą tego napięcia w

funkcji

pobieranego

prądu

będzie

najbardziej odczuwalny podczas konwersji

serii próbek, gdyż obciążenie napięcia

odniesienia zmieniać się będzie od zera do

maksimum z częstotliwością próbkowania.

Posłużmy się przykładem 16 bitowego

układu AD7980, omawianego wcześniej w

celu dokonania pewnych obliczeń. Średni

prąd napięcia odniesienia pobierany przez

ten układ wynosi 330 µA przy napięciu

odniesienia 5 V. Zakładamy maksymalny

spadek napięcia jako połowę LSB, zatem

impedancja wyjściowa bufora napięcia

odniesienia Ro musi wynieść:

Większość

scalonych

stabilizatorów

napięcia

odniesienia

nie

podaje

impedancji wyjściowej, a jedynie odchyłkę

napięcia w funkcji poboru prądu jako

ppm/mA. Układ ADR435 firmy Analog

Devices może poszczycić się 15 ppm/mA,

aby przeliczyć to na impedancję wejściową

korzystamy z prostego wzoru:

Zatem układ ten spełnia wymagania.

Według karty katalogowej jest w stanie

dostarczyć do 10 mA, co spełnia w 100%

wymagania układu przetwornika. Co

więcej możliwe jest także wpływanie

prądu 10 mA do układu napięcia

odniesienia, co może mieć miejsce gdy na

wejściu przetwornika ADC pojawi się

napięcie większe niż 5 V. Dzieje się tak w

skutek zadziałania diod zabezpieczających

na

wejściu

układu

przetwornika

analogowo-cyfrowego

AD7890.

Zabezpieczenie to jest pokazane na

poniższym rysunku

Jako że średni prąd wejściowy pobierany z

napięcia

odniesienia

przez

układ

przetwornika

analogowo-cyfrowego

skaluje

się

liniowo

z

jego

przepustowością(=częstotliwością

próbkowania) układ odniesienia o większej

impedancji wyjściowej, czyli mniejszej

mocy, może być w pełni akceptowalny w

naszej aplikacji, o ile odpowiednio

zmniejszymy częstotliwość próbkowania

układu ADC, albo zastosujemy inny,

wolniejszy przetwornik. Przykładem może

być tutaj rodzina układów AD9=7988 -

układy te charakteryzują się różnym

średnim prądem, odpowiednio mniejszym

niż ten pobierany przez szybszy AD7890.

Pracujący z prędkością 500 kSPS AD7988-5

lub AD7988-1 pracujący do 100 kSPS

pobierają nie więcej niż 250 µA podczas

pracy. Pamiętać oczywiście należy że

podawane

tutaj

równania

nie

odzwierciedlają w pełni rzeczywistości i

należy z nich korzystać tylko jako

wyznaczników do doboru elementów,

które finalnie i tak muszą zostać

przetestowane w świecie rzeczywistym.

Buforowanie napięcia odniesienia

Dodatkowy bufor napięcia odniesienia

może być zastosowany, jeśli wydajność

prądowa

użytego

źródła

napięcia

odniesienia jest niewystarczająca. Do

wykonania takiego bufora wystarczy

zaimplementować wzmacniacz operacyjny

w konfiguracji tzw. unity-gain czyli z

wzmocnieniem równym jeden. Preferuje

się

tutaj

zastosowanie

układów

charakteryzujących się niskim szumem

które nie dość że spełniają wymagania co

do prądu wyjściowego to są w stanie

pracować

z

obciążeniem

pojemnościowym. Dodatkowo warto także

zwrócić uwagę iż nie każdy wzmacniacz

operacyjny

może

pracować

przy

wzmocnieniu równym jeden, te które

mogą są oznaczone jako 'unity gain stable'

(przyp. tłum.). W kartach katalogowych

rzadko kiedy specyfikuje się jako-taką

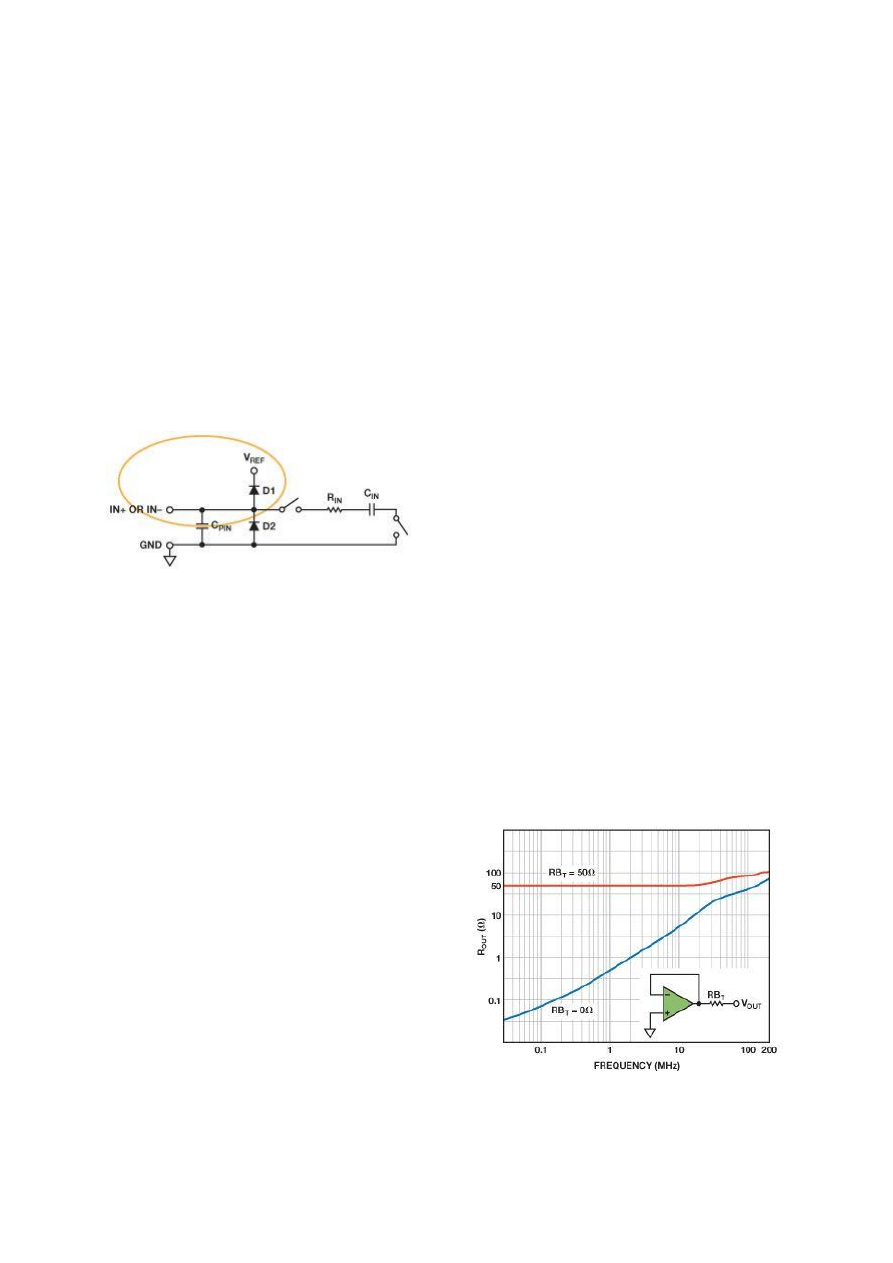

impedancję wyjściową, jednakże da się ją

często odczytać z wykresu impedancji w

funkcji częstotliwości pracy. Taki wykres,

dla układu AD8031 o pasmie 80 MHz

pokazano poniżej.

Jak łatwo odczytać z wykresu impedancja

wyjściowa jest mniejsza od 0.1 Ω przy 100

kHz i mniejsza niż 0.05 Ω przy napięciu

stałym. Jest to zatem dobry wybór do

buforowania napięcia odniesienia układu

AD7980 pracującego przy 1 MSPS.

Zachowanie niskiej impedancji przez

możliwie szeroki zakres częstotliwości jest

istotne dla konstrukcji dobrego drivera

układu napięcia odniesienia. Kondensator

filtrujący na tej linii nie jest w stanie nigdy

wygładzić wszystkich wynikających z

poboru prądu zakłóceń, nawet jeśli będzie

miał znaczną pojemność. Częstotliwość

zakłóceń prądowych w tej linii będzie

funkcją częstotliwości próbkowania i

pasma układu bufora napięcia odniesienia.

Duży kondensator filtrujący poradzi sobie z

wysokimi częstotliwościami wynikającymi

z pracy układu ADC przy częstotliwości 1

MHz

(taka

jest

częstotliwość

próbkowania),

natomiast

niskie

częstotliwości muszą być odfiltrowane

przez driver. Punktem spotkania obu

charakterystyk jest miejsce na spektrum w

którym impedancja kondensatora jest już

na tyle mała że przejmuje on rolę

dostarczania

prądu

przy

konkretnej

częstotliwości. Poniżej tej częstotliwości

prąd pobierany jest przede wszystkim z

wzmacniacza operacyjnego, dlatego tak

istotna jest jego impedancja dla niższych

częstotliwości.

Układ AD8031 jest dobrym rozwiązaniem

bufora napięcia odniesienia gdyż pracuje

stabilnie z obciążeniami pojemnościowymi

większymi niż 10 µF. Inne wzmacniacze

operacyjne, takie jak ADA4841, także

dobrze współpracują z obciążeniem

pojemnościowym, jednakże nie są stabilne

przy prądzie stałym (DC). Jednakowoż,

mimo tego, i tak wskazanym jest

testowanie układu przed ich aplikacją w

układzie. Niewskazane z kolei jest

dodawanie szeregowej rezystancji przed

obciążeniem

pojemnościowym,

gdyż

takowa znacznie zwiększa impedancję

wyjściową

(co

widać

na

wykresie

powyżej).

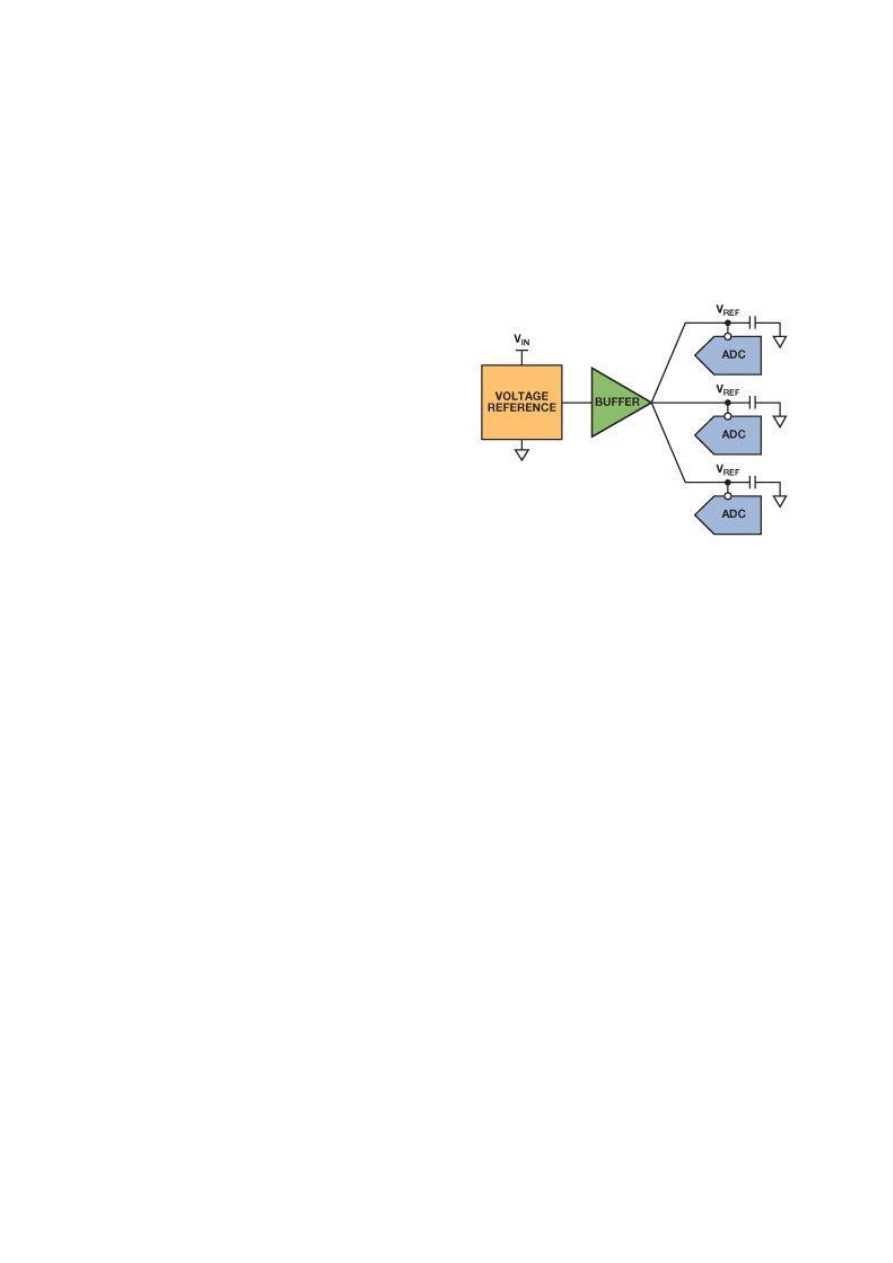

Dodatkową zaletą stosowania bufora

napięcia odniesienia jest buforowanie

napięcia dla systemów równoległych

przetworników analogowo-cyfrowych o

symultanicznym próbkowaniu. System

taki, pokazany na poniższym schemacie,

charakteryzuje się zwiększonym poborem

prądu z napięcia odniesienia.

Każdy z układów ADC ma swój własny

kondensator filtrujący, umieszczony blisko

doprowadzeń napięcia odniesienia do

układu. Ścieżki napięcia odniesienia są

potem podłączone w topologii gwiazdy, do

wyjścia bufora referencji. Takie połączenie

minimalizuje

przesłuch

pomiędzy

kanałami. Bufory charakteryzujące się

niską impedancją i dużym prądem

wyjściowym są w stanie wysterować

znaczną ilość przetworników ADC naraz.

Warto pamiętać iż w takim przypadku

wzrasta pojemność obciążenia i układ

musi być stabilny z taką pojemnością na

obciążeniu.

Szum i dryft termiczny

Gdy już upewnimy się iż zaprojektowany

przez

nas

układ

drivera

napięcia

odniesienia spełnia wymagania które

stawia mu przetwornik ADC upewnić się

musimy że szum pochodzący z układu

napięcia referencyjnego nie będzie miał

większego wpływu na pracę konwertera

analogowo-cyfrowego.

Aby

zachować

specyfikowane dla układu parametry,

takie jak SNR, musimy zagwarantować aby

szum napięcia odniesienia nie wprowadzał

zakłóceń do ADC, typowo przyjmuje się

aby jego wartość była ułamkiem szumu

samego

przetwornika

(zwyczajowo

zakłada się 20% i mniej jako wartość

idealną).

AD7980

w

swojej

karcie

katalogowej, przy pracy z napięciem

odniesienia 5 V charakteryzuje się 91

decybelowym odstępem sygnału od

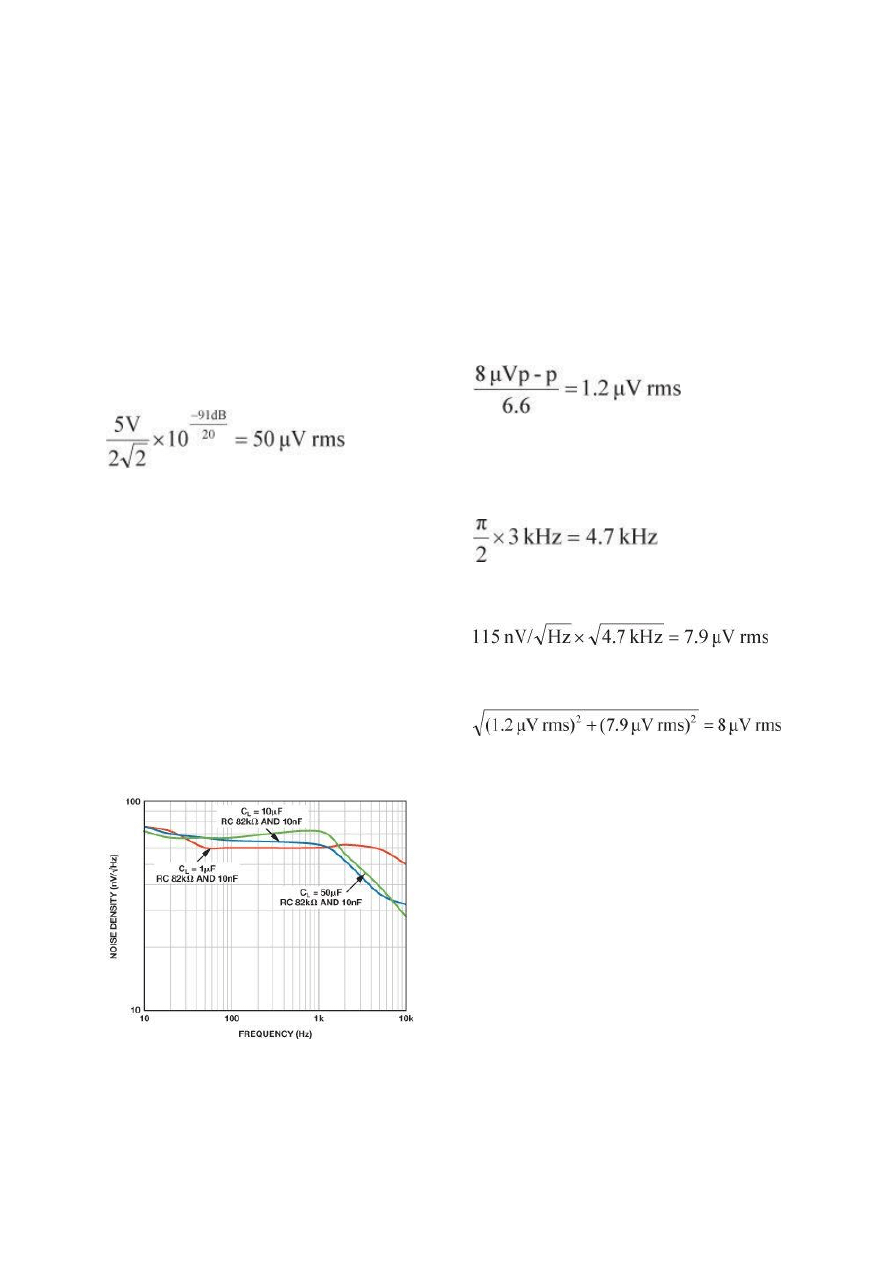

szumu. Po konwersji do rms otrzymujemy:

Zatem układ napięcia odniesienia musi

mieć mniej niż 10 µV rms szumu, aby mieć

minimalny wpływ na SNR całego systemu.

Specyfikacje szumowa układów stabilizacji

napięcia

odniesienia

i

wzmacniaczy

operacyjnych składają się z dwóch części -

szumu niskiej częstotliwości (1/f) i szumu

szerokopasmowego. Złożenie tych dwóch

szumów pozwala na ocenę całkowitego

wpływu układu na SNR projektowanego

systemu. Na poniższym wykresie pokazano

krzywą szumu w funkcji częstotliwości dla

układu ADR431, stabilizatora napięcia

odniesienia 2,5 V.

Układ

ADR435

kompensuje

swój

wewnętrzny wzmacniacz operacyjny w

celu poprawnej pracy z obciążeniem dużą

pojemnością i wygładzenia charakterystyki

szumowej - czyni go to niezwykle

atrakcyjnym do pracy z układami ADC.

Kompensacja ta jest opisana szerzej w

karcie katalogowej układu. Z pojemnością

10 mikro faradów jako obciążeniem

specyfikuje się mu szum 1/f na poziomie 8

µV p-p, a gęstość widmowa szumu

szerokopasmowego 115 nV/√Hz. Pasmo

szumu wynosi 3 kHz. Aby skonwertować

wartość szumu 1/f na rms podzielić należy

wartość peak-to-peak na rms podzielić

należy go przez 6,6, aby otrzymać:

Następnie,

obliczamy

wpływ

szumu

szerokopasmowego na całkowity szum

przy takim obciążeniu. Efektywne pasmo

obliczmy jako:

Korzystając z tego pasma obliczamy zatem

rms szumu szerokopasmowego:

A całkowity szum obliczamy jako średnią

kwadratową obu szumów rms:

Zatem szum wyniesie mniej niż 10 µV rms,

zatem nie będzie miał on wpływu na SNR

systemu. Takie równania mogą zostać

wykorzystane do oceny wpływu szumu na

pracę układów ADC w ogólności. Jednakże

należy pamiętać iż są to tylko obliczenia i

gotowy

układ

należy

zweryfikować

fizycznymi

pomiarami

na

gotowym

prototypie.

Taka

sama

analiza

może

zostać

wykorzystana do oceny wpływu buforu na

szum napięcia odniesienia. Na przykład

AD8031 charakteryzuje się gęstością

widmową szumu o wysokości 15 nV/√Hz. Z

10 µF obciążeniem pasmo efektywne

wynosi około 16 kHz. Jeśli pominiemy w

obliczeniach wpływ szumu 1/f całkowity

szum wyniesie 2.4 µV rms. Wartość tą

można dodać tak jak powyżej do wartości

szumu z napięcia odniesienia aby otrzymać

realną wartość. Generalnie bufor powinien

mieć znacznie mniejszy szum niż samo

źródło napięcia odniesienia.

Dodatkowo, przy wykorzystaniu bufora,

możliwe jest ograniczenie pasma sygnału

poprzez dodanie filtra RC. Schemat taki

pokazany jest na poniższym rysunku.

Pozwala to na ograniczenie pasma, a w

konsekwencji zmniejszenie wpływu szumu

szerokopasmowego na całkowity poziom

szumu w układzie.

Innym

istotnym

zagadnieniem

przy

doborze napięcia odniesienia jest jego

dokładność i dryft termiczny. Dokładność

podawana jest w procentach lub mV i w

systemach

gdzie

dokonywana

jest

wstępna kalibracja nie jest ona tak istotna

jak dryft. Dryft specyfikowany jest w

ppm/°C lub µV/°C. Większość dobrych

napięć

odniesienia

musi

się

charakteryzować dryftem poniżej 10

ppm/°C. Pamiętać należy że zmiana

wartości napięcia referencyjnego w funkcji

temperatury będzie miała wpływ na

całkowity

błąd

pomiarowy

projektowanego systemu.

Rozwiązywanie problemów z napięciem

odniesienia

Źle zaprojektowany układ stabilizacji i

buforowania napięcia odniesienia dla

układu

przetwornika

ADC

może

wprowadzić

poważne

błędy

do

konwertowanej wartości. Najczęstszymi

przykładami

takich

problemów

są

powtarzające się wartości konwersji. Taka

sytuacja zdarza się gdy szum napięcia

odniesienia powoduje że przetwornik

popełnia błąd podczas estymacji jednego z

bitów, co widoczne jest jako konkretna

wartość cyfrowa powtarzająca się kilka

razy, nawet pomimo zmiany napięcia

wejściowego np. ciągle pojawiające się

zero jako LSB. Taką sytuację pokazano na

poniższym wykresie. Czerwone okręgi

zaznaczają

miejsca

gdzie

utknęły

konkretne kody, przez co na wyjściu

widzimy

powtarzające

się

wartości.

Problem ten, generalnie, staje się bardziej

zauważalny przy napięciach wejściowych

bliskich pełnej skali przetwornika, gdyż w

takiej sytuacji szum może mieć większy

wpływ na bardziej znaczące bity.

Najczęstszym

powodem

powstawania

takich przebiegów z utkniętymi bitami jest

niepoprawna wielkość i umieszczenie

względem układu ADC kondensatora

filtrującego napięcie referencyjne dla

konwertera. Powodować to też mogą

bufory

napięcia

odniesienia

o

niewystarczającej mocy lub generujące

zbyt duży poziom szumu. Wynika to

najczęściej z nieodpowiedniego doboru

układu buforującego.

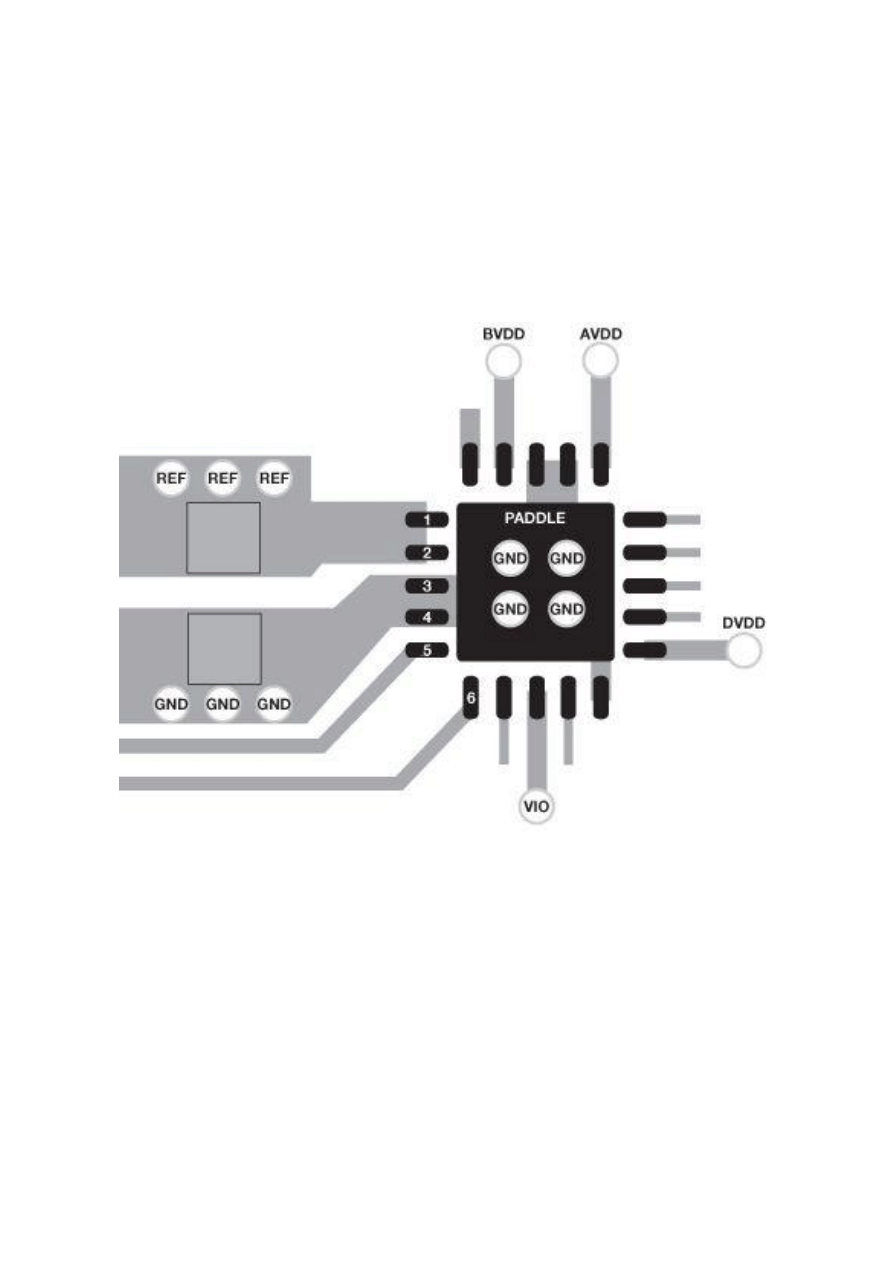

Niezwykle istotnym jest umieszczenie

kondensatorów

filtrujących

napięcie

odniesienia blisko pinów wejściowych ADC

używając możliwie szerokich ścieżek.

Proponowany rozkład pokazany jest na

poniższej

ilustracji.

Kondensator

zastosowany w tym miejscu musi

charakteryzować się niską impedancją do

masy, wskazane zatem jest zastosowanie

większej ilości przelotek łączących jego

wyprowadzenie z wylewką masy. Dobrym

wyborem są kondensatory z dielektrykiem

X5R o pojemności od 10 do 47

mikrofaradów.

Mniejsze

także

są

akceptowalne,

jednakże

zależy

to

dokładnie od poboru prądu przez wejście

ADC.

Wyszukiwarka

Podobne podstrony:

projektowanie systemów technicznych arkusz dla prowadzącego

WSTĘPNE ZAŁOŻENIA PROJEKTOWE SYSTEMU INFORMACJI PRZESTRZENNEJ DLA OBSZARU DZIAŁANIA ZAKŁADU RATOWNIC

Projekt systemu ocen dla przychodni prima-med. I apteki panaceum, Dokumenty(2)

Projekt kanalizacji deszczowej --- opis, Inżynieria Środowiska, mgr 2 semestr, Projektowanie systemó

Wniosek dla ubiegajacych sie o przyjecie do EINTI, szkola, metodyka projektowania systemow

Ośrodek wsparcia dla ojców samotnie wychowujących dzieci, Magisterka, Projektowanie systemów opiekuń

informatyka microsoft xna game studio 4 0 projektuj i buduj wlasne gry dla konsoli xbox 360 urzadzen

Microsoft XNA Game Studio 4 0 Projektuj i buduj wlasne gry dla konsoli Xbox 360 urzadzen z systemem

Microsoft XNA Game Studio 4 0 Projektuj i buduj wlasne gry dla konsoli Xbox 360 urzadzen z systemem

Projektowanie systemow rozproszonych Wzorce i paradygmaty dla skalowalnych niezawodnych uslug prsyro

Wykorzystanie modelu procesow w projektowaniu systemow informatycznych

Projektowanie systemow zarzadzania

Projekt systemu mebli

pskProjektI6A1N2, Arciuch.Artur, Projektowanie.Systemow

Funkcjonowanie klasycznego systemu MRP, Materiały dla ZiP, sem III

Wykład VII, politechnika infa 2 st, Projektowanie Systemów Informatycznych

Projekt systemy sorpcyjne

więcej podobnych podstron