Rodzaje

Rodzaje

mikroprocesorów –

mikroprocesorów –

opis najbardziej

opis najbardziej

charakterystycznych

charakterystycznych

Rafał Krupa

Rafał Krupa

CISC

CISC

(

(

Complex Instruction Set Computers

Complex Instruction Set Computers

)

)

RISC

RISC

(

(

Rationalized Instruction Set

Rationalized Instruction Set

Computers)

Computers)

EPIC

EPIC

(Explicitly Paralell Instruction

(Explicitly Paralell Instruction

Coumputing)

Coumputing)

MISC

MISC

(

(

Minimal Instruction Set Computer)

Minimal Instruction Set Computer)

ZISC

ZISC

(Zero Instruction Set Computer)

(Zero Instruction Set Computer)

Rodzaje

Rodzaje

mikroprocesorów

mikroprocesorów

Mikroprocesory CISC

Mikroprocesory CISC

Projektanci pierwszych procesorów zakładali, że

Projektanci pierwszych procesorów zakładali, że

komputery będą programowane bezpośrednio w

komputery będą programowane bezpośrednio w

kodzie maszynowym. Dlatego kosztem

kodzie maszynowym. Dlatego kosztem

ograniczenia liczby rejestrów tworzono

ograniczenia liczby rejestrów tworzono

procesory o bardzo rozbudowanych zestawach

procesory o bardzo rozbudowanych zestawach

instrukcji, które miały ułatwiać pisanie

instrukcji, które miały ułatwiać pisanie

programów. Instrukcje były implementowane w

programów. Instrukcje były implementowane w

procesorze jako mikroprogram, a czasy ich

procesorze jako mikroprogram, a czasy ich

wykonywania były długie. Procesory o takich

wykonywania były długie. Procesory o takich

cechach modelu programowego zostały

cechach modelu programowego zostały

nazwane procesorami CISC.

nazwane procesorami CISC.

Mikroprocesory CISC

Mikroprocesory CISC

Jest architektura zestawu instrukcji dla

Jest architektura zestawu instrukcji dla

mikroprocesora, w którym każda

mikroprocesora, w którym każda

instrukcja może wykonać kilka operacji

instrukcja może wykonać kilka operacji

niskiego poziomu, jak na przykład

niskiego poziomu, jak na przykład

pobranie z pamięci, operację

pobranie z pamięci, operację

arytmetyczną, albo zapisanie do pamięci

arytmetyczną, albo zapisanie do pamięci

a to wszystko w jednej instrukcji.

a to wszystko w jednej instrukcji.

Mikroprocesory CISC –

Mikroprocesory CISC –

cechy

cechy

duża liczba rozkazów (instrukcji)

duża liczba rozkazów (instrukcji)

mała optymalizacja – niektóre rozkazy

mała optymalizacja – niektóre rozkazy

potrzebują dużej liczby cykli procesora do

potrzebują dużej liczby cykli procesora do

wykonania

wykonania

występowanie złożonych, specjalistycznych

występowanie złożonych, specjalistycznych

rozkazów

rozkazów

duża liczba trybów adresowania

duża liczba trybów adresowania

do pamięci może się odwoływać

do pamięci może się odwoływać

bezpośrednio duża liczba rozkazów

bezpośrednio duża liczba rozkazów

mniejsza od

-ów częstotliwość

-ów częstotliwość

taktowania procesora

taktowania procesora

powolne działanie dekodera rozkazów

powolne działanie dekodera rozkazów

Mikroprocesory CISC

Mikroprocesory CISC

Z reguły procesory wykonane w

Z reguły procesory wykonane w

architekturze CISC działają wolniej

architekturze CISC działają wolniej

niż procesory, o przeciwstawnych

niż procesory, o przeciwstawnych

założeniach

założeniach

, działające z tą

, działające z tą

samą częstotliwością.

samą częstotliwością.

Mikroprocesory RISC

Mikroprocesory RISC

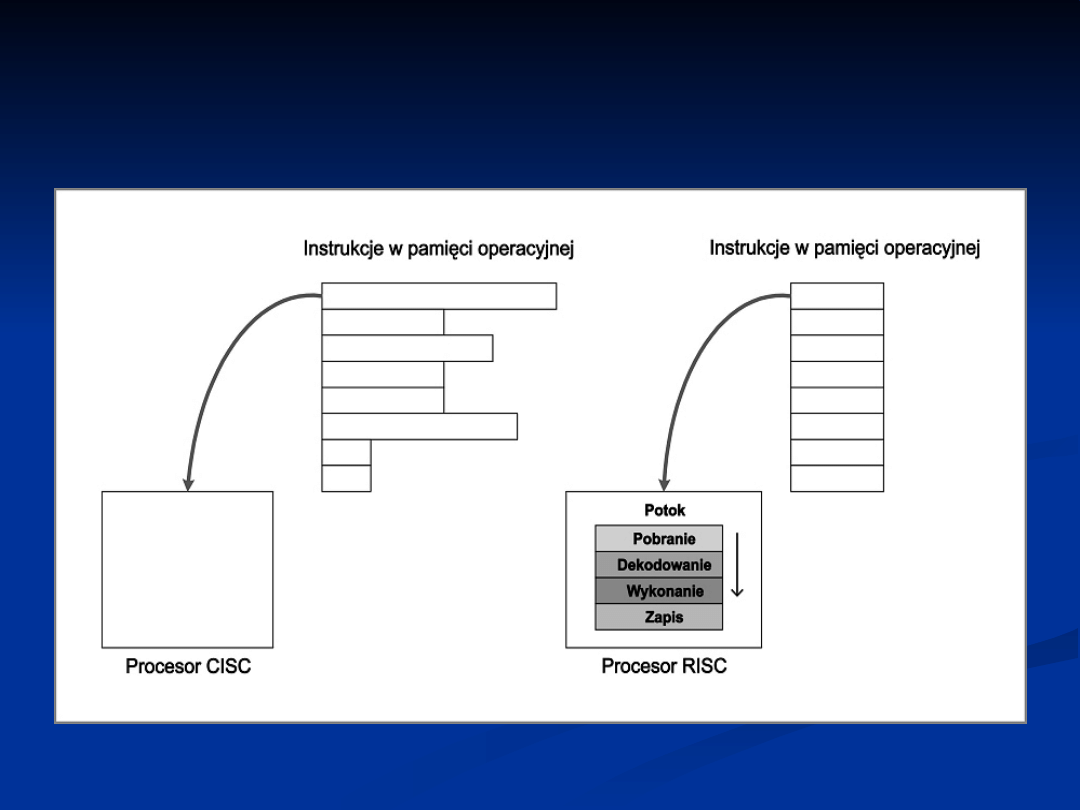

W procesorach RISC wprowadzono pojęcie potoku,

W procesorach RISC wprowadzono pojęcie potoku,

czyli ścieżki przetwarzania instrukcji wewnątrz

czyli ścieżki przetwarzania instrukcji wewnątrz

procesora. Wykonanie instrukcji podzielono na logiczne

procesora. Wykonanie instrukcji podzielono na logiczne

etapy, z których każdy wykonywany był niezależnie na

etapy, z których każdy wykonywany był niezależnie na

określonym stopniu potoku. Instrukcja po pobraniu z

określonym stopniu potoku. Instrukcja po pobraniu z

pamięci przemieszczana była w głąb potoku i

pamięci przemieszczana była w głąb potoku i

przechodziła przez jego stopnie. Po przejściu przez

przechodziła przez jego stopnie. Po przejściu przez

dany stopień potoku można było wykonywać w nim

dany stopień potoku można było wykonywać w nim

kolejną instrukcję. Najprostszy potok składa się z

kolejną instrukcję. Najprostszy potok składa się z

czterech stopni: pobrania instrukcji, dekodowania,

czterech stopni: pobrania instrukcji, dekodowania,

wykonania i zapisu wyniku. Dzięki wprowadzeniu

wykonania i zapisu wyniku. Dzięki wprowadzeniu

potoku możliwe było równoczesne wykonanie i

potoku możliwe było równoczesne wykonanie i

pobieranie kolejnych instrukcji, co dawało w efekcie

pobieranie kolejnych instrukcji, co dawało w efekcie

wydajność rzędu pojedynczej instrukcji na cykl zegara.

wydajność rzędu pojedynczej instrukcji na cykl zegara.

Mikroprocesory RISC -

Mikroprocesory RISC -

cechy

cechy

Zredukowana liczba rozkazów do niezbędnego

Zredukowana liczba rozkazów do niezbędnego

minimum. Ich liczba wynosi kilkadziesiąt, podczas gdy

minimum. Ich liczba wynosi kilkadziesiąt, podczas gdy

w procesorach CISC sięga setek. Upraszcza to znacznie

w procesorach CISC sięga setek. Upraszcza to znacznie

dekoder rozkazów.

dekoder rozkazów.

Redukcja trybów adresowania, dzięki czemu kody

Redukcja trybów adresowania, dzięki czemu kody

rozkazów są prostsze, bardziej zunifikowane, co

rozkazów są prostsze, bardziej zunifikowane, co

dodatkowo upraszcza wspomniany wcześniej dekoder

dodatkowo upraszcza wspomniany wcześniej dekoder

rozkazów. Ponadto wprowadzono tryb adresowania,

rozkazów. Ponadto wprowadzono tryb adresowania,

który ogranicza ilość przesłań - większość operacji

który ogranicza ilość przesłań - większość operacji

wykonuje się wg schematu:

wykonuje się wg schematu:

Mikroprocesory RISC -

Mikroprocesory RISC -

cechy

cechy

Ograniczenie komunikacji pomiędzy pamięcią, a

Ograniczenie komunikacji pomiędzy pamięcią, a

procesorem. Przede wszystkim do przesyłania danych

procesorem. Przede wszystkim do przesyłania danych

pomiędzy pamięcią, a rejestrami służą dedykowane

pomiędzy pamięcią, a rejestrami służą dedykowane

instrukcje, które zwykle nazywają się

instrukcje, które zwykle nazywają się

load

load

(załaduj z

(załaduj z

pamięci), oraz

pamięci), oraz

store

store

(zapisz do pamięci); pozostałe

(zapisz do pamięci); pozostałe

instrukcje mogą operować wyłącznie na rejestrach.

instrukcje mogą operować wyłącznie na rejestrach.

Schemat działania na liczbach znajdujących się w pamięci

Schemat działania na liczbach znajdujących się w pamięci

jest następujący: załaduj daną z pamięci do rejestru, na

jest następujący: załaduj daną z pamięci do rejestru, na

zawartości rejestru wykonaj działanie, przepisz wynik z

zawartości rejestru wykonaj działanie, przepisz wynik z

rejestru do pamięci.

rejestru do pamięci.

Zwiększenie liczby rejestrów (np. 32, 192, 256, podczas

Zwiększenie liczby rejestrów (np. 32, 192, 256, podczas

gdy np. w architekturze x86 jest zaledwie 8 rejestrów), co

gdy np. w architekturze x86 jest zaledwie 8 rejestrów), co

również ma wpływ na zmniejszenie liczby odwołań do

również ma wpływ na zmniejszenie liczby odwołań do

pamięci.

pamięci.

Mikroprocesory RISC -

Mikroprocesory RISC -

cechy

cechy

W procesorach RISC wprowadzono pojęcie potoku, czyli

W procesorach RISC wprowadzono pojęcie potoku, czyli

ścieżki przetwarzania instrukcji wewnątrz procesora.

ścieżki przetwarzania instrukcji wewnątrz procesora.

Wykonanie instrukcji podzielono na logiczne etapy, z

Wykonanie instrukcji podzielono na logiczne etapy, z

których każdy wykonywany był niezależnie na

których każdy wykonywany był niezależnie na

określonym stopniu potoku. Instrukcja po pobraniu z

określonym stopniu potoku. Instrukcja po pobraniu z

pamięci przemieszczana była w głąb potoku i

pamięci przemieszczana była w głąb potoku i

przechodziła przez jego stopnie. Po przejściu przez dany

przechodziła przez jego stopnie. Po przejściu przez dany

stopień potoku można było wykonywać w nim kolejną

stopień potoku można było wykonywać w nim kolejną

instrukcję. Najprostszy potok składa się z czterech

instrukcję. Najprostszy potok składa się z czterech

stopni: pobrania instrukcji, dekodowania, wykonania i

stopni: pobrania instrukcji, dekodowania, wykonania i

zapisu wyniku. Dzięki wprowadzeniu potoku możliwe

zapisu wyniku. Dzięki wprowadzeniu potoku możliwe

było równoczesne wykonanie i pobieranie kolejnych

było równoczesne wykonanie i pobieranie kolejnych

instrukcji, co dawało w efekcie wydajność rzędu

instrukcji, co dawało w efekcie wydajność rzędu

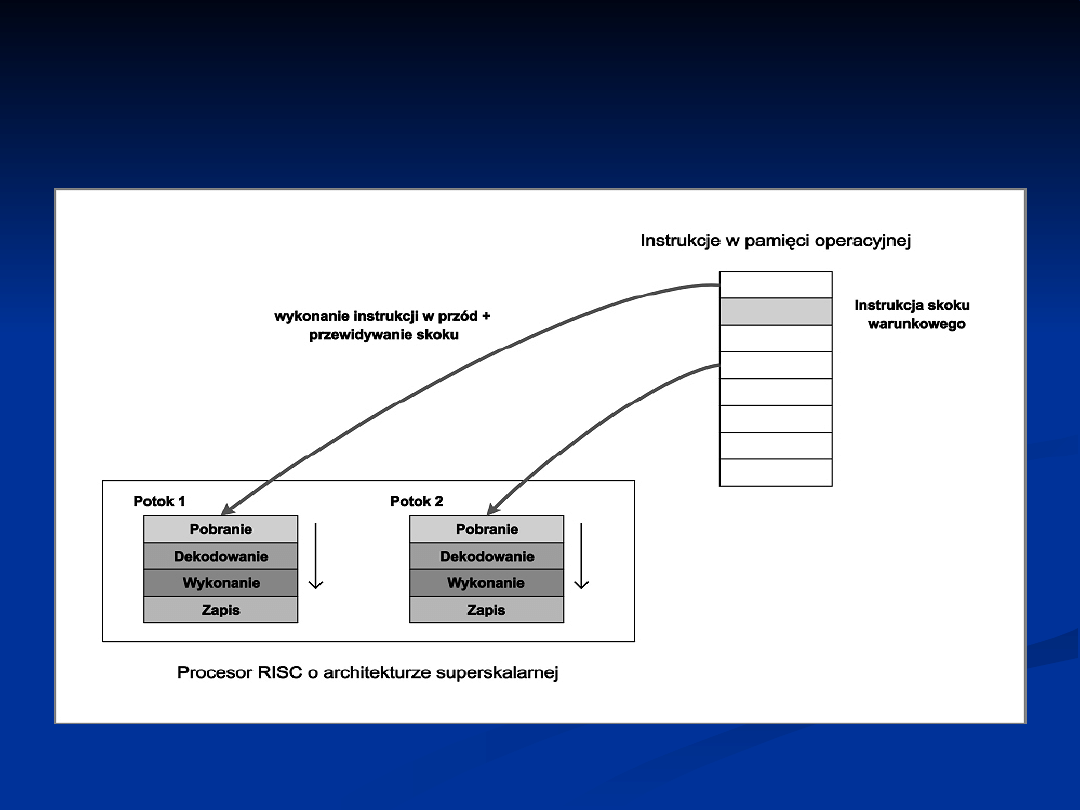

pojedynczej instrukcji na cykl zegara. Dodatkowo dzieki

pojedynczej instrukcji na cykl zegara. Dodatkowo dzieki

zaastosowaniu superskalarności uzyskano możliwość

zaastosowaniu superskalarności uzyskano możliwość

zrównoleglenia wykonywania rozkazów.

zrównoleglenia wykonywania rozkazów.

Mikroprocesory RISC

Mikroprocesory RISC

Różnica pomiędzy

Różnica pomiędzy

mikroprocesorami RISC i

mikroprocesorami RISC i

CISC

CISC

Mikroprocesory EPIC

Mikroprocesory EPIC

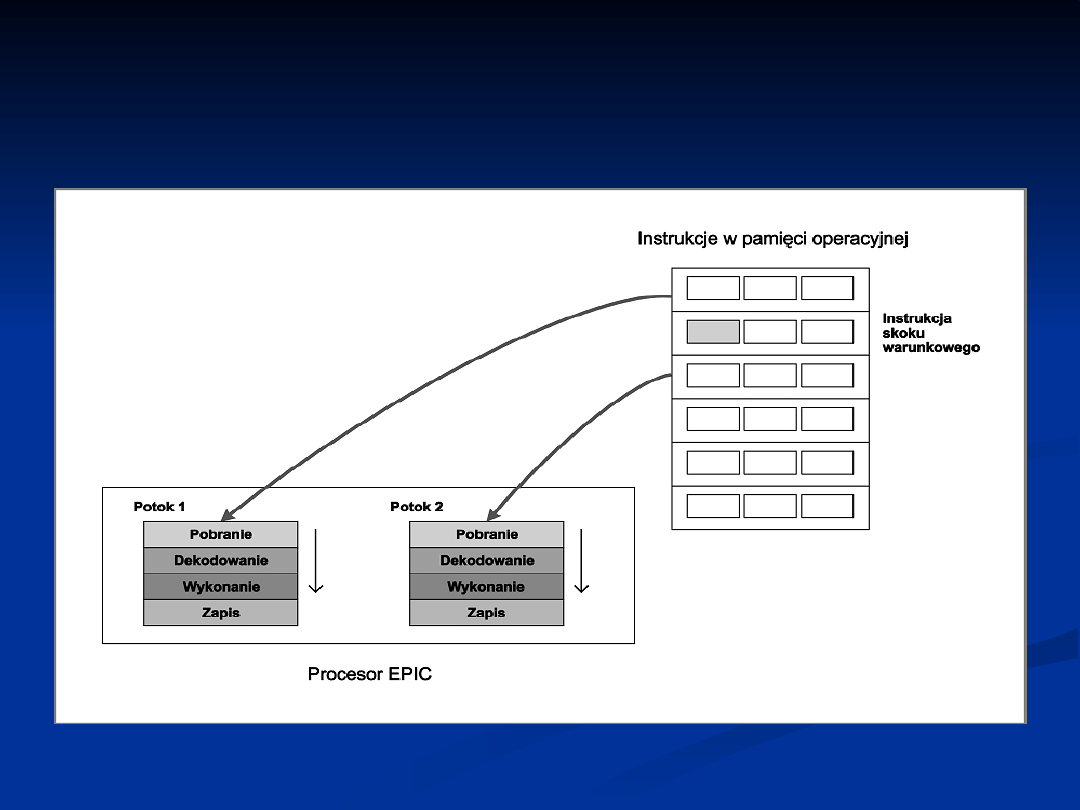

Model programowy EPIC wywodzi się ze starej

Model programowy EPIC wywodzi się ze starej

koncepcji o nazwie VLIW (Very Large Instruction Word),

koncepcji o nazwie VLIW (Very Large Instruction Word),

a polega na wykonywaniu prostych instrukcji

a polega na wykonywaniu prostych instrukcji

grupowanych w wielkie słowa rozkazowe. Instrukcje

grupowanych w wielkie słowa rozkazowe. Instrukcje

grupowane są w wielkie słowa rozkazowe na poziomie

grupowane są w wielkie słowa rozkazowe na poziomie

kompilacji, tzn. kompilator określa sposób równoległego

kompilacji, tzn. kompilator określa sposób równoległego

wykonania instrukcji. Procesor pobiera słowa i

wykonania instrukcji. Procesor pobiera słowa i

wykonuje wiele instrukcji równocześnie bez

wykonuje wiele instrukcji równocześnie bez

konieczności spekulowania i analizowania zależności

konieczności spekulowania i analizowania zależności

pomiędzy nimi. Dzięki prostej logice instrukcji może

pomiędzy nimi. Dzięki prostej logice instrukcji może

istnieć wiele jednostek wykonawczych, a procesor może

istnieć wiele jednostek wykonawczych, a procesor może

wykonywać wiele instrukcji tego samego typu w

wykonywać wiele instrukcji tego samego typu w

pojedynczym takcie zegara. Określoną liczbę

pojedynczym takcie zegara. Określoną liczbę

tranzystorów „zaoszczędzonych” wskutek uproszczenia

tranzystorów „zaoszczędzonych” wskutek uproszczenia

logiki układów przetwarzania można przeznaczyć na

logiki układów przetwarzania można przeznaczyć na

zwiększenie liczby rejestrów i jednostek wykonawczych.

zwiększenie liczby rejestrów i jednostek wykonawczych.

Mikroprocesory EPIC

Mikroprocesory EPIC

Mikroprocesory MISC

Mikroprocesory MISC

Jest to architektura procesora z bardzo małą liczbą

Jest to architektura procesora z bardzo małą liczbą

podstawowych operacji, które są zgodne z opcode.

podstawowych operacji, które są zgodne z opcode.

Takie zestawy instrukcji są częściej oparte na stosie,

Takie zestawy instrukcji są częściej oparte na stosie,

niż na rejestrach, żeby zmniejszyć rozmiar

niż na rejestrach, żeby zmniejszyć rozmiar

określników operacji. Architektura maszyny stosowej

określników operacji. Architektura maszyny stosowej

jest właściwie prostsza od kiedy wszystkie instrukcje

jest właściwie prostsza od kiedy wszystkie instrukcje

operują na szczycie większości zapisów w stosie.

operują na szczycie większości zapisów w stosie.

Rezultatem tego jest mniejszy zestaw instrukcji,

Rezultatem tego jest mniejszy zestaw instrukcji,

mniejsza i szybsza jednostka do dekodowania

mniejsza i szybsza jednostka do dekodowania

instrukcji i szybsze wykonanie pojedynczych

instrukcji i szybsze wykonanie pojedynczych

instrukcji. Wadą jest to, że instrukcje mają skłonność

instrukcji. Wadą jest to, że instrukcje mają skłonność

do posiadania większej ilości uzależnień

do posiadania większej ilości uzależnień

sekwencyjnych, przez to zmniejszając ilość instrukcji,

sekwencyjnych, przez to zmniejszając ilość instrukcji,

które mogą być wykonywane jednocześnie.

które mogą być wykonywane jednocześnie.

Mikroprocesory ZISC

Mikroprocesory ZISC

Jest to technologia oparta na pomysłach

Jest to technologia oparta na pomysłach

wziętych z sztucznej sieci nerwowej. Pierwsza

wziętych z sztucznej sieci nerwowej. Pierwsza

generacja chipu ZISC zawiera 36 niezależnych

generacja chipu ZISC zawiera 36 niezależnych

komórek, które mogą być uważane za neurony

komórek, które mogą być uważane za neurony

lub równoległe procesory. Każda z nich może

lub równoległe procesory. Każda z nich może

porównać wektor wejściowy, którego rozmiar

porównać wektor wejściowy, którego rozmiar

może osiągnąć do 64 bajtów z podobnym

może osiągnąć do 64 bajtów z podobnym

wektorem przechowywanym w komórkach

wektorem przechowywanym w komórkach

pamięci. Jeśli wektor wejściowy odpowiada

pamięci. Jeśli wektor wejściowy odpowiada

wektorowi w komórce pamięci to komórka ta

wektorowi w komórce pamięci to komórka ta

„wypala”. Sygnał wyjściowy zawiera komórki,

„wypala”. Sygnał wyjściowy zawiera komórki,

która miała dopasowanie, jak również

która miała dopasowanie, jak również

znacznik który mówi, że nie wystąpiło

znacznik który mówi, że nie wystąpiło

dopasowanie.

dopasowanie.

Mikroprocesory ZISC

Mikroprocesory ZISC

Równoległość jest kluczem do szybkości systemów

Równoległość jest kluczem do szybkości systemów

ZISC, które eliminują krok seryjnego ładowania i

ZISC, które eliminują krok seryjnego ładowania i

porównywania wzorca dla każdej lokalizacji. Kolejnym

porównywania wzorca dla każdej lokalizacji. Kolejnym

kluczowym czynnikiem ZISC jest skalowalność. Sieć

kluczowym czynnikiem ZISC jest skalowalność. Sieć

ZISC może być rozszerzona przez dodanie większej

ZISC może być rozszerzona przez dodanie większej

ilości urządzeń ZISC bez obniżenia szybkości

ilości urządzeń ZISC bez obniżenia szybkości

rozpoznawania – sieć z ilością 10,000 lub więcej

rozpoznawania – sieć z ilością 10,000 lub więcej

komórek może stać się powszechna. Dzisiejsze chipy

komórek może stać się powszechna. Dzisiejsze chipy

ZISC zawierają 78 neuronów na chip I mogą znaleźć

ZISC zawierają 78 neuronów na chip I mogą znaleźć

dopasowanie wśród 1,000,000 wzorców zaledwie w

dopasowanie wśród 1,000,000 wzorców zaledwie w

jedną sekundę operując z prędkością przynajmniej

jedną sekundę operując z prędkością przynajmniej

50Mhz. Następna generacja może zawierać nawet

50Mhz. Następna generacja może zawierać nawet

1,000 neuronów lub więcej w jednym chipie.

1,000 neuronów lub więcej w jednym chipie.

Praktyczne użytkowanie technologii ZISC jest skupione

Praktyczne użytkowanie technologii ZISC jest skupione

na rozpoznawaniu wzorców, ochronie, wyszukiwaniu

na rozpoznawaniu wzorców, ochronie, wyszukiwaniu

informacji (data mining) i innych podobnych zadaniach.

informacji (data mining) i innych podobnych zadaniach.

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

Wyszukiwarka

Podobne podstrony:

13 Rodzaje mikroprocesorów

Najbardziej charakterystyczne odchylenia od stanu prawidłowego w badaniu

Opis zawodu Charakteryzator, Opis-stanowiska-pracy-DOC

Rodzaje niepełnosprawności opis

Polski, DO DRUKOWANIA, KSIĘGA RODZAJU - zawiera opis kolejnych czynności Boga - stwórcy

13. Rodzaje ciast cukierniczych, licencjat(1)

Balneoterapia ZABIEGI WODNE, Balneoterapia jest grupą zabiegów, jedną z najbardziej charakterystyczn

Najbardziej charakterystyczni bohaterowie polskiego kina, znalezione, filmoznawstwo, kino polskie po

Rodzaje papierw wartociowych i ich charakterystyka, Materiały AGH- zarządzanie finansami, finanse pr

13. Rodzaje map geologicznych stosowanych w Polsce(1), Budownictwo

hs, hs 7 Durkheim III, W religii tkwią najbardziej charakterystyczne elementy życia religijnego

Rachunkowość - wykłady - 13, Rodzaje dokumentów:

13 karty umiej tn?chy charakteru

Najbardziej charakterystyczne odchylenia od stanu prawidłowego w badaniu

rodzaje cer opis

Okres poniemowlęcy obejmuje dzieci od 13 do 36 miesiąca życia i charakteryzuje się wolniejszym w por

charakterystyka i opis problemu jakosciowego, Socjologia

więcej podobnych podstron