Opracowanie TC 2008

Autorzy:

Wojciech Abratkiewicz

Michał Antolik

Paweł Gawkowski

Piotr Pytko

©

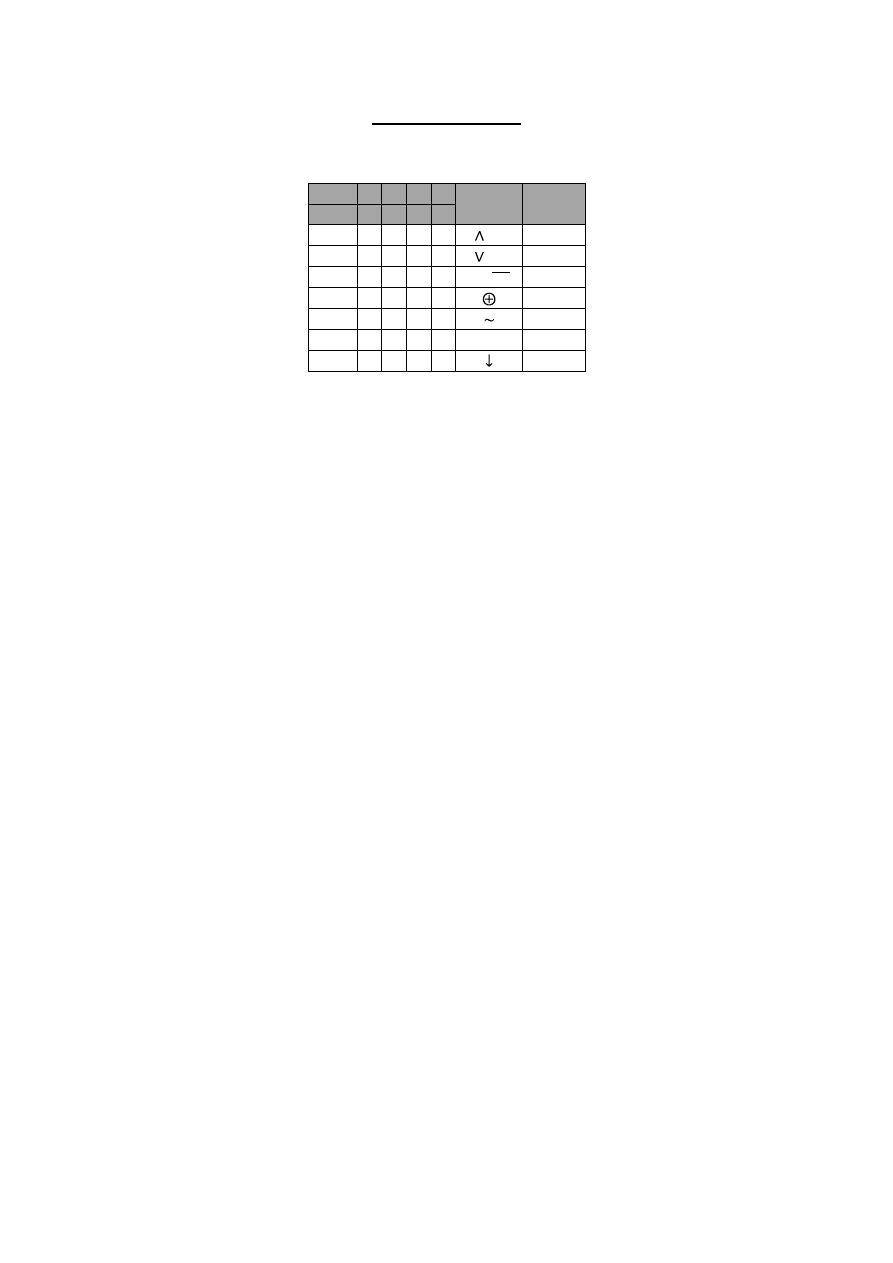

Funkcje podstawowe:

Są to funkcje, które posiadają nazwy operatorów. W sensie algebry Boole’a są to: OR, AND, NOT

x

1

0 1 0 1

Symbol Nazwa

x

2

0 0 1 1

f

1

0 0 0 1

•

AND

f

2

0 1 1 1

+

OR

f

3

(x

1

) 1 0 1 0

!

NOT

f

4

0 1 1 0

XOR

f

5

1 0 0 1

XNOR

f

6

1 1 1 0

|

NAND

f

7

1 0 0 0

NOR

System funkcjonalnie pełny – zbiór operatorów pozwalający na zapisanie dowolnej funkcji

boolowskiej w postaci wyrażenia

Pojęcia boolowskie

Literał – pojedynczy symbol zmiennej (zanegowanej lub nie), np. x lub ~x

Term iloczynowy – iloczyn literałów, w którym zmienne nie powtarzają się

Term sumacyjny – suma literałów, w której żadna zmienna nie powtarza się

Iloczyn pełny n zmiennych (minterm) – term iloczynowy zawierający n literałów

Suma pełna n zmiennych (max term) – term sumacyjny zawierający n literałów

Alfabety itp.

Wektor wyjściowy/słowo wyjściowe/stan wyjściowy/odpowiedź układu:

Kombinacja wartości wszystkich sygnałów wyjściowych - Y= y1,y2,…,ym)

Język wyjściowy = alfabet wyjściowy:

Zbiór wszystkich wektorów wyjściowych (wszystkie kombinacje wartości wyjśd, które mogą wystąpid).

Dla m wejśd istnieje max. 2^m kombinacji. W rzeczywistych układach często nie wykorzystuje się

wszystkich kombinacji.

Układ kombinacyjny:

Układ w którym stan każdego z wyjśd zależy od wartości wejśd . Można powiedzied, że stan każdego

wyjścia jest funkcją wszystkich wejśd. W konsekwencji słowo wyjściowe jest jednoznacznie określone

przez słowo wejściowe.

Liczba możliwych funkcji przełączających

Stan każdego z wyjśd jest pewną funkcją wszystkich wejśd (dla każdego z wyjśd funkcja ta może byd

różna):

Funkcję

nazywamy przełączającą

Wyrażenie boolowskie/funkcja boolowska/wielomian boolowski:

Wyrażenie utworzone ze zmiennych boolowskich (takich, które mogą przyjmowad wartości 0 i 1),

stałych 0 i 1 na których wykonujemy operacje boolowskie (+, *, ~)

Dualnośd wyrażeo boolowskich:

Każde wyrażenie boolowskie można przekształcid na dualne (są one równoważne) poprzez zamianę

miejsc operatorów +,* wartości 0,1 oraz zanegowanie zmiennych niezanegowanych i odwrotnie.

Mówi o tym tzw. Wzór Shannona (uogólnione prawa De Morgana)

~f(x

1

,f

2

,…,x

n

,+,*) = f(~x

1

,~x

2

,…,~x

n

,*,+)

Np.:

f(X) = x

1

~x

2

+ ~x

1

x

3

+ x

1

x

2

x

3

~f(X) = (~x

1

+x

2

) * (x

1

+~x

3

) * (~x

1

+~x

2

+~x

3

)

Liczba funkcji przełączających:

moc (Y^X) = moc (B^(B^n) = 2^(2^n)

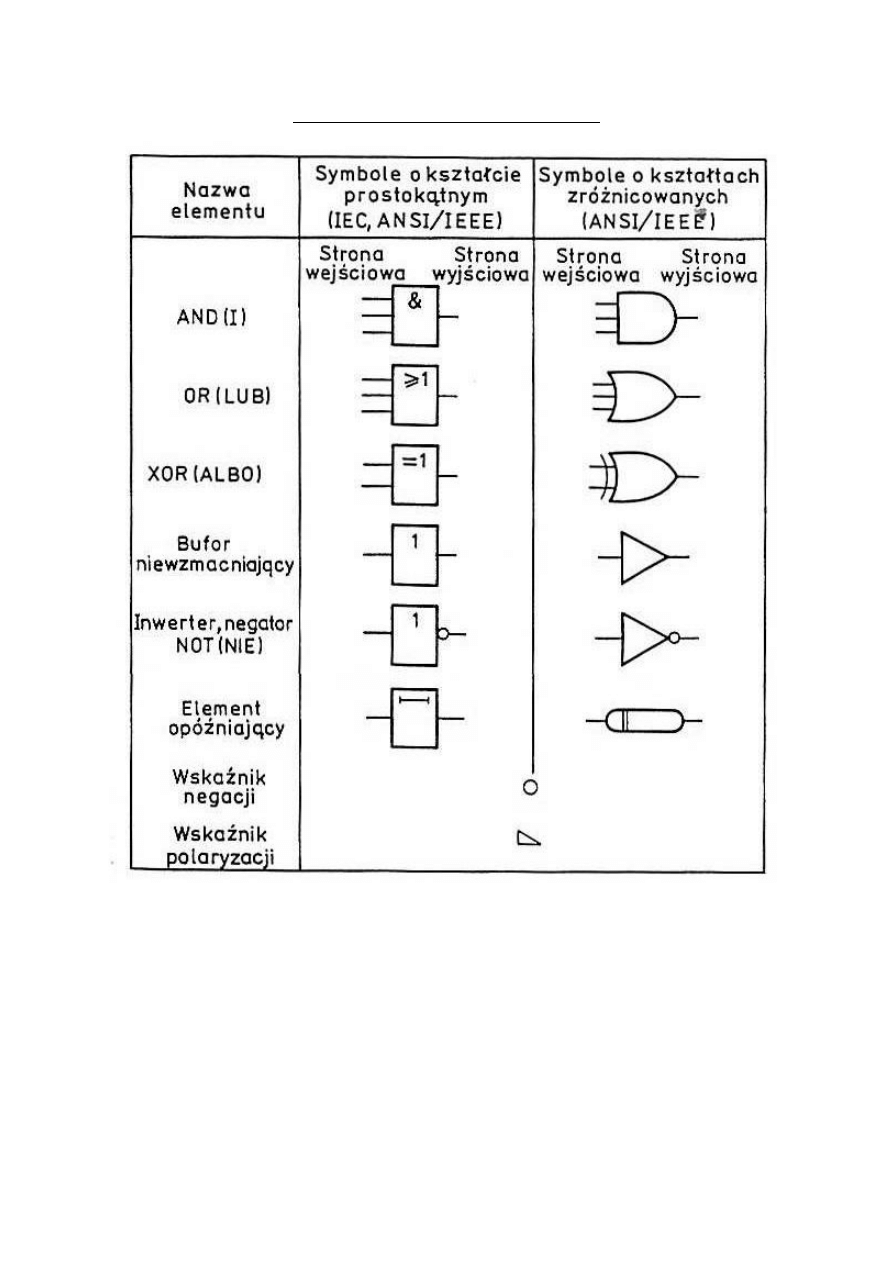

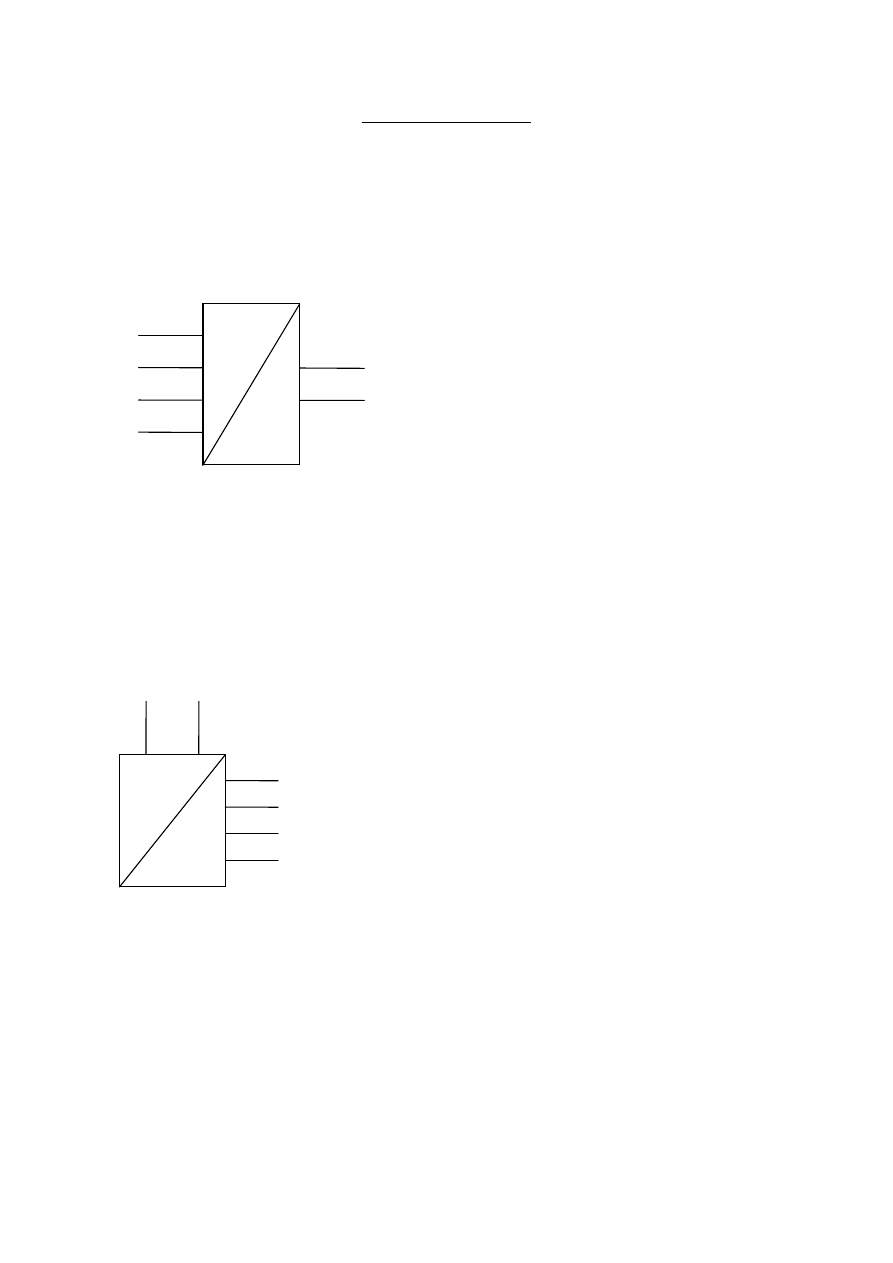

Symbole podstawowych układów kombinacyjnych

Parametry statyczne i dynamiczne bramek

1. Parametry bramek logicznych

a) statyczne

- napięcie zasilania U

CC

- napięcie wejściowe w stanie wysokim U

IH

- napięcie wejściowe w stanie niskim U

IL

- napięcie wyjściowe w stanie wysokim U

OH

- napięcie wyjściowe w stanie niskim U

OL

// te same z prądem, napięcie zamieniam na prąd a U na I

- prąd wyjściowy zwarcia I

OS

- prąd zasilania w stanie 1 na wyjściu I

CCH

- prąd zasilania w stanie 0 na wyjściu I

CCL

- straty mocy w bramce P

S

b) dynamiczne

- Średni czas propagacji – czas potrzebny na to, by zmiana sygnału na wejściu z 0 na 1

lub odwrotnie spowodowała stosowną zmianę na wyjściu

- Obciążalnośd – granica obciążenia bramki, czyli maksymalna ilośd bramek, jakie

dana bramka będzie w stanie sterowad podobne do siebie bramki. W związku z tym

definiuje się obciążenie jednostkowe oznaczane UL – Unity Load lub fan-in, i mówi

się, że obciążalnośdbramku wynosi np. 10 UL.

- Związek pomiędzy poborem mocy przez bramkę a częstotliwością przełączania –

ogólnie można stwierdzid, że jeśli bramka jest przełączana z częstotliwością f, to moc

pobierana da się opisad zależnością:

Pd=(Cl+Cpd)(Vdd-Vss)^2*f – Cl – pojemnośd obciążająca układ, Cpd – ekwiwalentna

pojemnośd związana z poborem prądu z zasilania w fazie przełączania bramki, Vss i

Vdd napięcia komplementarnych tranzystorów

- Średni pobór mocy,

- Zakres częstotliwości pracy- częstotliwośd pracy danego układu logicznego, kiedyś

układy ECL pracowały z częstotliwością 100 MHz, teraz PECL pracują z częstotliwością

3-4GHz i mają czasu propagacji rzędu 200-300ps

- Margines zakłóceo - maksymalne zewnętrzne napięcie, które nie spowoduje

niepożądanych zmian na wyjściu

- Moc rozpraszania - moc pobierana ze źródła i tracona przez bramkę

- Poziomy logiczne - wartości napięd odpowiadające stanom logicznym

- Związek między poborem mocy a częstotliwością przełączania - jak zmiana

częstotliwości wpływa na pobór mocy

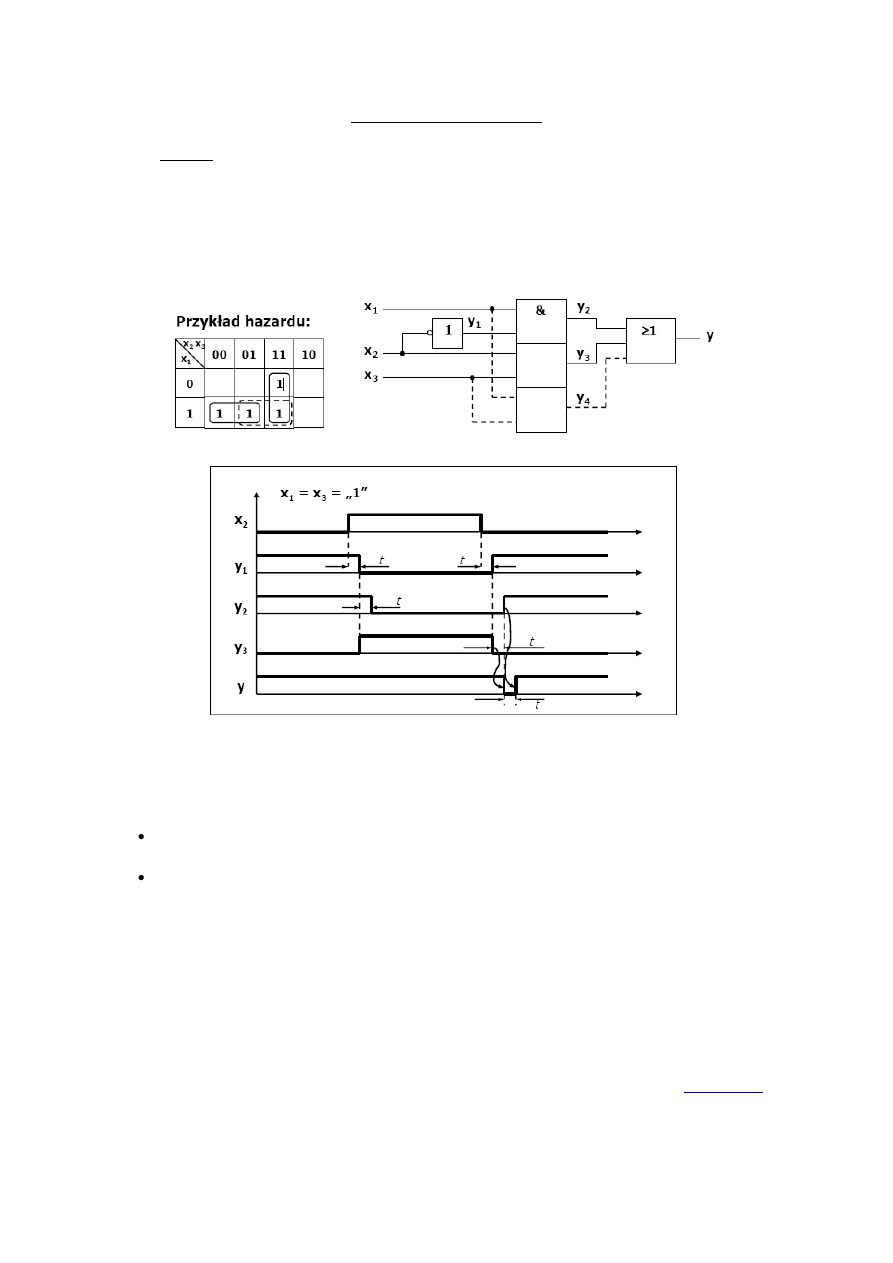

Hazard statyczny i dynamiczny

Hazard – zakłócenia szpilkowe występujące na wyjściu układu kombinacyjnego

podczas procesow przejściowych. Zjawisko występuje wówczas, gdy co najmniej

jeden sygnał jest przesyłany dwoma różnymi drogami prowadzącymi do jednej

bramki. Wyrożniamy hazard statyczny i dynamiczny.

Hazard statyczny – chwilowa zmiana stanu wyjściowego układu występującą przy zmianie

stanu jego wejścia wtedy, gdy wyjście powinno zostać niezmienione. Powstaje na skutek

nieidealnych właściwości przełączających. Dzielimy na:

hazard jedynki – chwilowa zmiana wyjścia 1-0-1 wtedy, gdy wyjście to powinno

zostać niezmienione w stanie 1

hazard zera – chwilowa zmiana wyjścia 0-1-0 wtedy, gdy wyjście to powinno pozostać

niezmienione w stanie 0

Hazard dynamiczny – kilkukrotna zmiana stanu wyjścia przy zmianie stanu wejścia wtedy,

gdy wyjście to powinno zmieniać swój stan tylko jeden raz i w nim pozostać np. przy zmianie

1-0 następuje zmiana 1-0-1-0, lub przy zmianie 0-1 następuje zmiana 0-1-0-1. Powstaje na

skutek nieidealnych właściwości transmisyjnych.

Hazard statyczny można wyeliminować już na etapie projektowanie układu, dzieje się to

kosztem skomplikowania układu. Eliminacja hazardu statycznego powoduje równoczesną

eliminację hazardu dynamicznego. Jedną z metod eliminacji jest wprowadzenie

układu. Likwidacja hazardu może polegać również na wprowadzeniu do układu dodatkowej

grupy (oczywiście nie będzie to już wówczas postać minimalna takiej funkcji), zawierającej

elementy sąsiadujących ze sobą grup.

~S

~R

J

C

K

Q

~Q

Przerzutniki D i JK

Przerzutnik (z ang. flip-flop) jest to podstawowy element pamiętający każdego układu

cyfrowego, przeznaczonego do przechowywania i ewentualnego przetwarzania informacji.

Przerzutnik współtworzy najniższe piętro struktury układu i zdolny jest do zapamiętania

jednego bitu informacji. Grupa czterech lub ośmiu połączonych ze sobą przerzutników

tworzy następne, wyższe piętro - tzw. rejestr, zdolny już do pamiętania jednego bajtu

informacji.

Parametry dynamiczne

Czas narastania

Czas opadania

Czas propagacji

o z L do H

o z H do L

minimalny czas trwania aktywnego poziomu sygnału

Minimalny czas trwania poziomu poprzedzającego i następującego po aktywnym zboczu

sygnału

Maksymalny czas trwania zbocza wyzwalającego

Czas ustalenia

Czas utrzymania

Maksymalna częstotliwość przebiegu zegarowego

Czas martwy

Parametry statyczne

Napięcia poziomów logicznych (na wyjściu i wejściu)

o

dla sygnału L

o

dla sygnału H

Marginesy zakłóceń statycznych dla stanów logicznych

Wydajności prądowe stopni wejściowych i wyjściowych dla stanów L i H

Przerzutnik typu D:

Przerzutnik typu JK:

J K Q(n) Q(n+1)

0 X

0

0

1 X

0

1

X 1

1

0

X 0

1

1

D Q

C

~Q

D

Q

n

0

0

1

1

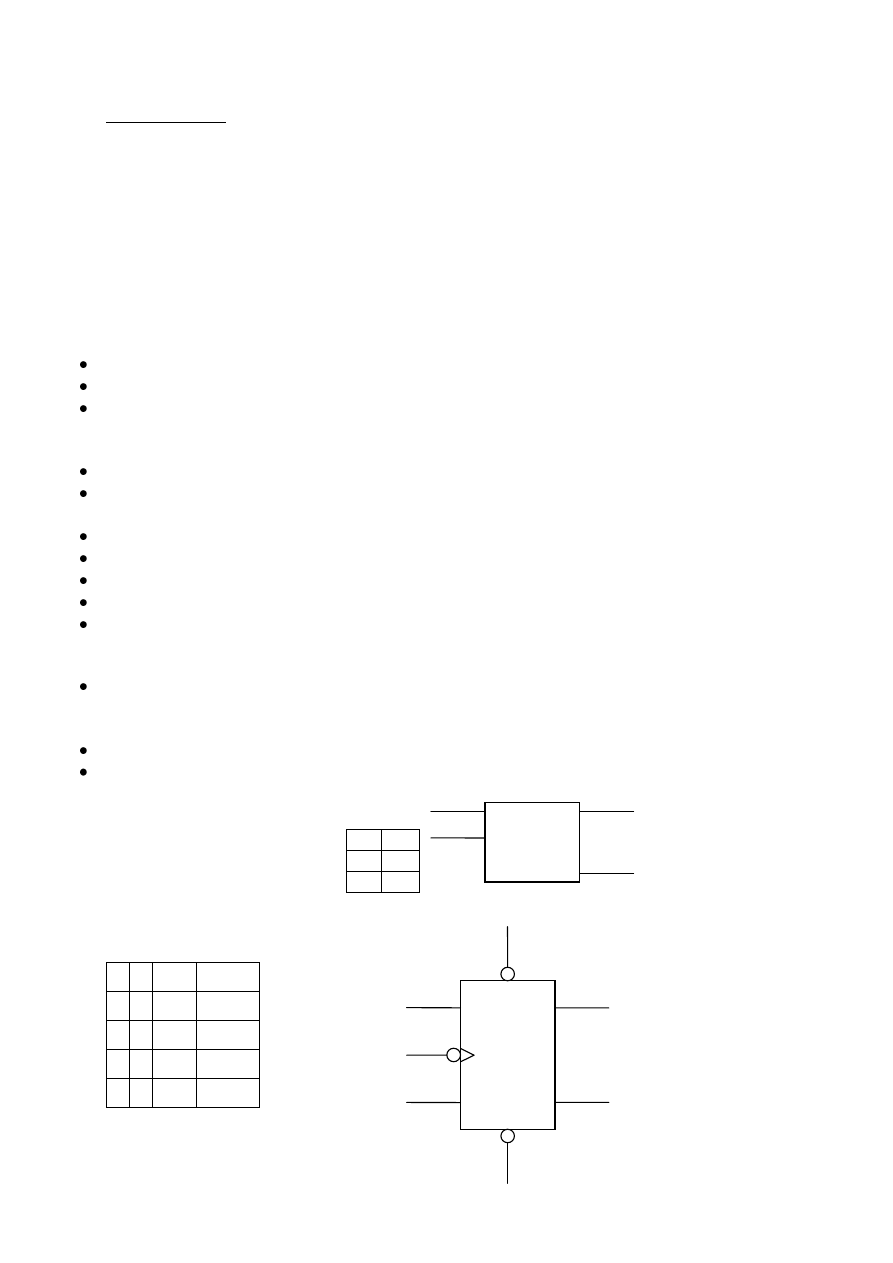

Koder, dekoder, transkoder

Koder

Definicja: Układ kombinacyjny posiadający n wyjśd i m<=2

n

wejśd. Służy do zamiany kodu „1

z m” na kod o długości n, tak aby każde słowo tworzyło niepowtarzalny kod wyjściowy.

Schemat blokowy:

Dekoder

Definicja: Układ kombinacyjny posiadający n wejśd i m<=2

n

wyjśd. Służy do zamiany kodu o

długości n na kod „1 z m” (odwrotnie do kodera).

Schemat blokowy:

Transkoder to układ cyfrowy o n wejściach oraz k wyjściach (k=2n). Jego działanie polega na

zamianie dowolnego kodu cyfrowego (poza kodem 1zN) na inny, dowolny kod cyfrowy

(również z wyjątkiem kodu 1zN). Typowym przykładem takiego układu jest układ

zamieniający naturalny kod binarny na kod wyświetlacza siedmiosegmentowego.

S1 S0

D0

D1

D2

D3

I3

I2

I1

I0

S1

S0

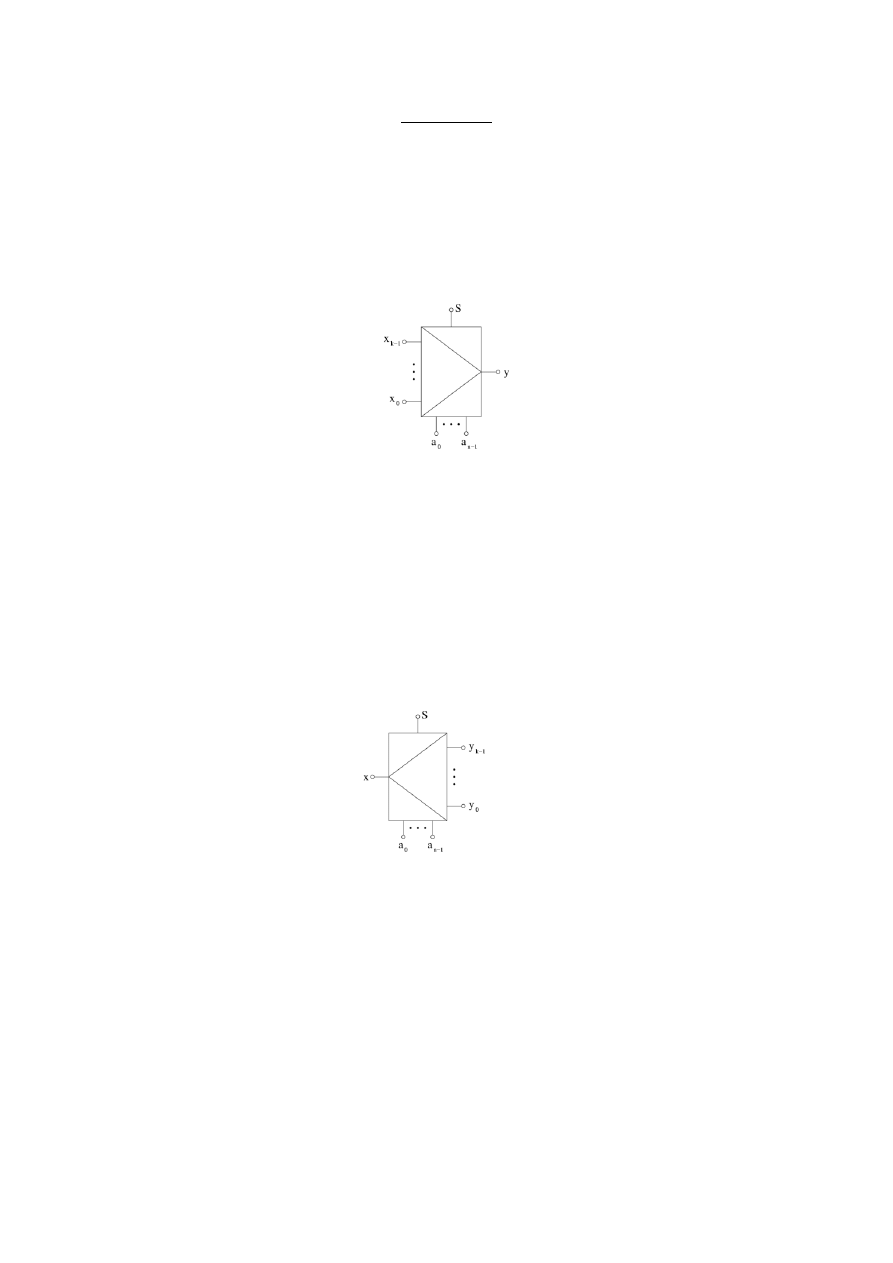

MUX i DMUX

Multiplekser jest układem przełączającym, posiadającym k wejść informacyjnych (zwanych

też wejściami danych), n wejść adresowych (sterujących) (zazwyczaj k=2n) i jedno wyjście y.

Posiada też wejście sterujące działaniem układu oznaczane S (ang. strobe) lub e (ang. enable).

Jego działanie polega na połączeniu jednego z wejść x

i

z wyjściem y. Numer wejścia jest

określany przez podanie jego numeru na linie adresowe A. Jeśli na wejście strobujące

(blokujące) S podane zostanie logiczne zero, to wyjście y przyjmuje określony stan logiczny

(zazwyczaj zero), niezależny od stanu wejść X i A.

Demultiplekser jest układem posiadającym jedno wejście x, n wejść adresowych, oraz k

wyjść (zazwyczaj k=2

n

). Jego działanie polega na połączeniu wejścia x do jednego z wyjść y

i

.

Numer wyjścia jest określany przez podanie jego numeru na linie adresowe a

0

... a

n-1

. Na

pozostałych wyjściach panuje stan zera logicznego. W praktyce spotykane są jedynie

demultipleksery w wyjściach zanegowanych czyli na wybranym wyjściu jest stan a na

wszystkich pozostałych 1 logiczna. Jeśli na wejście strobujące (blokujące) S (ang. strobe)

podane zostanie logiczne zero, to wyjścia y

i

przyjmują określony stan logiczny (zwykle zero),

niezależny ani od stanu wejścia x, ani wejść adresowych.

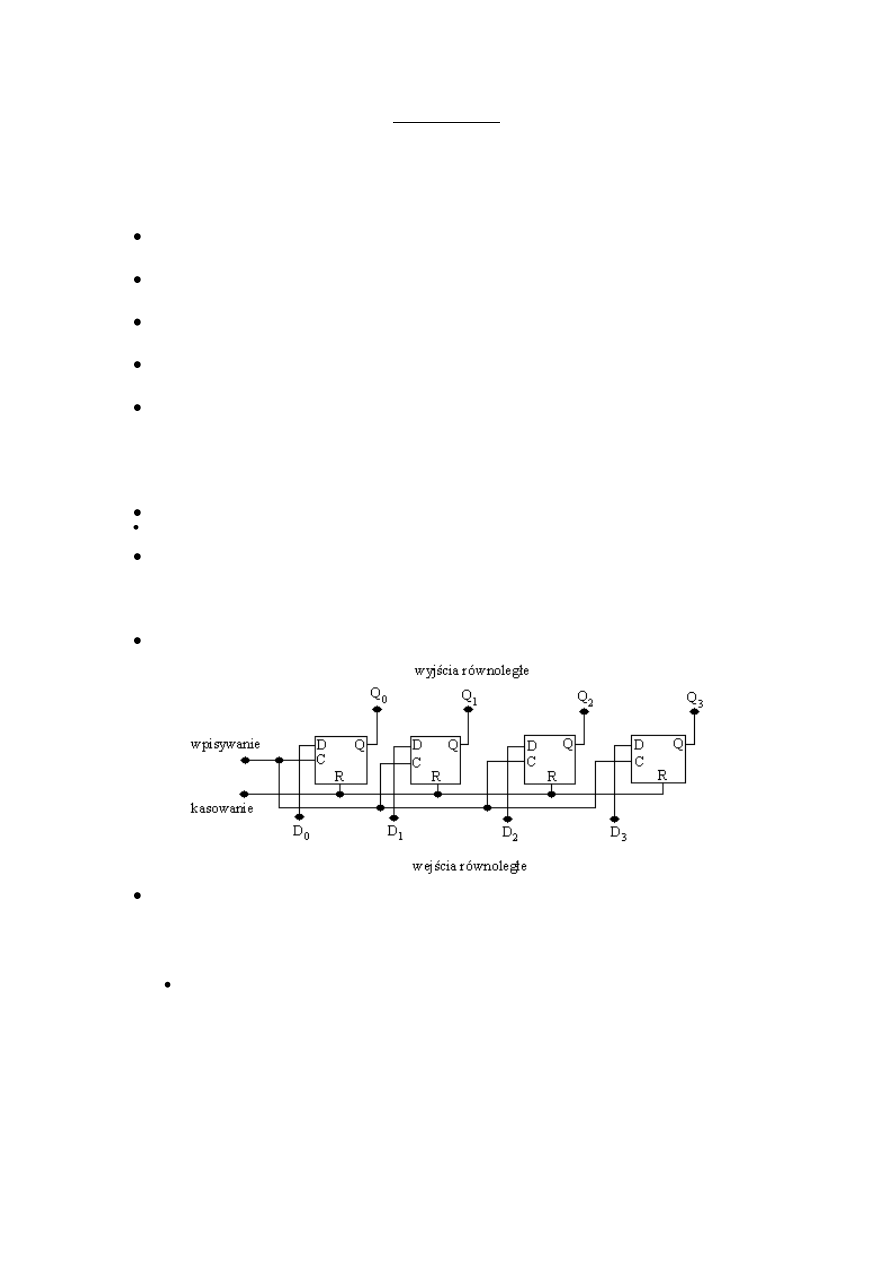

Rejestry i liczniki

Rejestrem nazywamy układ służący do przechowywania informacji w postaci bitów. Na

każdej pozycji rejestru przechowywany jest jeden bit informacji.

Ze względu na sposób wprowadzania i wyprowadzania informacji dzielimy rejestry na :

Szeregowe - umożliwiające szeregowe wprowadzenie i wyprowadzenie danych (tzn.

bit po bicie), są to tak zwane rejestry SISO (Serial In Serial Out)

Równoległe - umożliwiające równoległe wprowadzenie i wyprowadzenie informacji

jednocześnie do wszystkich pozycji rejestru, PIPO (Parallel In Parallel Out)

Szeregowo-równoległe - umożliwiające szeregowe wprowadzenie i równoległe

wyprowadzenie informacji, SIPO (Serial In Parallel Out)

Równoległo–szeregowe - umożliwiające równolegle wprowadzenie i szeregowe

wyprowadzenie informacji, PISO (Parallel In Serial Out)

uniwersalne, umożliwiające wprowadzenie i wyprowadzenie informacji zarówno w

sposób równoległy, jak i szeregowy.

Rejestry można podzielić także na asynchroniczne i synchroniczne. Jednakże najczęściej

stosowane są rejestry synchroniczne.

Parametrami charakteryzującymi rejestr są:

Długość rejestru, równa liczbie przerzutników N

Pojemność rejestru, równa 2

N

Szybkość rejestru; w przypadku rejestru równoległego będzie to czas wprowadzania

lub wyprowadzania informacji, natomiast w przypadku rejestru szeregowego

maksymalna możliwa częstotliwość impulsów przesuwających, przy której nie

następuje zniekształcenie informacji.

Rejestr równoległy 4 - bitowy

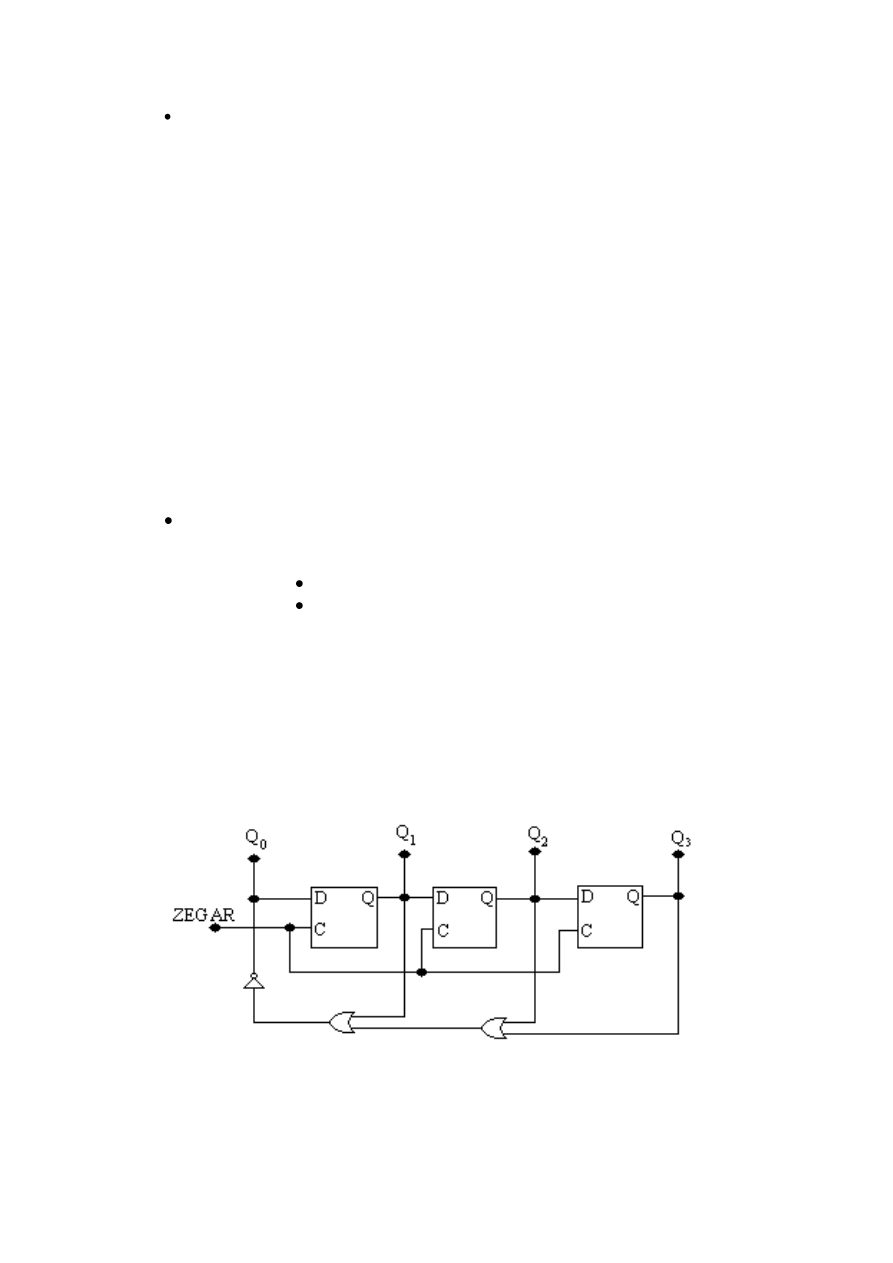

Rejestr przesuwający z przerzutników JK

Definicja

Układ zliczający występowanie sygnału zegarowego.

Parametry

o Opisowe

Stan licznika

Stan początkowy

Cykl

Pojemność

Kierunek zliczania

o Statyczne

Maksymalny prąd wejściowy

Maksymalne napięcie wejściowe

Napięcia poziomów logicznych na wyjściu i wejściu

Moc strat

Minimalne napięcie wejściowe

Wydajności prądowe stopni wejściowych i wyjściowych

Marginesy zakłóceń statycznych dla stanów logicznych

o Dynamiczne

Czas narastania

Czas opadania

Czasy propagacji z L do H i z H do L

Czas ustalenia

Czas utrzymania

Maksymalna częstotliwość przebiegu zegarowego

Klasyfikacja

o I rodzaj klasyfikacji:

jednokierunkowe

Zliczające w tył

Zliczające w przód

Dwukierunkowe (rewersyjne, można przestawiać)

o II rodzaj klasyfikacji:

Szeregowe (asynchroniczne)

Równoległe (synchroniczne)

Licznik pierścieniowy samokorygujący

Układy arytmetyczne

Półsumator jest układem kombinacyjnym o dwóch wejściach A i B oraz dwóch wyjściach : S - sumy i C -

przeniesienia. Z tabelki wynika że:

S = AxorB oraz C = AB

Sumator

Ze względu na sposób wykonywania działao na kolejnych pozycjach

liczb wielocyfrowych stosowane są :

a) sumatory równoległe

b) sumatory szeregowe

Wśród sumatorów równoległych można wyróżnid :

a) sumatory z przeniesieniami równoległymi

b) sumatory z przeniesieniami szeregowymi

Sumator szeregowy

W sumatorze szeregowym dodawane liczby są wprowadzane do sumatora bit po bicie,

poczynając od bitu najmniej znaczącego. W układzie takim występuje koniecznośd

odróżnienia jednakowych stanów wejśd. Jest to typowy układ synchroniczny.

Sumator równoległy

Sumator równoległy z przeniesieniami szeregowymi, zwany inaczej sumatorem

kaskadowym jest najprostszym typem sumatora równoległego.

Dla realizacji dodawania liczb dodatnich sumator pozycji najmniej znaczącej może

byd zastąpiony półsumatorem

Sposoby reprezentacji układów sekwencyjnych:

Opis słowny – opisanie zasady działania układu, jakie spełnia funkcje, dla jakich wartości na wejściu

jakie wartości są przypisywane na wyjściu układu

Wykres czasowy – wykres (zero-jedynkowy) ilustrujący zależnośd wyjścia układu od stanów wejśd

Opis pełny – wymienienie wszystkich 5ciu elementów opisujących <A,X,Y,δ,λ> (grafy przejśd i wyjśd

oraz tablice przejśd i wyjśd)

U

kłady asynchroniczne

• Brak wejścia sterującego (synchronizującego, zegarowego)

• Natychmiastowa reakcja na zmiany stanu X (zmiana stanu A lub Y jedynie po zmianie stanu

X)

• Każdy stan A

t

+ ustala się po niezerowym opoźnieniu (czas propagacji)

• Opoźnienia ti sygnałow Qi (i=1, 2, ..., k) są niejednakowe

• Zmiana stanu X -> 1 lub więcej stanow niestabilnych, po ktorych powinien wystąpić stan

stabilny

Układy asynchroniczne statyczne – reakcja na stan wejść

Układy asynchroniczne dynamiczne – reakcja na zmianę stanu

Układy synchroniczne:

• Zmaiany stanu X tylko w określonych, dyskretnych chwilach czasu określanych przez

zewnętrzny sygnał okresowy niewchodzący do wektora X (sygnał sterujący, synchronizujący,

zegarowy, taktujący)

• Kolejny stan może być oznaczony liczbą naturalną (zamiast t)

A

t+1

= d(A

t

, X

t

); A

t

= d(A

t-1

, X

t-1

); A’= d(A, X)

• Brak stanow niestabilnych: T

m

= < T

0

Zamiast oznaczenia t używamy umownego n dla chwil t

n

, t

n+1

-> A

n

, A

n+1

Układy synchroniczne autonomiczne – brak wejść X

Automaty

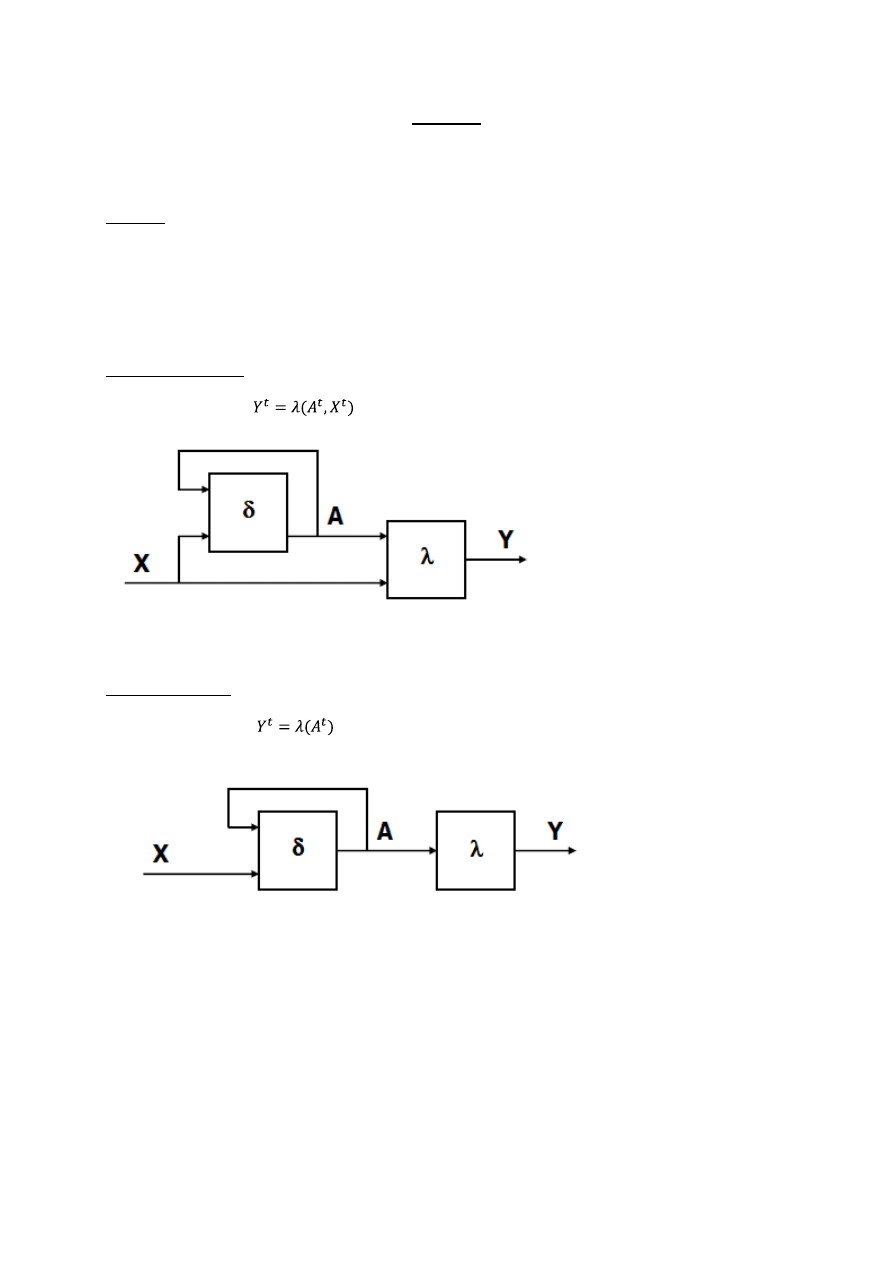

Jako δ oznaczamy funkcję przejśd (stany opóźnione o czas τ), natomiast jako λ oznaczamy funkcję

wyjśd (stany na faktycznym wyjściu układu).

Automat – model matematyczny układu sekwencyjnego opisywany przez <A,X,Y,δ,λ>

A – wektor stanów wewnętrznych w odniesieniu do stanów elementów pamięciowych

X – wektor danych (chyba)

Automat Mealy’ego:

Określony funkcją:

Automat Moore’a:

Określony funkcją:

Definicje automatów

Automat skooczony – automat, w którym zbiory A,X,Y są skooczone

Automat deterministyczny – jeśli λ i δ są funkcjami

Automat zupełny – jeśli dla wszystkich par (A,X) ze zbioru (A×X) istnieją określone wartości funkcji λ i

δ

Automat niezupełny – jeśli istnieje chodby jedna para, która nie ma określonej wartości funkcji λ i δ

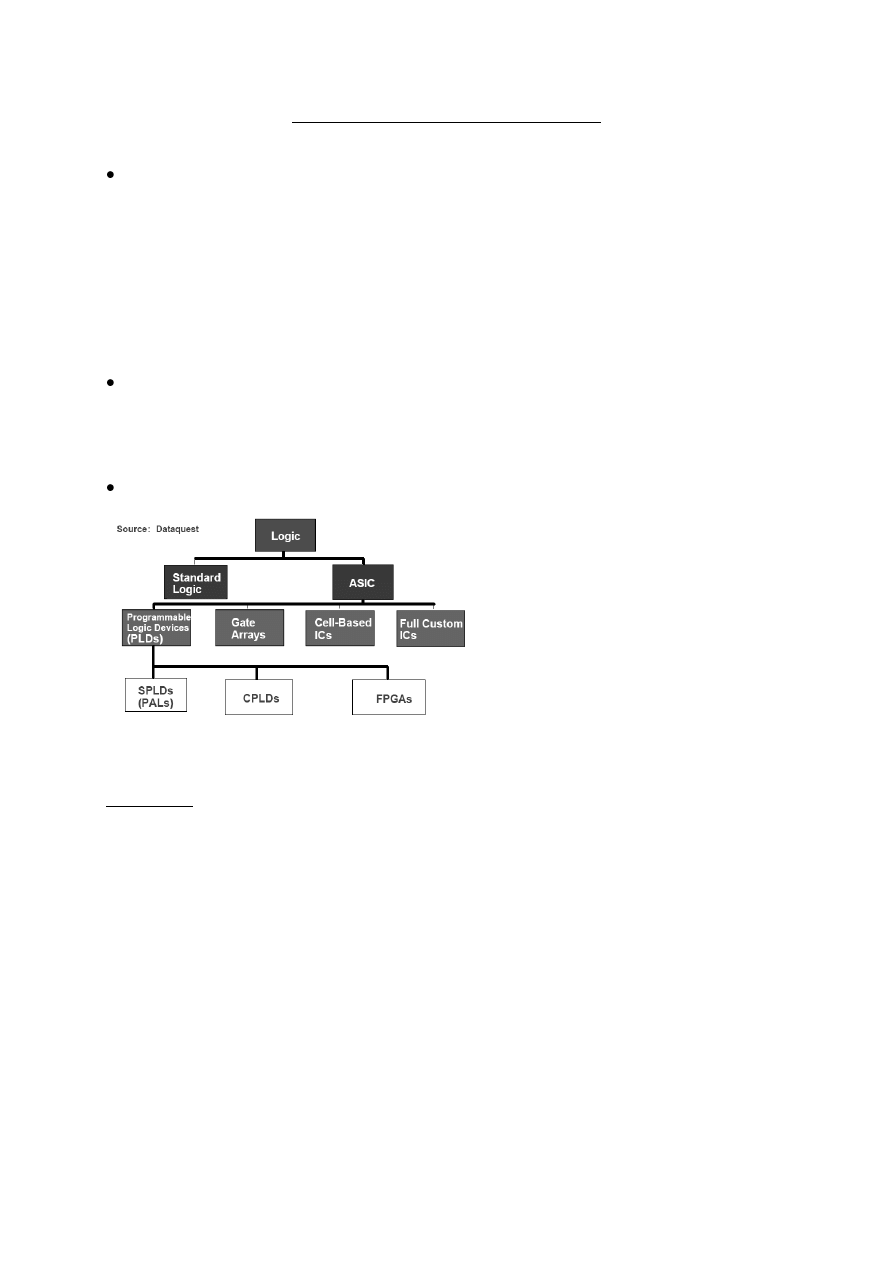

Układy reprogramowalne (PLA PAL CPLD GAL)

Programowalne układy cyfrowe(PLD):

SPLD (Simple Programmable Logic Device) – proste układy programowalne

o PLA (Programmable Logic Array)

o PAL (Programmable Array Logic) (Technologia bipolarna. Jednokrotne

programowanie przez przepalenia „fuse”)

o GAL (Generic Array Logic)

Są to układy o najskromniejszych możliwościach logicznych, a więc i najtańsze ze

wszystkich układów programowalnych. Niemniej jednak ich zasoby logiczne są spore,

zawierają bowiem typowo od 4 do 22 makrokomórek logicznych o dwupoziomowej

strukturze logicznej i mogą zwykle zastąpić kilka standardowych układów scalonych rodziny

74xx.

CPLD (Complex Programmable Logic Devices) – złożone układy programowalne

Układy CPLD są koncepcyjnie podobne do układów SPLD, lecz są bardziej złożone –

mają większe zasoby logiczne i możliwości funkcjonalne. Ich architektura ma strukturę

hierarchiczną opartą na makrokomórkach logicznych, których zawierają od kilkudziesięciu

do kilkuset.

FPGA (Field Programmable Gate Array) – programowalne matryce bramkowe

Rozkodowanie symbolu dla układów typu PAL:

PAL xx Y z

xx - liczba wejść

Y - L-logika ujemna

H - logika dodatnia

C - wyjścia komplementarne

R - wersja z przerzutnikami synchronicznymi

RA - wersja z przerzutnikami asynchronicznymi

X, A - wersja z układami arytmetycznymi

S - wersja z dzielonymi iloczynami

z - liczba wyjść (kombinacyjnych lub rejestrowych)

Klasyfikacja układów scalonych

Ze względu na sposób przetwarzania informacji:

układy sekwencyjne – w których stan wyjść zależy od stanu wejść x oraz od

poprzedniego stanu

układy kombinacyjne – w których sygnały wyjściowe zmieniają się w chwili zmian

sygnałów wejściowych

Ze względu na technologie w jakiej wykonano bramki logiczne:

bipolarne:

o TTL (ang. Transistor-Transistor Logic)

o ECL (ang. Emitter Coupled Logic)

o

I²L (ang. Integrated Injection Logic)

unipolarne:

o NMOS i PMOS

o CMOS (ang. Complementary MOS)

Obudowy

Funkcje obudowy:

Ochrona mechaniczna i fizykochemiczna (zewnętrzna warstwa nie przepuszcza,

zalanie elementów materiałem nie pozwala na ich przesuwanie się)

Ułatwianie montażu oraz rozpraszania ciepła (metalowy szkielet oddaje dobrze ciepło,

np. nóżki pozwalają na łączenie automatyczne oraz umiejscowienie w wybranym

miejscu)

Rodzaje obudów:

Plastykowe

o Tanie

o Odporne mechanicznie

Ceramiczne

o Bdb. hermetyzacja

o

Duża odporność chemiczna

Podział obudów ze względu na montaż:

Do montażu wgłębnego (piny)

o DIP

o SDIP

o HDIP

o

…

Do montażu powierzchniowego (styki płaskie, styki sprężynowe)

o SOP

o SOJ

o SSOP

o PLCC

o

…

VHDL

Very High Speed Integrated Circuits Hardware Description Language

Jest to bardzo popularny język opisu sprzętu używany w komputerowym

projektowaniu układów cyfrowych typu FPGA i ASIC.

Dlaczego VHDL?

Niezależna od technologii specyfikacja projektu

Możliwość współpracy pomiędzy różnymi producentami

Łatwość zmian funkcjonalnych

Automatyzacja projektowania (redukcja czasu i kosztów)

Ułatwienie weryfikacji funkcjonalnej oraz implementacji

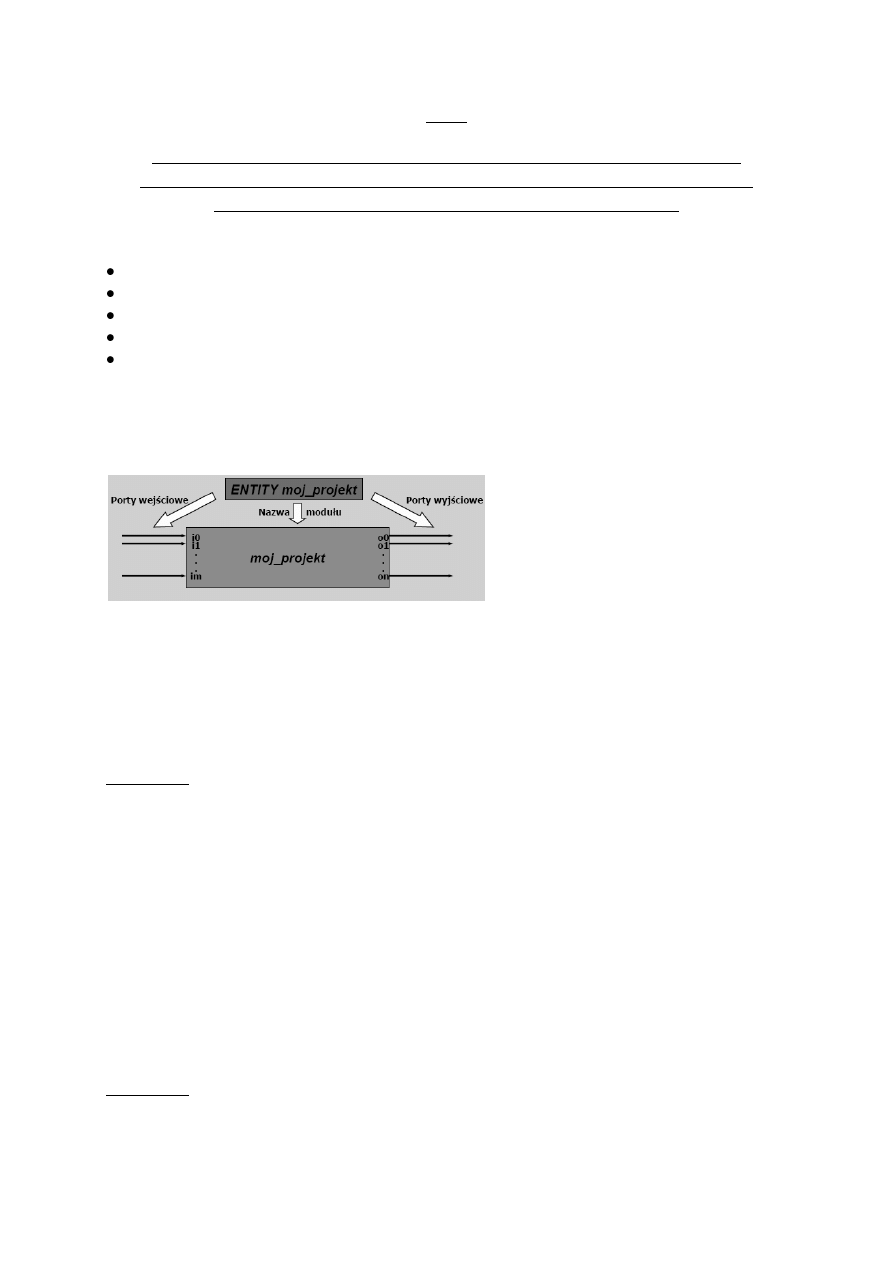

Entity – jednostka projektowa

Każdy moduł projektu w VHDL musi zawierać jednostkę projektową entity. Jednostka

projektowa (entity) w VHDL oznacza konstrukcję służącą do specyfikacji interfejsu do

komunikacji ze światem zewnętrznym.

Każda jednostka projektowa (entity) w projekcie musi posiadać unikalną nazwę. Wejścia i

wyjścia w projekcie noszą nazwę portów (PORTS).

Typy portów:

in – port wejściowy

out – port wyjściowy

inout – port dwukierunkowy, wykorzystywany w sytuacji, gdy dane przekazywane są przez

moduł bez ich zmiany

Deklaracja:

entity moj_projekt is

port(

i0, i1, i2, i3: in bit;

o0, o1, o2: out bit

);

end moj_projekt;

Generic - parametry ogólne

Wykorzystywana do parametryzacji projektu – jednostki projektowej. Składa się z ogólnej

listy interfejsu (generic interface list), w której zdefiniowane są parametry jednostki

projektowej (formal generic constants). Elementy składowe ogólnej listy interfejsu mogą być

jedynie stałymi rodzaju in (rodzaj jest pomijany w części deklaracyjnej).

Deklaracja:

entity projekt_testowy is

generic(N: integer);

port(

a_in, b_in: in bit_vector(N-1 downto 0);

stat: in bit;

y_out: out bit_vector (N-1 downto 0);

);

end projekt_testowy;

Deklaracja generic jest widoczna dla wszystkich architektur opartych na danej jednostce

projektowej (entity).

Architecture – implementacja jednostki projektowej

Ciało architektury (architecture) definiuje sposób działania jednostki projektowej od pobrania

danych z portów wejściowych do wygenerowania danych na portach wyjściowych.

Istnieje możliwość przyporządkowania wielu architektur do jednej jednostki projektowej:

cecha użyteczna w podejściu top down – dedykowana architektura opisuje kolejne stopnie

redefinicji na różnych poziomach abstrakcji

potrzeba opisu różnych wariantów tego samego modułu

Składnia:

architecture behaw of projekt_testowy is

signal a, b, c: bit;

begin

suma <= a XOR b;

end behaw;

Typy danych w VHDLu

Ścisła kontrola typow danych:

Typy wbudowane:

wyliczeniowe

całkowite

zmiennoprzecinkowe

fizyczne

tablicowe

Typy wyliczeniowe:

definiowane przez użytkownika, określające wyższy poziom abstrakcji

PRZYKŁAD:

Przy modelowaniu jednostki sterującej procesora zamiast kodów binarnych określających

jego stan wygodniej (czytelniej) jest stosować nazwy opisowe:

type stan_proc is (idle, add, store, compare, move, wait);

. . . . . . . . . . . . .

variable operacja:stan_proc := wait;

Typ boolowski:

wyliczeniowy typ predefiniowany

wykorzystywany do reprezentacji wartości zmiennych warunkowych sterujących

wykonaniem modeli behawioralnych

DEFINICJA:

type boolean is (false, true);

Zastosowanie:

relacje równości i nierówności (porównanie operandów tego samego typu daje w wyniku

wartość boolowską)

relacje mniejszości i większości – ostre i nieostre (stosowane do typów porządkowych –

całkowitych i znakowych)

Typ bitowy

Typ predefiniowany VHDL

Najczęściej używany typ danych

Typ syntezowalny

DEFINICJA:

type bit is (‘0’, ‘1’);

Konsekwencje:

Symbole „0” i „1” należą do typu bit oraz character

Operacje logiczne analogiczne do typu boolean

‘0’ or ‘1’ = ‘1’; -- poprawnie

‘0’ xor false – błąd

Typ bitowy a boolowski

Wartości boolowskie stosowane są do modelowania abstrakcyjnych uwarunkowań

Typ bitowy reprezentuje sprzętowy poziom logiczny

Operacje logiczne na typie bitowym wykorzystują logikę dodatnią

Typ bit_vector

Typ predefiniowany

W VHDL zdefiniowany jako tablica bitów

Wykorzystywany do reprezentacji magistral – uproszczona notacja dla funkcji logicznych

na magistralach (np. operacja XOR wykonywana na zawartości 8-bitowych rejestrów

zamiast ośmiu instrukcji bitowych)

Typ znakowy

Typ wyliczeniowy predefiniowany VHDL

Zdefiniowany w paczce (package) STANDARD

Zapisujemy w apostrofach

Każdy znak reprezentuje liczbę 8 bitową (format ASCII), syntezowalną do magistrali 8-

bitowej

DEFINICJA:

type character is (NUL, SOH, ESC, FSP (w chuj innych kodów…), ‘!’, ‘T’, ‘u’, ‘~’, DEL

(etc – każdy chyba pojął) )

PRZYKŁAD:

variable znak: character;

znak:=‘T’;

Typ całkowity (integer)

typ syntezowalny z ograniczeniami

automatyczna synteza -> zbyt szerokie magistrale

alternatywa: tablice bitów (bit_vector)

Typ zmiennoprzecinkowy (real)

!!!nie syntezowalny!!!

wykorzystywany w symulacjach

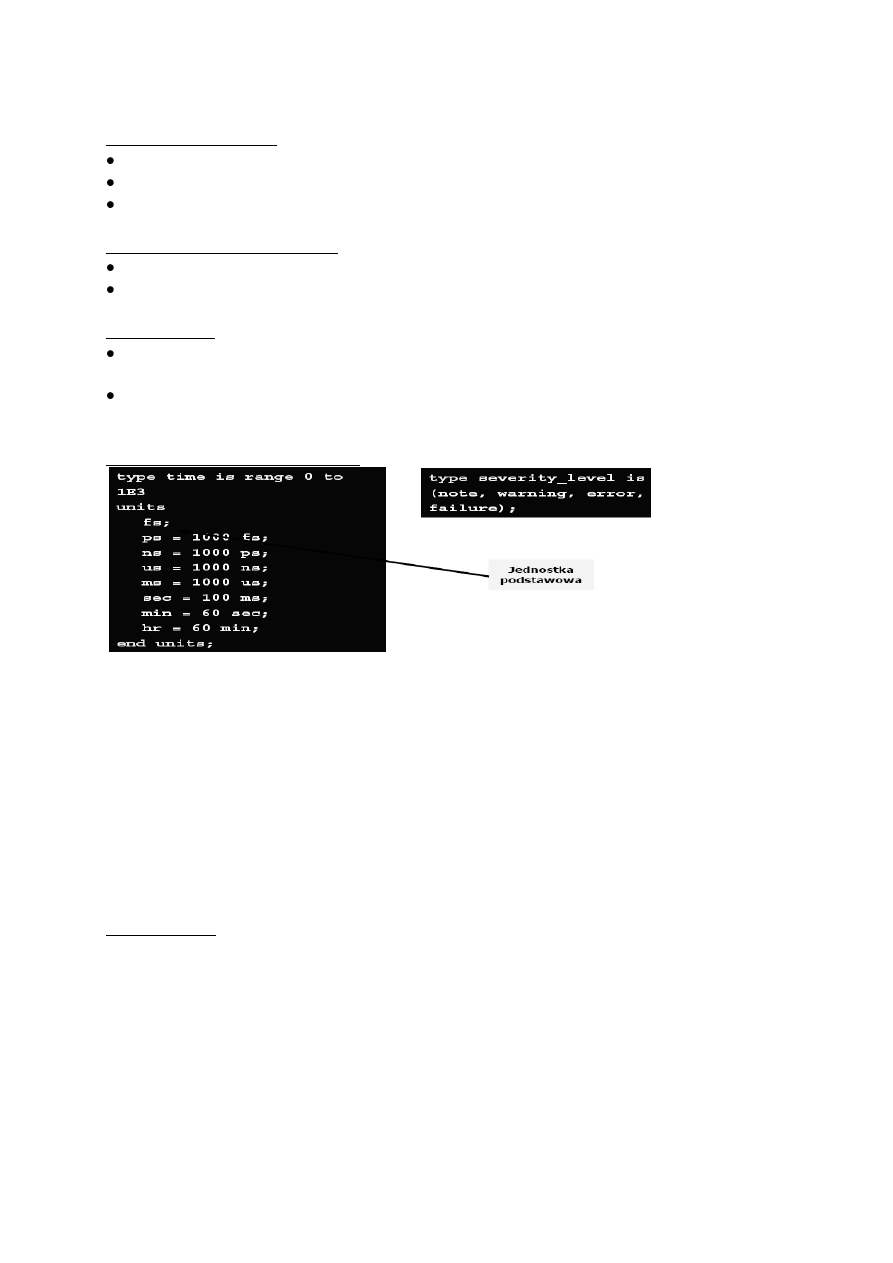

Typy fizyczne:

Reprezentacja wielkości występujących w świecie fizycznym (np. masa, długość, czas,

prąd itp.)

Definicja typu fizycznego zawiera podstawową jednostkę miary i może zawierać wtórne

jednostki miary (powstałe przez całkowite pomnożenie jednostki podstawowej)

Typy TIME i SEVERITY_LEVEL

Przykład zastosowania:

entity tik is

port(clk: out bit);

end tik;

architecture tak of tik is

begin

process

begin

clk <= ‘0’;

wait for 5ns; -- instrukcja nie syntezowalna

clk <= ‘1’;

wait for 5ns;

end process;

end tak;

Podsumowanie

• typ całkowity: INTEGER

• podtypy całkowite: NATURAL, POSITIVE

• typ zmiennoprzecinkowy: REAL

• typ fizyczny: TIME

• typy tablicowe: STRING, BIT_VECTOR

• typy wyliczeniowe: BIT, BOOLEAN, SEVERITY_LEVEL,

CHARACTER

Sposoby projektowania systemów

Top-down:

Idea całości projektu

Dekompozycja na mniejsze bloki

Projekt i rafinacja podbloków

Łączenie bloków w całość

PRZYKŁAD (sumator kaskadowy):

zdefiniowanie operacji sumatora kaskadowego

określenie projektu za pomocą szeregu pełnych sumatorów

zdefiniowanie pełnego sumatora za pomocą półsumatora

skonstruowanie pełnego sumatora

połączenie wszystkich bloków

Down-top (bottom-up)

Projektowanie najmniejszych elementów

Łączenie komponentów w bloki funkcjonalne

Powtarzanie procesu łączenia

PRZYKŁAD (sumator kaskadowy)

Zdefiniowanie, zaprojektowanie, symulacja oraz synteza pełnego sumatora za pomocą

półsumatora

Skonstruowanie pełnego sumatora poprzez połączenie dwóch półsumatorów

Zaprojektowanie sumatora n-bitowego dzięki szeregowemu połączeniu n pełnych

sumatorów

Top-down i Bottom-up

Wybór sposobu projektowania zależy od rozmiaru i złożoności projektu, dostępnych zasobów

oraz doświadczenia i preferencji projektanta

Wybór stylu top-down:

duże i złożone projekty z małym wykorzystaniem IP core

we wczesnej fazie projektowej brak możliwości dekompozycji projektu na mniejsze

elementy

brak informacji dotyczącej komponentów na poziomie strukturalnym

Kod strukturalny

Możliwość stworzenia hierarchicznego projektu za pomocą zbioru

połączonych komponentów

Komponenty (bloki uprzednio zweryfikowane i zsyntezowane) mogą

być umieszczone w bibliotekach

Uproszczenie procesu rafinacji, uruchamiania i usuwania bledów

(mniejszy układ, łatwiejsze uruchamianie)

Tworzenie komponentów:

Mniejsze komponenty

Wyrażenia logiczne

Opis funkcjonalny (behawioralny)

Rodzaje komponentów na różnych poziomach abstrakcji (netlista, RTL)

Reprezentacja strukturalna w VHDL

Implementacja jednostki projektowej za pomocą specyfikacji

połączeń podsystemów

o

Ciało architektury złożone tylko z połączonych podsystemów

Elementy strukturalne ciała architektury

deklaracja sygnałów

deklaracja komponentów

konkretyzacja komponentów

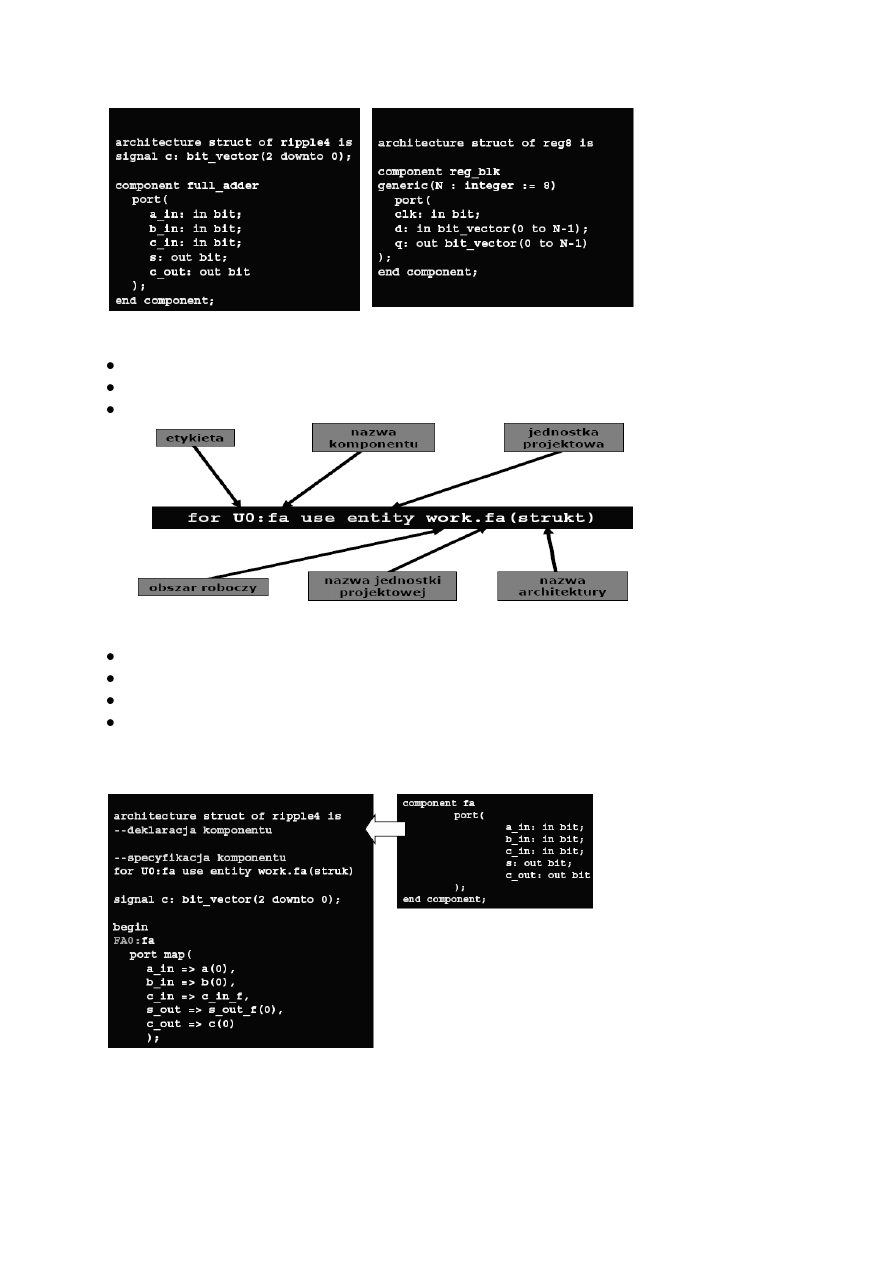

Przykład: 4-bitowy sumator kaskadowy:

Deklaracja komponentów (component)

Deklaracja komponentów – specyfikacja zewnętrznego interfejsu pod kątem stałych

(generic) oraz portów (port)

o

brak wymagania implementacji komponentu, konieczność znajomości jego

interfejsu

Deklaracja komponentu wykorzystuje nazwę, którą posiada jednostka projektowa definiująca

komponent, a także taką samą deklarację portów.

Istnienie wielu komponentów o tej samej nazwie -> konieczność specyfikacji komponentu do

wykorzystania.

Specyfikacja komponentów i synteza

Specyfikacja komponentów tylko do celów symulacji

Narzędzia syntezy ignorują specyfikację komponentów

Do syntezy projektu używane są najpóźniej skompilowane komponenty

Konkretyzacja komponentów

deklaracja komponentu – definicja rodzaju modułu

konkretyzacja – wykorzystanie modułu w projekcie

deklaracja komponentu w ciele architektury wraz z deklaracją sygnału (przed begin)

konkretyzacja komponentu w ciele architektury (po begin)

Uwaga: komponenty mogą być opisane strukturalnie lub behawioralnie w

oddzielnych jednostkach projektowych, traktując je jako oddzielne projekty

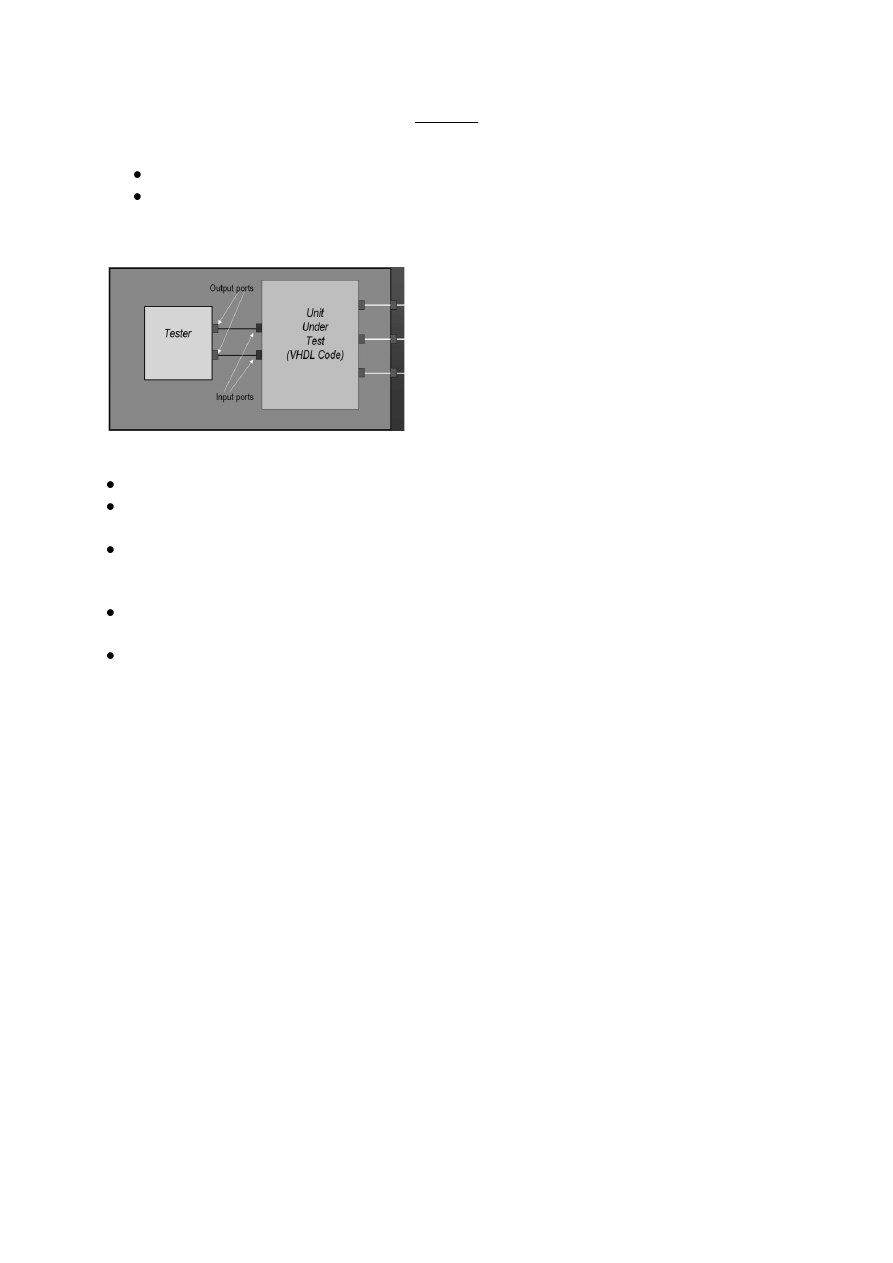

Testbench

Składa się z dwóch bloków:

Nadrzędnego modułu projektowanego bloku VHDL

jednostki projektowej wykorzystywanej do generowania wymuszeń (łącznie z

zegarem), odczytu wektorów testowych z pliku zewnętrznego, prezentacji wyników w

oknie symulatora lub zapis do pliku

Główne zastosowania konstrukcji testbench:

Generowanie wymuszeń do celów symulacji

Doprowadzenie wektorów testowych do układu podawanego testowaniu (CUT – circuit

under test) oraz pobieranie z niego odpowiedzi

Zadanie opcjonalne: porównanie otrzymanych wyników z wartościami oczekiwanymi

Testbench:

Wektor podawany jest automatycznie do odpowiednich portów CUT poprzez konstrukcję

mapowania portów polegającą na wewnętrznym przypisaniu sygnałów

Potrzeba generowania dwóch typów sygnałów:

o Zegar – sygnał powtarzalny, okresowy

o

sekwencyjne przypisanie sygnałów – wektory testowe CUT

Zgodność łączeniowa

Zgodność łączeniowa - Układy A i B są ze sobą zgodne łączeniowo, jeżeli odpowiednie połączenia wejść i

wyjść tych układów zapewniają poprawną (elektrycznie) pracę układów

Obciążalność wyjściowa - ilość wejść następnych bramek, jaką można podłączyć do wyjścia rozpatrywanej

bramki.

Cechy projektowania układów cyfrowych

-wartości zmiennych i stałych są przechowywane w rejestrach lub pamięciach,

-zmienne i stałe są pobierane z miejsc przechowywania przy narastającym zboczu sygnału

zegarowego,

-w układach kombinacyjnych dokonywana jest transformacja (w czasie pomiędzy dwoma

narastającymi zboczami sygnału zegarowego),

-wyniki są przechowywane w pamięciach lub rejestrach przy kolejnym zboczu zegara jeden

przerzutnik ja jeden stan

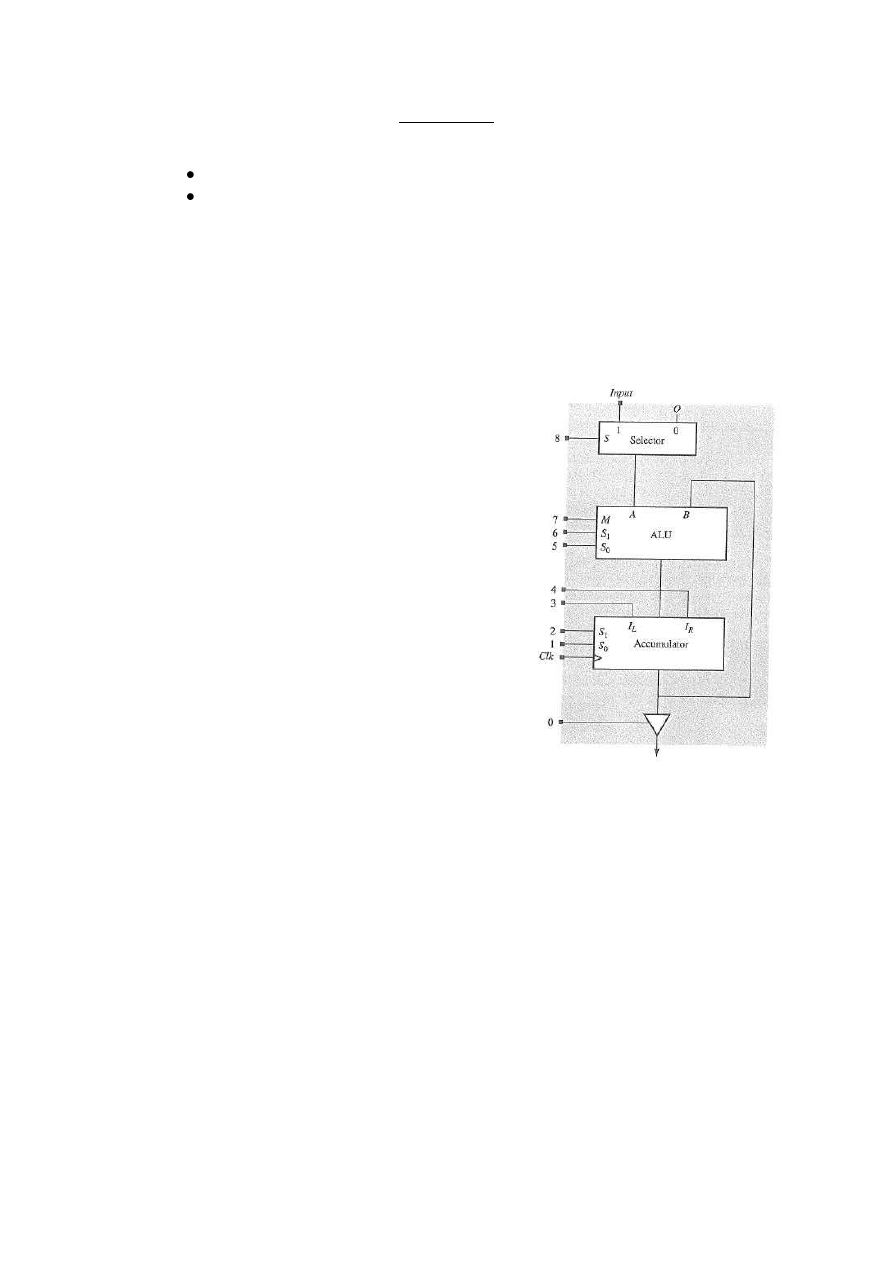

Ścieżka danych

Wykorzystanie ścieżki danych:

standardowe procesory

implementacje ASIC

Ścieżka danych służy do tymczasowego przechowywania informacji w połączeniu z układami

arytmetycznymi i logicznymi.

Przykład: Operacja sumowania 100 liczb.

suma = 0

Ciało pętli:

loop:

- 32-bitowa ścieżka danych

for i = 1 to 100

- Akumulator

suma = suma + xi

- ALU

end loop

Zmienna suma jest przechowywana w akumulatorze. W

każdym takcie zegara nowa wartość xi jest dodawana do

zmiennej suma w ALU. Nowa wartość suma jest

ponownie przechowywana w Akumulatorze.

Słowo sterujące definiuje zachowanie ścieżki danych w

każdym takcie zegara. Obliczenie sumy wymaga 102

taktów zegara:

1 – zerowanie akumulatora

100 – dodawanie

1 – wyprowadzenie danych

Wyszukiwarka

Podobne podstrony:

opracowanie uoop 2008 wpiaforum.na7.pl, Prawo - materialy

LABORKI OPRACOWANE DOŚWIADCZENIA, 2008.01.12 KOROZJA METALI I, KOROZJA METALI I

opracowanie z TC

dydaktyka opracowanie 2008 2009 wpuw 091011124634 phpapp02

pytania z anatomii z 2008 roku z anatomii - opracowane, Studia, Ratownictwo Medyczne, Semestr I, Ana

opracowania, Ochrona Środowiska studia, 2 rok (2007-2008), Semestr IV (Rok 2), Kartografia Geologicz

TEMATY do opracowania ZARZĄDZANIE W PIELĘGNIARSTWIE 2008, I

PPG opracowanie, 11 partnerstwo, USTAWA z dnia 19 grudnia 2008 r

Tc Tu wyniki 2008, EIT

więcej podobnych podstron