- 1 -

11.UKŁADY CYFROWE (UKŁADY LOGICZNE)

11.1. WPROWADZENIE

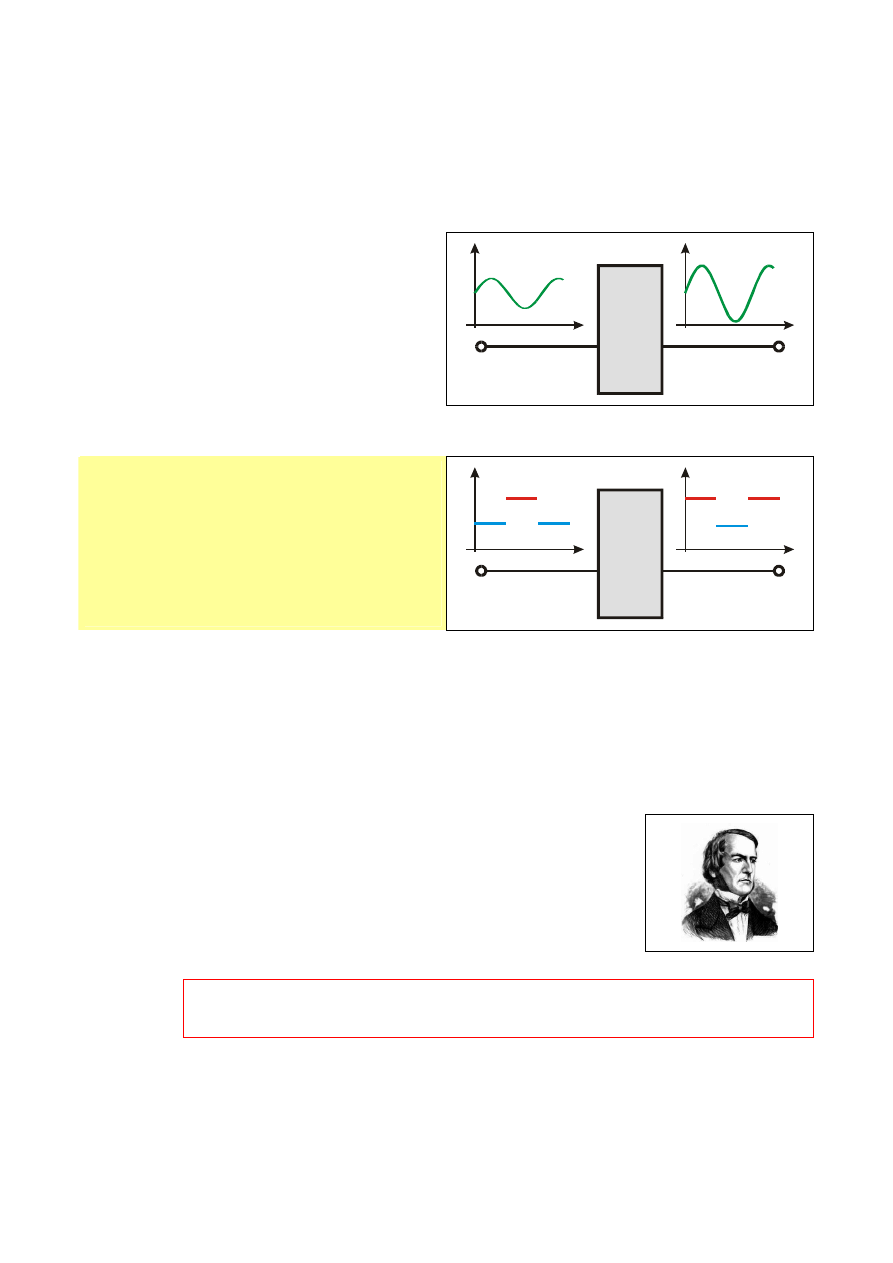

Układy analogowe (UA) to

rodzaj układów elektronicznych, w

których przetwarzane sygnały mogą

przyjmować dowolną wartość z

określonego przedziału.

S

WE

t

UA

WE

WY

S

WY

t

Układy cyfrowe (UC) to rodzaj

układów elektronicznych, w których

przetwarzane sygnały przyjmują

zazwyczaj tylko dwa poziomy,

oznaczane literami

H

(wysoki -

high

) i

L

(niski

- low

).

S

WE

t

UC

WE

WY

S

WY

t

H

L

L

H

L

Poziomom sygnału przypisuje się wartości logiczne 0 lub 1.

Patrząc na sygnały jako na zmienne logiczne, działanie układów

cyfrowych można przedstawić jako wykonywanie operacji logicznych na

tych zmiennych. Sygnałom wejściowym odpowiadają zmienne będące

argumentami tych operacji, zaś wyjściowym – zmienne będące wynikami.

Z tego względu do opisu i analizy właściwości

układów cyfrowych jest stosowany aparat pojęciowy

logiki matematycznej – algebry

ZATEM:

Układy cyfrowe (fizycznie istniejące) modeluje się za pomocą

układów logicznych (tworów abstrakcyjnych)

- 2 -

11.2. POZIOMY LOGICZNE

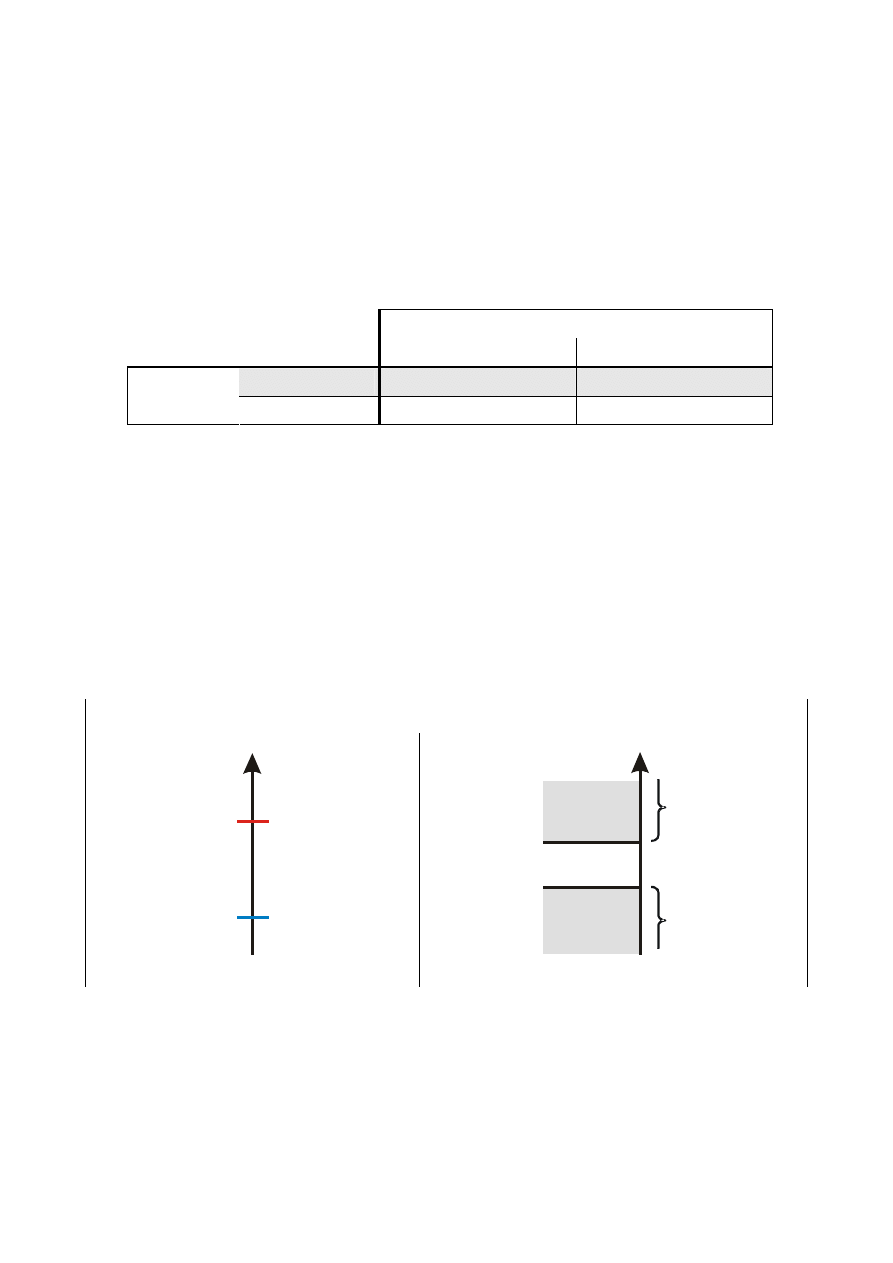

Poziomom sygnału przypisuje się wartości logiczne: prawda i fałsz,

oznaczane symbolami odpowiednio 1 i 0.

Są dwa sposoby przyporządkowania poziomom sygnału wartości

logicznych: w logice dodatniej poziomowi wysokiemu odpowiada 1

(prawda) a niskiemu 0 (fałsz), natomiast w logice ujemnej – odwrotnie.

Poziom sygnału

niski

L

wysoki

H

dodatnia

0

1

Logika

ujemna

1

0

W elektronicznych układach cyfrowych nośnikiem sygnału najczęściej

jest napięcie,

ze względu na:

wahania napięcia zasilającego

rozrzut parametrów elementów

szumy i zniekształcenia

nie ma ściśle określonej wartości, stąd też wartościom logicznym

odpowiadają nie wartości napięć, ale zakresy (obszary) napięć.

Reprezentacja zmiennej logicznej za pomocą poziomów napięciowych

U

L

H

1

0

reprezentacja idealna

U

L

H

1

0

obszar

zabroniony

reprezentacja rzeczywista

Gdy napięcie przyjmuje wartość nie należącą do żadnego z wyróżnionych

zakresów, wówczas wartość logiczna sygnału nie jest określona!

- 3 -

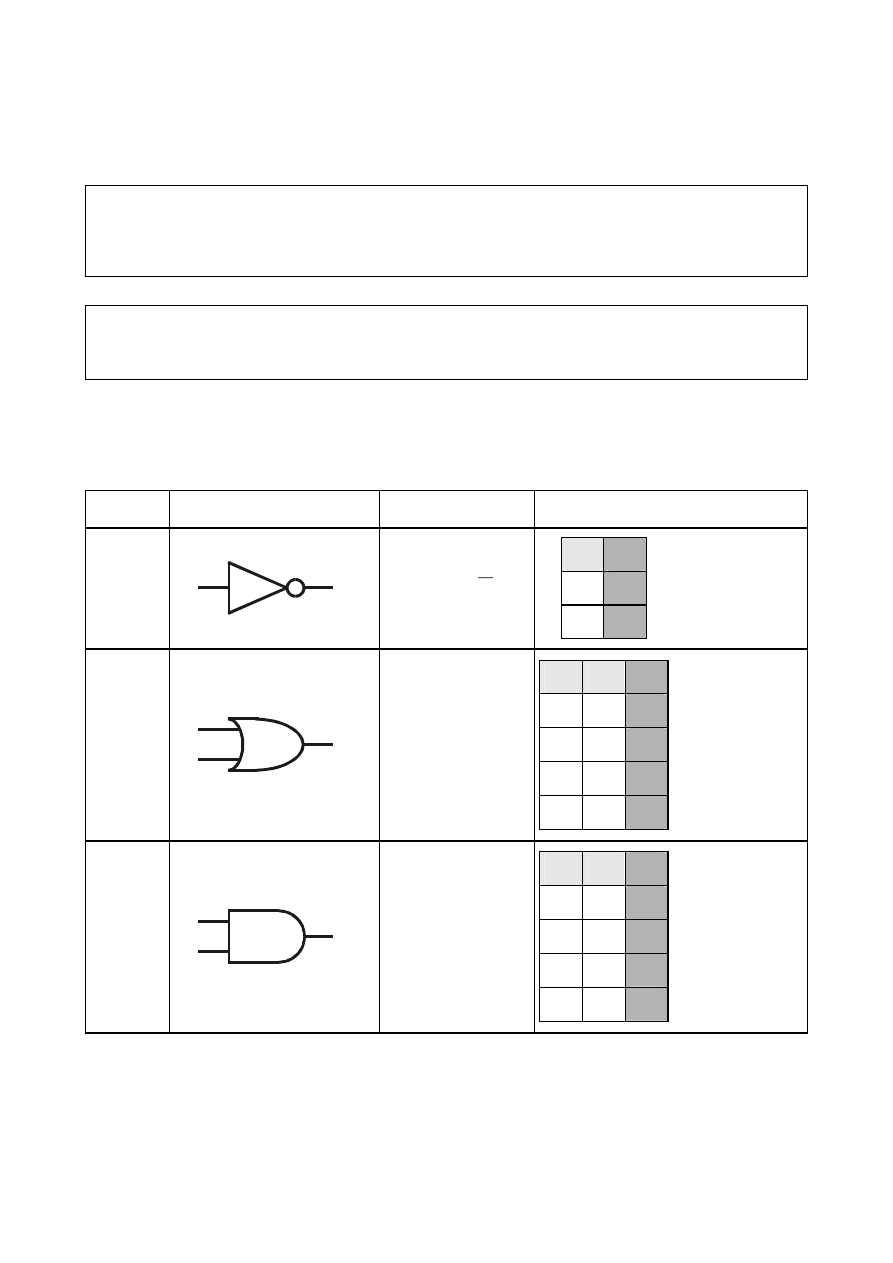

11.3. FUNKTORY LOGICZNE

Logika matematyczna uczy, że

każdą funkcje logiczną (funktor) można złożyć z kombinacji trzech

podstawowych działań logicznych: negacji (inwersji – nie – NOT),

sumy (alternatywy – lub- OR) oraz iloczynu (koniunkcji – i – AND).

Urządzenia elektroniczne realizujące te funkcje nazywamy

bramkami

,

odpowiednio

NOT

,

OR

i

AND

.

Bramka scharakteryzowana jest poprzez nazwę, symbol graficzny,

funkcje logiczne oraz tablicę prawdy.

Nazwa

Symbol

Funkcja

Tablica prawdy

NOT

WY

A

A

WY

A

WY

0

1

1

0

OR

A

B

WY

B

A

WY

A

B

WY

0

0

0

0

1

1

1

0

1

1

1

1

na

wyjściu

pojawia się zero

wtedy i tylko

wtedy,

kiedy

oba sygnały na

wej. posiadają

wartość

logiczną zero

AND

A

B

WY

AB

WY

A

B

WY

0

0

0

0

1

0

1

0

0

1

1

1

na

wyjściu

pojawia

się

sygnał 1 wtedy i

tylko

wtedy,

kiedy

oba

sygnały

wej.

posiadają

wartość

logiczną jeden

- 4 -

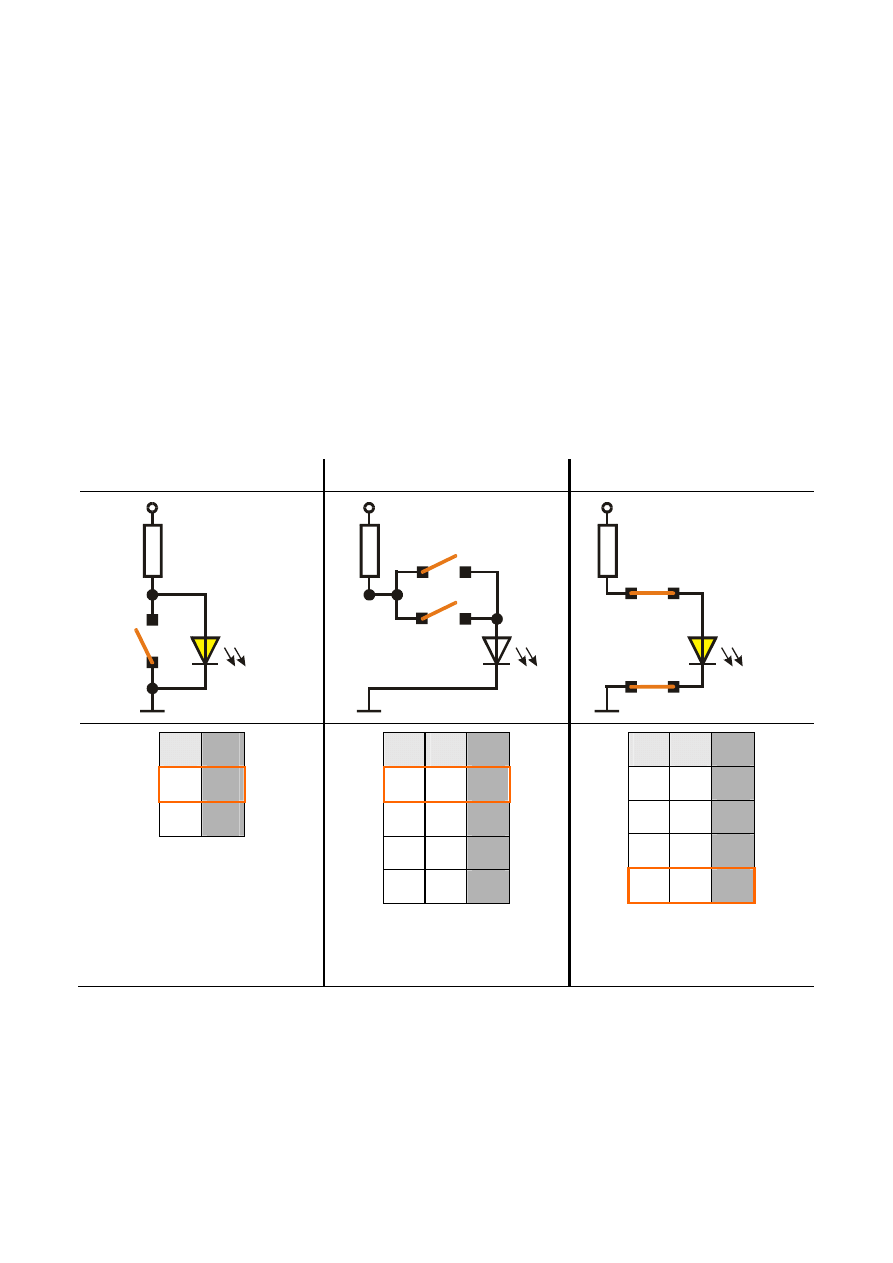

UWAGA:

Bramki można rozpatrywać jako swoiste połączenie kluczy

elektronicznych

EKSPERYMENT

Założenia:

sygnał wejściowy układu określa pozycję klucza

przypisanego danemu wejściu; poziom wysoki wymusza

zwarcie klucza, natomiast poziom niski – rozwarcie klucza,

czyli:

rozwarcie

L

zwarcie

H

,

stan wyjścia układu (poziom sygnału wyjściowego) określa

dioda LED (świecenie – stan wysoki H).

NOT

OR

AND

A

+3V

WY=A

_

+3V

WY=A+B

B

A

+3V

A

B

WY=AB

A

WY

L

H

H

L

A

B

WY

L

L

L

L

H

H

H

L

H

H

H

H

A

B

WY

L

L

L

L

H

L

H

L

L

H

H

H

Dioda nie świeci wtedy i

tylko wtedy, kiedy oba

klucze są rozwarte

Dioda świeci wtedy i tylko

wtedy, kiedy oba klucze są

zwarte

Problem:

Jak zrealizować klucz elektroniczny

?

- 5 -

Rozwiązanie:

Można wykorzystać diody i tranzystory

!

PRZYKŁADY:

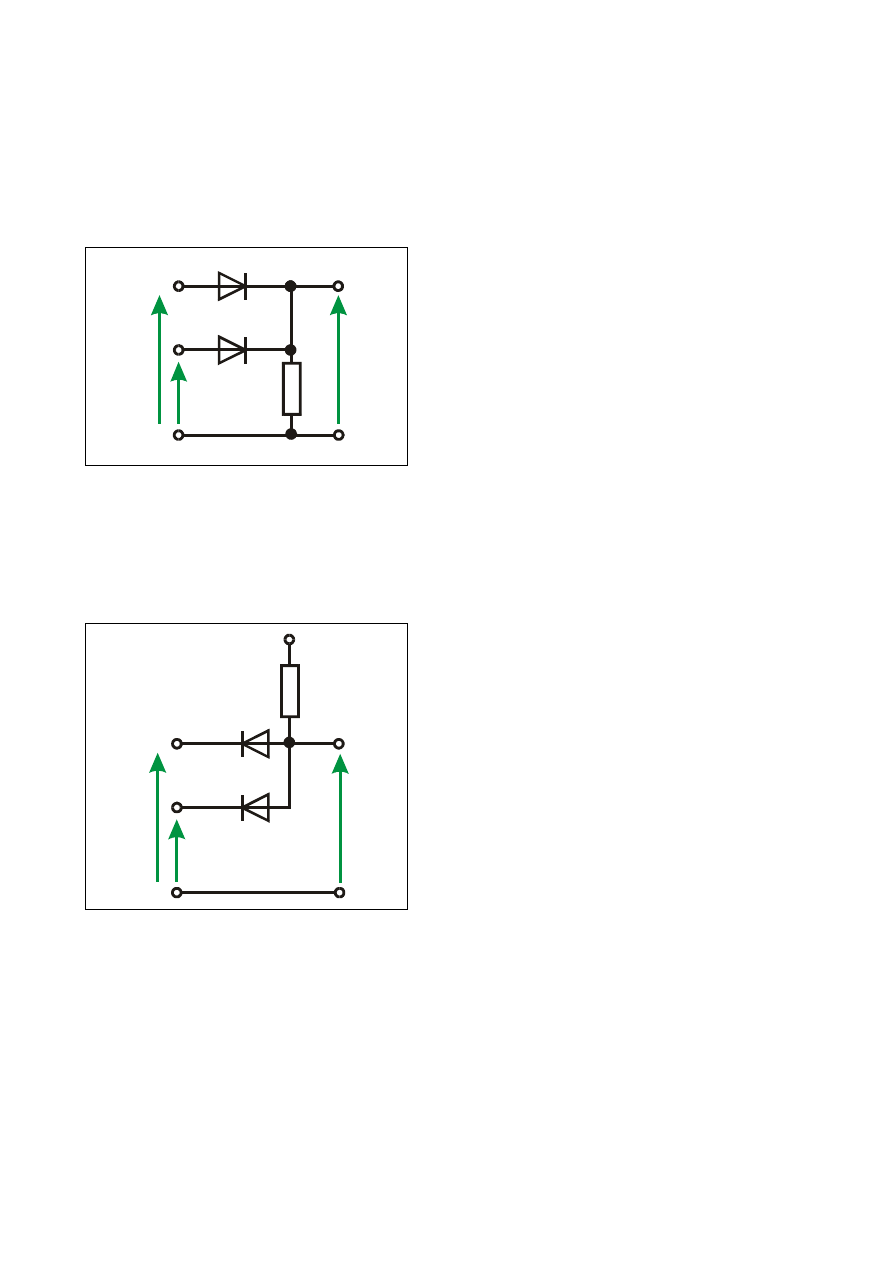

układ diodowy bramki

OR

D

2

D

1

U

we1

U

we2

U

wy

R

Jeżeli na obydwu wejściach jest 0

logiczne, to również wyjście jest w stanie 0.

Jeżeli do jednego z wejść zostanie

doprowadzone

napięcie

dodatnie

(1

logiczna), to na wyjściu wystąpi również to

napięcie (zmniejszone o spadek napięcia na

przewodzącej diodzie). Przy doprowadzeniu

dwóch napięć wejściowych, wartość napięcia

jest określona przez wartość napięcia o

większej wartości.

Napięcie wyjściowe ma więc wartość dodatnią, jeżeli jedno lub dwa

napięcia wejściowe mają wartość dodatnią. W logice dodatniej jest to

zatem element OR.

układ diodowy bramki

AND

D

2

D

1

U

we1

U

we2

+U

CC

R

U

wy

Jeżeli co najmniej na jednym z wejść

poziom napięcia przyjmuje 0 logiczne, to

odpowiednia dioda jest spolaryzowana w

kierunku przewodzenia, przez rezystor R

płynie prąd i prawie całe napięcie zasilające

U

CC

odkłada się na rezystorze. Oznacza to, że

na wyjściu panuje napięcie zbliżone do zera.

Jeżeli na obu wejściach jest napięcia mają

wartość 0 logicznego to obydwie diody

przewodzą.

Jedynie w przypadku gdy na obydwa wejścia jednocześnie podane są

napięcia o poziomie 1 logicznej (umożliwiające polaryzację zaporową

diod), żadna z diod nie przewodzi i dzięki temu potencjał wyjścia osiąga

poziom 1 logicznej. W logice dodatniej jest to zatem element AND.

- 6 -

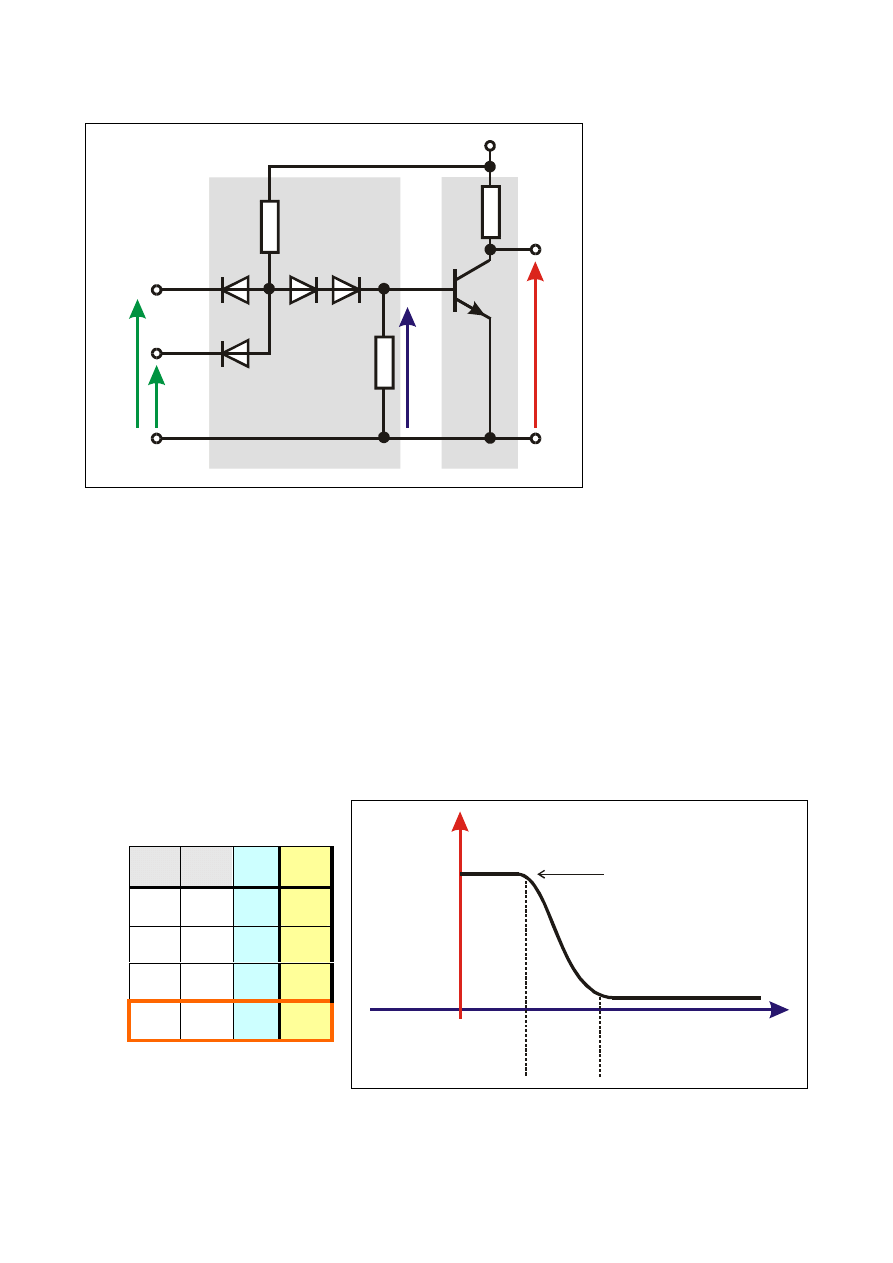

układ diodowo-tranzystorowy bramki

NAND

D

2

D

1

U

we1

U

we2

U

wy

+U

CC

D

3

D

4

R

1

R

2

R

C

AND

NOT

U

BE

Na wejściu znajduje

się układ logiczny AND

złożony z dwóch diod

wejściowych D

1

i D

2

oraz diod szeregowych

D

3

i D

4

. Diody są

zasilane

ze

źródła

napięcia U

CC

poprzez

rezystory R

1

i R

2

. Diody

D

3

i D

4

podnoszą próg

przewodzenia

złącza

baza-emiter zapewniając

prawidłowe

działanie

układu.

Tranzystor jest w układzie elementem pełniącym rolę separatora i

jednocześnie wykonuje funkcję logiczną

NOT

- odwracając fazę przebiegu

sterującego bazę.

Gdy podawane na wejście bramki

NOT

napięcie ma poziom niski L

(U

BE

<0,7V), wówczas tranzystor nie przewodzi – jest zatkany – na jego

kolektorze występuje napięcie (U

wy

) bliskie U

CC

, czyli wysoki poziom

napięcia H.

Jeżeli natomiast napięcie U

BE

ma odpowiednio dużą wartość, czyli na

wejściu bramki

NOT

występuje wysoki poziom napięcia H, to tranzystor

jest nasycony i na jego kolektorze niski poziom napięcia L.

U

we1

U

we2

U

BE

U

WY

L

L

L

H

L

H

L

H

H

L

L

H

H

H

H

L

U

wy

U

BE

U =5V

CC

ZATKANIE

NASYCENIE

(U - poziom H)

BE

(U - poziom L)

BE

(U - poziom H)

wy

(U - poziom L)

wy

U

CEsat

- 7 -

11.4. KLASYFIKACJA UKŁADÓW CYFROWYCH

Ze względu na

technologię wykonania bramek

wyróżnia się układy:

bipolarne

TTL

: tranzystorowo- tranzystorowe (

Transistor-Transistor Logic

);

ECL

: o sprzężeniu emiterowym (

Emitter Coupled Logic

);

I

2

L

: ze wstrzykiwaniem nośników ładunku (

Integrated Injection Logic

);

unipolarne

NMOS

: z tranzystorami z kanałem typu N;

PMOS

: z tranzystorami z kanałem typu P;

CMOS

: z tranzystorami komplementarnymi (

Complementary MOS

).

Z uwagi na charakter zależności stanu sygnału (sygnałów) wyjściowego

od stanów sygnałów wejściowych

wyróżnia się układy:

kombinacyjne

-

stan sygnału wyjściowego zależy w każdej

chwili wyłącznie od bieżącego stanu sygnałów

wejściowych

, do układów kombinacyjnych

należą m.in.:

bramki;

kodery, dekodery;

komparatory;

sumatory.

sekwencyjne

-

stan sygnału wyjściowego zależy nie tylko od

aktualnego poziomu sygnałów wejściowych,

ale również poprzedniego stanu układu.

- 8 -

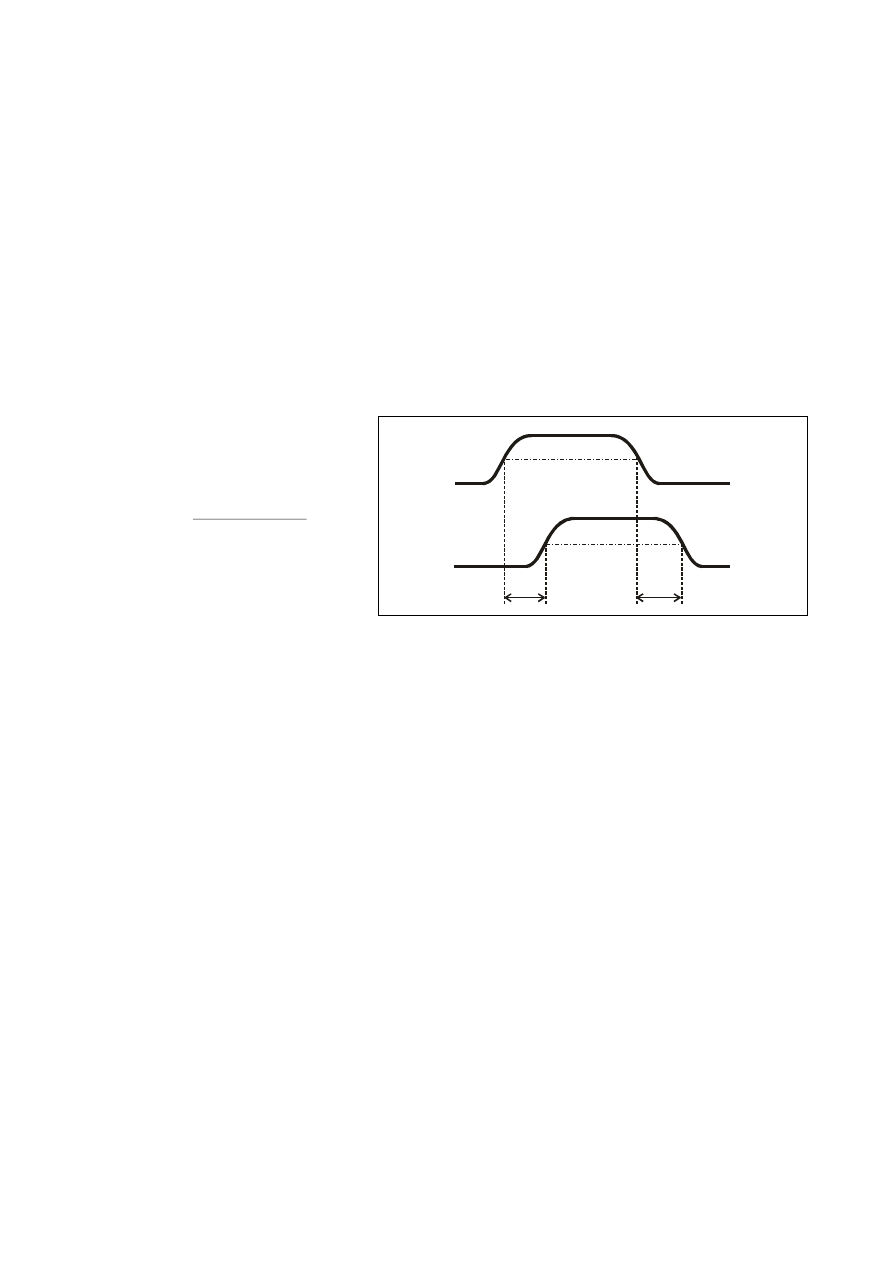

11.5. PODSTAWOWE PARAMETRY UC

Do najważniejszych parametrów układów cyfrowych zalicza się

czas propagacji t

P

Zmiana sygnału wyjściowego spowodowana zmianą sygnału wejściowego nie

następuje natychmiast, lecz z opóźnieniem. Opóźnienie to może być inne przy

zmianie sygnału wej. z poziomu H na L i inne przy zmianie odwrotnej. Jako

miarę opóźnienia przyjmuje się czas propagacji będący średnią czasów

opóźnienia przy zmianach sygnałów w obu kierunkach

2

HL

P

LH

P

p

t

t

t

L

t

P LH

L

H

H

t

P HL

S

WE

S

WY

moc strat P

S

Jest to moc pobierana przez układ . Określa się ją w sposób uproszcony

wartością iloczynu napięcia zasilania układu i średniego prądu pobieranego

przez układ ze źródła zasilania:

śr

zas

S

I

U

P

obciążalność N

max

Określa liczbę wejść innych układów, które można dołączyć do wyjścia

danego układu.

- 9 -

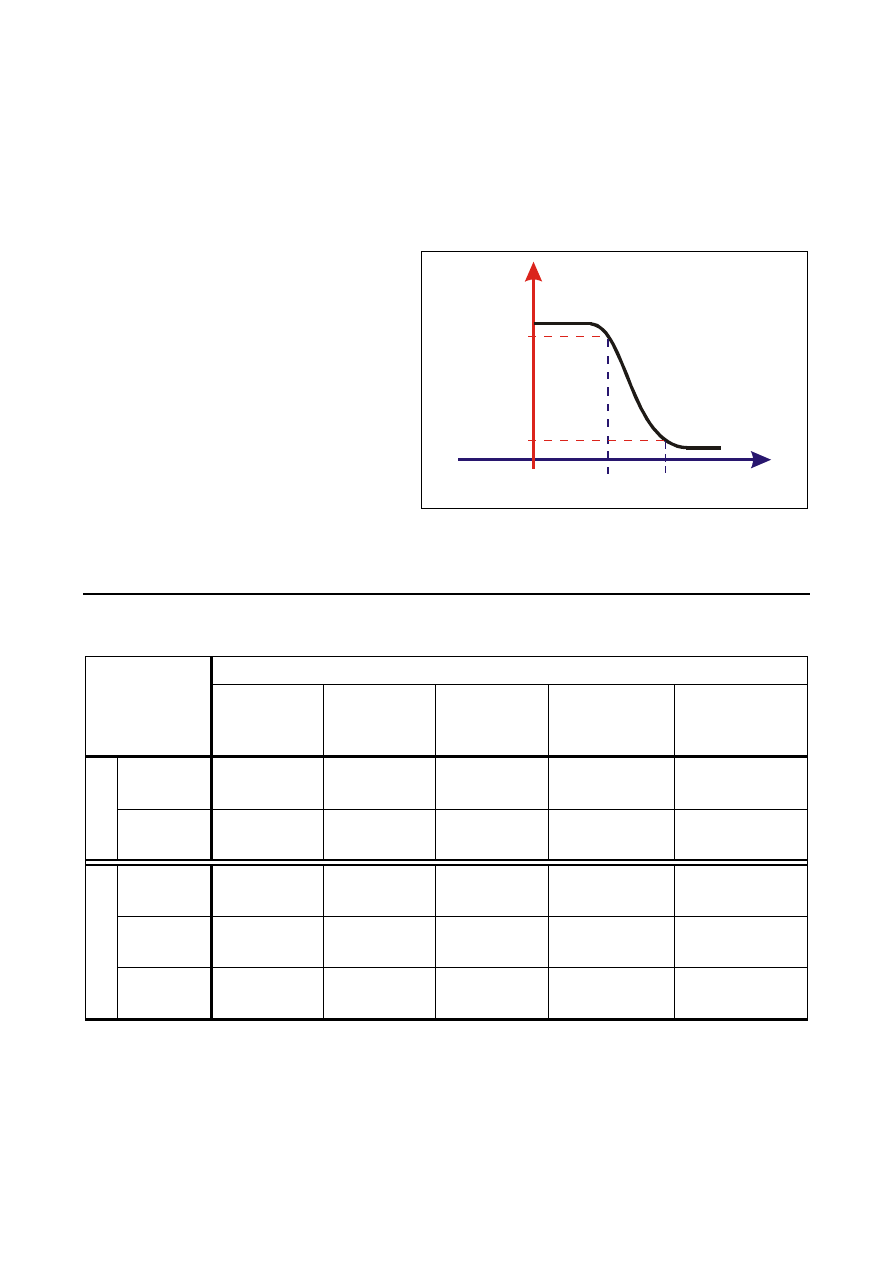

Margines zakłóceń M

(odporność na zakłócenia)

Określa dopuszczalne wartości amplitudy sygnału zakłócającego nie

powodujące jeszcze nieprawidłowej pracy układu. Marginesy zakłóceń M

L

dla

stanu niskiego i M

H

dla stanu wysokiego na wejściu bramki można określić na

podstawie jej charakterystyki przejściowej:

max

max

L

wy

L

we

L

U

U

M

min

min

H

we

H

wy

H

U

U

M

U

wy

U

we

U

we Lmax

U

we Hmin

U

wy Hmin

U

wy Lmax

ZESTAWIENIE PORÓWNAWCZE

Parametr

technologie

t

Ptyp

[ns]

P

Styp

[mW]

N

max

Zasilanie

[V]

M

typ

[V]

TTL

2 - 33

1-23

10

5

1

b

ip

o

la

rn

e

ECL

1-3

25-60

63-92

-5,2

0,2

PMOS

35-300

0,5-1,5

> 20

Dwa lub trzy z

-27...+27

0,7-1,5

NMOS

15-150

1

> 20

jedno do trzech

z

-15...+15

1

u

n

ip

o

la

rn

e

CMOS

50

10

nW

> 50

3-18

0,45 U

zas

typ. - typowe wartości

- 10 -

11.6. UKŁADY SEKWENCYJNE

W układach sekwencyjnych stan sygnału wyjściowego jest nie tylko

funkcją bieżących poziomów sygnałów wejściowych, ale również

poprzedniego stanu układu.

W układach tych występują więc

elementy pamięciowe

(przerzutniki), dzięki którym może być realizowana zależność

aktualnego stanu układu sekwencyjnego od jego stanu poprzedniego.

Zależnie od trybu pracy elementów pamięciowych,

układy

sekwencyjne dzieli się na:

asynchroniczne

-

zmiana stanu na wyjściach układu następuje

bezpośrednio po zmianie stanu na jego

wejściach;

synchroniczne

-

zmiana stanu wyjść odbywa się w chwilach

wyznaczonych sygnałem synchronizującym.

11.6.1. PRZERZUTNIK

to układ mający dwa stany równowagi trwałej, przy czym w każdym z

tych stanów przerzutnik może pozostawać dowolnie długo,

natomiast przejście z jednego stanu równowagi do drugiego następuje

tylko pod wpływem zewnętrznego sygnału wyzwalającego

- 11 -

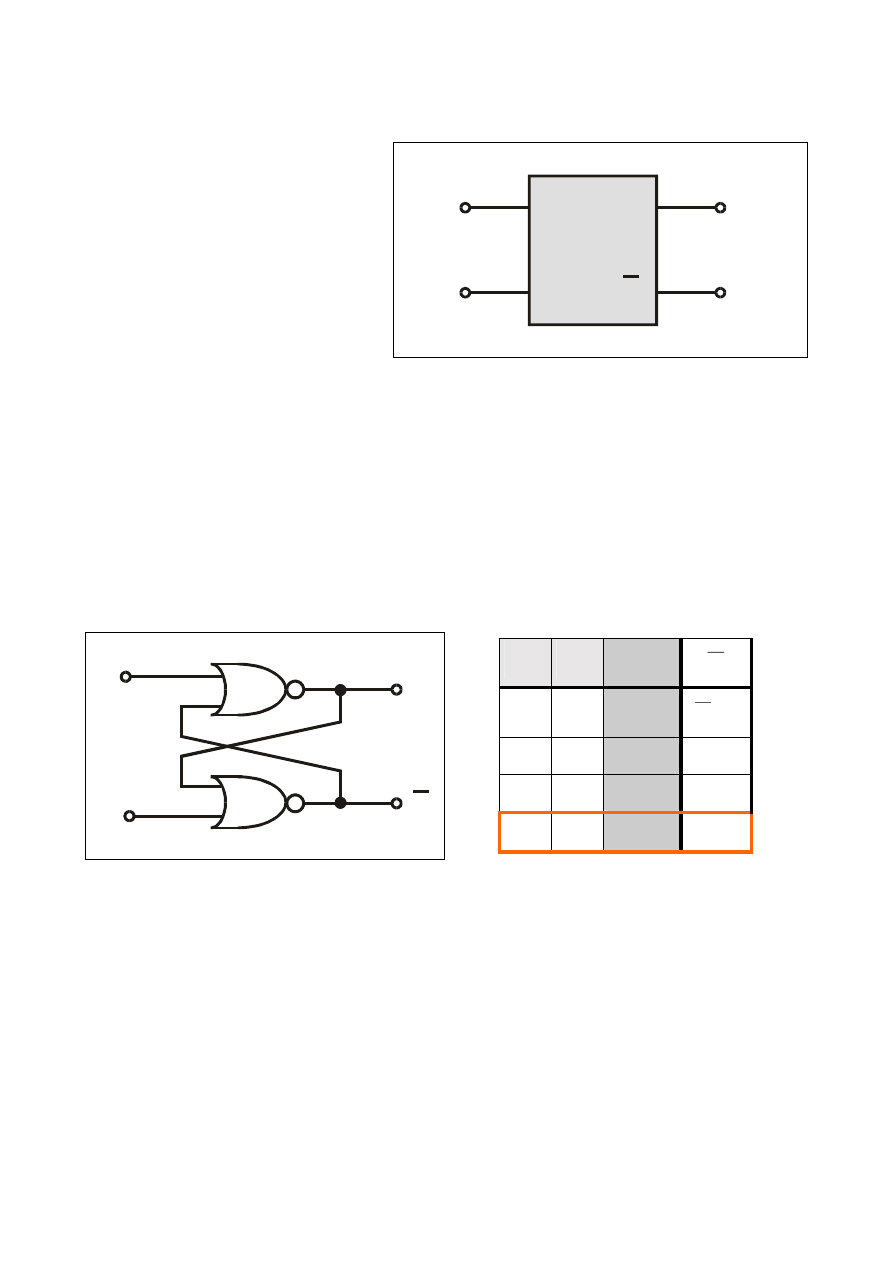

PRZERZUTNIK asynchroniczny RS

Ten typ przerzutnika RS

(

R-

reset, S-

set

), można

utworzyć z dwóch bramek

NOR

(negacji sumy logicznej)

połączonych

w

układzie

(dodatniego)

sprzężenia

zwrotnego.

R

S

Q

Q

wejście

zerujące

wejście

ustawiające

wyjście

zanegowane

wyjście

proste

Wejście S jest nazywane wejściem ustawiającym, a wejście R –

kasującym. Jeżeli w stanie spoczynku na obu wejściach panuje stan 0 – to

przerzutnik jest ustawiony w pewnym stanie zależnym od poprzednich

wartości logicznych na wejściach, a jeżeli napięcie zasilające zostało

właśnie włączone – to stan przerzutnika jest przypadkowy.

Przerzutnik RS zmienia swój stan tylko wówczas, gdy na wejściach

R i S są różne stany logiczne.

tabela stanów

R

S

Q

Q

S

R

Q

Q

0

0

Q

n-1

1

n

Q

1

0

1

0

0

1

0

1

1

1

-

-

Stan logicznie zabroniony

- 12 -

PRZERZUTNIK synchroniczny RS

PRZERZUTNIK typu D

11.6.2. REJESTR SZEREGOWY

11.6.3. LICZNIK BINARNY

Wyszukiwarka

Podobne podstrony:

Elektronika- Układy logiczne cz.1- dekodery, trans-latory.DOC, Wydz. E i A Grupa

Elektronika- Układy logiczne cz.1- dekodery, trans-latory.DOC, Wydz. E i A Grupa

04CD 05 PEiM Sensory i Układy scalone doc

Elektronika- UKŁADY LOGICZNE CZ. II.DOC, LABORATORIUM Z ELEKTRONIKI .

sprawozdanie układy logiczne ćw 4

SYNTEZEAUTOMATU, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Logika, układy LOGI

układy logiczne, ptul2, Tablice Karnaugha

Układy logiczne

Elementarne uklady logiczne

Układy logiczne cz.2, Laboratorium układów elektronicznych

Programowalne uklady logiczne

Kombinacyjne uklady logiczne

UKŁADY LOGICZNE

07.11.15 Układy urbanistyczne

07 Podstawowe uklady logiczne (2)

więcej podobnych podstron